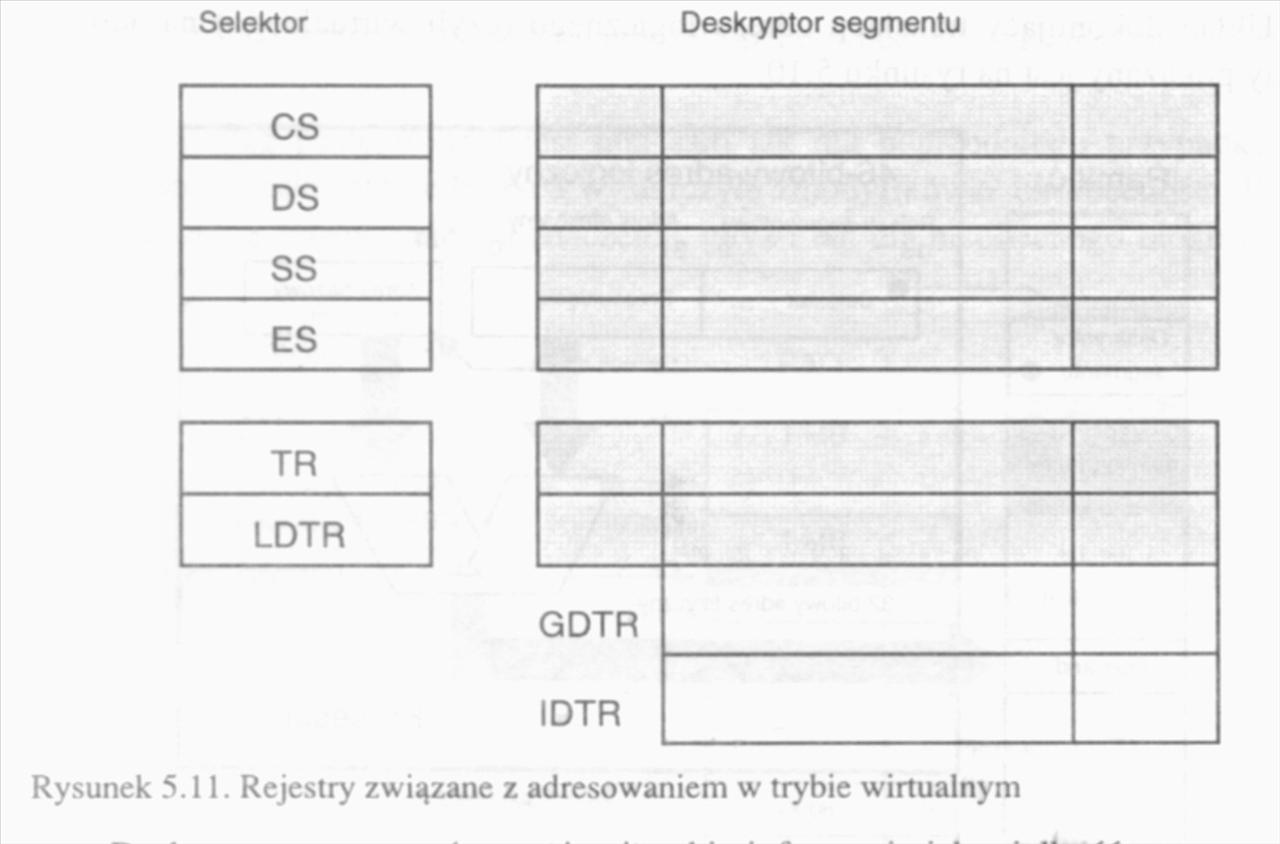

rys 5 11

Selektor

Deskryptor segmentu

|

GDTR IDTR | ||

Rysunek 5.11. Rejestry związane z adresowaniem w trybie wirtualnym

Wyszukiwarka

Podobne podstrony:

rys 2 11(1) Rysunek 2.11. Schemat blokowy karty EGA pracującej w trybie graficznym Do cyfrowego wejś

Przykład przebiegu o takim charakterze tłumienia pokazuje rysunek 11.6: -1,5 Rys. 11.6. Przykład prz

Rys. 11.2. Rysunek wykonawczy wału stopniowego

rys 1 11 Wyjście proste Wyjście zanegowane Rysunek 1.11. Symbol przerzutnika RS

rys 11 10 -0 Rysunek 11.9. Multipleksowanie w dziedzinie czasu Rysunek 11.10. Multipleksowanie w dzi

rys 11 13 Rysunek 11.13. Porównanie pracy koncentratora i przełącznika

rys 11 14 Rysunek 11.14. Regeneracja sygnału cyfrowego

rys 11 16 a) Rysunek 11.16. Topologie sieci z punktem dostępowym (a, b) i punkt dostępowy (c)

rys 11 2 11 3 Rysunek 11.2. Topologia magistrali uni tej topologii są jej prostota, mała długość kab

rys 11 2 101 100 011 010 001 000 Rysunek 11.2. Ilustracja błędu digitalizacji

rys 11 3 t Rysunek 11.3. Ilustracja znaczenia częstotliwości próbkowania

rys 11 4 11 5 3. Pierścień Rysunek 11.4. Topologia pierścienia Logiczna topologia pierścienia jest r

rys 11 5 Rysunek 11.5. Synteza dźwięków metodą FM

rys 11 6 Interfejs MIDI Rysunek 11.6. Schemat blokowy karty dźwiękowej

rys 11 7 11 8 5. Siatka Rysunek 11.7. Topologia siatki Topologia ta dotyczy w zasadzie sieci bezprze

rys 3 11(1) Strona 0 Ścieżka Sektor Rysunek 3.11. Podział dyskietki na ścieżki i sektory

Image172 (3) ■ Podstawy Rys. 11 Mostek tyrystorowy: 3-pulsowy z diodą zerową - rysunek górny; 6-puls

więcej podobnych podstron