Uklady cyfrowe kolo"I2003ў

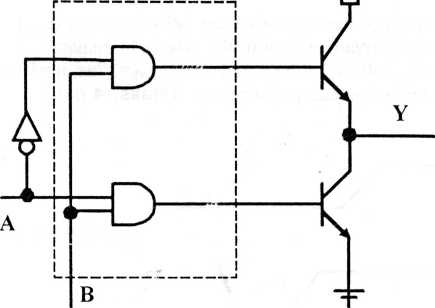

Zad. 4. MajД…c dany schemat elektryczny logiczny (rys. poniЕјej) wyjaЕӣnij, co to za ukЕӮad, narysuj jego schemat logiczny oraz uzupeЕӮnij tabelДҷ prawdy (Maks. 4 pkt).

Gr. A

X

Tabela:

Schemat log.:

|

A |

B |

Y |

|

0 |

0 | |

|

0 |

1 | |

|

1 |

0 | |

|

1 |

1 |

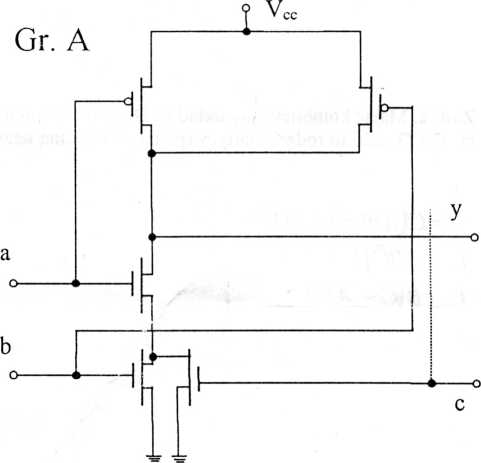

Sterowanie

Zad. 5. W powyЕјszym schemacie ukЕӮadu kombinacyjnego CMOS zapomniano wrysowaДҮ 1 tranzystor z kanaЕӮem p sterowany z wejЕӣcia (Maks. 4 pkt)

a) . UzupeЕӮnij schemat wpisujД…c brakujД…cy tranzystor,

b) . Podaj zrealizowanД… funkcjДҷ logicznД….

*

UWAGA! Wolno przecinaДҮ poЕӮД…czenia, aby wrysowaДҮ tranzystor!

y =

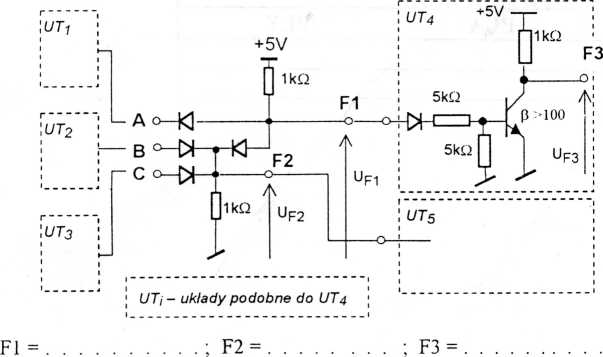

Zad.7. Dla sieci logicznej pokazanej na rysunku: a) zapisaДҮ funkcje logiczne FI, F2, F3; gdy argumentami sД… A, B, C , b) okreЕӣliДҮ wartoЕӣci napiДҷДҮ Ufi, Uf2, Uf3 , gdy argumenty A, B, C przyjmujД… nastДҷpujД…ce wartoЕӣci logiczne:

A=1,B = 0, C = 1 - oszacowania dokonaДҮ dla najgorszych warunkГіw sterowania z UT j, UT2, UT3 (Maks. 4 pkt)

ZaЕӮoЕјenia:*) PrzyporzД…dkowanie napiДҷciom wartoЕӣci logicznych: UxL ~ 0 i Uxh ~ 1 *) NapiДҷcia na wyjЕӣciu UT;

0V < UoL ВЈ 0,4V ; 2,4V < U0H ВЈ 5,0V

*) PrД…d wsteczny diody IД… В» 0;

*) Spadek napiДҷcia na

przewodzД…cej diodzie UД… = 0,7V *) UcEnas ВЈ 0,4V *) UBEnas ~ В°-5V 'в– UBEzat^ 0,2V

; Ufi =.......; Uf2 =....... Uf3 =

Wyszukiwarka

Podobne podstrony:

Uklady cyfrowe kolo I2003? vcc Gr. B Sterowanie Zad. 4. MajД…c dany schemat elektryczny logiczny (rys

Uklady cyfrowe kolo I2003? GRUPA B ImiДҷ i nazwisko, nr indeksu Zad. 1. WyznaczyДҮ maksymalnД… czДҷstotl

Uklady cyfrowe kolo I2003? GRUPA A D Q CLK Q Rys. DwГіjka liczД…ca Roz.wici~.anie ImiДҷ i naz

Uklady cyfrowe kolo I2003? GRUPA A CLK Q Rys. DwГіjka liczД…ca Roz.wici~.anie ImiДҷ i nazwis

ROZDZIAЕҒ 4 в– Cyfrowe ukЕӮady logiczne PYTANIA I POLECENIA KONTROLNE 1. Co to jest

Image423 Rys. 4.498. Schemat elektryczny ukЕӮadu Rys. 4.499. Schemat elektryczny ro

Schowek04 (12) Rys. 2. Schemat nadajnika Rys. 4. Schemat elektryczny modelu Rys. 3

44 (141) 44 UKЕҒADY RГ“WNAЕғ 17. Suma dwГіch liczb wynosi 223, a ich rГіЕјnica 25. Co to za liczby? 18. Ks

uklady logiczne 1 Rys. 1A Realizacja funkcji OR za pomocД… dwГіch wyЕӮД…cznikГіw i ЕјarГіwki. Е»arГіwka A zaЕӣ

wiДҷcej podobnych podstron