707svc 16

|

CPU HD6303X |

Port Assignment | ||||

|

Pin Configuration (Top View) |

PIN NO. |

PORT NAME |

OESCRIPTION | ||

|

HM I |

Unueed, pulled up *SV | ||||

|

2-4 |

NC |

Unueed, open | |||

|

3,c . p |

5 |

P20 |

Input, TEMPO CLOCK | ||

|

o. „‘.y fis • |

6 |

Ml |

Output, TEMPO CLOCK (DIN) | ||

|

P22 |

output, ACCEHT LEVEL tnput trlggar for Internat AOC | ||||

|

F23 |

Input, MIDI IN | ||||

|

■j. |

9 |

P24 |

output, MIDI OUT | ||

|

•yj |

10 |

P25 |

output, TAFE SYNC | ||

|

•3 |

11 |

P26 |

output, CONT START (DIN) | ||

|

sT |

12 |

P27 |

output, START/STOP (DIN) | ||

|

"U |

3* |

13 |

HC |

unused, open | |

|

:£ |

14 |

PS0 |

IRQ1 unueed, pulled down | ||

|

15 |

PSI |

IRQ2 | |||

|

Input, ACCENT LEVEI. | |||||

|

-i |

16 |

P52 |

KR unused, pulled up *5V | ||

|

3“ |

W |

P53 |

BAŁT unueed, pulled up *5V | ||

|

18 |

P54 |

RAM cartddge contiol | |||

|

•-3 |

3- |

19 |

P5S |

Input. CONT START (DIN IN) | |

|

.3 |

20 |

P56 |

Input, START/STOf (DIN IN) | ||

|

3^ |

21 |

P57 |

input, START/STOP (ro* reaote cootrol | ||

|

-3 |

|2 |

22-24 |

NC |

unueed, open | |

|

___ |

25-28 |

P60-P63 |

output, acanning algne! to LEO and KEK | ||

|

29 |

P64 |

output, Interna! TEMPO CLOCK | |||

|

30 |

P65 | ||||

|

31 |

P66 |

output, TAPE STNC TEMPO CLOCK | |||

|

32 |

P67 |

output, Trlgger (RIM SHOT:TR-707)(HI ACOCO:TV-727) | |||

|

33 |

Vcc |

Input, *59 power eupply | |||

|

34-40 |

At 3-A9 |

output, addreaa A15---A19 | |||

|

41-42 |

HC |

unueed, open | |||

|

43 |

A8 |

output, addreaa AS | |||

|

44 |

V#, |

CND | |||

|

45-52 |

A7-A0 |

output, addreaa A7---AO | |||

|

53-54 |

HC |

unueed, open | |||

|

55-59 |

07-03 |

data bua 07--03 | |||

|

60-61 |

NC |

unueed, open | |||

|

62 |

02 |

data bua 02 | |||

|

63 |

NC |

unueed, open | |||

|

64-65 |

01-00 |

data bua 01---00 | |||

|

66 |

BA |

output, unueed | |||

|

67 |

UR |

output.unueed | |||

|

68 |

NC |

unueed, open | |||

|

69 |

R/W |

output | |||

|

70 |

WR |

output | |||

|

71 |

RD |

output | |||

|

72 |

E |

output, eyetea clock IHHt | |||

|

73 |

Vi« |

CND | |||

|

74 |

XTAL |

teralnel, Utai | |||

|

75 |

EXTAL |

ceninai, Xtal or external ayatea clock ln | |||

|

76 |

NC |

unueed, opee | |||

|

77 |

HP0 |

Input, MCU aode aettlng pulled up *5V | |||

|

78 |

MP1 |

input, HCU aode aettlng pulled down CND | |||

|

79 |

RES |

input, MCU reaet (actlve Iow) | |||

|

80 |

STBY |

unuaed, pulled up *5V (actlve Iow) | |||

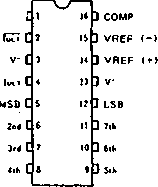

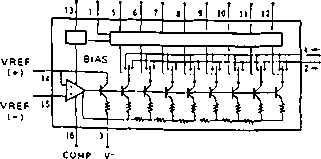

threshold,

CONT IN

V* vu wse 2ed 3rd 4tk StS 7(k LSB

|

Pm |

fii/if |

PIH |

nimf |

PIH |

nimf |

|

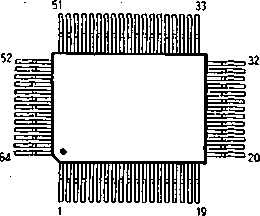

1 |

1 NHO |

23 |

CST 6 |

46 |

TTT5 |

|

1 |

ADRC |

24 |

GATE? |

46 |

W |

|

3 |

A |

25 |

GATE6 |

47 |

tstt |

|

4 |

0 |

26 |

yDO |

48 |

TST 1 |

|

5 |

e |

27 |

GATE5 |

49 |

TST2 |

|

6 |

AOR 7 |

28 |

GATE4 |

50 |

XSTA |

|

7 |

C |

29 |

GATE 3 |

51 |

USEL |

|

8 |

AOR 6 |

30 |

GATE 2 |

52 |

CEK 1 |

|

9 |

AOR 8 |

31 |

GATE) |

53 |

CLX? |

|

10 |

VS$ |

32 |

GATE 0 |

54 |

C L X 3 |

|

1 1 |

A0R9 |

33 |

KRES |

55 |

CLK4 |

|

12 |

AORb |

34 |

osc; |

56 |

XCK 0 |

|

n |

A0R8 |

35 |

scoo |

57 |

XCK ł |

|

A |

ADR4 |

36 |

SCO ł |

58 |

VOD |

|

15 |

A0R3 |

37 |

CLKO |

59 |

XCK2 |

|

16 |

A 0 R A |

38 |

xi> T 0 |

60 |

XC K 3 |

|

17 |

A DR 2 |

39 |

X 5 T i |

61 |

1ĆK4 |

|

18 |

AOR 1 |

40 |

xSTS |

62 |

KCK 5 |

|

19 |

AORO |

i \ |

x$T 3 |

63 |

xck6 |

|

20 |

CST 0 |

42 |

v s s |

64 |

JCK 7 |

|

21 |

CST 2 |

43 |

JtflUT | ||

|

22 |

csta |

44 |

kSTa |

|

DESIGNATION |

PIN |

MSCRtPTtON |

1/0 | ||

|

CST 0 |

20 |

counter 0 |

I | ||

|

2 |

21 |

> pulled up V contlnot turt counter 2 |

1 | ||

|

A |

22 |

1 C*5V) 1 |

counter 4 |

1 | |

|

6 |

23 |

counter 6 |

1 | ||

|

xsr a |

50 |

XST0-XST7 «nabl |

, aetlee Iow |

I | |

|

0 |

38 |

\ |

counter 0 |

\ | |

|

i |

39 |

counter 1 |

1 | ||

|

2 |

40 |

V counter atart, actlee Iow counter 2 |

1 | ||

|

3 |

counter 3 |

1 | |||

|

4 |

44 |

counter 4 |

1 | ||

|

5 |

45 |

cooncer 5 |

I | ||

|

6 |

46 |

counter 6 |

1 | ||

|

7 |

47 |

counter 7 |

l | ||

|

XCA 0 |

56 |

counter 0 |

l | ||

|

1 |

57 |

counter 1 |

1 | ||

|

2 |

59 |

counter |

counter 2 |

1 | |

|

3 |

60 |

clock Input |

counter 3 |

1 | |

|

4 |

61 |

counter 4 |

I | ||

|

5 |

62 |

counter S |

I | ||

|

6 |

63 |

counter 6 |

I | ||

|

7 |

64 |

counter 7 |

1 | ||

|

XOUT |

43 |

addreaa(ADRO-ADRC) ost eoable. |

•ctlee Iow; hlgh>Hl < |

I | |

|

~AD* 5" |

19 |

U | |||

|

1 |

ie |

0 | |||

|

2 |

17 |

0 | |||

|

3 |

15 |

0 | |||

|

A |

14 |

1 ROM AOORESS |

0 | ||

|

5 |

12 |

0 | |||

|

6 |

8 |

0 | |||

|

7 |

6 |

0 | |||

|

6 |

9 |

0 | |||

|

9 |

11 |

0 | |||

|

A |

16 |

0 | |||

|

B |

13 |

0 | |||

|

C |

2 |

0 | |||

|

A |

3 |

•i MUX.DMUX |

IDOkHz |

0 | |

|

B |

5 |

' l channel ' |

ayatea clock |

50kHz |

0 |

|

C |

7 |

J aelect |

'r for • |

25kHz |

0 |

|

0 |

4 |

couatera 12.5kHz |

0 | ||

|

INHO |

1 |

OKUX lohlblt |

0 | ||

|

OŚCI |

34 |

'i lnternal |

1 | ||

|

scco |

35 |

l c lock |

0 | ||

|

scoi |

36 |

) tenerator uitci clock out |

l.6KHi |

0 | |

|

Tl? Jfi |

TT |

ayatea clock In |

1.6HIU |

TT | |

|

i |

52 |

ayatea clock |

00kHz-1 |

0 | |

|

2 |

53 |

HUT |

0 | ||

|

3 |

54 |

nc |

- ROH |

lnhlblt |

0 |

|

A |

55 |

J latch clock- |

cblp eoable — |

0 | |

|

XRES |

3) |

rcaet pulae, actlve Iow |

1 | ||

|

HSEL |

51 |

counter 12/13 bit aelect |

pulled down |

I | |

|

TST 1 |

46 |

> IC teat |

pulled down |

l | |

|

TST 2 |

49 |

l | |||

|

Vss |

10 |

\ CND | |||

|

Vss |

42 | ||||

|

VOD |

26 |

power aupplr * |

iv | ||

|

CAT 5" |

32 |

T- | |||

|

1 |

31 |

> counter feta output low-counter tunnln| | |||

|

2 |

30 |

0 | |||

|

3 |

30 |

0 | |||

|

A |

29 |

0 | |||

|

3 |

28 |

0 | |||

|

6 |

25 |

0 | |||

|

7 |

24 |

0 | |||

12

Wyszukiwarka

Podobne podstrony:

Fig# Gif 0 4 8 16 19 24 32 Source Port DestinationPort Seąuence Number A ckno wie dgement Numb

19uni01 PROCESS LAYOUT TEXT Sharable Program Codę Initialized DATA Pre-defined values assigned to

ZAKLADNl ŚKOLA a MATĘ ftSKA ŚKOLA V AL8RECHTIC1CH NAD VLTAVOU ALBRECHTICE NAD VLTAVOU 139, 398 16&nb

tcp6 o 8 12 16 20 24 28 Jk Port nadawcy Port odbiorcy Num

19uni01 PROCESS LAYOUT TEXT Sharable Program Codę Initialized DATA Pre-defined values assigned to

save0008 (16) ic/CC u uLsęv I vjujLaa_ cN lO : • P> ŃT w (M OT S UJÓIO N A Pjocc?^

16(6) • ić tU.cu y Lc<f.<u o&Aufece. &6.U& Oj> AUjcCcu< Xi^U Cl

ISY-BP EOZAMINU LICENCJACKIEGO 4 ...5 ....10 12 14 16 Ic/a 1. Praw. <rtądnoś£ •

img135 (7) Zadanie 16. LP. Data Treść operacji Kurs banku (w zł) Kurs średni NBP (w

51415 Zdjęcie0628 (7) Zadanie 16. Dwa data o ciężarach G«Q clęiar Q tak aby Ima AB pn^b poto na

więcej podobnych podstron