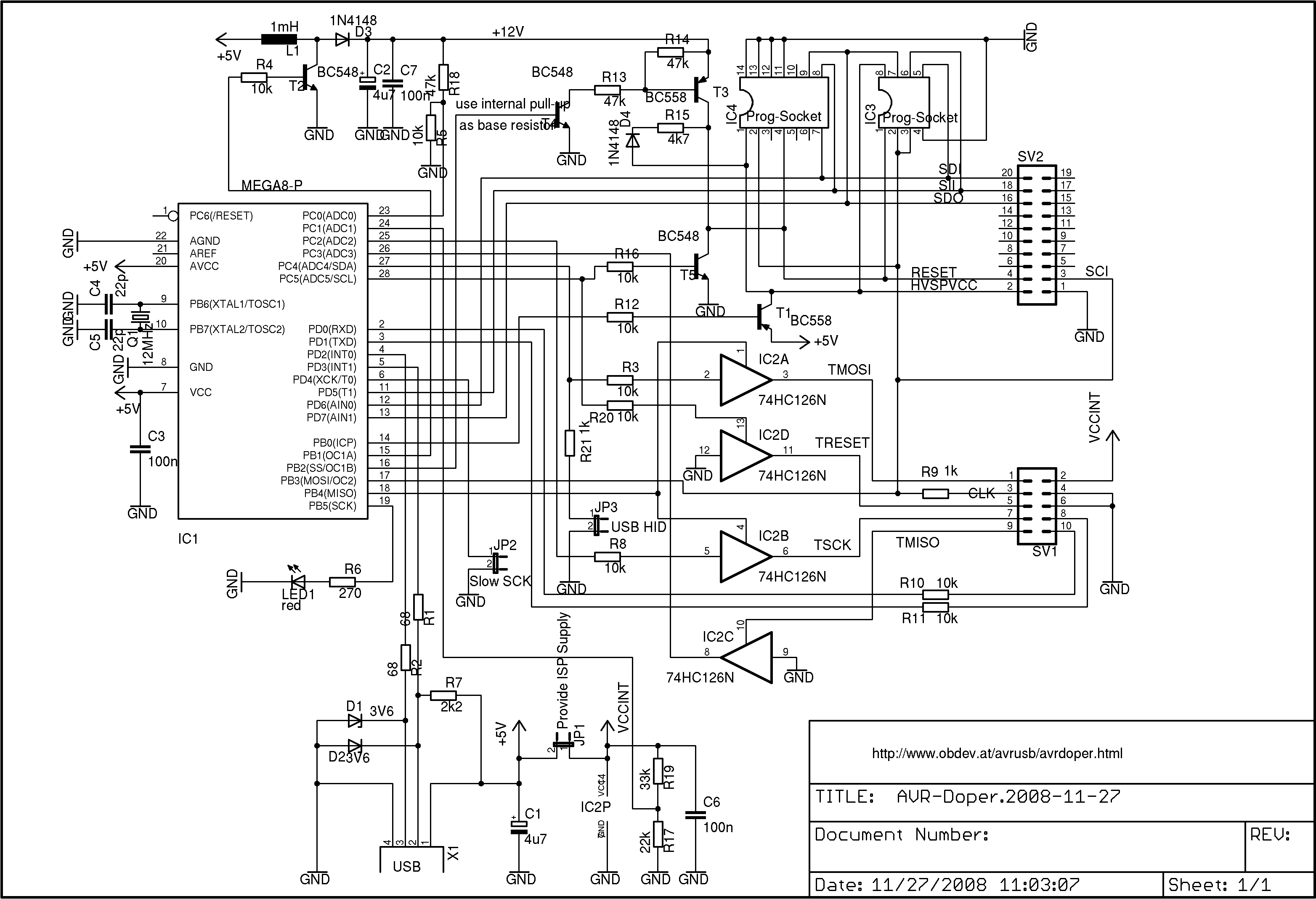

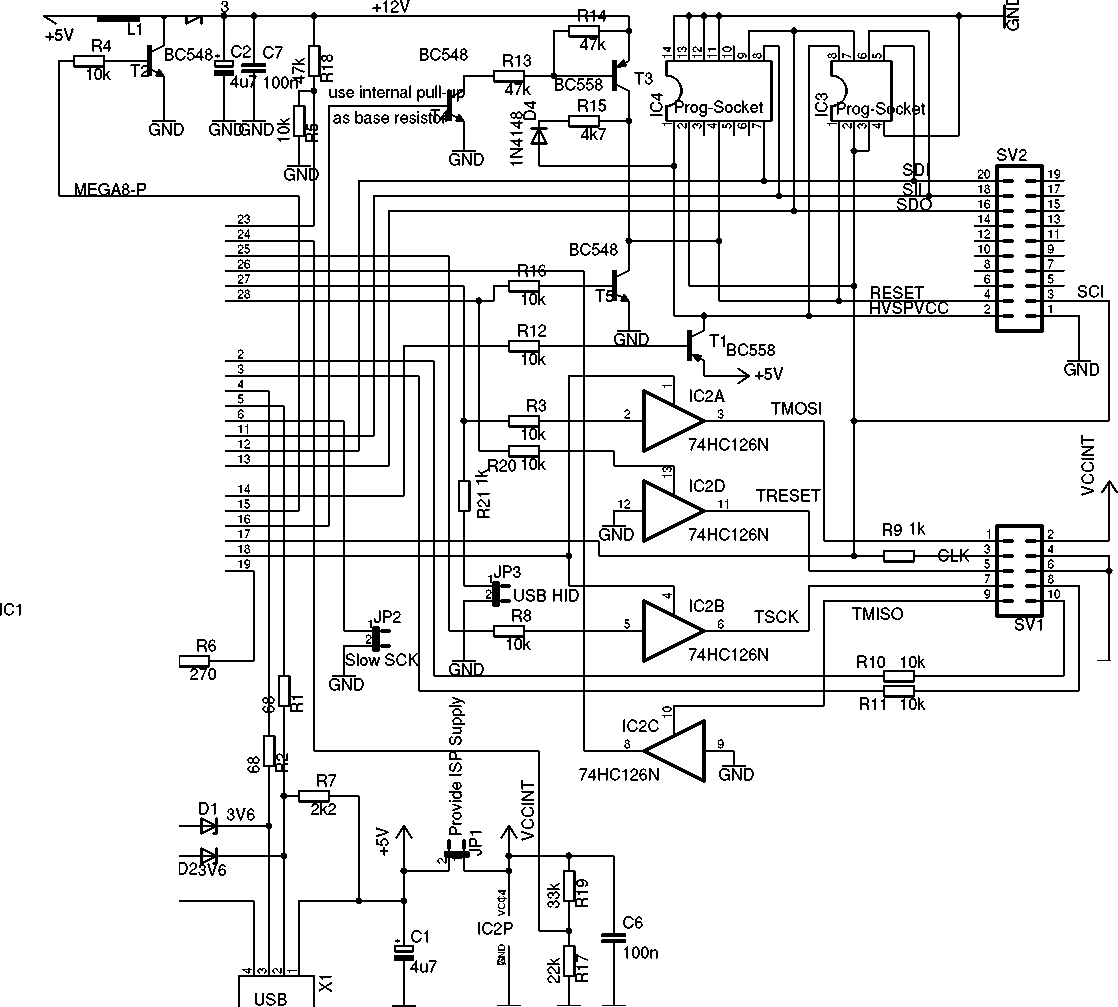

AVR Doper schematics

+5 V

C3

"lOOn

GND

1N4148

D

1mH

GND

21

20

O co ® 2

Oi ™

<r

|

PC6(/RESET) |

PCO(ADCO) |

|

PC1(ADC1) | |

|

AGND |

PC2(ADC2) |

|

AREF |

PC3(ADC3) |

|

AVCC |

PC4(ADC4/SDA) |

|

PC5(ADC5/SCL) | |

|

PB6(XTAL1/TOSC1) | |

|

PB7(XTAL2/TOSC2) PD0(RXD) | |

|

PD1 (TXD) | |

|

PD2(INT0) | |

|

GND |

PD3(INT1) |

|

PD4(XCK/T0) | |

|

VCC |

PD5(T1) |

|

PD6(AIN0) | |

|

PD7(AIN1) | |

|

PBO(ICP) | |

|

PB1(OC1A) | |

|

PB2(SS/OC1B) | |

|

PB3(MOSI/OC2) | |

|

PB4(MISO) | |

|

PB5(SCK) | |

GND

GND

GND GND GND

|

TITLE: AUR-Doper. 2008-11-27 | ||

|

Document Number: |

REU: | |

|

Datę: 11/27/2008 11:03:07 |

Sheet: ' |

./I |

Wyszukiwarka

Podobne podstrony:

avr programmer schematic AVR Próg ram mer electronics-diy.comBC549 RESET + 5V SCK MISO MOSI GND

TV2050MK5 djvu CHASSIS SCHEMATIC DIAGRAM MODEL: TV2050MK5 ’ C3 JKK., 1 lE3The Shematic Diagram from

Imobil schemat ZLI ZŁĄCZE I4PJN ♦ I2V GND PK1 PKI Zapłon Zapłon H2V Stacyjka CiN» LEP-K LEPR-A LEDCi

M* T Mo W T fte m T Md 2.96.00$ /syn.15.5}.*/ ł-5* 21 2.66.014

bat rys4 Schemat zasilacza napięcia zmiennego z automatycznie odłączanym wyjściem.1N4148 lub 1N4001

TesoroII C6 220n yCkl/IHTe/lb npM@MHMK3 C3 22P R37 270K OaaoBhm KOMnapaTop L2 20

schematic J1 Dl :C11 +12V CIO GND E Qivcc GND U3 LCD L-L+ D7 D6 D5 D4 D

DSC00552 3 i fcc, min a ( O,Oł541 MO -* 0,0464} JO,64). Is.a3 - 5.75 e(T^ Mb = (- 0,405; AAUŚ> -

30491 P1080515 Rys. 108. Schemat ciągłego wyrobu masła według metody Alfa-Laval (wg Stigena i współp

LPC11UOOARMCortex-MO Up to 50 MHz </> •3 00 LU t —i có I <High Speed GPIO Up to

mediumk5vxt25648abb1e61cd7b29721 MO, Nie przechodź obojętnie, usiądź koło mnie, na chwilę Co ro

więcej podobnych podstron