grA 2

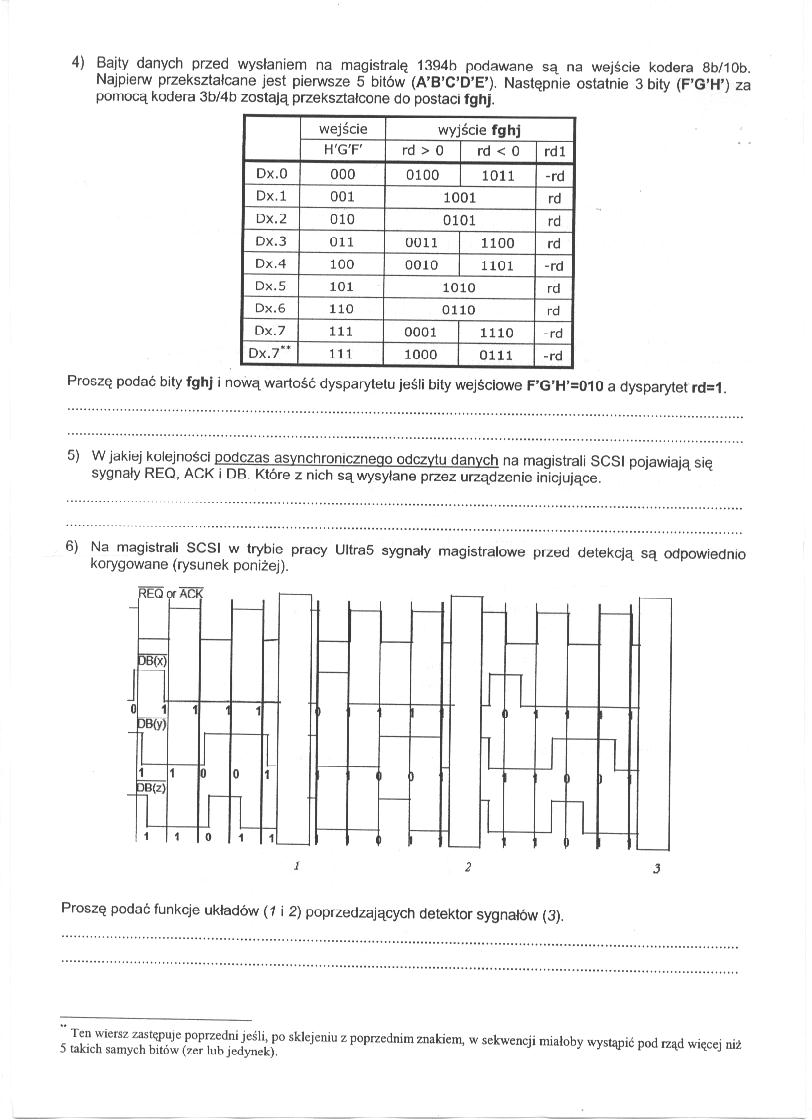

4) Bajty danych przed wysłaniem na magistralą 1394h podawane są na wejście kodera 8b/10b. Najpierw przekształcane jest pierwsze 5 bitów (A^CDT'). Następnie ostatnie 3 bity (F’G’H’) za pomocą kodera 3b/4b zostają przekształcone do postaci fghj.

|

wejście |

wyjście fghj | |||

|

H'G'F' |

rd > 0 |

rd < 0 |

rdl | |

|

Dx.O |

000 |

0100 |

1011 |

-rd |

|

Dx.l |

001 |

1001 |

rd | |

|

DX.2 |

010 |

0101 |

rd | |

|

Dx.3 |

011 |

0011 |

1100 |

rd |

|

Dx.4 |

100 |

0010 |

1101 |

-rd |

|

Dx.5 |

101 |

1010 |

rd | |

|

Dx.6 |

110 |

0110 |

rd | |

|

Dx.7 |

111 |

0001 |

1110 |

rd |

|

Dx.7“ |

111 |

1000 |

0111 |

-rd |

Proszę podać bity fghj i nową wartość dysparytetu jeśli bity wejściowe F'G’H’=010 a dysparytet rd=1.

5) W jakiej kolejności podczas asynchronicznego odczytu danych na magistrali SCSI pojawiają się sygnały REG, ACK i DR Które z nich są wysyłane przez urządzenie inicjujące.

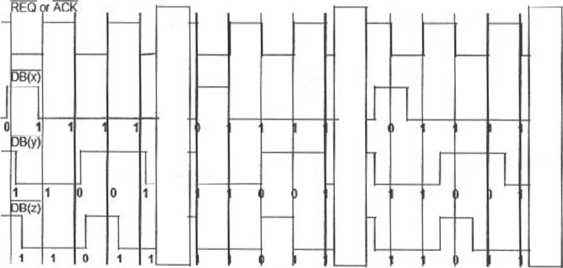

6) Na magistrali SCSI w trybie pracy UltraS sygnały magistralowe pized detekcją są odpowiednio korygowane (rysunek poniżej).

/ 2 3

Proszę podać funkcje układów (1 i 2) popizedzających detektor sygnałów (3).

Ten wiersz zastępuje poprzedni jeśli, po sklejeniu z poprzednim znakiem, w sekwencji miałoby wystąpić pod rząd więcej niż 5 takich samych bitów (zer lub jedynek).

Wyszukiwarka

Podobne podstrony:

grB 2 4) Bajty danych przed wysłaniem na magistrale 1394b podawane są na wejście kodera 8b/10b.

I IZABEZPIECZ URZĄDZENIE SZYFRUJĄC DANE Jedyną metodą na zabezpieczenie danych przed ich niepowołany

Zakończenie Możliwości, jakie stoją przed archiwum prac magisterskich opartych na XML-u, są ogranicz

Image118 lenia informacji na wejściu D (ts) przed zmianą stanu wejścia taktującego z 0 na 1 wynika z

68 grzmotem na potoku Roztoce (patrz N. 31; cennik jazdy str. 24). B) Tuż przed mostem na prawo ( &g

53 4) przed „Gierlachem” na Krupówkach (przed willą JV? 13); 5) na Chramcówkach, przed zakładem

skanuj0006 (205) 4 1 .Przygotowanie do kardiowersji -leki rozrzedzające krew; tlen; przed zabiegiem

Image8547a Datagram UDP wysłany na zamknięty port. Datagram posiada zapalony bit DF oraz rozmia

Przykładowe przebiegi charakterystyk pompy wirowej przed-stawiono na rys. 1.3. tt Rys. 1.3. Przykład

więcej podobnych podstron