wykl05

.......Architektura procesora . ' i

Modele zestawu instrukcji procesora

O Buforowy rejestr rozkazów

(ang. instruction buff er register -1BR). Jest wykorzystywany do czasowego przechowywania podręcznego rozkazu pochodzącego ze słowa w pamięci.

O Licznik programu

(ang. program counter - PC).

Zawiera adres następnej pary

rozkazów, która ma być pobrana z pamięci.

O Akumulator (AO i rejestr mnożenia-

(ang. mułtipiier-quotier - MQ). Wykorzystywane do czasowego

przechowywania argumentów i

wyników operacji prowadzonych przez ALU.

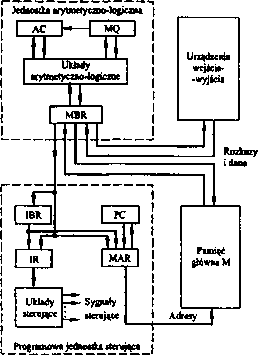

JedMftka ccfttralna

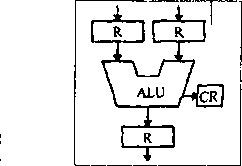

Jednostka sterująca, jak i ALU zawierają miejsca pamięci zwane rejestrami:

° ,Ręję$tr buforowy Pamięci

(ang. memory bu fter register - MBR). Zawiera słowo, które ma być przechowywane w pamięci, lub też jest wykorzystywany do pobierania słów z pamięci.

O Rejestr adresowy pamięci

(ang. memory address register - MAR). Określa adres w pamięci dotyczący słowa, które ma być zapisane w rejestrze MBR lub z niego odczytane.

o Pęjęstr rożków

(ang. instruction register - IR). Zawiera 8-bitowy kod operacyjny rozkazu, który jest wykonywany.

Jednostka centralna

Jednostka aiytmetyczno-logiczM | AC M MQ |

|

pc | |

|

Układy |

Sygnały |

|

Ucrojącc |

sterujące |

Programowa jednostka sterująca

m^or

Założenia:

i > Procesor zawiera akumulator (AC) służący do czasowego przechowywania danych.

i> Zarówno rozkazy, jak i dane są słowami 16-bitowymi. i > Pamięć jest zorganizowana przy użyciu pozycji (lub słów) 16-bitowych.

Format rozkazu wskazuje, że występuje 24 =16 różnych kodów operacji, a liczba słów w pamięci możliwych do bezpośredniego zaadresowania wynosi 212 = 4096 (4 K).

0_34___

A | Kod operacji | Adres ~ |

(a) format rozkazu;

(b) format liczby całkowitej;

(c) wewnętrzne rejestry procesora;

(d) częściowa lista kodów operacji

01_

B 1 S | Wjcjhołć

C Uczaik rozkazów (PC)" adres rozkazu

R^Mtr rozkazów (IR) - wykonywany rozkaz Akumulator (AC) “ tymczasowe przechowywanie

D

0001 - Ładtg AC z pamięci 0010-Zapisz AC w Mmkd

Lęgęnda;

Memory ( Pt Register* Mentor} CPl. Register*

Licznik rozkazów (PC) = adres rozkazu

Rejestr rozkazów (IR) = wykonywany rozkaz

|

4iKł |

i y 4 o |

— |

1 0 011*1’ |

400 |

19 4 0 |

4 0 0| Pl | |||

|

401 |

5 y 4 i |

) |

AC |

401 |

5 9 4 1 |

0 0 0 4 |

AC | ||

|

402 |

2 y 4 i |

i y 4 o |

IK |

402 |

2 9 4 1 |

19 4 0 |

IK | ||

|

_ | |||||||||

|

940 |

o o n 4 |

[300; MAR |

940 |

0 0 0 4 |

^ 9 4 0 1 MAR | ||||

|

941 |

0 (I 0 2 |

941 |

TrrrrrT | ||||||

|

Stop t |

Step 2 | ||||||||

|

Memory |

CPl Register* |

Mentor \ |

CPl. Register* | ||||||

|

400 |

i y 4 o |

4 n 1 1 IV |

400 |

19 4 0 |

4 0 l| PI | ||||

|

401 |

i y 4 i |

“■'t |

0 0 0 4 |

AC |

401 |

5 9 4 1 |

0 0 0 5 |

AC | |

|

402 |

2 y 4 i |

5 9 4 1 |

IR |

402 |

2 9 4 1 |

( |

5 9 4 1 |

ty | |

|

V, | |||||||||

|

940 |

0 0 0 4 |

[3 0_Ll MAR |

94t) |

U 0 0 4 |

Ifl |

L4 + 2 - 5—' | |||

|

*441 |

o o o : |

941 |

U 0 (1 i | ||||||

|

941| MAK | |||||||||

|

Step 4 |

Step 4 | ||||||||

|

Memory |

CPl Register* |

Memory |

CPL. Register* | ||||||

|

400 |

i y 4 o |

4 o :|i*c |

400 |

19 4 0 |

4 0 2| K | ||||

|

401 |

$ y 4 i |

0 i) 0 * |

AC |

401 |

5 9 4 1 |

0 0 0 5 |

AC | ||

|

402 |

2 y 4 t |

-P |

2 9 4 1 |

IR |

402 |

2 9 4 1 |

I |

2 9 4 1 |

IK |

|

\ | |||||||||

|

yio |

0 0 0 4 |

302 MAR |

940 |

U 0 0 4 |

) i |

9 4 1 | MAR | |||

|

941 |

0 0 0 2 |

941 |

0 0 (1 5 | ||||||

Step 5__ Step O

Akumulator (AC)

= tymczasowe przechowywanie

0001

= ładuj AC z pamięci 0010

= zapisz AC w pamięci 0101

= dodaj z pamięci do AC

Architektura procesora

Architektura procesora = zestaw zasobów logicznych dostępnych dla programisty (kompilatora)

W ogólności nie ma bezpośredniego związku z techniczną implementacją

Składniki architektury:

♦ liczba i funkcjo na In ość rejestrów procesora

♦ sposoby specyfikacji argumentów operacji

♦ sposób realizacji konstrukcji warunkowych

♦ zestaw operacji, jakie może wykonać procesor

r

Przykład działania 8K - cz.lll

CPl

Memory

Iit4rudiitn

Inslrudion

litsirudinn

l <-pc, pc<-pc+i

2. IR<-DAXE (KOD)

3. MAR <-PC PC<-PC+1

4. MBRl <-DAXE (OPRi)

5. MAR <-PC\ PC<-PC+1

6. MBRh<-DAXE (OPRh) ' MAR<-MBR

8. A<-DAXE

Architektura procesora

Składniki architektury procesora są ze sobą powiązane - nie mogą być projektowane we wzajemnym oderwaniu

Techniczna implementacja może silnie wpływać na architekturę (ograniczenia realizacji technicznej)

Problem - realizacja danej architektury w innej, niż oryginalna, strukturze procesora (zachowanie kompatybilności wstecznej, np. x86)

Zadania procesora:

Pobieranie rozkazów - odczytywanie rozkazów z pamięci

Interpretowanie rozkazów - dekodowanie w celu określenia wymaganych działań

Pobieranie danych - odczytywanie danych z pamięci lub z modułu wejścla-wy|ścla.

Przetwarzanie danych - wykonywanie operacji arytmetycznych lub logicznych

Zapisanie danych - zapisanie danych w pamięci lub w module wejścia-wyjścia.

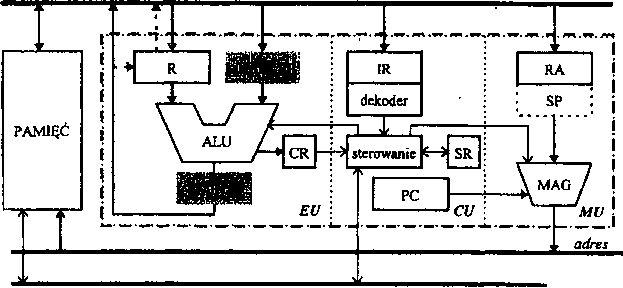

Uproszczona architektura procesora i komputera

dane

sterowanie

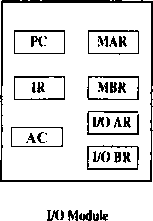

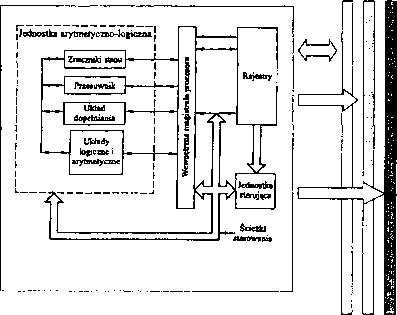

Struktura wewnętrzna procesora. Rejestry procesora

Funkcje rejestrów procesora

Rejestry widzialne dla użytkownika - umożliwiają programiście (język maszynowy/symboliczny) minimalizowanie odniesień o pamięci głównej

Rejestry sterowania i stanu - do sterowania pracą procesora oraz do sterowania wykonywaniem programów (system operacyjny)

Do rejestrów widzialnych można się odnosić za pomocą języka maszynowego, którym posługuje się procesor

Rejestry widzialne dla użytkownika:

•ogólnego przeznaczenia, czyli robocze generał purpose”), •danych,

•adresów,

•kodów warunkowych.

Funkcje rejestrów sterowania i stanu

Rejestry zasadnicze dla wykonywania rozkazów:

Licznik programu (PC) - zawiera adres rozkazu przewidzianego do pobrania.

Rejestr rozkazu (IR) - zawiera ostatnio pobrany rozkaz

Rejestr adresowy pamięci (IAR) - zawiera adres lokacji w pamięci

Rejestr buforowy pamięci (MAR) - zawiera słowo danych, które ma być transferowane

We wszystkich procesorach jest rejestr(y) stanu (PSW) - zawiera informację o stanie procesora i o wyniku wykonanej operacji.

Funkcje rejestrów widzialnych

Rejestry robocze mogą realizować wiele funkcji (dane, adresy, warunki); często ograniczenia (np. dedykacja operacjom zmiennopozycyjnym).

Rejestry danych - tylko do przechowywania danych; nie można ich używać do obliczania adresów argumentów.

Rejestry adresowe - uniwersalne lub przypisane określonym trybom adresowania

•Wskaźniki segmentu - adres podstawy segmentu (może być wiele wskaźników segmentów)

•Rejestry indeksowe - do adresowania indeksowego (mogą być indeksowane automatycznie, liczniki)

•Wskaźnik stosu - (jeśli adresowanie stosowe widzialne dla użytkownika); pozwala na adresowanie domyślne (bez jawnego adresu argumentu)

Funkcje rejestrów sterowania i stanu

Rejestr stanu (PSW)

Pola rejestru stanu (znaczniki stanu, czyli flagi):

•Znak - bit znaku wyniku ostatniej operacji arytmetycznej

•Zero - ustawiane, gdy wynik jest równy zero

•Przeniesienie - ustawiane, gdy w wyniku operacji przeniesienie

•Półprzeniesienie - ustawiane przy przeniesieniu pomiędzy tetradami

•Równość - ustawiane, gdy w wyniku porównania logicznego jest równość.

•Przepełnienie - ustawiane, gdy w wyniku operacji następuje przekroczenie zakresu.

•Zezwolenie/blokowanie przerwania - do sterowania obsługą przerwań

•Nadzorca - wskazuje, czy procesor pracuje w trybie nadzorcy

• Brak (pamięć - pamięć)

* Minimalny (akumulatorowa)

♦ Mały zestaw rejestrów specjalizowanych

♦ Mały zestaw rejestrów uniwersalnych

* Duży zestaw rejestrów uniwersalnych

• Zestaw rejestrów jako bufor ramki stosu

• Stosowy zestaw rejestrów

Architektury procesorów. Rejestry

Akumulator Rejestr znaczników Rejestr adresowy Wskaźnik stosu Licznk mstrukcj

Motorola 6800

Architektura akumulatorowa (minimalny zestaw rejestrów)

Architektury procesorów. Rejestry

Bezrejestrowa (pamięć-pamięć)

• Muszą zawierać 1 3 rejestry w tym PC

• Operacje na danych ‘'pamięć-pamięć"

• Obecnie prawie me spotykane

• Architektura Jmove"

• Lokacje przestrzeni adresowej odwzorowane w rejestry

• rejestry są 'ukryte' pod postacią komorek pamięci

• Współczesny przykład mikrokontrolery MA<Q firmy Maxim akumulatorowa (minimalny zestaw rejestrów)

• PC - licznik instrukcji

• SP-wskaźnik stosu

• Akumulator (pełni rolę rejestru wartości)

• Rejestr adresowy do adresowania struktur danych

• Przykład mikrokontrolery 8-bitowe Freescale (dawniej Motorola) rodziny 68HC08

Architektury procesorów. Rejestry I 1 2

cd... rejestrowa

c) duży zestaw rejestrów uniwersalnych

• 16 lub 32 rejestry uniwersalne

• Przykłady

• MIPS IBM Power - 32 rejestry

• AMD64. IBM S/3G0 zSenes - 16 rejestrów

• Rejestry używane do przekazywania kilku parametrów i przechowywania kilku zmiennych lokalnych

• Istotna redukcja liczby odwołań do pamięci

d) duży zestaw rejestrów danych i duży zestaw rejestrów adresowych

• Przykłady:

• MC68000

Przykłady organizacji rejestrów I

...mały zestaw rejestrów uniwersalnych (ad. b)

Ktjnlr) «g4l»r

|

^ U I |

AX |

i | |

|

E3.\ 23 ^ |

3X | |

|

fctN |

C.\ | |

|

FD\ ’ | |

_D\ |

‘ I |

|

m 7. I I |

’1p |

--T j |

|

EBP | |

BP | |

|

nsi > .. i |

SI |

1 |

|

EDI | __ |

Dl |

_ ! |

$Ua pn>xnuna

Rejestry macjrwko* tfaiiu W.vLwj;ik rc^Lun

Organizacja rejestrów w i8386

•Zestaw trybów adresowania umożliwiający adresowanie wszystkich rejestrów •Nowe instrukcje mnożenia (likwidacja przywiązania rejestrów do instrukcji) •Znacznie elastyczniejsze wykorzystanie rejestrów niż w poprzednich x86

Intel 386

|

Rejestry ogółaego przeznaczenia | |

|

AA |

Akumulator |

|

EJX |

Bazowy |

|

cx |

ZiKujący |

|

I)X |

Danych |

|

Wikniniki i indeksy | |

|

SP |

Wskaźnik «ovu |

|

BP |

Wskaźnik bazy |

|

SI |

Indeks źródła |

|

Dl |

(nil cntejsca prze/. j |

|

Segmentowe | |

|

CS |

Kod ) |

|

PS |

Dwie » |

|

ss | |

|

F.S |

Dodatkowy |

|

Stel profmna | |

|

Wskaźmk rozkazu | |

|

Znaczniki ttanu | |

Ogólnego przeinaczenia

Rejestry pełnia dowolną funkcję (danych, adresowe, wskaźnikowe itd.)

Krjcitn «cółor|»ti prte/aacrmia

WakaraiŁ >tosu

Przykłady organizacji rejestrów I

..mały zestaw rejestrów specjalizowanych (ad. a)

Struktura procesora i organizacja rejestrów w i8086

• AX - akumulator

• DX - rozszerzenie akumulatora dla mnożenia i dzielenia

• CX - licznik iteraqi

• BX - główny rejestr adresowy

• SP - wskaźnik stosu

• BP - wskaźnik ramki

• SI, D - pomocnicze rejestry adresowe

• IP - licznik instrukcji

• FLAGS - rejestr znaczników

Niektóre rejestry „przywiązane” do pewnych instrukcji

Przykłady organizacji rejestrów I

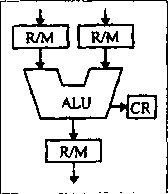

...duży zestaw rejestrów uniwersalnych (ad. c)

Organizacja rejestrów w procesorach Zilog

RM RM RR-J JŁR6 RRS RR 0

rr::

RRK RRU. RR! 3 RR lii

hjri:

RR'J _ RR2t> r KRih I RWuf

Przykłady organizacji rejestrów I

...duży zestaw rejestrów danych i duży zestaw rejestrów adresowych (ad d)

|

Rejestry danych | ||

|

DO | ||

|

D! | ||

|

d: | ||

|

Dl | ||

|

Ol | ||

|

D5 | ||

|

Dft | ||

|

D7 | ||

|

Rejestry Adresu | ||

|

AO | ||

|

A] | ||

|

A2 | ||

|

AJ | ||

|

A4 | ||

|

A5 | ||

|

A6 | ||

|

A7 |

WikaJsuk ilosu użytkownika | |

|

AT |

Wikaatik stocu nadcorcy | |

|

Stu proframn | ||

|

f Licznik rozfcjurtw | ||

|

| Rejestr stanu | ||

Organizacja rejestrów w procesorach Motorola 68k

MC680000-16/32 bit MC680020 - 32 bit

Architektury procesorów. Rajastry I 4 3

•architektura rzadko stosowana

stosowa

SP 1

j----1**

a) zestaw rejestrów stosowych

3 8 rejestrów tworzących stos

Często brak nazw rejestrów

Operacje wykonywane na wierzchołku stosu rejestrów

* Bezargumentowe lubjednoargumentowe

• Argumenty pobierane z wierzchołka stosu, wynik odkładany na stos Przykłady

♦ Transputery

• Jednostka zmiennopozycyjna x87

b) Bufor ramki stosu

• Duży zestaw rejestrów (32 128), który z założenia ma mieścić prawie całą ramkę stosu (bez zmiennych strukturalnych)

• Dwa rozwązania

* Okna rejestrów - SPARC

* Bufor stosu -Am29k. IA-64 (Itamum)

• Wykonanie procedury niemal bez odwołań do pamięci

Tryby adresowania I

Tryby adresowania

Tryb adresowania = sposób wyznaczenia lokalizacji argumentu

i

• Tryby adresowania argumentu operacji

|

Tryb adresowania |

Zanaczenie |

|

natychmiastowe (immediate) |

w instrukcji podany jest argument |

|

bezpośrednie (direct) |

w instrukcji pole adresu argumentu |

|

przez implikację (implied) |

instrukcja określa jak wyznaczyć adres |

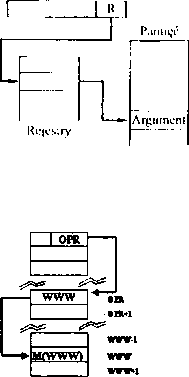

Rozkaz

Adresowanie natychmiastowe -----------------------> | | Argument |

adresowanie przez implikację

- pośrednie

- z przesunięciem

- indeksowe

- względne

Adresowanie bezpośrednie

•Rejestrowe - w instrukcji wskazany rejestr •Bezwzględne - w instrukcji zawarty adres •Strony zerowej - w instrukcji skrócony adres

Rozkaz

H a .......I

Pamięć

Aiguiiient

Rc|cst»y

Argument

ADR=RX

• Adresowanie pośrednie rejestrowe

OPR wskazuje rejestr w którym znajduje się adres operandu

Zwykle rejestry mogą być inkrementowane lub dekrementowane oddzielnymi rozkazami albo auto-inkrementowane i auto dekrementowane.

• Adresowanie pośrednie pamięciowe

ADR=M(OPR)

zastosowanie: rrlokacja tabtic, zmiennych i podprogramów.

Z uwagi na pcwołność niechętnie stosowany.

Rożka/

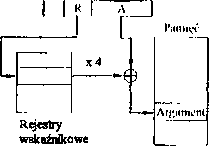

• Adresowanie z wykorzystaniem rejestru

indeksowego _

może być skalowany

ADR=1X+0PR Kózka/

|

wskaźnik adresu _^ 1 |

1 i 1 |

A T |

Z] | ||

|

bazowego /x |

1 |

L |

Pamięć | ||

|

przesunięcie - | |||||

|

Zflstos: aOrtsowame tablic (macierz) | |||||

|

obHc&nia iteracyjne (autoinkrcmenf) |

Argument | ||||

|

fynamicz/tt retokowatde tablic |

Rejestry | ||||

Przykład:

IX=AA00h

-► ADR= AA05h

OPR=05h

Tryby adresowania I

|

-U | ||||

|

I ± PRZESUNIECIE I ^ | ||||

|

-przes | ||||

|

I PC I— | ||||

|

L |

+przes \ |

f | ||

|

zastos: skoki, | ||||

|

ułatwia relokację | ||||

|

• adresowanie wzgl. liczn. rozkazów | ||||

Przykład;

PC=FF05h

OPR=FFh (-1)

ADR= FF04h

I

Tryby adresowania i

I

!

!

Segmentacja

•w celu organizowania programów i danych; kojarzenia atrybutów przywileju i ochrony z rozkazami i danymi.

•pamięć widziana jako wiele przestrzeni adresowych (segmentów); zwykle programy, dane, stos -przypisane do różnych segmentów

•segment może mieć przypisane prawa dostępu i użytkowania.

•Lokalizacja danych * adres określony na podstawie numeru segmentu i adresu względnego.

Ku/kay.

segmentów

Np. N=16

Rejestry

Np. jeżeli długość segmentu 64 kB • adres wewnętrzny w segmencie (przesunięcie) - 16-bitowy.

Początek segmentu w rejestrze wskaźnikowym segmentu; często „krótszym” od słowa adresowego, np. adres 20 bitów (1MB), długość wskaźnika 16 bitów (uzupełniany nieznaczącymi zerami).

•CS - segm programu •DS - segm danych •SS - segm stosu •ES - segm dodatkowy

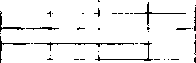

Tryby adresowania w Pentium

Algorytm Argument - A LA - R

I.A - tSR» i-A IA tSUM-(U)

LA (SIOi(in + A LA - (SU) i (I) x S +A LA ^ (SR) 4 (B) ł (I) i A

LA - (SR) + (h x S 4 (B) 4 A LA = (PC) + A

Tryb

Natychmiastowy Rejestrowy Z pi zesunięciom Z rejcsliem podstawowym / rcjcslrem podstawowym /. przesunięciem Skalowane indeksowanie z. przesunięciem / lejesliem podstawowym z iinleksem i / pi/osunięciem

Z rejestrem podstawowym ze skalowanym indeksowaniem i z przesunięciem Względny

Model operacji warunkowych i

• Określa sposób realizacji przez procesor operacji warunkowych

* Model ze znacznikami

• Model bez znaczników ('porównaj i °)

♦ Model z predykatami

PSW (FLAGS) !“

• Znaczniki - jednobitowe rejestry atrybutów wynjkujistatnio "

wykonanej operacji 5———

* Zwykle zgrupowane w jeden kilku bitowy rejestr

• Operacja warunkowa realizowana za pomocą dwóch instrukcji

* Ustawienie znaczników

* lnstrukqa warunkowa zależna od ustawienia znaczników

Model operacji warunkowych 1

Model operacji warunkowych

i

12 11 10 9876543210

• Ł1;,"1:.1’i i1 .....t'1^4 1 r"'.r-i" 1 i;v".

|

n |

ists |

m |

CF |

OF - nadmiar SF - znak ZF - zero

AF - przeniesienie pomocnicze PF - parzystość CF • przeniesienie

• Instrukcja specyfikuje warunek wykonania

• jeśli warunek me jest spełniony instrukcja wykonuje się jako pusta

• Skoki warunkowe - dostępne we wszystkich architekturach

• Przesłania warunkowe - dostępne w nowszych procesorach

• umożliwiają eliminaqę częśa skoków i przyspieszenie wykonania kodu

• Ustawienie (SETcc)

• zamienia wartość logiczną warunku na wartość danej cakowitej

• Architektury z warunkowym wykonaniem większości instrukcji -npARM

• eliminaqa znacznej części skoków w rozwmęciach krótkich konstrukcji typu if-then-else

„zakodowane” w kodzie instrukcji

Warunki wykonania instrukcji

• Specyfikowane jako wartość jednego znaczni ______

logiczne na wartościach kilku znaczników

• Symboliczne oznaczenie nazwy warunku stanowi część nazwy instrukcji warunkowej, np JNZ - “jump if not zero"^__^

„zakodowane” w mnemoniku

Usta instrukcji procesora i

Modele procesorów ze względu na listę instrukcji

Procesory CISC Procesory RISC

mb Inne modele instrukcji warunkowych I

Model bez znaczników

• Pojedyncza instrukcja ewaluuje relację i wykonuje operację jeśli relacja jest spełniona

* np "skocz jeśli zawartości rejestrów równe'

• Charakterystyczny dla prostych procesorów RISC, np MIPS

Model z predykatami

• Predykaty - uogólnione znaczniki, mogą przechowywać wartość logiczną dowolnej wcześniej obliczonej relacji

• Duża liczba predykatów w procesorze - możliwość równoczesnego przechowywania wartości wielu relacji

• Instrukcje w większości warunkowe, specyfikują numer predykatu jako warunek wykonania

• Model zaimplementowany w architekturze IA-64 (ltanium)

i

i

i

Model CISC

• Podejście stosowanie w latach 60-tych i 70-łych XX w

• Zakłada odpowiedmość pomiędzy instrukcjami procesora i instrukcjami języka wysokiego poziomu

• instrukcja języka wysokiego poziomu jest za zamieniana na jedną lub kilka instrukcji procesora

• Rejestry służą tylko do tymczasowego przechowywania wyników pośrednich i adresów, dane znajdują się w pamięci

• instrukcje operują na danych w parnię a

• Instrukcje operują na argumentach o różnych długościach

• bajty, słowa 16-. 32. ew 64-bitowe

• długość argumentu zapisana w kodzie instrukcji

Procesor CISC

♦ Bogaty repertuar trybów adresowania

• konieczny dostęp do argumentów operacji w pamięci

• zwykle operacje stosowe zrealizowane w liście instrukcji

♦ Operacje warunkowe - najczęściej z użyciem znaczników

♦ Dominują instrukcje dwuargumentowe - wynik zastępuje argument źródłowy

• specyfikacja dwóch argumentów wymaga mniejszej liczby bitów w obrazie binarnym instrukcji niż specyfikacja trzech argumentów

• rejestry przechowują tymczasowe wyniki obliczeń - nowy wynik tymczasowy zastępuje poprzedni

Procesor RISC l

• Skalarne dane lokalne procedury są przechowywane w rejestrach

* Odwołania do pamięci głównie w prologu i epilogu procedury -przeładowanie ramki stosu

• Duży zestaw rejestrów - min 16, zwykle przynajmniej 32

* rejestry powinny mieścić skalarne argumenty i dane lokalne procedury

• Instrukcje trój argumentowe - nie niszczą argumentów źródłowych

* dane lokalne nie są zamazywane podczas wykonywania na nich operacji

• Rzadkie odwołania do pamięci nie wymagają złożonych trybów adresowania

* proste kodowanie instrukcji

Model RISC I

• Podejście RISC wprowadzono na początku lat 80-tych XX wieku

• projekt IBM 801

• architektury MIPS i Berkeley RISC

• Wtedy również wprowadzono skróty O SC i RISC

• Ważniejsze współczesne architektury RISC

• MIPS

• SPARC

• ARM

I

I

L

i

i

I

• Proste instrukcje dają się wykonać w prostej i szybkiej jednostce wykonawczej

• Każda instrukqa ma tylko jeden argument docelowy

• Najwyżej jedno odwołanie do pamięci

• Złożone operacje można zsyntezować z kilku instrukcji

• Również tryby adresowania

• Instrukcje arytmetyczne i logiczne operują tylko na danych w rejestrach i argumentach natychmiastowych

• długość argumentu jest zwykle równa długości rejestru

• brak operacji 8- i 16-bitowych

• Tylko dwa rodzaje instrukcji operują na pamięci

• Load - ‘ładuj"

• Storę - ‘składuj’

• Tzw ‘architektura load-store’

CISC vs RISC

Mniejsza objętość programu

SOURCEiARSTECHNKA

•Prostsze instrukcje •Stały format

•Krótki, „stały” czas wykonywania •Łatwiejsza realizacja potokowości

1

Wykonanie operacji przez CISC:

MULT 2:3, 5:2 ___

Wykonanie operacji przez RISC:

LOAD A, 2:3 LOAD B, 5:2 PROD A, B STORĘ 2:3. A

I

RISC _lr CISC

• I nstrukcje są zapisane w pamięci podobnie jak dane - w postaci słów binarnych

• Poszczególne instrukcje procesorów CISC mają różne długości

• procesory x86 - instrukcje zajmują od 1 do 15 bajtów

• w innych architekturach granularność instrukcji jest wyrażana w

słowach 16-bitowych___________________________

• RISC - stała długość instrukcji

• w typowych procesorach RISC (np MIPS. ARM) - każda instrukcja ma długość 32 bitów (4 bajtów)

• ARM Thumb - instrukcje 16-bitowe. dwuargumentowe

• Zapis instrukcji

• kod operaqi

• specyfikacja argumentów

• Complex Instruction Set Computer, Reduced Instruction Set Computer

• Chodzi o złożoność poszczególnych instrukcji, a nie o liczbę dostępnych instrukcji

• Procesory RISC często wykonują więcej instrukcji niż procesory CISC

• Skomplikowane instrukcje wymagają złożonej jednostki wykonawczej

O • Duża liczba odwołań do danych w pamięci spowalnia wykonanie

W programu

O • Duża liczba i złożoność trybów adresowania powoduje

wydłużenie pól specyfikacji argumentów w zapisie binarnym instrukcji

• Więcej instrukcji - dłuższa postać binarna programu O • Wszystkie instrukcje mają taką samą długość obrazu binarnego (O * Zwykle 32 bity

£ • Jeden lub dwa tryby adresowania pamięci - rejestrowy pośredni z

przemieszczeniem, ew dwu rejestrowy pośredni

o

spice matm nasa7 Ipppp tomcatv doduc espresso egntott

li

Rejestrowa

a) mały zestaw rejestrów specjalizowanych

• 6 8 rejestrów pełniących różne, sztywno określone funkcje

• Przykład -x86 w trybie 16-bitowym

• Brak możliwości efektywnego wykorzystania rejestrów przez kompilator

• Rejestry służą wyłącznie do obliczeń i przechowywania wyników pośrednich

b) mały zestaw rejestrów uniwersalnych

•68 rejestrów uniwersalnych

• Przykład - x86 w trybie 32-bitowym

• 8 rejestrów (EAX EDX ECX EBX ESP EBP ESI EDI)

Wszystkie rejestry mogą służyć jako akumulatory i rejestry'adresowe wszystkie poza ESP - jako rejestry indeksowe

• 3 4 rejestry mogą być użyte dla zmiennych lokalnych lub parametrów

• alokacja obiektów lokalnych w rejestrach przyspiesza wykonanie kodu

wolniejsze wykonanie operacji z użyciem pamięci niż operacji z użyciem rejestrów

uniwersalna

• lista rozkazów nie preferuje użycia rejestrów lub pamięci

Szczegółowe zasady ustawiania znaczników są zdefiniowane w dokumentacji modelu programowego każdego procesora

• Wszystkie znaczniki są ustawianie przez podstawowe dwuargumentowe instrukcje arytmetyczne i logiczne

• Inne instrukcje (np jednoargumentowe) - nie zawsze wszystkie znaczniki

• W niektórych architekturach znaczniki zera i znaku są ustawiane przez instrukcje przesłań

♦ np M68k. HC08

Wyszukiwarka

Podobne podstrony:

wykl05 .......Architektura procesora . iRejestry procesoraTryby adresowaniaInstr

Architektura procesora (2) ALU- lista operacji zestaw rejestrów -

Architektura procesora CISC Cechy architektury CISC (Complex Instruction Set Computers): *

Architektura procesora RISC Cechy architektury RISC (Reduced Instruction Set Computer): *

IMAG0647 (5) Architektura x861 liczba cykli zegara na instrukcję (procesory klasyczne - bez potoków,

Architektura procesora CISC Cechy architektury CISC (Complex Instruction Set Computers): *

Architektura procesora RISC Cechy architektury RISC (Reduced Instruction Set Computer): ■k Zredukowa

Slajd22 (109) Schemat blokowy procesora 0.13pm IU - instruction unit + stała pamięć ROM EU - executi

Architektura procesora (1)Architektura procesora określa najważniejszych z punktu widzenia budowy i

Rodziny procesorów (Intel) x86 to rodzina architektur procesorów firmy Intel, należących do kategori

& Rodziny procesorów (AMD) AMD64 (tylko AMD) (x86-64 lub x64) to 64-bitowa architektura procesor

Najważniejsze spośród rozszerzeń dodanych do architektury procesorów MMX (MultiMedia eXtenntion) -

IMAG0650 (5) Architektura x86 - tryby adresowania (wybrane) Bez dostępu do pamięci: •

Architektura procesorów Intel

Instrukcje programowe mikroprocesora I80C51 Tryby adresowania • Natychmiastowe

Zarządzanie procesamiLiteratura podstawowa (Ciesielski M. Instrumety zarządzania łańcuchami dostaw.

więcej podobnych podstron