DSCF0348

'nn

M2

<> " O MP

Stoik /

Soft node

-HL"1

+

O, zĄz VUO

V

VJS»-(Vm-Vjr)

FIGURĘ 8.6 Circuit levcl model for soft node leakage.

Ł-S

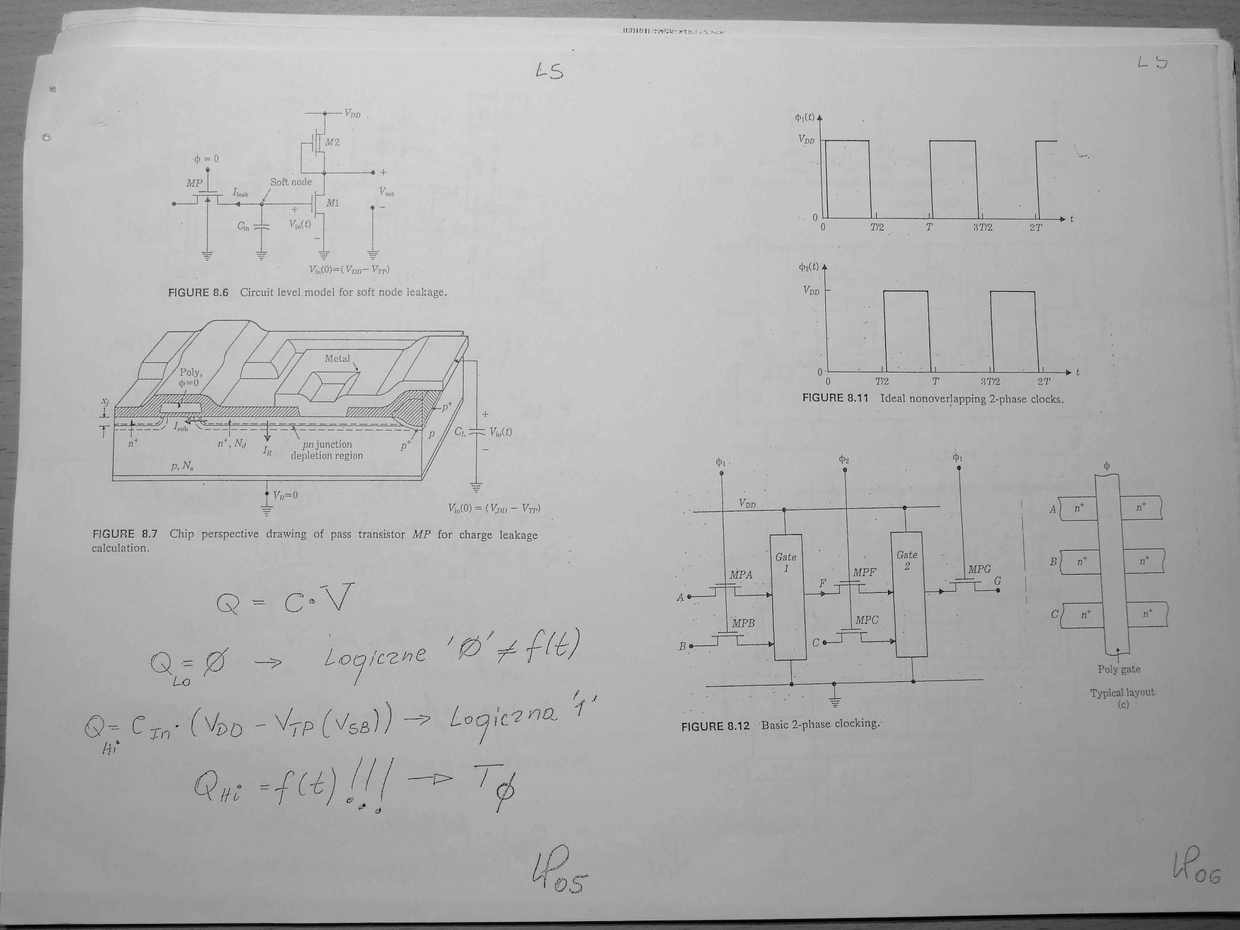

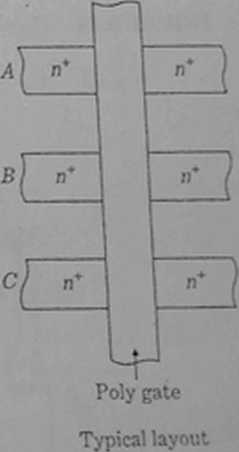

FIGURĘ 8.7 Chip pcrspcctivc drawing of pass transistor MP for charge leakage calculation.

G> - C-V

Lonicz^e

7

/

/

Q~ (/^ LoCj\C.'2

1

='f^)

/

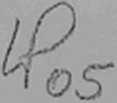

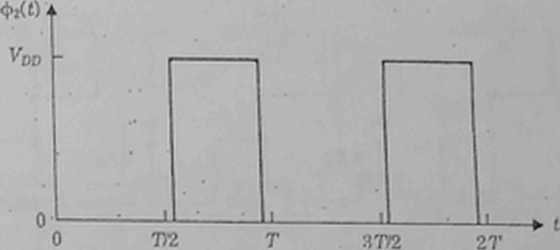

FIGURĘ 8.11 Ideał nonovcrlapping 2-phase clocks.

<*>, •

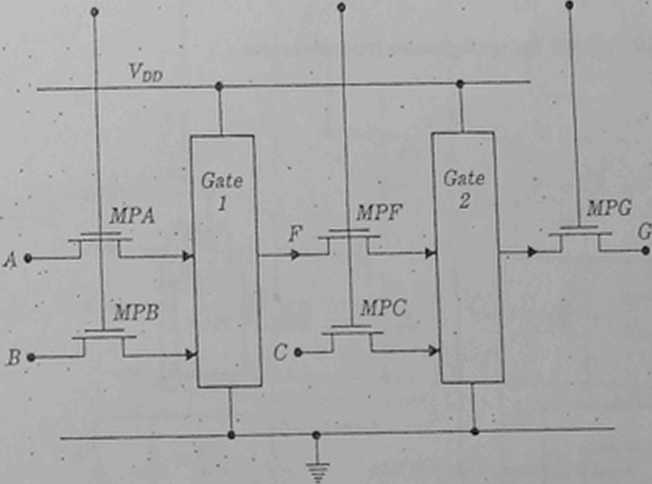

FIGURĘ 8.12 Basic 2-phase clocking.

<>

(O

Wyszukiwarka

Podobne podstrony:

Radio Network Controller (RNC): Manages the radio resources of each of the Node Bs that are connect

DSCF0347 u "lip ii rw + ♦- Vjp *» O ‘1 <t>“lI, MP C= VfM) M2 —-• + vm- Voll + *u -

n/n n/nn n/nnn z/n z/nn z/z z/zz KRZ Kp ~Kp K~p Mp ~

1 nh»h * ‘/i u N»*ut !U Ąybfdi lity 1 Jut * mi A w tę! WL/hł ifśitttnU ii mp/ą t>0**r"U

Introny i g«ny irttronow* - c.d. i HUillltiif M2. Hł M, ii

DSC00295 (8) J, if‘ V i« ** 1 —r"* MP‘*- -v4~jy ___L*,. C(-., jlM y i*, j....... * 1 • »pTł H»

nauka o literaturze nn! 1 Siłi Hl V *,ł fł t>

Zdjęcie0080 (6) u9flM0

71 mieć postać Hl : mi / m2 albo H£ : , albo H-j : nij > Zaleca się stosować je

DSC09187 M«m wimMkt Km ■ >nn mp*l I MwwU Mm)rffc> S^W wini. foijotfU ■MHMM

39809 str17 (23) Przykład 1 (ciąg dalszy). Błąd pola powierzchni działki wynosi (rys. 4.3.1): mp - 1

DSCF0357 L S 2 as a o!a dnia ta a!cc Jxn r ^do </f=i -*> mP, } Mu * Od ^

Hamnoy Rainbow Sakrisoy Island Lofoten Islands Norway u V, ^ /, nn ? i ■Hł ra: i; 2El

■ s 1 mt rn n VI m nn " Mp] m iw n ■fel *• fi -- . yl ■ _ * *1 .

lilii! ™ pjj^jpi^j ni^ I / ^Hl f

więcej podobnych podstron