PLD21

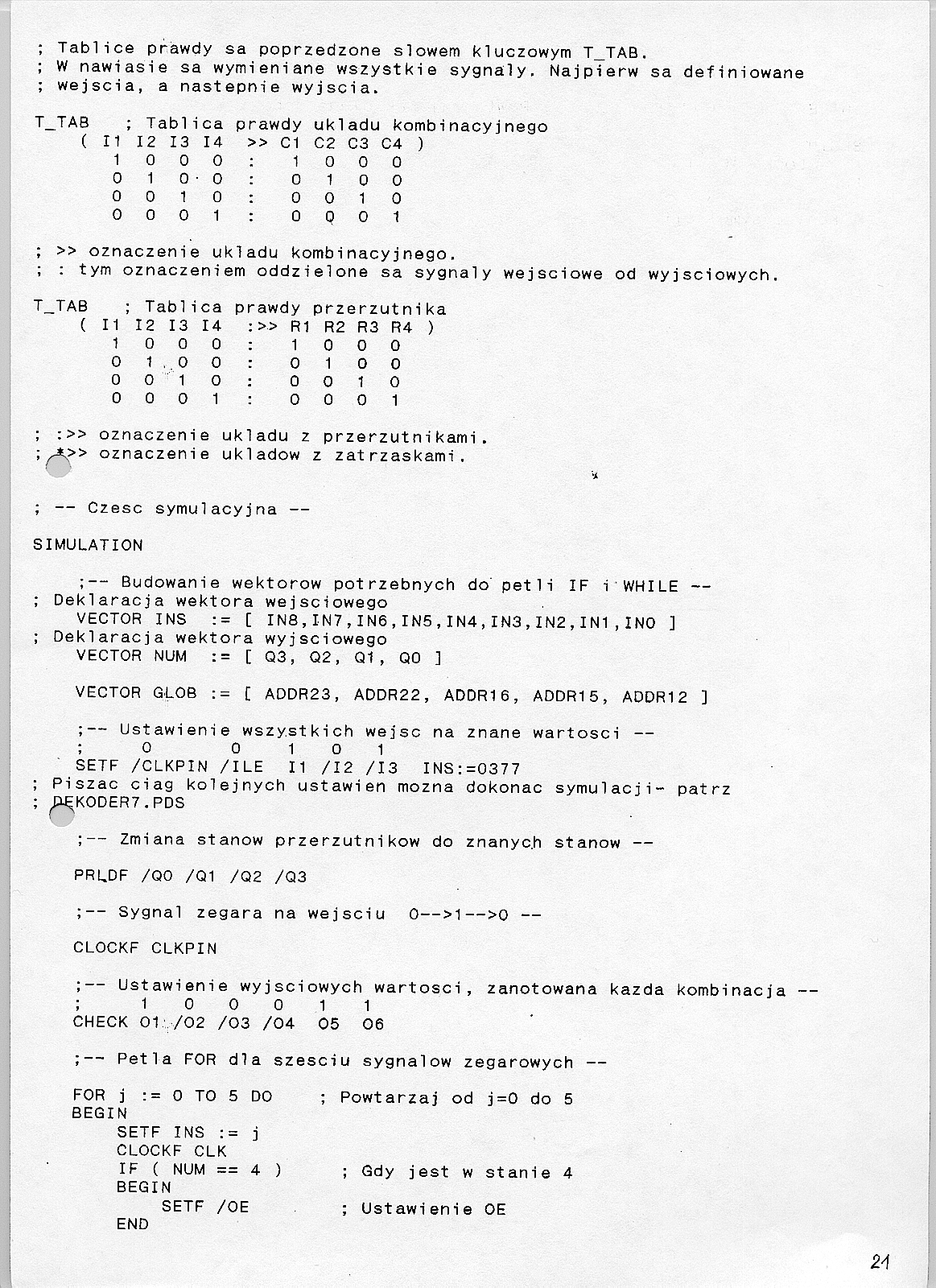

; Tablice prawdy sa poprzedzone słowem kluczowym T_TAB.

; W nawiasie sa wymieniane wszystkie sygnały. Najpierw sa definiowane ; wejścia, a następnie wyjścia.

T_TA8 ; Tablica prawdy układu kombinacyjnego

|

( 11 |

12 |

13 |

14 |

» C1 |

C2 |

C3 |

C4 |

|

1 |

0 |

0 |

0 |

: 1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

: 0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

0 |

: 0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

: 0 |

0 |

0 |

1 |

; >> oznaczenie układu kombinacyjnego,

; : tym oznaczeniem oddzielone sa sygnały wejściowe od wyjściowych.

T_TAB ; Tablica prawdy przerzutnika

|

( U |

12 |

13 |

14 |

» R1 |

R2 |

R3 |

R4 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

. 0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

" 1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

; :>> oznaczenie układu z przerzutnikami. ; ^A>> oznaczenie układów z zatrzaskami.

; — Czesc symulacyjna —

SIMULATION

;— Budowanie wektorów potrzebnych do' pętli IF i WHILE —

; Deklaracja wektora wejściowego

VECTOR INS := [ IN8,IN7,IN6,IN5,IN4,IN3,IN2,IN1,INO ]

; Deklaracja wektora wyjściowego

VECTOR NUM := [ Q3, Q2, Q1, Q0 ]

VECTOR GLOB := [ ADDR23, ADDR22, ADDR16, ADDR15, ADDR12 ]

;— Ustawienie wszystkich wejsc na znane wartości —

; 0 0 10 1 SETF /CLKPIN /ILE 11 /I2 /I3 INS:=0377

; Pisząc ciąg kolejnych ustawień można dokonać symulacji- patrz ; ^JiąKODERT.PDS

;— Zmiana stanów przerzutni kow do znanyc.h stanów —

PRLDF /Q0 /Q1 /Q2 /Q3

Sygnał zegara na wejściu 0—>1—>0 — CLOCKF CLKPIN

kombinacja —

;— Ustawienie wyjściowych wartości, zanotowana każda ; 10 0 0 1 1

CHECK 01/02 /03 /04 05 06

Pętla FOR dla szesciu sygnałów zegarowych —

FOR j := 0 TO 5 DO ; Powtarzaj od j=0 do 5 BEGIN

SETF INS := j CLOCKF CLK

IF ( NUM == 4 ) ; Gdy jest w stanie 4

BEGIN

SETF /0E ; Ustawienie OE

END

24

Wyszukiwarka

Podobne podstrony:

11363 skanuj0027 (63) Typ H2a (tablica XLI) Są to okazy podobne do poprzednich, mają Jednak ostrze u

Słowo kluczowe „static" 3 Poprzedzenie metody lub pola danej klasy słowem kluczowym static wska

Image061 w katalogach firmowych. Tablice prawdy bramek rzeczywistych operują bądź abstrakcyjnymi sta

Image344 Tablica prawdy en koderów zwykłych Tablica

Image350 Tablica prawdy enkodera scalonego 148 Tablica

MG 77 Sterowanie wyświetlaczem 7-segmentowym - tablica• Tablica prawdy .i 4 .o 7 • typa i f r .

rozklad poissona (2) Tablico Rozkład Polssona W tablicy podane są wartości prawdopodobieństwa / (.V«

173 4 340 przedstawiono na rys. 9. Sb. Do zakodowania tablicy konieczne są trzy sygnały, hipersześci

METALE CIĘŻKIE Metale ciężkie są to pierwiastki, które leżą od 3 do 18 grupy na tablicy Mendelejewa.

zadania UTC X ZESTAW EGZAMINACYJNY 28/2/13/A 1. Masz tablicę prawdy pewnej

cw1part1 Z RÓD TO SAM! 1, W tablicy 1A są podane możliwości produkcyjne pewnego przedsiębiorstwa, a)

więcej podobnych podstron