p1030021

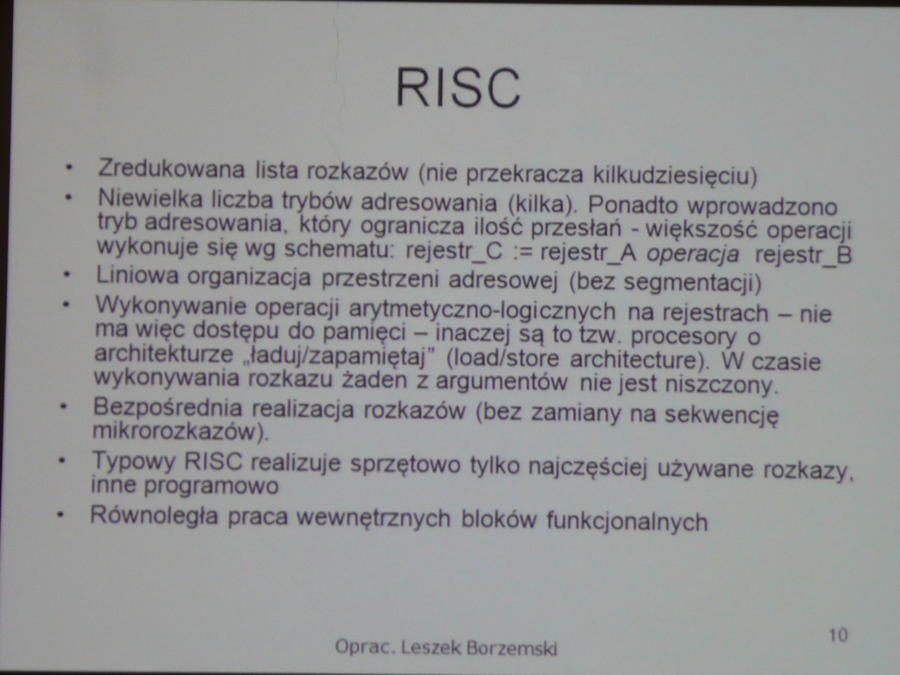

RISC

• Zredukowana lista rozkazów (nie przekracza kilkudziesięciu)

• Niewielka liczba trybów adresowania (kilka). Ponadto wprowadzono tryb adresowania, który ogranicza ilość przesłań - większość operacji wykonuje się wg schematu: rejestr_C := rejestr_A operacja rejestr_B

• Liniowa organizacja przestrzeni adresowej (bez segmentacji)

• Wykonywanie operacji arytmetyczno-logicznych na rejestrach - nie ma więc dostępu do pamięci - inaczej są to tzw. procesory o architekturze „ładuj/zapamiętaj" (load/store architecture). W czasie wykonywania rozkazu żaden z argumentów nie jest niszczony.

• Bezpośrednia realizacja rozkazów (bez zamiany na sekwencję mikrorozkazów)

• Typowy RISC realizuje sprzętowo tylko najczęściej używane rozkazy, inne programowo

• Równoległa praca wewnętrznych bloków funkcjonalnych

Oprać. Leszek Borzemsld

10

Wyszukiwarka

Podobne podstrony:

Różnice między technologią RISC a CISC. a) Zredukowana liczba rozkazów do niezbędn

Image195 /maksymalna częstotliwość impulsów wejściowych nie przekraczała wartości I katalogowej. fma

Image21 (3) *TABLICA ROZDZIELCZA Obrotomierz Nie przekraczać strefy zaznaczonej na czerwono. W okres

Image22 (3) *TABLICA ROZDZIELCZA Obrotomierz Nie przekraczać strety zaznaczo nej na czerwono W okres

Zdjęcie267 U Znieczulenie nadoponowe ^ w otwór krzyżowo-lędźwiowy - lidokaina • 2 -3 mg/kg, nie prze

Zdj?cie054 (2) Badanie przedmiotowe znaczno wychudzenie BMI<1B,5, masa dała nie przekracza 40kg i

zx instrukcja33 Tablica rozdzielcza * Obrotomierz Nie przekraczać strefy zaznaczonej na czerwono. Li

więcej podobnych podstron