27814 Zdjęcia 0030 (4)

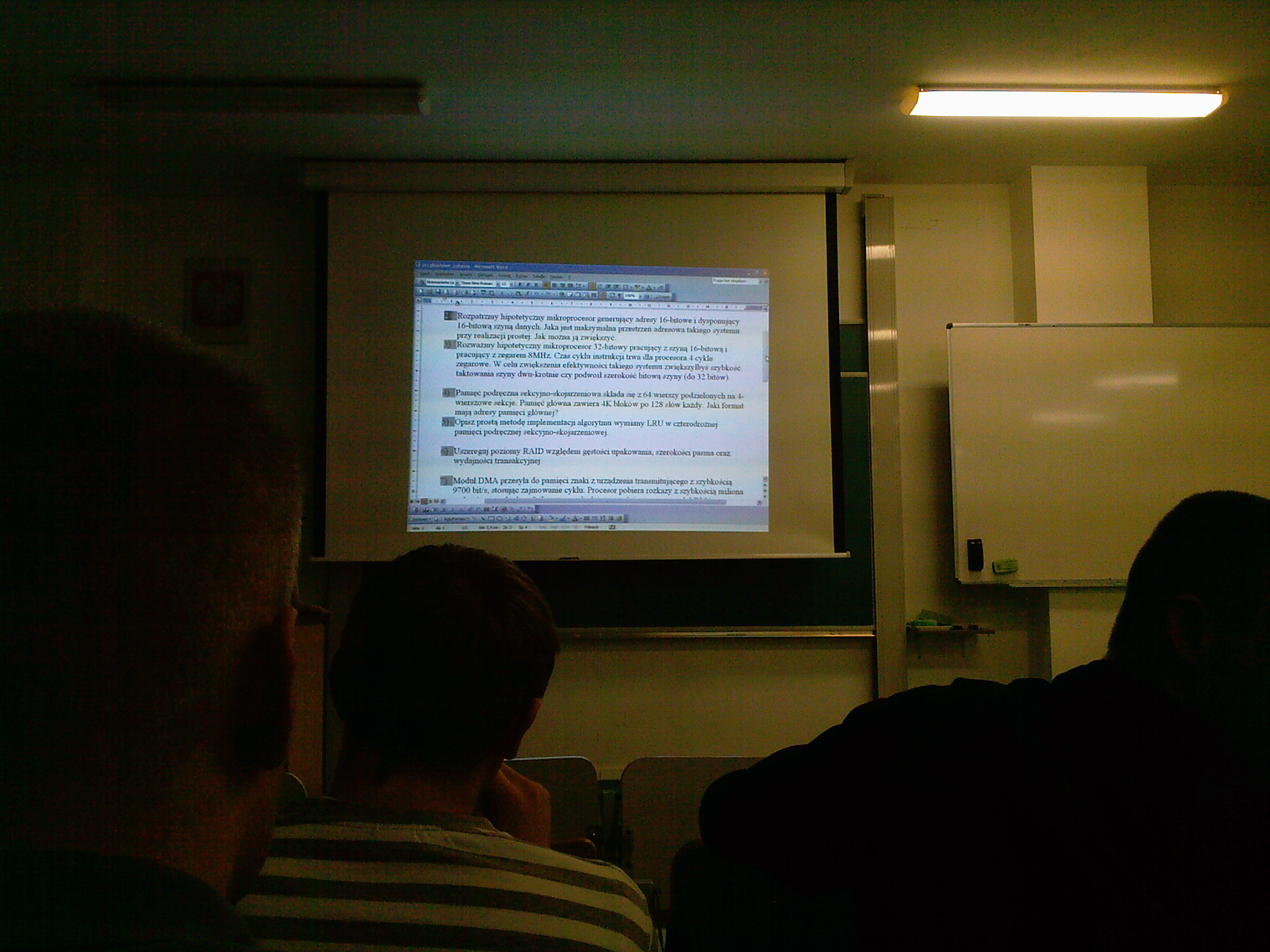

BBKozpjiratiN mporttyczny mikroprocesor generujący adresy 16-bitowe i dysponujący 16-łntową szyną danych Jola je»1 maksymalna prawtroń afawowi takiego systemu |>ray realizacji pudlej Jak nwnu ją zwiększyć

» :R«v\\ .i/niy hipotetyczny mikroproccsoi 32-bitowy piacujicy 7. szyną !6*hitową 1 pracujący /. zrjcuem 8MHz. Czas cyklu nurt mi ej 1 trwa dla procesora J cy kle zrjaiowe W celu zwiększenia efektywności takiego systemu zwiększyłby* szybko* taktowania szyny dwu*krotnie czy podwoił szrroko* intową szyny (do 32 łutów)

dPanuęc |>odręczn.i sekcyjno-skojarzcmowa składa «ę z 6-1 wieńczy podzielony eh na 1-wicrrzowc sekcje Pamięć główna zawiera -łK. bloków po 128 słów Lady Jaki formuł mają adresy pamięci głównej?

£}JOpbz prostą metodę implementacji algorytmu wymiany LRU w czictodroaicj pamięci podręcznej sckcyjno-skojarzciuowcj

^Uszereguj poziomy RAID względem gęstości upakowania, szerokości pasma oraz wydajności transakcyjnej

"} J.Modul DMA przesyła do pamięci znaki z. mzndzcru.1 tran/notującego z szybkością 9700 biL s. stosując zajmowanie cyklu Procesor pobiera rozkazy z szybkością miliona

Wyszukiwarka

Podobne podstrony:

Zdjęcia 0031 ozpotrany hipotetyczny mikroprocesor generujący adresy 16-bit owe i dysponująca 16-bito

Zdjęcie 0030 - l o-4^ _r jcA

Zdj?cia 0030 W zależność5 od stopnia uszkodzenia siatkówki może z ftoGó0¥M(tzciMt o rożnym stopniu z

11536 Zdjęcie 0030 Normalizacja t» itiiwikitowt noitny itutyi •

Zdjęcia 0030 (3) " ij ( a N «a (cW: ‘K łi4 V j • VAv f C^(A ^ V» >W t$v, <Ut

Zdjęcie 0030 Normalizacja t» itiiwikitowt noitny itutyi •

11536 Zdjęcie 0030 Normalizacja t» itiiwikitowt noitny itutyi •

Zdj?cia 0030 (2) Konwersja Konwersją zdania kategorycznego nazywamy zdanie, które powstaje z tego zd

Zdjecia 0030 nową i «usmtfCtoK •» trzonu W prm** v p pr/rpony podp«K</V"<**‘o*H e Vkomor

Zdjecie 0030 Cmwęm AZMt <AAxryl fpdadc eaam • lo»fj AGTC i pod aśakaacm 15 MP* wyłujrzyotupęc fóm

Zdjęcia 0030�0 Jk fM&UA 2 wchłaniania zwrotnego histaminy 3

Zdjęcia 0030 Nazwisko, imię:. 3. Ugięcie końca wspornika wynosi: A. 3 B I C.

więcej podobnych podstron