Zdjęcia 0031

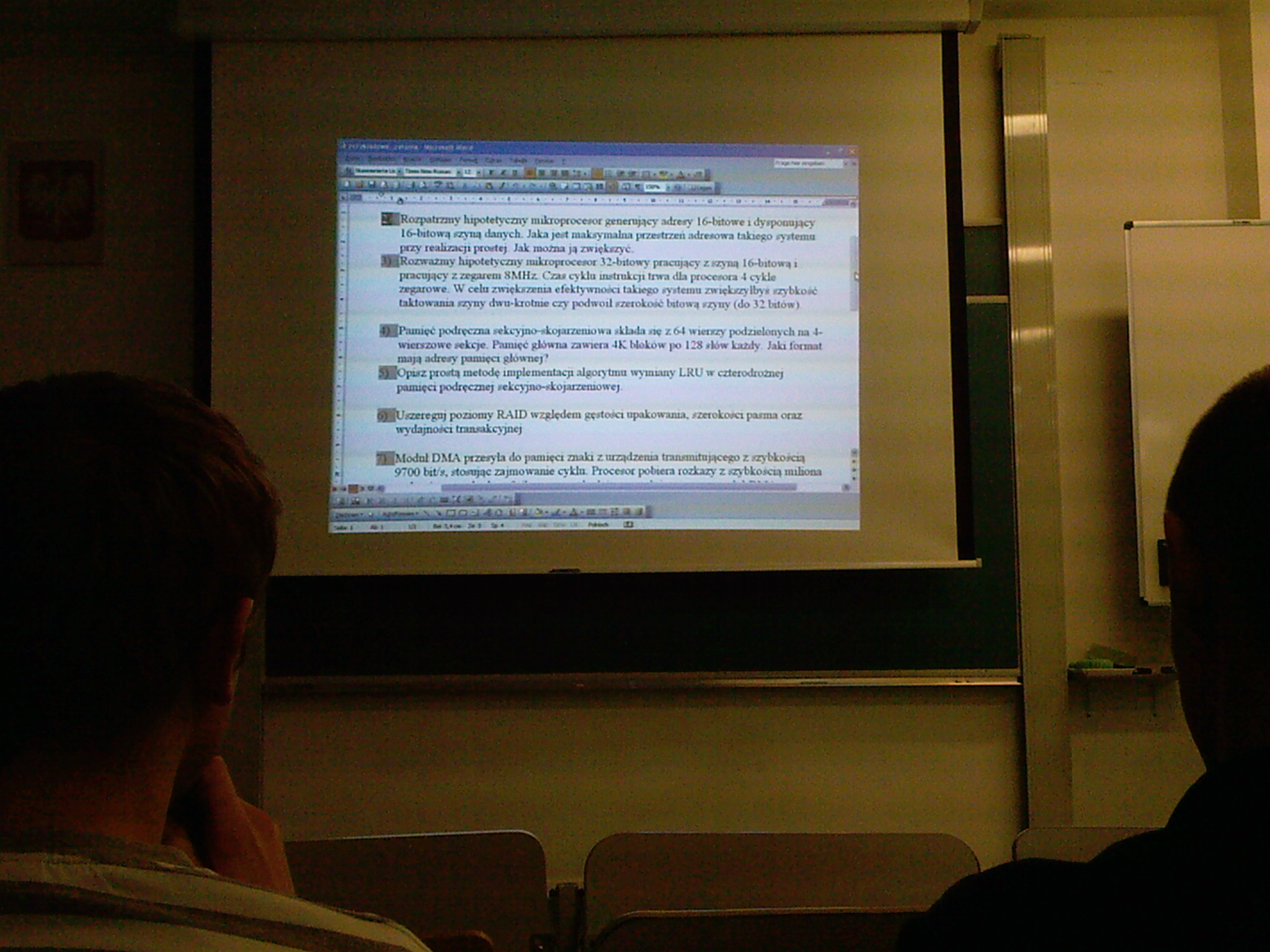

ozpotrany hipotetyczny mikroprocesor generujący adresy 16-bit owe i dysponująca 16-bitową szyną danych Jaka jest maksymalna |»r/rytr/ni adresowa takiego systemu przy rvaiuaqi prostej Jak rooJna ją zwiększyć

3 » |Rozwaziuy hipotety czny mikroprocesor 32-bjtowy pracujący z szyną l6*lntową i pracujący z zegarem HM Hz Czaj cyklu mstiukcji Inra *Ua procesora l cykle zrgaiowe W celu zwiększenia efektywności takiego systemu zw iębzy lin * .--rtbkosc taktów .mu czyny dw u-kiotmc czy podwoił s/rtokosc lutową szyny (do 32 bitów)

HP.iiuicc podręczna sekcyjno-skujaizriinm.i ALida nę z64 wierszy pod/jciomch na 1-wicuzowc sekcje Pamięć główna zawiera 4k Idokow po 128 slow Ludy Jaki format mają adresy |Kimięci główncj ’

■Kw prostą metodę implementacji algoty tiuu wymiany LRU w cztcrodruzncj pomięci jiodręcznej sekcyjno-sko jarzeniowej

MlUszcicgni poziomy RAID względem gęstości upakowania. /zetokojci pasma oraz wydajności tnuuakcyyncj fodnl DMA przesyt* do pamięci znaki z uizadzenu transmitującego z szybkością 700 Ut'J. stosując zajmowanie cy klu Procesor pobiera tozkazy z szybkoscią inibc

Wyszukiwarka

Podobne podstrony:

27814 Zdjęcia 0030 (4) BBKozpjiratiN mporttyczny mikroprocesor generujący adresy 16-bitowe i dysponu

Zdjęcie078 (2) w wieku produkcyjnym (w Polsce jest to wiek 16-60 lat dla kobiet i 16-65 lat dla mężc

Zdj?cia 0031 (2) Przykłady Konwersją zdania A azdy ’ mętczy znajest dobry 77/ mętem jesl zdanie Każd

Zdj?cie 0045 xs. Ergonomiczne aspekty reklamy w transporcie. 16. Ergonomiczna list

103. Jak zrobić dobre zdjęcie : warsztaty fotograficzne w bibliotece szkolnej Gimn

Zdjęcie 7. i 8. Zajęcia z przedsiębiorczości w Białostockim Parku Naukowo-Technologicznym 16

Technika mikroprocesorowa Mikrokontroler AT90S8515 posiada 16-bitowa szynę adresowa i może dodatkowo

Zdjęcie 0031 Normalizacja Ogólna zasada stosowania wymagań norm • Wymagania odnoszące się do takich

Zdjecie105 Nta)riap

Zdjęcia 0031 S. Wskazać właściwe położenie osi obojętnej dla przekroju w kształcie prostokąta obciąż

Zdjęcie163 Zawartość kwasów tłuszczowych — f CI I.O mirystynowy W 3,41 C 16:0

Zdjecia 0031 sfcOm* tv*r> uda Q^ł «?» Sfrilfti l***CwyrT> * rutiff in xr*uUujcmy. MH»^ H«^-

więcej podobnych podstron