222 223

222

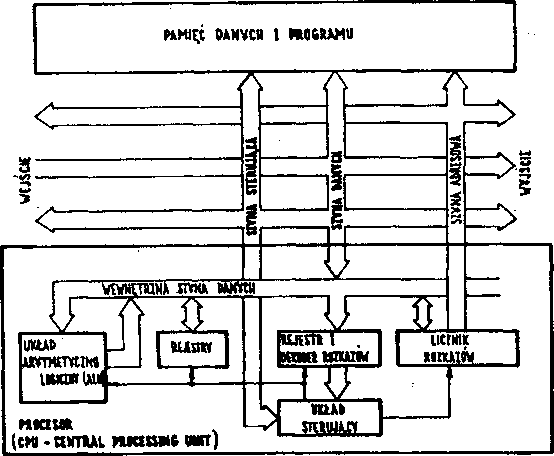

Rys• 6.2. Schemat blokowy komputera

słowa o długości równaj liczbie bitów rozkazu przy czym kolejne rozkazy programu umieszczone są pod kolejnymi adresami.

Przypuśćmy, że procesor maszyny (CPU - Central Processing Unit) prze- . syła do pamięci, poprzez szynę adresową, adres kolejnego rozkazu.. W odpowiedzi pamięć przesyła do procesora, poprzez szynę danych,wskazany przez adres rozkaz. Rozkaz tren jest w procesorze dekodowany i wykonywany. Zakończenie wykonywania rozkazu powoduje automatyczne zwiększenie zawartości licznika rozkazów o Jedność i ta nowa Jego zawartość przesyłana jest do pamięci jako adres następnego rozkazu. Proces ten Jest kontynuowany aż do wykonania wszystkich rozkazów danego programu zawartego w pamięci. Licznik rozkazów spełnia więc ważną rolę generatora adresów kolejnych rozkazów wykonywanych przez procesor.

Po każdym wykonaniu rozkazu zawartość licznika rozkazów zwiększa się o jedność co powoduje, że rozkazy normalnie pobierane są spod kolejnych, rosnących adresów pamięci. Kolejność ta może być jednak zmieniana przez tzw. rozkazy skoku, które oddziaływują na zawartość licznika rozkazów.Wykonanie przez procesor rozkazu skoku powoduje wpisanie do licznika rozkazów zawartości określonej przez ten rozkaz. Tym samym adres następnego pobranego przez procesor rozkazu nie będzie następny w kolejności, a dowolny, wyznaczony przez rozkaz skoku.

W czasie wykonywania programu tworzą się wyniki pośrednie, które należy okresowo przechowywać. Wykorzystywany Jest do tego celu zespół rejestrów pomocniczych « obrębie procesora oraz pamięć zewnętrzna (pamięć danych na rya. 6.2). Tale więc w pamięci, na zewnątrz procesora mogą się znajdować obok siebie rozkazy i dane. Zarówno dana jak i rozkazy są liczbami dwójkowymi o ustalonej i identycznej liczbie bitów 1 są nlerozróż-nlalne, tzn. pobierając z pamięci jakąś liczbę nie można stwierdzić, czy jest to rozkaz czy dana. Pomimo tej nierozróżnialaości, poprawne napisanie programu z ewentualnym utyciem rśzkazów skoku zapobiega -pobieraniu przez procesor danych 1 traktowaniu Ich jako rozkazów (jeżeli na ; skutek błędu w programie dana zostanie przesłana do procesora, który oczekuje właśnie na rozkaz, to potraktuje ją jako rozkaż z zupełnie nieoczekiwanym rezultatem).

Operacje arytmetyczne i logiczne wykonywane są w układzie arytmetyczno--loglcznym (AUT), zaś za synchronizacje wykonywania tych operacji oraz przesyłać informacji wewnątrz procesora i pomiędzy procesorem a pamięcią odpowiedzialny jest układ sterujący. Oprócz przesyłania liczb pomiędzy procesorem i pamięcią mogą one być pobierane z zewnątrz komputera lub wysyłane na zewnątrz poprzez urządzenia wejścia/wyjścla.

Omówiliśmy tu krótko zasadę działania maszyny cyfrowej. V dalszym ciągu zajmiemy się opisem budowy i działania wybranego jiP 1 yiK oraz wprowadzimy dodatkowo szereg nowych i niezbędnych wiadomości ogólnych. Nowe pojęcia i terminy będziemy wyjaśniali na bieżąco w miarę ich pojawiania się.

6.3. BUDOWA I DZIA ZANIE ^P INTEL 6080*>

Jednym z najczęściej stosowanych mikroprocesorów jest 8080 firmy Intel i bazujący na nim UCS 80. Poza Intelem produkuje go na licencji szereg znanych firm, między innymi Texas Instruments, National Semiconductor i Siemens.

Układ 8080 jest kompletnym procesorem 8-bitowym (tzn. rozkazy i dane są liczbami 8-bitowymi), zbudowanym na jednej płytce w wielkoscalonej technologii NUOS. Zawiera on binarny układ arytmetyczno-logiczny AUT, rejestr A (akumulator) 1 sześć rejestrów danych B,C,D,E,H,L oraz pięć test owalnych wskaźników. Układ korekcji dziesiętnej umożliwia łatwe wykonywanie operacji na liczbach BCD. Z kolei wskaźnik stosu ułatwia organizowanie stosu w zewnętrznej pamięci RAM, gdzie może być przechowywana zawartość rejestrów i wskaźników wg zasady LIPO. Do przesyłania danych pomiędzy wymienionymi, głównymi blokami procesora służy 8-bltowa wewnętrzna szyna danych. Przesyłanie danych pomiędzy |iF a układami zewnętrznymi odbywa się za pośrednictwem 8-bitowej, dwukierunkowej, trójstanowej szyny danych, oddzielonej od szyny wewnętrznej odpowiednim buforem. Odrębna 16--bitowa szyna adresowa z buforem trójstanowym upraszcza organizację otoczenia procesora. Taka liczba bitów adresowych pozwala na bezpośrednie adresowanie pamięci zewnętrznej ROM lub RAM o pojemności do 65536 (64 k)

Podane tu schematy i parametry opierają się na prospektach i katalogach firny INTEL.

Wyszukiwarka

Podobne podstrony:

222 223 222 O Rys. 6.2. Schemat blokowy komputera słowa o długości równej liczbie bitów rozkazu przy

Image147 U(t) Rys. Schemat blokowy układu opisanego równaniem stanu i równaniem wyjścia

Image148 Rys. Schemat blokowy układu gdy wektory U(t)=u(t) i Y(t)=y(t) są jednowymiarowe

Image156 Rys. Schemat blokowy układu gdy sygnały sterujące oddziały wuj ą także na sygnały wyjściowe

zadanych Rys. 8. Otrzymana charakterystyka wskazań magnetometru w kierunku osi X i Y Rys. 6. Schemat

zadanych Rys. 8. Otrzymana charakterystyka wskazań magnetometru w kierunku osi X i Y Rys. 6. Schemat

zadanych Rys. 8. Otrzymana charakterystyka wskazań magnetometru w kierunku osi X i Y Rys. 6. Schemat

instrukcja7 Rys. 6: Schemat blokowy ufcfodu strojenia Ro Rg 2.3. Przód przystąpien

zadanych Rys. 8. Otrzymana charakterystyka wskazań magnetometru w kierunku osi X i Y Rys. 6. Schemat

zadanych Rys. 8. Otrzymana charakterystyka wskazań magnetometru w kierunku osi X i Y Rys. 6. Schemat

Ui i U2 przykładane napięcia o częstotliwościach odpowiednio równych Vi i V2 Rys. Schemat blokowy uk

więcej podobnych podstron