63552 skanuj0021 (99)

nych, to układy te spełniają funkcją demultiplekserów ośmiowejścio-wych.

Na rysunku 4.382 przedstawiono sposób wykorzystania dwóch dekoderów 42 do konwersji naturalnego 4-bitowego kodu dwójkowego na kod 1 z 16. Wejścia A, B i C obydwu dekoderów są połączone równolegle, a wejścia D poprzez inwerter. Z dekodera ’42 otrzymuje się (rys. 4.382b) wyjścia dziesiętne 0, 1,9, natomiast z dekodera ’42 z in-werterem — wyjścia 8, 9,15 i wyjścia 0, 1. Z tego wynika, że wyjścia 0, 1 i 8, 9 są dostępne z obydwu dekoderów.

Przez połączenie dwu dekoderów ’42 w sposób pokazany na rys. 4.383 otrzymuje się demultiplekser 16-wyjściowy.

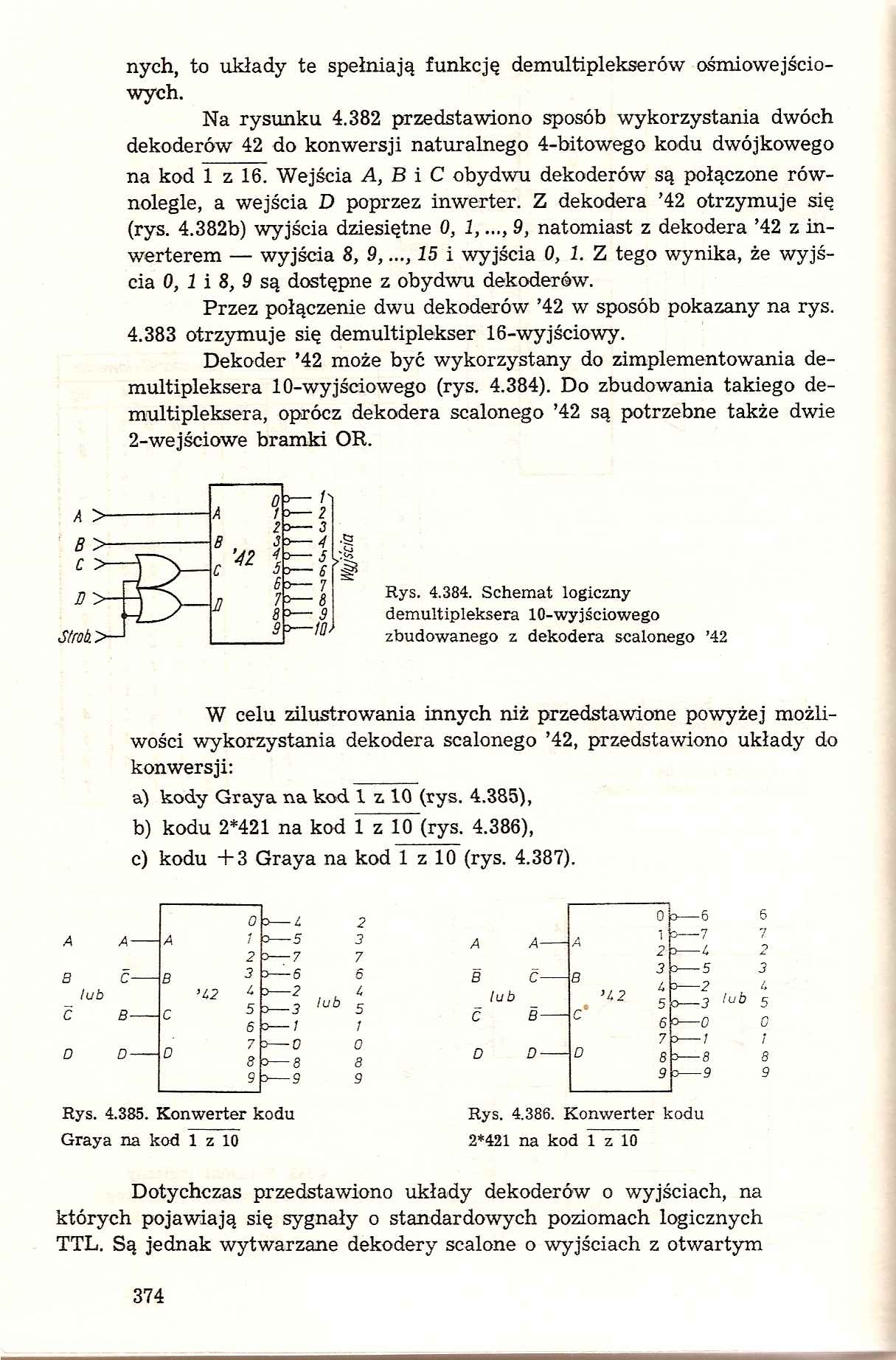

Dekoder ’42 może być wykorzystany do zimplementowania de-multipleksera 10-wyjściowego (rys. 4.384). Do zbudowania takiego de-multipleksera, oprócz dekodera scalonego ’42 są potrzebne także dwie 2-wejściowe bramki OR.

Rys. 4.384. Schemat logiczny demultipleksera 10-wyjściowego zbudowanego z dekodera scalonego ’42

W celu zilustrowania innych niż przedstawione powyżej możliwości wykorzystania dekodera scalonego ’42, przedstawiono układy do konwersji:

a) kody Graya na kod 1 z 10 (rys. 4.385),

b) kodu 2*421 na kod 1 z 10 (rys. 4.386),

c) kodu +3 Graya na kod 1 z 10 (rys. 4.387).

Rys. 4.385. Konwerter kodu Rys. 4.386. Konwerter kodu

Graya na kod 1 z 10 2*421 na kod 1 z 10

Dotychczas przedstawiono układy dekoderów o wyjściach, na których pojawiają się sygnały o standardowych poziomach logicznych TTL. Są jednak wytwarzane dekodery scalone o wyjściach z otwartym

374

Wyszukiwarka

Podobne podstrony:

skanuj0014 (232) nych, jakie powinny one spełniać, aby ładunki mogły być w nich przemieszczane pod z

68015 skanuj0014 18 CO TO JEST FILOZOFIA? w niemałej mierze od tego, jak na te piania odpowie. Nie t

generat nap sin008 8 Analogowe Elementy I Układy Elektroniki sprzężenia zwrotnego. Diody te spełniaj

64878 Scan Pic0060 odpowiednio I, i I2, to natężenia te spełniają zależność:A. §Afg &nbs

260 O TŁUMACZENIACH polskim, przecinek w liście w języku angielskim). Konwencje te spełniają funkcję

skanuj0011 (102) Zadanie 15. Które ze zjawisk elektrycznych może wystąpić w przedstawionym na rysunk

skanuj0109 (25) Kliny nastawcze. Służą one do ustalania położenia części maszynowych. Na rysunku 5.1

66524 skanuj0009 (116) Zadanie 8. Schemat funkcjonalny odbiornika telewizyjnego przedstawiono na rys

więcej podobnych podstron