CIMG5129

11. Podstawowe bramki logiczne

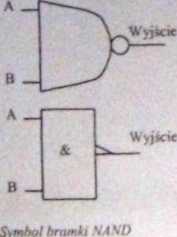

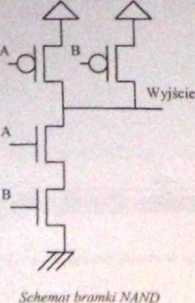

11.1. Bramka NAND

Tablica prawdy i schemat elektryczny dwu wejściowej bramki NAND są przedstawione na Rys. 45. Bramka NAND zbudowana jest z dwóch tranzystorów NMOS połączonych szeregowo i dwóch tranzystorów PMOS połączonych równolegle.

|

dwuwejściowa bramka NAND | |

|

A B |

Wyjście |

|

0 0 |

1 |

|

0 1 |

l |

|

t 0 |

1 |

|

i i |

0 |

fiys. 45. Tablica prawdy I schemat elektryczny bramki SAND

11.1.1. Projektowanie bramki NAND

Narysujmy bramkę NAND nanosząc po kolei warstwy jak w przypadku inwertera. według scbcwata elektrycznego przedstawionego na Rys. 45. Nie zapomnijmy o sprawdzaniu reguł projektowania DRO.

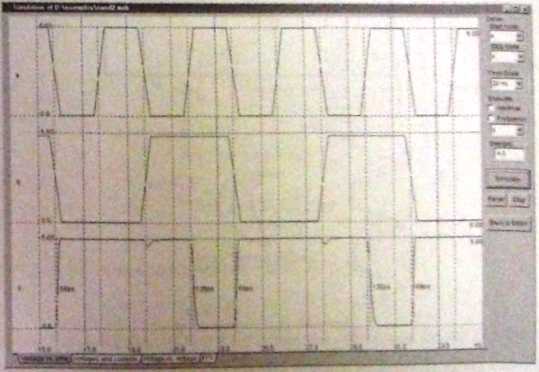

11.1.2. Symulacja bramki NAND

Symulację przeprowadzamy podobnie jak to było opisane w przypadku inwertera. Dołączamy vdD> masę VSS, sygnały wejścia i wyjścia. Przykład poprawnej symulacji jest pokazany na Rys 46.

Rys 46. Symulacja bramki SAMO

Wyszukiwarka

Podobne podstrony:

CIMG5130 52 Podstawy Mikroelektroniki 52 Podstawy Mikroelektroniki11.2. Bramka NOR Tablica prawdy i

50. Realizacja podstawowych zależności logicznych za pomoc li najprostszego układu elektrycznego Zap

Image106 4.1.4.2. Bramka podstawowa z serii malej mocy (L) Schemat elektryczny bramki I-NIE (NAND) z

skrypt171 Tablica 11.-.: Podstawowe właściwości czystego żelaza 13, 5, 37] Rodzaj

Elementy układów cyfrowych -podstawowe bramki logiczne W3: Technika cyfrowa XOR lub

Elementy układów cyfrowych -bramki wielowejściowe Przykład - trójwejściowa bramka OR tablica

DSC00040 (34) Fizyczną realizacją podstawowych operacji logicznych są układy nazywane bramkami Są to

Rys. 10. Jednoczesna realizacja funkcji logicznych NOR i NAND a) na bramkach prądowych b) z pokazani

DSC00904 (7) BLOK 4 BRAMKI LOGICZNE Podstawowe bramki OR i AND (oraz pochodne) mają dwa wejścia i je

Układy z elementów logicznych Bramki logiczne Elementami logicznymi (bramkami logicznymi) są urządze

uklady logiczne 2 Rys. 2 Bramka NAND zbudowana z dwóch tranzystorów. Wyjście A przechodzi

PODSTAWOWE UKŁADY LOGICZNEZZt i "‘■•♦i I? ^->•"1:11) I * ^J.w^łiSS^ *

25182 P3040870 1.11. Spoiny Podstawy prorfsfclo wanto konotmkcp motatowyoh Tablica 1.8. Elektrody za

CIMG5131 54 Podstawy Mikroelektroniki12. Kompilator układów logicznych W programie MicroMind możemy

więcej podobnych podstron