DSC1200493

" J10™" • podmoduły kontrolera

kontrolera , Sygna^ —

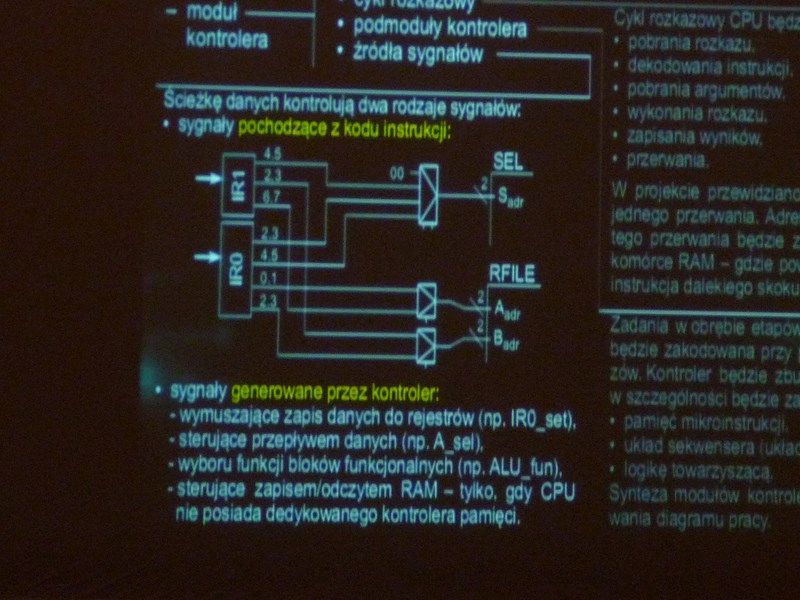

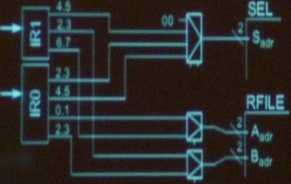

Soezkf danych kontrolun dwe raSje sygnałów:

• sygnały pochodzące 2 kodu instrukcji:

Cykl 'ozkazowy CPU oeoz

• pobrania rozkazu

• dekodowana instrukcji.

• pobrania argumentów.

• wykonania rozkazu.

• zapisania wyników.

• przerwania

W projekcie przewidziane jednego przerwania Adre tego przerwania oeazie z komorce RAM - gdzie pot mstrukqa dalekiego skoku

’eoe etapom oedzie zakodowana przy 1 zOw. Kontroler oedzie zbu w szczególności bedz1 za

• pamec mikrcmstrukcji

• ukiad seKwensera (ukiac

• logikę towarzysząca Synteza modurow kontroli wama diagramu pracy

sygnały generowane przez kontroler:

• wymuszające zapis danych do rejestrów mp. IRO.set),

• steruiace przepływem danych (np. A_seł).

• wyboru funkcji bloków funkcjonalnych (np. ALU Jun),

• steruiące zapisem/odczytem RAM - tylko, gdy CPU me posiada dedykowanego kontrolera pamięci.

Wyszukiwarka

Podobne podstrony:

Informatyka 1 Zestaw pytań kontrolnych z informatyki Bajg? danych 1. Podaj definicją tezy danych. K.

VII. Ewaluacja programu Współczesne rozumienie ewaluacji to nie tylko kontrola, ocena i zbieranie da

1) kontrola zgodności przetwarzania danych z przepisami o ochronie danych

DSC1200486 Założenia da kontrolera: • sygnały 1-bitowe: mg, m,. mg. •

Kontrolę poprawności przesyłania danych w sieciach Ethernet zapewnia protokół O HTTP ® TCP O IP O UD

Informatyka 1 Zestaw pytań kontrolnych z informatyki Bajg? danych 1. Podaj definicją tezy danych. K.

CAM00184 Kontrola dostępu w bazach danychGrzegorz Potaczała Gwałtowny rozwój technologii informatycz

skanuj0266 (3) 280 PHP i MySQL dla każdego ♦ DCL, język kontroli danych (ang. Data Control Language)

img5 (11) Podstawowe funkcje DBMS cd Zarządzanie bezpieczeństwem bazy danych: DBMS zapewnia kontrolę

skanuj0027 (178) Rozdział 2. ♦ Znaczniki, zmienne i typy danych 39 Tabela 2.2. F

SL374217 EKSPERYMENTY Eksperymenty umożliwiają zbieranie danych w warunkach kontrolowanych, co pomag

118,119 wtórne do zaburzeń mowy, na sytuację szkolną dziecka; danych, kióro umożliwiłyby kontrolę pr

118,119 wtórne do zaburzeń mowy, na sytuację szkolną dziecka: danych, kt umożliwiłyby kontrolę przeb

510-Konstrukcje murowe Komunikaty kontroli wprowadzanych danych:

więcej podobnych podstron