IMAG0644 (4)

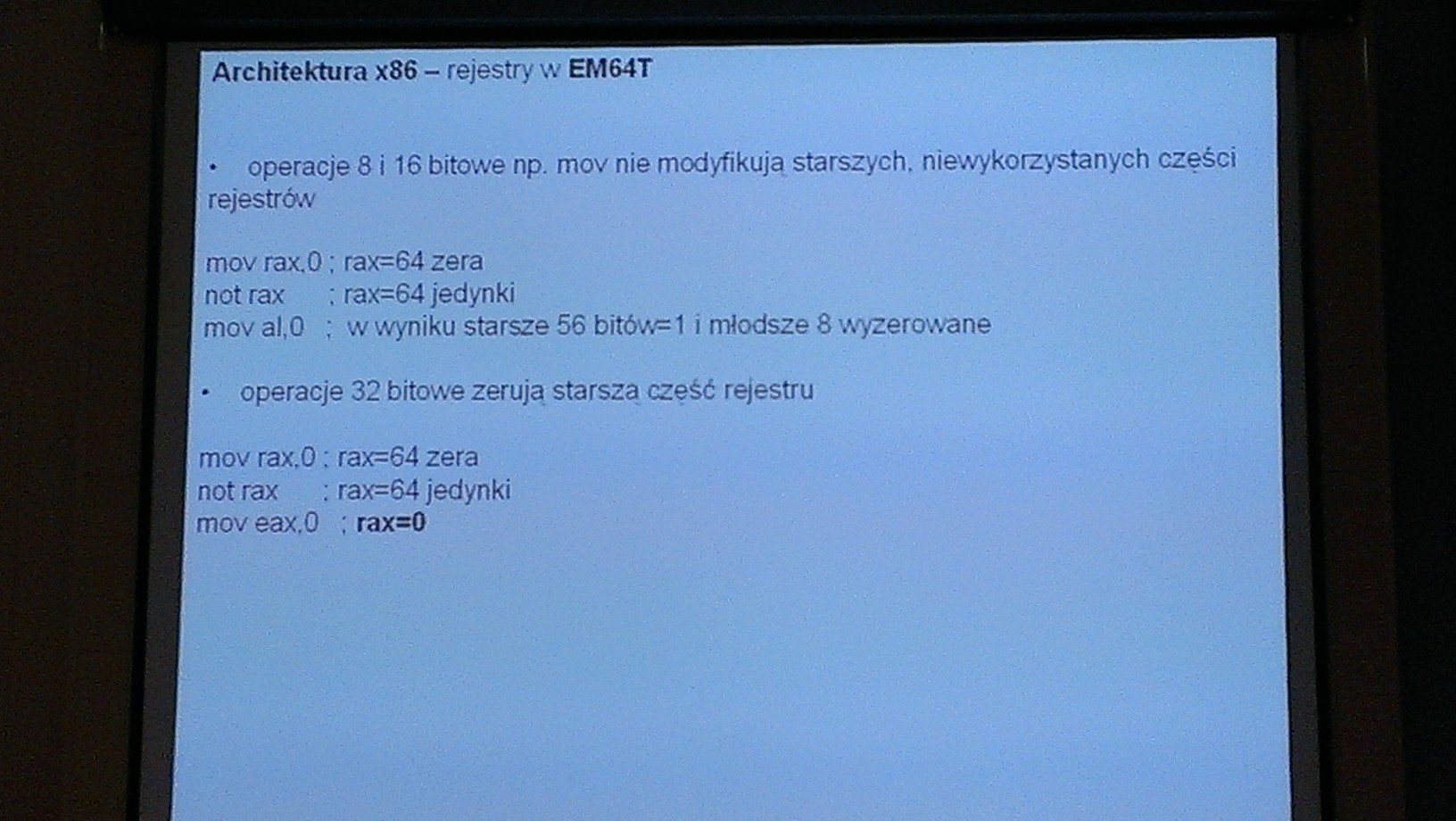

Architektura x86 - rejestry w EM64T * operacje 8 i 16 bitowe np. mov nie modyfikują starszych, niewykorzystanych części rejestrów

mov rax,0; rax=64 zera not rax ; rax=64 jedynki

mov al,0 ; w wyniku starsze 56 bitów= 1 i młodsze 8 wyzerowane

| operacje 32 bitowe zerują starszą część rejestru

mov rax,0: rax=64 zera not rax ; rax=64 jedynki mov eax,0 ; rax=0

Wyszukiwarka

Podobne podstrony:

IMAG0643 (5) Architektura x86 - rejestry w EM64T Rejestry ogólnego przeznaczenia (GPR - generał purp

IMAG0642 (4) Architektura x86 - rejestry 1A-32 O UM GPRO GPR1

IMAG0651 (4) Architektura x86 - tryby pracy procesora Chroniony - dla wielozadaniowych systemów oper

IMAG0645 (5) Architektura x86 Flagi 3130 29 28 27282* 2423 22 2120 1918 171*1514 13 1211 10 9 8 78*

IMAG0650 (5) Architektura x86 - tryby adresowania (wybrane) Bez dostępu do pamięci: •

IMAG0652 (4) 3 Architektura x86 - podsumowanie: technical elegance * market success I - maniakalne u

Slajd5 (105) Rodziny procesorów• Intel x86 (komputery PC): - 16 bitowe: 8086 88. 8

Architektura procesora (2) ALU- lista operacji zestaw rejestrów -

Projektowanie obiektów architektury krajobrazu część 2 MONOGRAFIA sztuka 3 [16] ogrodu / sztuka

IMAG0647 (5) Architektura x861 liczba cykli zegara na instrukcję (procesory klasyczne - bez potoków,

IMAG0655 (4) Stos * struktura danych w pamięci operacyjnej komputera zorganiz

Rejestr kasowyOsE] Operacje Edycja Punktowanie Widok Podgląd Procedury

67 (11) 134 Opis rozkazów jest rejestr DPTR, to 16-bitowy adres jest wysyłany przez porty PO (z DPL

04 02 Omawiamy 16-bitowe przetworniki analogowo-cyfrowe firmy Maxim, o małym poborze mocy,&nbs

04 10 INFORMACJA O PODZESPOŁACHMAX1167/MAX1168Wielokanałowe 16-bitowe przetworniki a/c Producent Ma

MIKROPROCESOROWE METODY STEROWANIA MIKROKONTROLERY RODZINY MCS5I -5- 1.2. Liczby 16-bitowe W

więcej podobnych podstron