IMAG0651 (4)

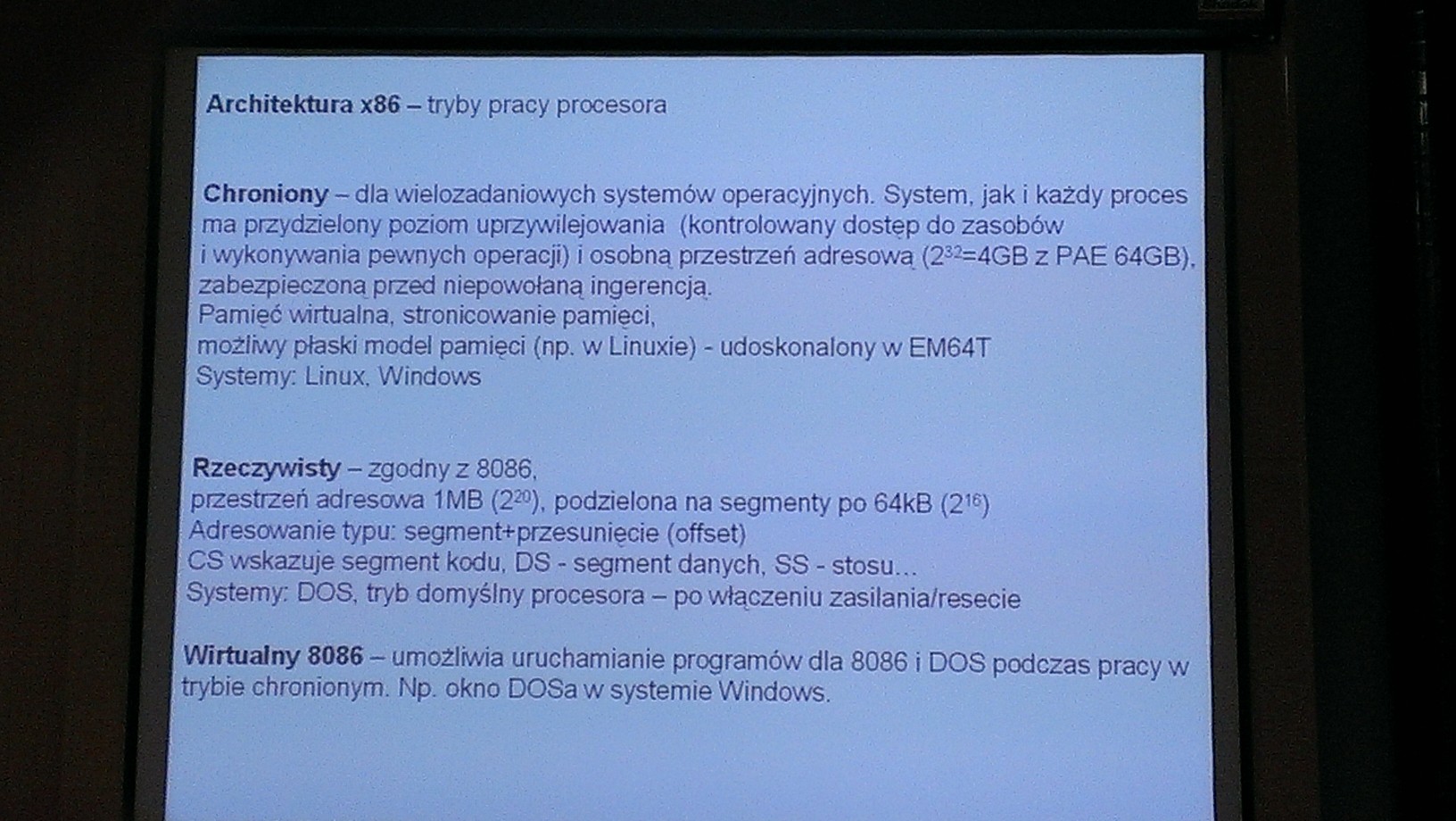

Architektura x86 - tryby pracy procesora

Chroniony - dla wielozadaniowych systemów operacyjnych. System, jak i każdy proces ma przydzielony poziom uprzywilejowania (kontrolowany dostęp do zasobów i wykonywania pewnych operacji) i osobną przestrzeń adresową (23J=4GB z PAE 64GB), zabezpieczoną przed niepowołaną ingerencją.

Pamięć wirtualna, stronicowanie pamięci,

możliwy piaski model pamięci (np. w Linuxie) | udoskonalony w EM64T

Systemy: Linux. Windows

Rzeczywisty - zgodny z 8086,

przestrzeń adresowa 1MB (220), podzielona na segmenty po 64kB (216)

Adresowanie typu: segment+przesunięcie (offset)

CS wskazuje segment kodu, DS - segment danych, SS - stosu...

Systemy: DOS, tryb domyślny procesora - po włączeniu zasilania/reseóie

Wirtualny 8086 - umożliwia uruchamianie programów dla 8086 i DOS podczas pracy w trybie chronionym. Np. okno DOSa w systemie Windows.

Wyszukiwarka

Podobne podstrony:

IMAG0650 (5) Architektura x86 - tryby adresowania (wybrane) Bez dostępu do pamięci: •

Tryby pracy procesora s Tryb chroniony: ■tryb wprowadzony w celu ochrony poszczególnych zadań

Tryby pracy procesora s Tryb rzeczywisty: ■ procesor przełącza sie w stan odwzorowujący zachowanie

Tryby pracy procesora S tryb wirtualny: ■stanowi kombinacje duch wcześniej omawianych trybów; ■

IMAG0642 (4) Architektura x86 - rejestry 1A-32 O UM GPRO GPR1

IMAG0643 (5) Architektura x86 - rejestry w EM64T Rejestry ogólnego przeznaczenia (GPR - generał purp

IMAG0644 (4) Architektura x86 - rejestry w EM64T * operacje 8 i 16 bitowe np. mov nie modyfikują sta

IMAG0645 (5) Architektura x86 Flagi 3130 29 28 27282* 2423 22 2120 1918 171*1514 13 1211 10 9 8 78*

IMAG0652 (4) 3 Architektura x86 - podsumowanie: technical elegance * market success I - maniakalne u

skanuj0009 (71) Zarówno dla projektowania systemu, jak i dla przygotowania jego struktury organizacy

IMAG0647 (5) Architektura x861 liczba cykli zegara na instrukcję (procesory klasyczne - bez potoków,

1003965I1012507635112?1858838 n I2N Rozdzia11 . U magnncj pracy na określonym stanowisku na wolnym

11. Werner A.W., Proces inwestycyjny dla architektów. Ofic. Wyd. Poli. Warszaw. 2000 Warunki zalicze

M Feld TBM558 558 12. Projektowanie procesu technologicznego dla części płaskich RYS. 12.19. Zasada

86536 skanuj0049 (2) Tabl. I. Schemat procesu konserwatorskiego dla zabytku architektury> Table I

więcej podobnych podstron