4544139287

Częstotliwość PCLK w wyniku podziału musi być mniejsza niż 4.5MHz. Gdy nie jest możliwe dobranie dokładnej wartości można wybrać częstotliwość jak najbliżej wymaganej. Częstotliwość PCLK jest dzielona przez CLKDIV+1 dla uniknięcia dzielenia przez zero. Sygnał zegarowy taktujący przetwornik można zablokować przy użyciu rejestru PDN. Po zerowaniu przetwornik jest wyłączony, zatem oprócz podania sygnału zegarowego należy go wyłączyć, ustawiając 1 na tym bicie. Bity SEL pozwalają wybrać kanały, w których będą wykonywane pomiary. Każdy z kanałów ma w polu SEL przypisany jeden bit odpowiedzialny za jego aktywację. Włączenie trybu BURST wymaga ustawienia bitów CLKS. W tym trybie pracy przetwornik wykonuje ciągłe pomiary w kanale. Pole CLKS określa kompromis pomiędzy prędkością pomiarów wyrażoną w liczbie okresów zegara CLK przetwornika a dokładnością pomiaru w trybie BURST. Pole START pozwala zatrzymać lub rozpocząć konwersję. Użytkownik może spowodować, aby pomiar zapoczątkowało zbocze sygnału na wejściu zewnętrznym CAPO.O lub CAP0.2 lub na wyjściu MAT0.1 MAT0.3, MAT1.0, MATl.l.

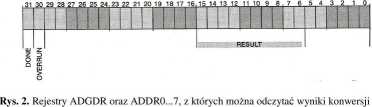

Przetwornik może mierzyć sygnał na wyprowadzeniach zewnętrznych, nawet gdy są skonfigurowane do pracy w trybie GPIO - co może obniżać dokładność przetwarzania. Wynik konwersji jest dostępny w polu RESULT rejestrów ADnDR0...7 oraz ADnGDR (w tym rejestrze wynik konwersji jest podawany wraz z numerem kanału). Po zakończeniu przetwarzania bit DONE zostaje ustawiony, co można wykorzystać do wygenerowania przerwania. Jeżeli po zakończeniu pomiaru wartość w polu RESULT nie zostanie odczytana, to zostaje ona utracona, gdyż przetwornik wykona kolejny pomiar i nadpisze ostatnio zmierzoną wartość w polu wynik. Fakt ten jest sygnalizowany ustawieniem bitu OYERRUN.

ADnDDR0...7 - ADC Dala Registers

Przetwornik ADC może pracować w trybie odpytywania oraz w trybie przerwań. Konfiguracja przetwornika do pracy w pierwszym wymienionym trybie jest przedstawiona poniżej.

18

Wyszukiwarka

Podobne podstrony:

2 Każda działalność gospodarcza musi być w mniejszym lub większym stopniu zaplanowana. Jest to jeden

img112 Podziałka t musi być taka sama w obu płaskownikach, również ze względów wytrzymałościowych.

img254 (3) winna być o 3/3 mniejsza niż średnica gwoździa. Po całkowitym wbiciu gwoździa należy zagi

25. Długość odcinków niwelacji i ciągów dowiązujących sieć musi być: A. Mniejsza

P5195941 11. Założycielami banku mogą być: f osoby fizyczne, z tym że liczba założycieli nie może by

§5 Minimalna liczba godzin kształcenia na KKZ prowadzonego w formie zaocznej nie może być mniejsza n

PN-EN 1996-1 -1+A1:2013-05/Ap1:2013-11 Liczba kotew łączących nie może być mniejsza niż 4 na 1 m2

zapas nie powinien byc mniejszy niż 50% jednorazowego zakupu zatwierdzonego przez Dyrektora

Rzut oszczepem0067 9.1. Rzutnia do rzutu oszczepem Długość rozl>cgu nie może przekraczać 36.5 m a

DSC04099 Zadanie Twardość na powierzchni hartowanego wału o średnicy 60 mm nie może być mniejsza niż

3. PODSTAWOWE URZĄDZENIA I APARATY STACJI warunkach probierczych nie powinna być mniejsza niż 0,05

Zadanie główne jest cykliczne lub okresowe (czas wykonania cyklu musi być krótszy niż zadeklarowany

Kadencja 4 lata z możliwością jednej reelekcji. frekwencja wyborcza musi być wyższa niż 50%, musi by

Wskaźnik zagęszczenia warstw zasypki, zdaniem autora, nie powinien być mniejszy niż 0,95. Wartość

zdjecie01�3 BALNEOLOGIA 1. Związki siarki w wodach leczniczych nie mogą być mniejs

BUDOWLE I ROBOTY ZIEMNE 1.3.3. Pochylenie skarpy nasypu lub wykopu może być mniejsze niż określone u

więcej podobnych podstron