LABORATORIUM ELEKTRONICZNE |

|||

BADANIE UKŁADÓW CMOS |

|||

ARMATYS TOMASZ BROŻEK RAFAŁ DROZDOWSKI JERZY DROZDOWSKI WOJCIECH FABIA MATEUSZ |

DATA: |

OCENA: |

PODPIS: |

WSTĘP:

Układy logiczne buduje się również przy użyciu tranzystorów unipolarnych. W układach scalonych stosuje się tranzystory z izolowaną bramką zwane MIS (MISFET), przy czym gdy izolatorem jest tlenek krzemu ( a tak jest najczęściej), stosowana jest nazwa MOS (MOSFET).

Istnieją trzy podstawowe rodzaje układów:

z tranzystorami z kanałem typu p (PMOS),

z tranzystorami z kanałem typu n (NMOS),

z tranzystorami komplementarnymi (CMOS).

Układy CMOS mają korzystne właściwości odróżniające je od realizowanych w technice PMOS i NMOS:

napięcia zasilające mogą zmieniać się w dużym zakresie (4 ÷ 16 V);

moc pobierana w stanach spoczynkowych jest znikomo mała, rzędu nanowatów i „liczy się” głównie moc tracona podczas przełączanie;

odporność na zakłócenia jest bardzo duża (podobnie jak układów DZTL);

układy CMOS mogą współpracować z układami TTL, DZTL i MOS.

Układy CMOS wytwarza się w małej, średniej i dużej skali scalenia.

Technologia wytwarzania układów typu CMOS polega na wykonaniu w tej samej kostce krzemowej dwóch tranzystorów unipolarnych MOS z kanałami wzbogaconymi o przeciwnym typie przewodnictwa „p” i „n”.

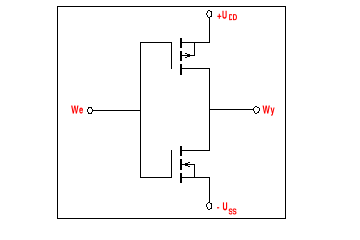

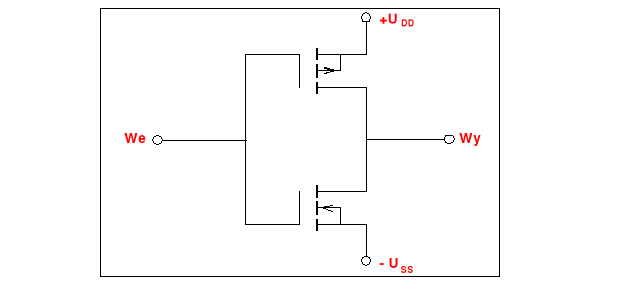

Łącząc szeregowo dwa tranzystory MOS ( elektrodami wspólnymi są obie bramki i oba dreny, a końcówki podłoży łączy się ze źródłami ) uzyskuje się inwerter CMOS:

TABELE I WYKRESY:

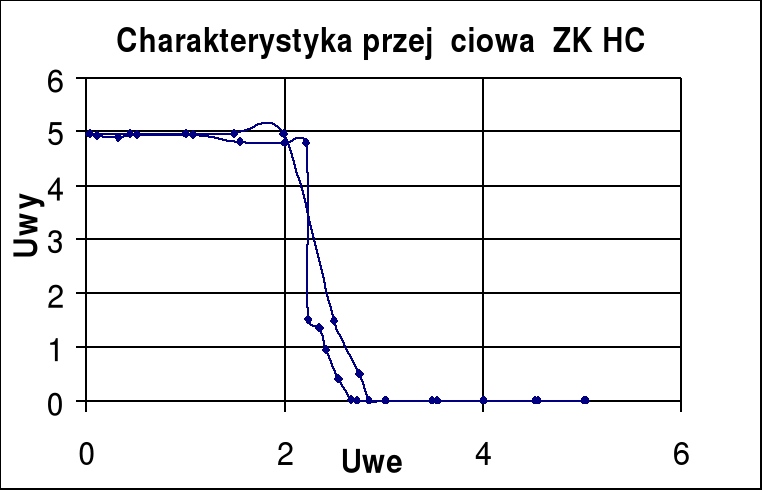

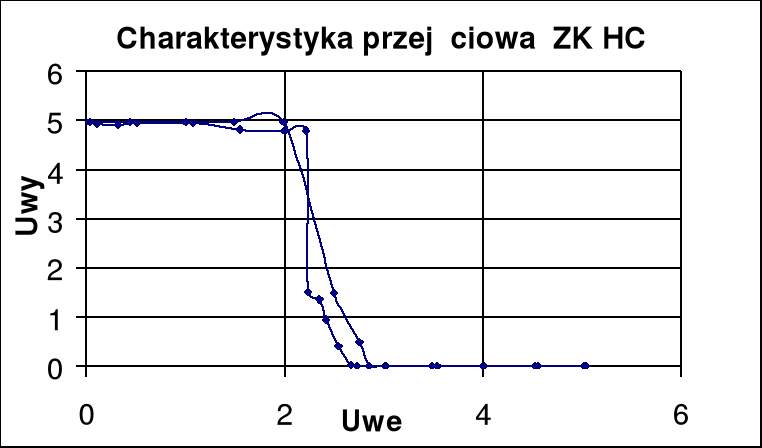

A) Inwerter ...

We [v] |

Wy [v] |

We[v] |

Wy [v] |

0.11 |

4.92 |

5.02 |

0.004 |

0.32 |

4.90 |

4.55 |

0.006 |

0.51 |

4.94 |

4.0 |

0.005 |

1.07 |

4.95 |

3.54 |

0.005 |

1.55 |

4.82 |

3.01 |

0.006 |

2.0 |

4.80 |

2.85 |

0.009 |

2.21 |

4.79 |

2.75 |

0.49 |

2.23 |

1.52 |

2.5 |

1.5 |

2.35 |

1.35 |

1.99 |

4.97 |

2.42 |

0.96 |

1.49 |

4.97 |

2.54 |

0.42 |

1.0 |

4.97 |

2.67 |

0.012 |

0.44 |

4.97 |

2.73 |

0.008 |

0.03 |

4.97 |

3.02 |

0.006 |

|

|

3.49 |

0.003 |

|

|

4.01 |

0.001 |

|

|

4.53 |

0.001 |

|

|

5.04 |

0.0 |

|

|

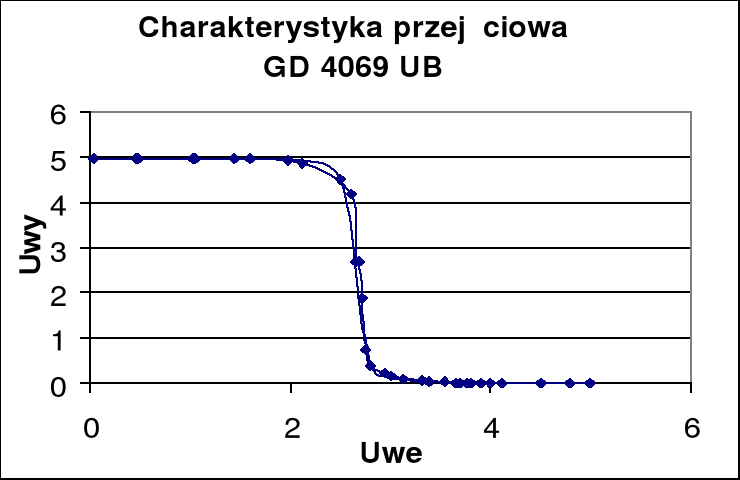

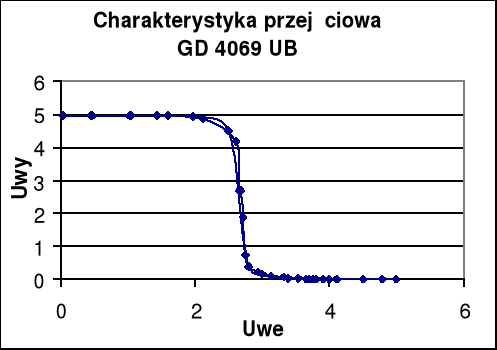

B) Badanie układu GD 4069 UB

We [v] |

Wy [v] |

We[v] |

Wy [v] |

0.03 |

4.97 |

4.99 |

0.0 |

0.46 |

4.97 |

4.79 |

0.0 |

1.02 |

4.97 |

4.5 |

0.0 |

1.43 |

4.97 |

4.0 |

0.0 |

2.11 |

4.87 |

3.81 |

0.001 |

2.60 |

4.20 |

3.7 |

0.006 |

2.66 |

2.69 |

3.54 |

0.018 |

2.68 |

2.69 |

3.38 |

0.042 |

2.71 |

1.87 |

3.13 |

0.112 |

2.74 |

0.84 |

2.80 |

0.4 |

2.80 |

0.4 |

2.50 |

4.52 |

2.94 |

0.22 |

1.97 |

4.92 |

3.0 |

0.17 |

1.59 |

4.97 |

3.12 |

0.11 |

1.04 |

4.97 |

3.31 |

0.05 |

0.47 |

4.97 |

3.65 |

0.008 |

|

|

3.76 |

0.002 |

|

|

3.8 |

0.001 |

|

|

3.9 |

0.0 |

|

|

4.1 |

0.0 |

|

|

4.5 |

0.0 |

|

|

3. WNIOSKI

Wejścia ,których stan jest obojętny (np.wejścia nie wykorzystanych bramek ) nie mogą nigdy pozostawać rozwarte w układach CMOS. Wejścia CMOS mogą być w miarę potrzeby zwierane bezpośrednio do masy lub do napięcia zasilania Udd . Ponieważ wejścia ustawiające SET i zerujące RESET w układach CMOS są zazwyczaj aktywne poziomem wysokim , powinny zostać zwarte do masy, podczas gdy np. na nie wykorzystane wejścia wielowejściowej bramki NAND powinno się podać stały poziom wysoki . Nie wolno pozostawić luzem nie wykorzystanych fragmentów układów , znajdujących się w jednej strukturze scalonej CMOS, co jest dopuszczalne w innych rodzinach układów. Nie wykorzystana bramka z rozwartym wejściem zacznie pobierać z zasilania spory prąd , płynący przez dwa jednocześnie przewodzące tranzystory, a na jej wyjściu ustali się napięcie o wartości połowy napięcia zasilania.

Wyszukiwarka

Podobne podstrony:

cmos, Bramki CMOS, Laboratorium Miernictwa Elektrycznego

06, Politechnika Lubelska, Studia, semestr 5, Sem V, Sprawozdania, sprawozdania, Sprawozdania, Labor

SPRAWOZDANIE Z LABORATORIUM ELEKTRONIKI

Laboratorium elektrotechnika Pomiary w obwodach trójfazowych

10, Politechnika Lubelska, Studia, semestr 5, Sem V, Sprawozdania, sprawozdania, Sprawozdania, Labor

Pomiar mocy, Laboratorium elektrotechniki

Laboratorium Elektroniki cw 2

Kopia (2) pchrezonans, Energetyka I stopień PŚk, sem1 Elektrotechnika, Laboratorium elektrotechnika,

Kopia pchrezonans, Energetyka I stopień PŚk, sem1 Elektrotechnika, Laboratorium elektrotechnika, rez

Badanie scalonego wzmacniacza prądu stałego v2, Politechnika Lubelska, Elektrotechnika inż, ROK 3, E

el.cw4 - Obwody trójfazowe2, Politechnika Lubelska, Studia, Studia, Elektrotechnika - laboratorium,

Sprawozdanie nr.1, Politechnika Lubelska, Studia, ELEKTROTECHNIKA LABORATORIUM, Laboratoria z elektr

Sprawozdanie nr 4, Politechnika Lubelska, Studia, ELEKTROTECHNIKA LABORATORIUM, Laboratoria z elektr

Sp 12, Politechnika Lubelska, Studia, Elektrotechnika, ELEKTROTECHNIKA LABORATORIUM, Laboratoria z e

Strona tytułowa sprawozdania LABORATORIUM ELEKTRONIKI

LABORATORIUM ELEKTROTECHNIKI

Badanie obwodów trójfazowych, 3fazyed3, LABORATORIUM ELEKTROTECHNIKI

więcej podobnych podstron