5460978347

Mikrokontrolery i mikrosystemy - Z' 14

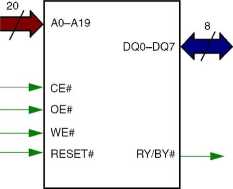

3. Schemat logiczny, znaczenie linii pamięci FLASH typu NOR o dostępie równoległym i pojemności np. 1 MB.

Znaczenie linii pamięci FLASH z interfejsem standardowym:

AO - An - (n+l)-bitowa magistrala adresowa (dla Am29F080B n = 19), wystawiany jest na niej n-bitowy adres komórki do odczytu lub zapisu,

DQ0 - DQ7 - 8-bitowa dwukierunkowa magistrala danych służąca do wprowadzania i wyprowadzania danych spod adresów ustawianych na magistrali adresowej,

CE# - (Chip Enable) wybór (aktywacja) układu poziomem niskim,

WE# - (Write Enable) niski poziom na tej linii powoduje zapis bajta pod wskazany adres (ale nie zapis bajta do pamięci FLASH - to wymaga uruchomienia procedury programowania),

OE# - (Output Enable) niski poziom na tej linii powoduje wystawienie na magistrali danych danej spod wskazanego adresu,

RESET# - sprzętowy reset wprowadzający pamięć w tryb odczytu, aktywny stanem niskim,

RY/BY# - wyjście służące do sprawdzania czy pamięć zakończyła wewnętrzne algorytmy kasowania/programowania, stan wysoki oznacza gotowość na przyjęcie kolejnych poleceń, stan niski informuje, że pamięć jest zajęta (niegotowa), bo jest w trakcie wykonywania wewnętrznych operacji.

Wyszukiwarka

Podobne podstrony:

Mikrokontrolery i mikrosystemy -Z18. Budowa i zasada działania linii portów równoległych. -

Mikrokontrolery i mikrosystemy -Z110. Schematyczna budowa układu czasowego w mk oraz jego zasada pra

53203 skanuj0023 (88) u Rys. 4.389. Schemat logiczny układu sterującego wskaźnikiem paskowym ty

Mikrokontrolery i mikrosystemy - Z" 18 Znaczenie linii: CS - wybór układu do transmisji (aktywn

Mikrokontrolery i mikrosystemy - Z1 15 4. Schemat blokowy układów SPLD standardu GAL16V8 oraz funkcj

Mikrokontrolery i mikrosystemy - Z 1910. Uogólniony schemat blokowy 7V-bitowych /("-kanałowych

Mikrokontrolery i mikrosystemy - Z1 2011. Schemat blokowy układu cyfrowego czujnika temperatury z in

Mikrokontrolery i mikrosystemy - Z1 12. Sterowanie oraz sposób odczytu i zapisu danych do wewnętrzne

Image064 I I ©Z-O . Jz Rys. 3.20. Schematy logiczne układów realizujących wieloargumentową funkcję A

Image070 Konwersja Schematy logiczne JK 3K dwójkę liczącą JK —-D dwójkę liczącą ■JK T —t J

Image125 Na rysunku 4.68 przedstawiono schemat logiczny czterobitowego rejestru przesuwającego, zbud

Image126 w prawo, jeśli zaś X = 0, wówczas może być przesuwana w lewo. Rejestr, którego schemat logi

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

więcej podobnych podstron