Image070

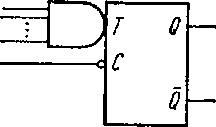

Konwersja Schematy logiczne

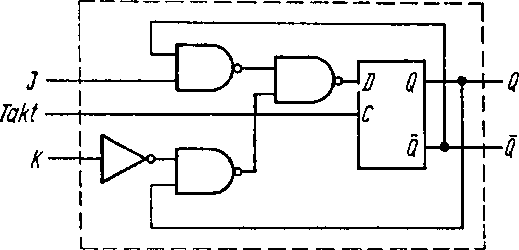

JK

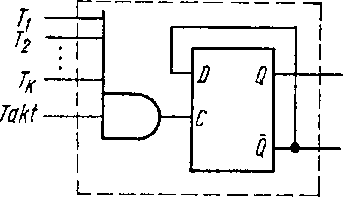

3K

dwójkę

liczącą

JK —-D

dwójkę

liczącą

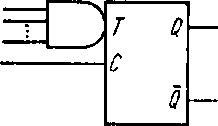

■JK

T —t J Q

Takt-

Takt

C

K GY-

n

J O

c

K Q

Takt-

|

J |

Q | |

|

c | ||

|

K |

8 |

|

/- |

J Q |

|

Takt — |

C |

|

/- |

K_J\ |

B-Takt■

J G C

K Q

Takt -

B Q C

U

r-

■4—

Takt

T-W-TK

Ti — h —

Takt —

|

B |

Q |

|

C |

Q |

T-W~TK

Rys. 3.30. Przykłady konwersji typu przerzutnika

80

Wyszukiwarka

Podobne podstrony:

Image064 I I ©Z-O . Jz Rys. 3.20. Schematy logiczne układów realizujących wieloargumentową funkcję A

Image229 Schemat logiczny dekady liczącej w kodzie 8421 przedstawiono na rys. 4.230. Maksymalna częs

Image241 Rys. 4.254. Schemat logiczny dekady rewersyjnej liczącej w kodzie Johnsona Rys. 4.255. Sche

Image244 1 Rys. 4.257 Schemat logiczny rejestru liczącego mod.2rc—1Takt Rys. 4.258 Schemat logiczny

57732 skanuj0007 (236) xzn Rys. 4.369. Schemat logiczny konwertera kodu £ z 8 na kod 1 z 8, z równol

Image064 I I ©Z-O . Jz Rys. 3.20. Schematy logiczne układów realizujących wieloargumentową funkcję A

Image010 jących stanom logicznym) i mały margines zakłóceń. Pobór prądu przez bramkę w obydwu stanac

Image050 operację sumy logicznej Y, jest przedstawiony na rys. 3.4. Napięcie baterii roz-świeci żaró

więcej podobnych podstron