6800810194

Organizacja laboratorium

W czasie laboratorium należy wykonać 9 ćwiczeń, po 3 z części PSPICE, Verilog oraz VHDL. Ćwiczenia punktowane są odpowiednio po 5, 5, 6 (PSPICE), 5, 6, 6 (Verilog) oraz 5, 6, 6 (VHDL) punktów co daje łącznie 50pkt. Warunkiem zaliczenia laboratorium jest uzyskanie minimum 25 punków. Informacje dotyczące obsługi oprogramowania Xilix ISE 10.1 wykorzystywanego podczas laboratorium można znaleźć tutaj :http://www.ue.eti.pg.gda.pl/lpgalab/info próg spartan3/index.html

Zadania do wykonania w czasie laboratorium z części PSPICE

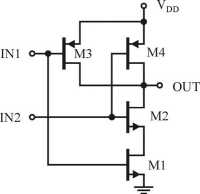

Zadanie 1 - badanie bramki CMOS nand. W czasie laboratorium należy' wykonać badania symulacyjne bramki NAND CMOS. Schemat bramki przedstawiony jest na poniższym rysunku. Należy zastosować nazwy węzłów sygnałowych jak podane na rysunku. Modele tranzystorów MOS (technologia AMI C5) należy pobrać z następującego linka: http://www.ue.eti.pg. gda.pl/~bpa/imis/ami c5 .lib. Jako napięcie zasilające należy przyjąć źródło napięciowe o wydajności 3.3V.

Badana bramka CMOS NAND. Należy przyjąć wymiary tranzystorów NMOS w=l,8um 1=0,6um oraz PMOS w=5,-tum 1=0,(mm.

Należy stworzyć plik tekstowy w który m będzie znajdował się opis listy' połączeniowej badanego układu wraz z zadanymi symulacjami. W ramach symulacji należy wykonać następujące badania:

1) Należy sprawdzić poprawność działania bramki poprzez podanie na wejścia przebiegów prostokątnych o częstotliwościach odpowiednio 50MHz i 25MHz.

2) Należy bramkę obciążyć drugą bramką NAND (pojedynczym wejściem kolejnej bramki) i znaleźć czas narastania sygnału na wyjściu bramki (liczony od 10% do 90% wartości sygnału), czas opadania sygnału na wyjściu bramki (liczony od 90% do 10% wartości sygnału) oraz czas propagacji sygnału z wejścia do wyjścia (liczony dla 50% wartości sygnału na wejściu i wyjściu).

3) Należy zewrzeć oba wejścia bramki i traktować te zwarte wyprowadzenia jako pojedyncze wejście. Dla takiego układu należy wykonać analizę staloprądową zmieniając napięcie wejściowe w zakresie od 0 do 3,3V. Należy znaleźć napięcie wejściowe dla którego napięcie wyjściowe jest równe 1,65V.

4) Dla stałego napięcia wejściowego wyznaczonego w pkt. 3) należy wykonać analizę zmiennoprądowy i wyznaczyć wzmocnienie oraz pasmo 3dB bramki NAND w układzie wzmacniacza.

5) Należy do wejścia wzmacniacza podać sygnał harmoniczny o amplitudzie 30mV, częstotliwości 10kHz i składowej stałej wyznaczonej w pkt. 3) i wyznaczyć zniekształcenia harmoniczne sygnału na wyjściu bramki.

Wyszukiwarka

Podobne podstrony:

2. Wyznaczanie stałej tensometru Ćwiczenie laboratoryjne należy wykonać na specjalnie przygotowanym

PLANOWANIE 1. Ustal, w jakim czasie należy wykonać ćwiczenie. 2.

skanuj0004 (167) 28. Jakie czynności należy wykonać bezpośrednio po uwolnieniu porażonego spod dział

Mikrobilogia zywności�9 Temperatura Pomiar temperatury należy wykonać natychmiast po pobraniu próbki

49809 skanuj0004 (167) 28. Jakie czynności należy wykonać bezpośrednio po uwolnieniu porażonego spod

Jeżeli w wytłoczę© otrzymanej na drodze ciągnienia przewidziany jest otwór w dnie, to należy wykonać

Wydział PPT Laboratorium PODSTAW BIOFOTONIKI Ćwiczenie nr 4 Pomiar parametrów ilościowych oraz

BN-75 6026-24 5 Miareczkowanie należy wykonać bezpośrednio po przeprowadzeniu

Przebieg ćwiczenia. Po włączeniu zasilacza spektrofometru oraz lampy rtęciowej regulujemy przyrząd

9 Laboratorium_ W ćwiczeniu laboratoryjnym, po wprowadzeniu do programu MA-TLAB, należy wykonać

Laboratorium nr 1Sprawy organizacyjne Laboratoria podzielone są na 3 cykle po 5 ćwiczeń w każdym. Po

Materiałoznawstwo - ćwiczenia laboratoryjne Rys. 9. Młotek Schmidta po wykonaniu badania - trzpień

więcej podobnych podstron