Procesory rodziny x86

Dariusz Chaberski

8086

§ produkowany od 1978

§ magistrala adresowa - 20 bitów (1 MB)

§ magistrala danych - 16 bitów

§ wielkość instrukcji - od 1 do 6 bajtów

§ częstotliwośc pracy

od 5 MHz (IBM PC 4.77 MHz)

do 10 MHz (tryb TURBO)

§ praca w trybie rzeczywistym

2

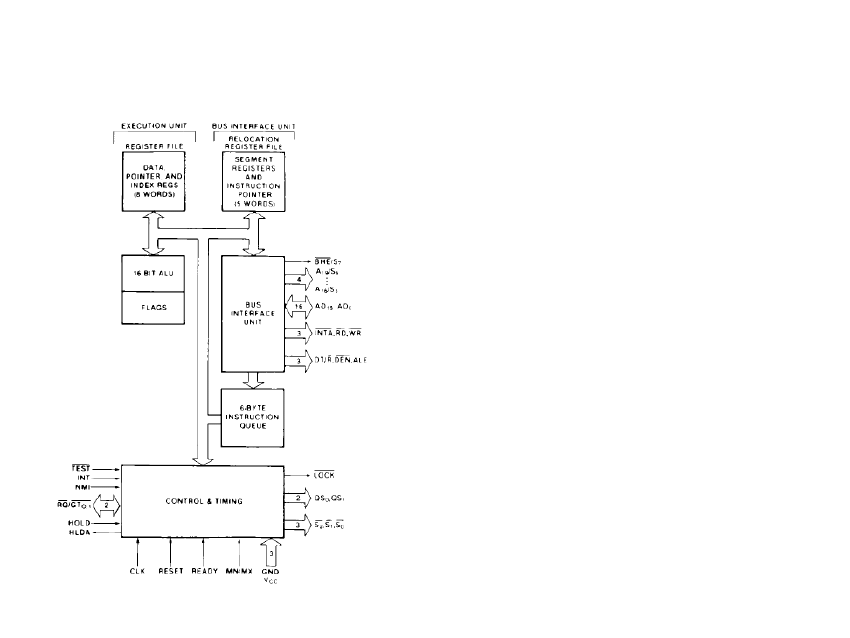

§ Obudowa

3

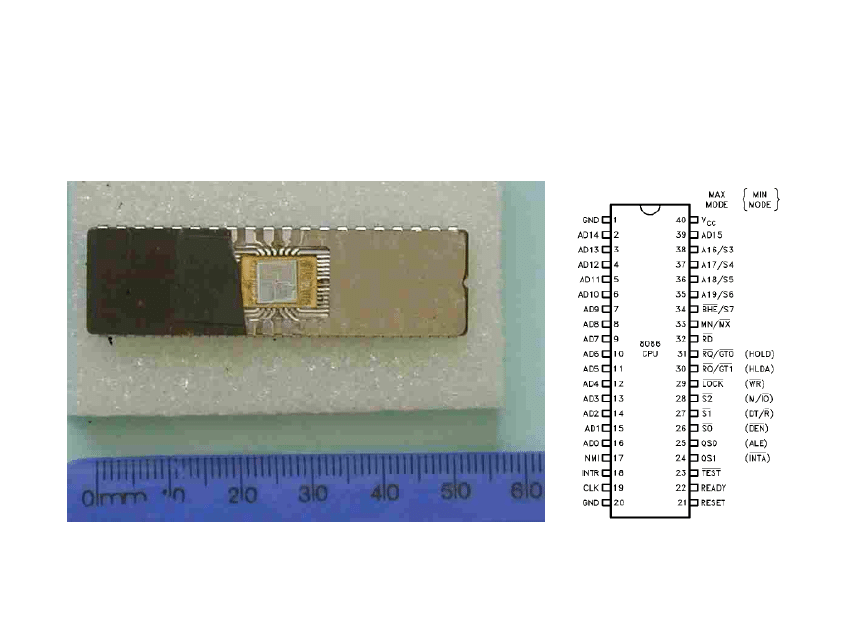

§ Technologia

§ 29000 tranzystorów

§ technologia 3 µm NMOS

§ pojedyncze zasilanie 5V

4

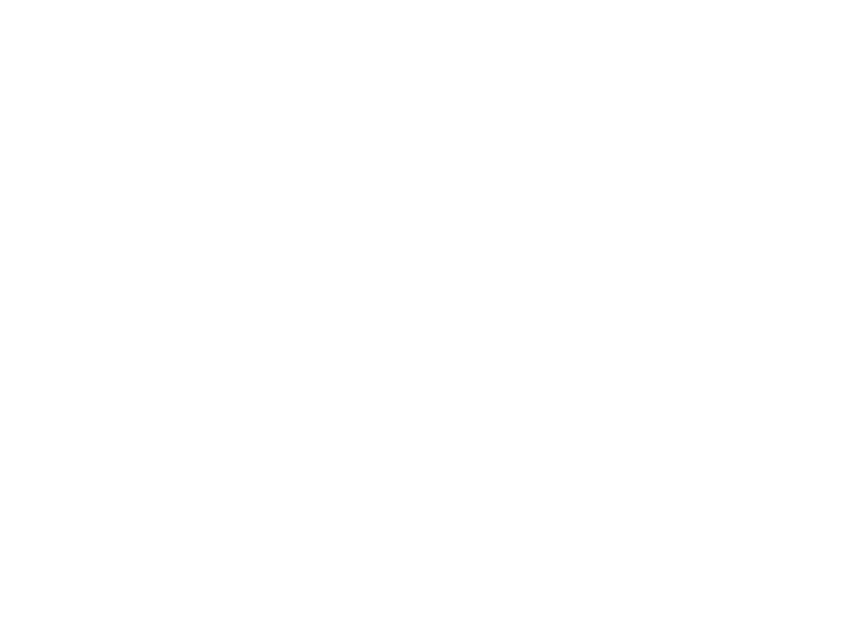

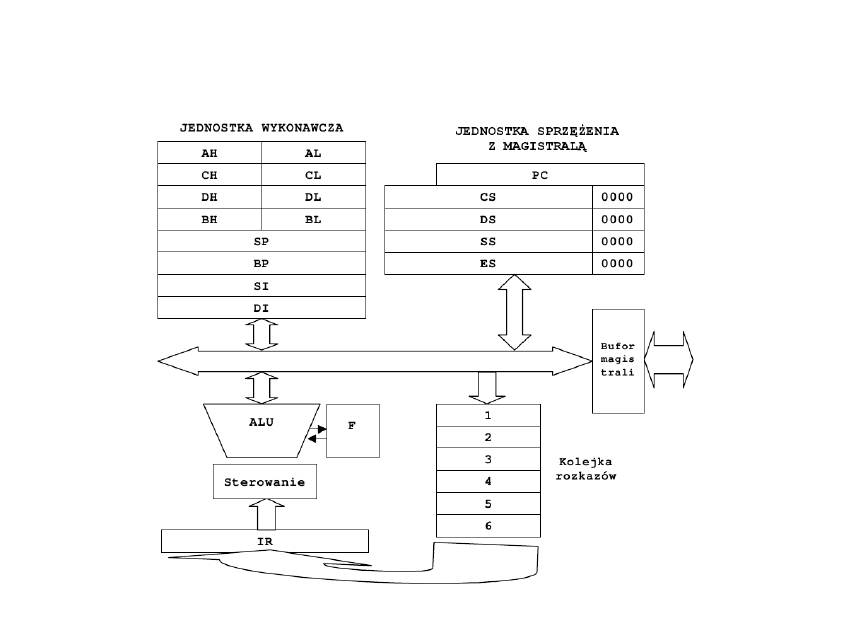

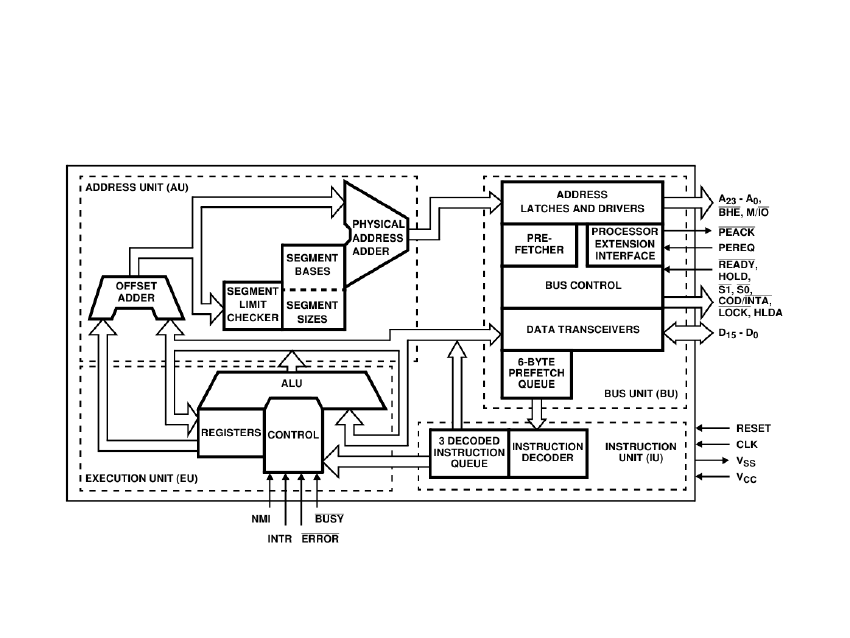

§ Budowa procesora 8086

5

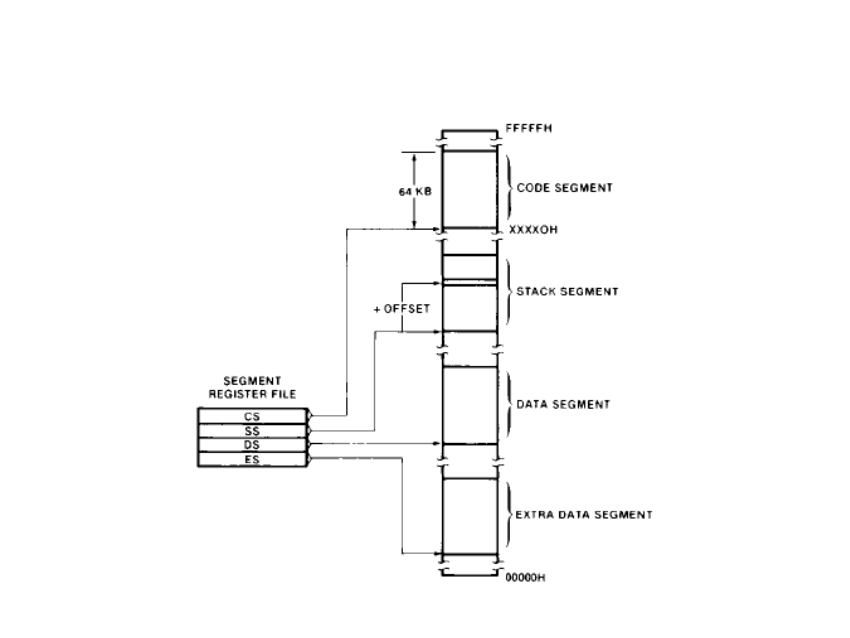

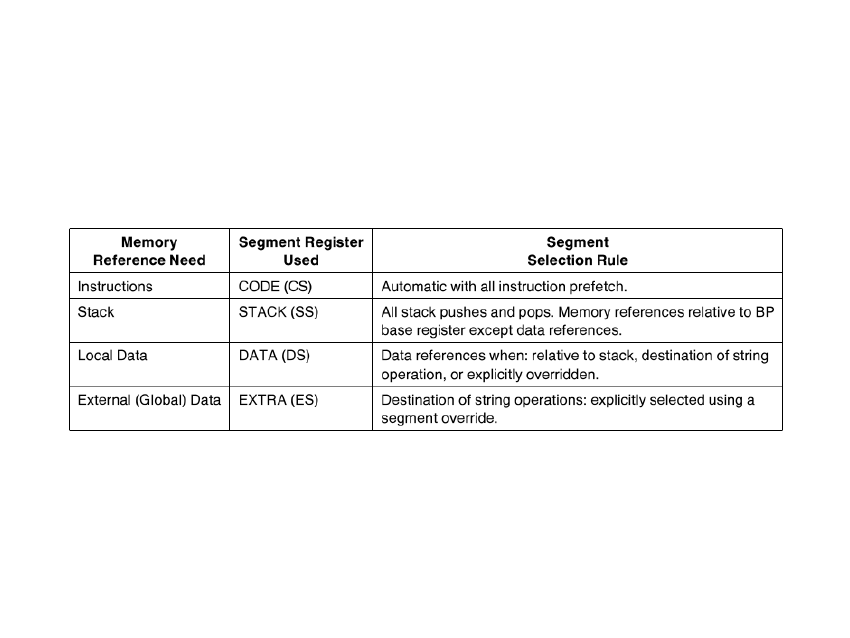

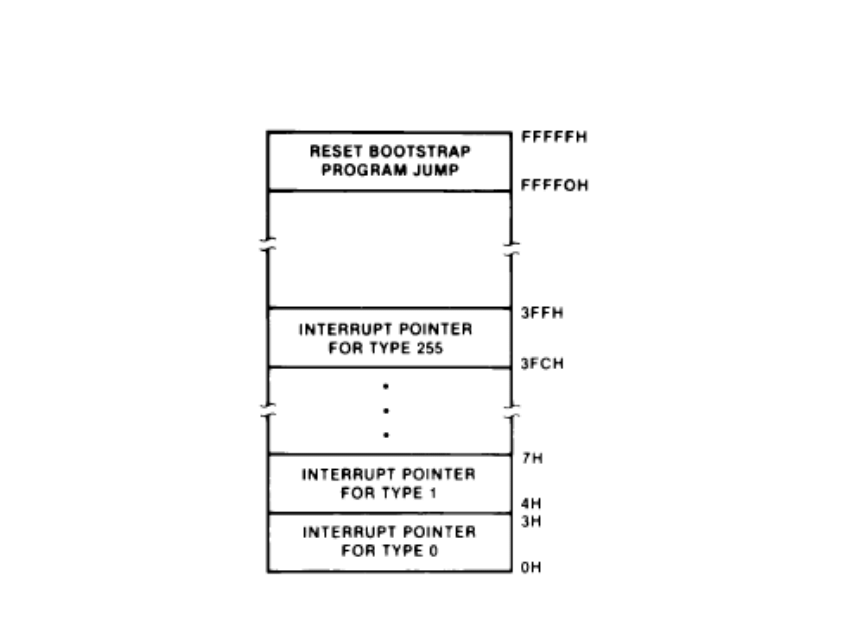

§ Memory Organization

6

7

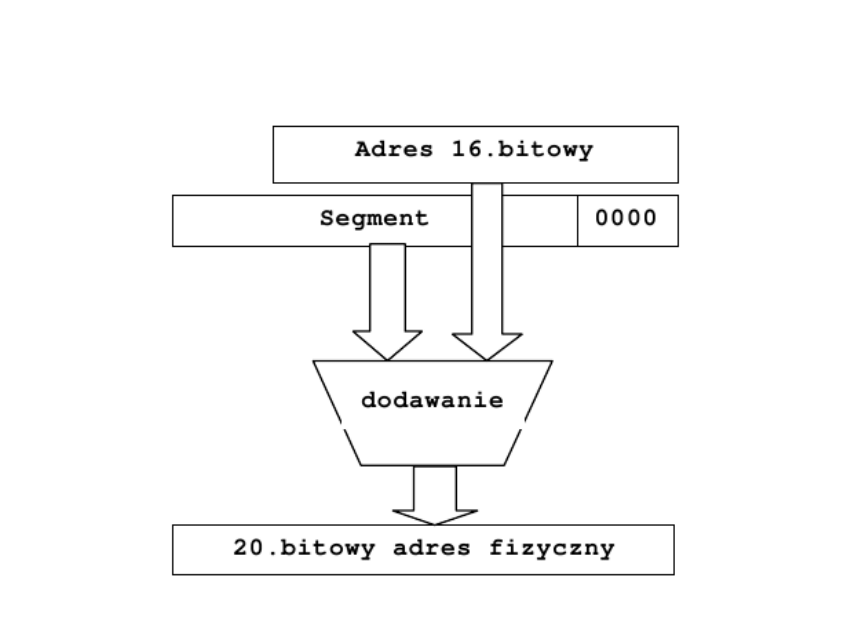

§ Sumator do obliczania 20-bitowego adresu fizycznego

8

§ Reserved Memory Locations

9

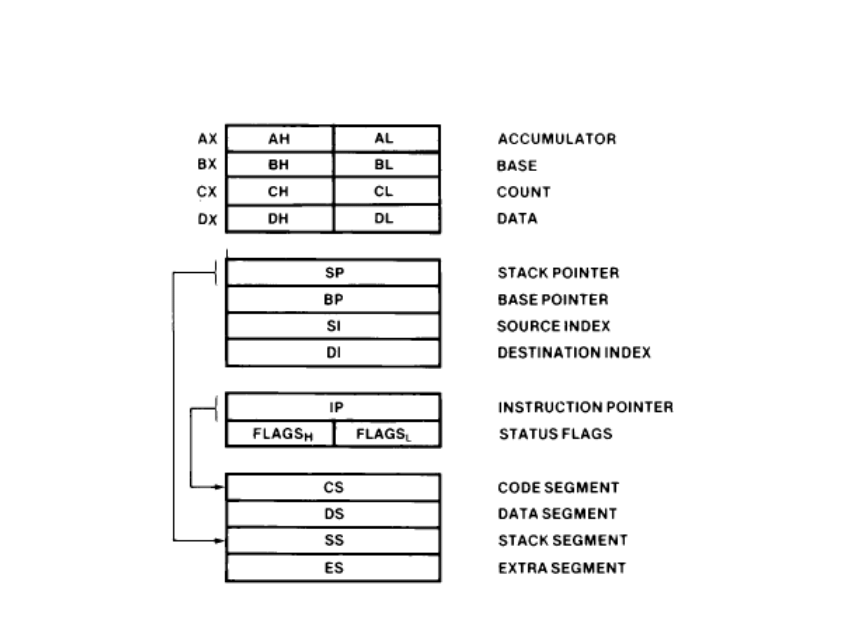

§ 8086 Register Model

10

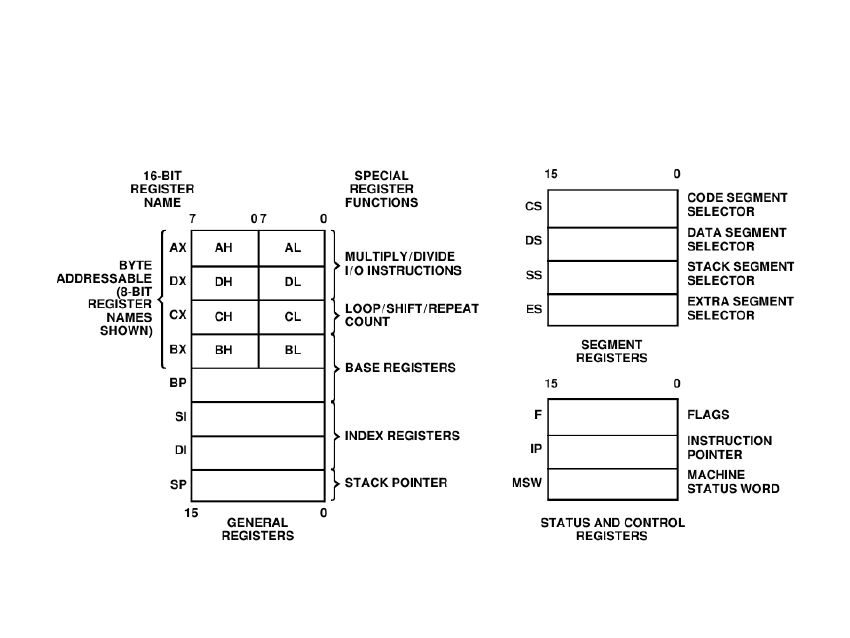

§ Rejestry

+ AX AH:AL - akumulator

+ BX BH:BL - rejestr podstawowy

+ CX CH:CL - rejestr zliczający

+ DX DH:DL - rejestr danych

+ F - rejestr znaczników

+ SP - wskaźnik stosu

+ BP - wskaźnik bazy

+ SI - rejestr indeksowy źródła

+ DI - rejestr indeksowy przeznaczenia

11

§

+ CS - rejestr segmentowy programu

+ DS - rejestr segmentowy danych

+ SS -rejestr segmentowy stosu

+ ES - dodatkowy rejestr segmentowy

+ PC - licznik rozkazów

+ IR - rejestr instrukcji

12

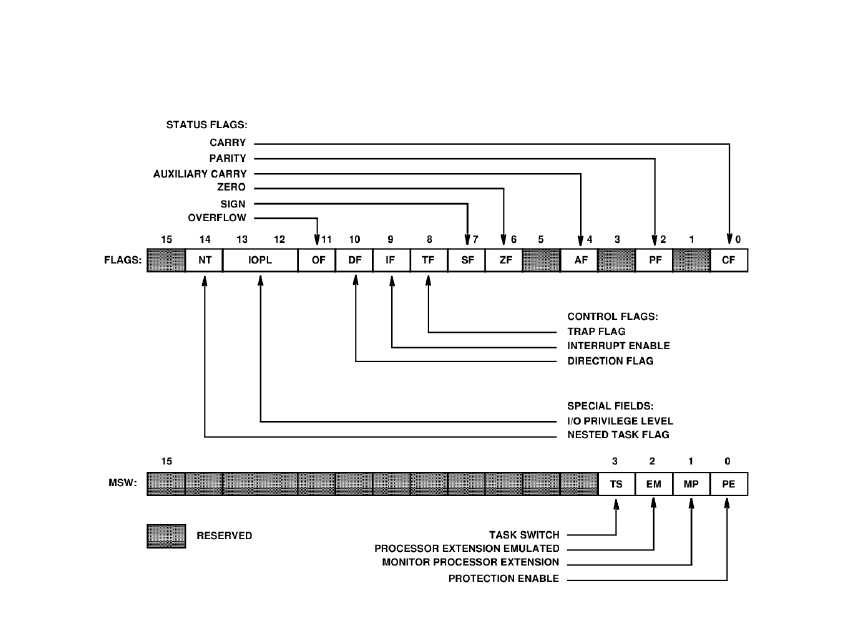

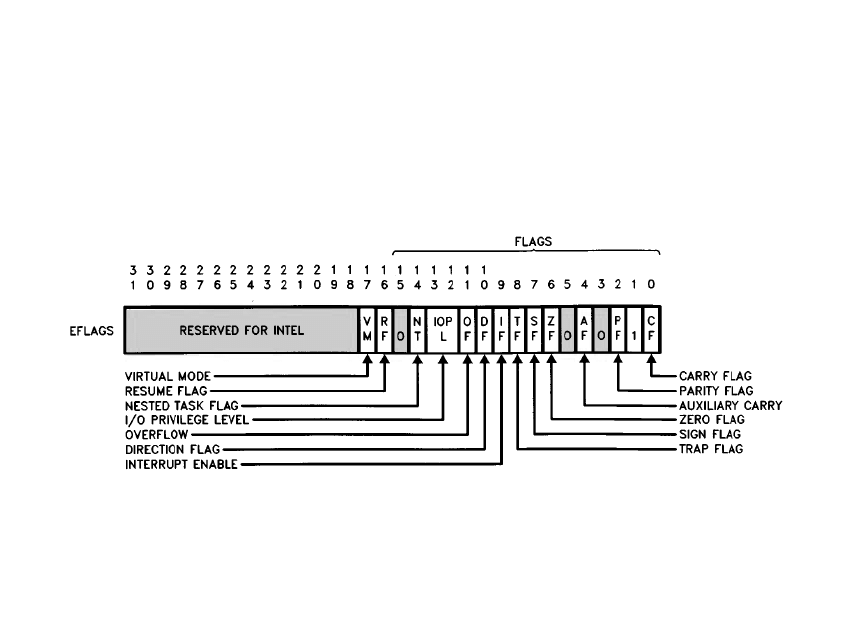

§ rejestr znaczników F (16 bitów)

+ operacje arytmetyczno logiczne

3 b0 - C - wskaźnik przeniesienia

3 b2 - P - wskaźnik parzystości

3 b4 - AC - wskaźnik przeniesienia pomocniczego

3 b6 - Z - wskaźnik zera

3 b7 - S - wskaźnik znaku

3 b11 - V - wskaźnik nadmiaru

+ znaczniki kontrolne

3 b8 - T - wskaźnik pracy krokowej

3 b9 - I - wskaźnik globalnego blokowania przerwań

3 b10 - D - wskaźnik kierunku automodyfikacji adresu operandu (przesłania blokowe)

13

§ przykładowe instrukcje

+ MOV DL, 10101000B - przesłanie 8 bitowe

+ MOV AX, CX - przesłanie 16 bitowe

+ PUSH CS (brak wersji 8 bitowej)

+ POP DI (brak wersji 8 bitowej)

+ IN AX, DX - przesłanie 16 bitowe

+ IN AL, DX - przesłanie 8 bitowe

+ OUT DX, AX/AL

+ ADD DI, CX

+ ADC CL, CH

+ SUB AL, 10H

+ SBB AX, DI (ang. with borrow)

+ MOV [DI], AX

14

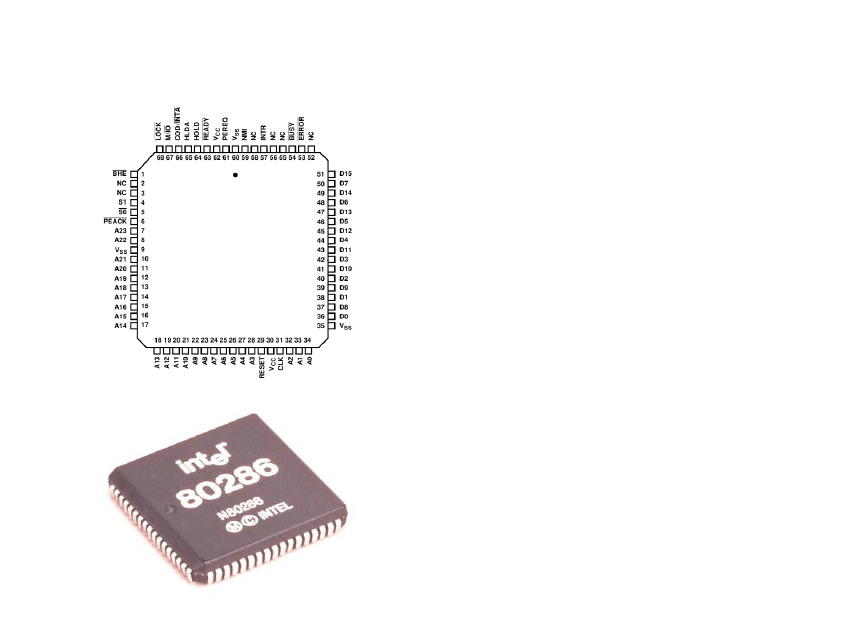

80286

15

§ Obudowa

§ Charakterystyka

+ produkowany od 1982

+ magistrala adresowa - 24 bity (16 MB

pamięci fizycznej)

+ magistrala danych - 16 bitów

+ częstotliwośc pracy - od 6 MHz do 25

MHz

+ praca w trybie rzeczywistym

+ praca w trybie chronionym

16

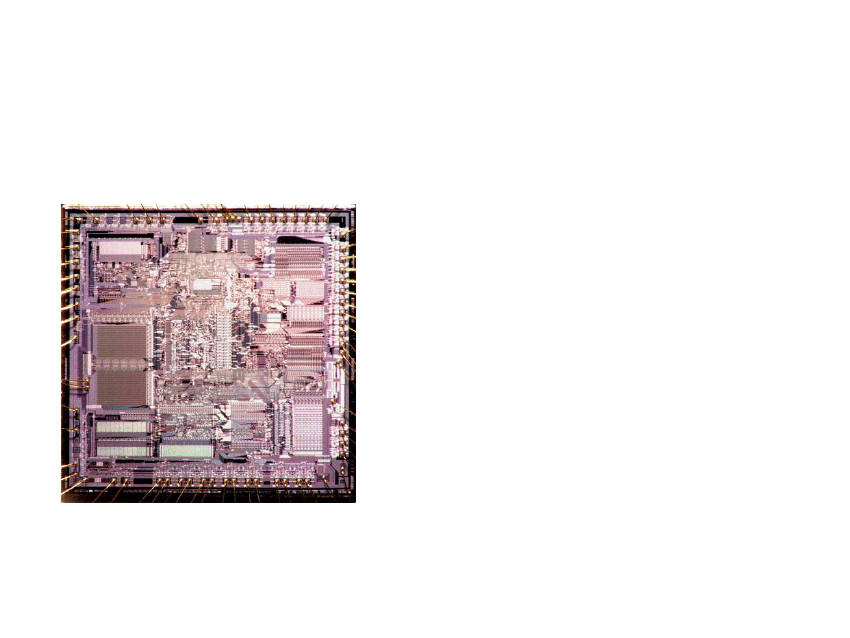

§ Technologia

§ 134000 tranzystorów

§ technologia 1.5 µm CMOS

§ pojedyncze zasilanie 5V

17

§ Registers

18

§ STATUS AND CONTROL REGISTER BIT FUNCTIONS

19

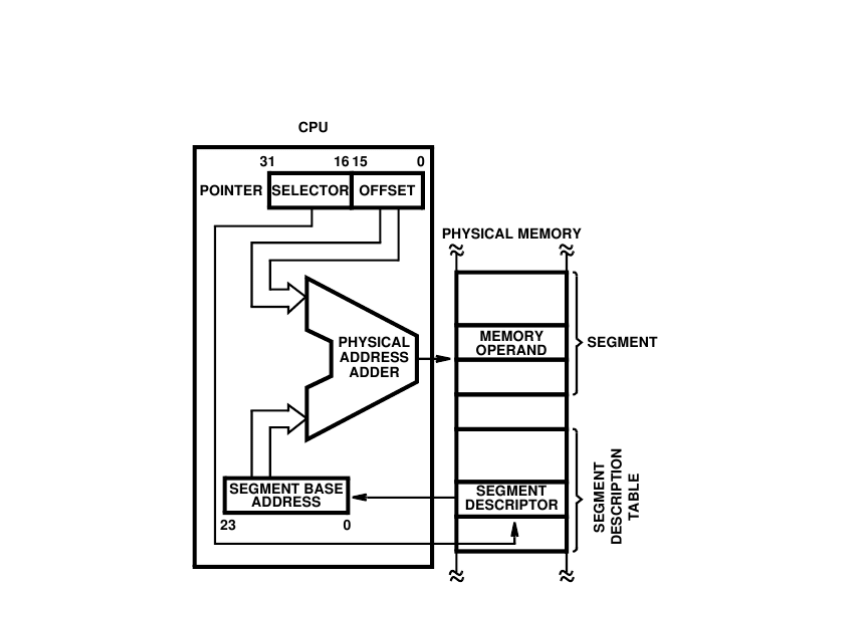

§ PROTECTED MODE MEMORY ADDRESSING

20

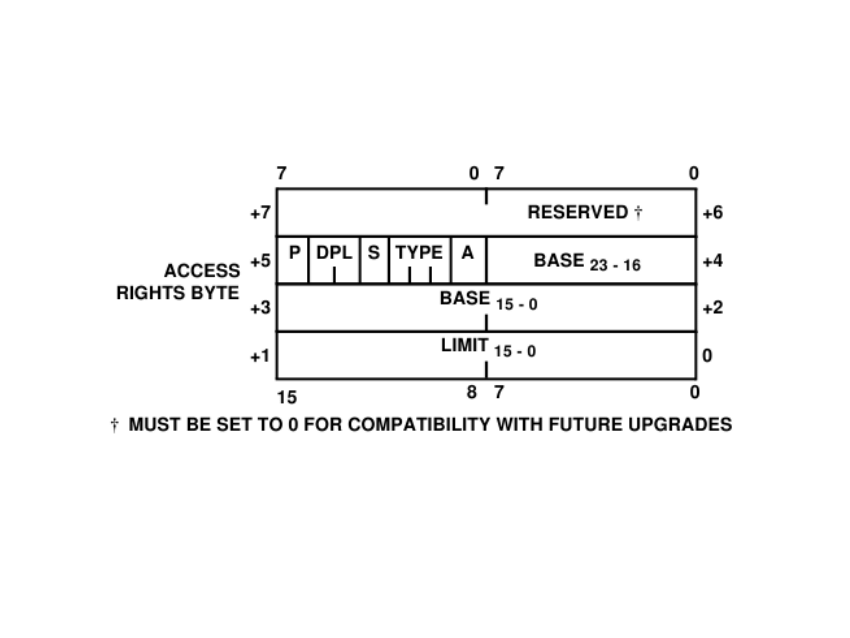

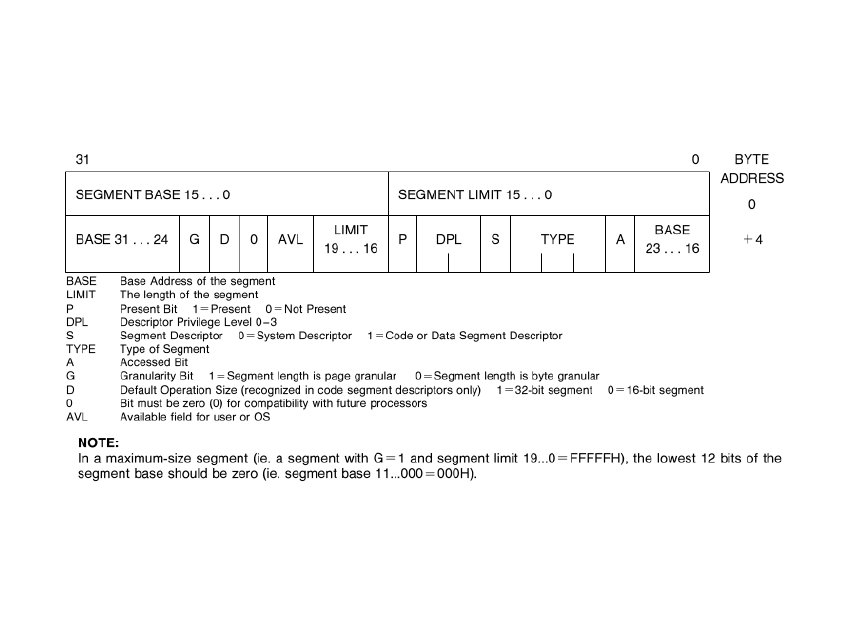

§ CODE OR DATA SEGMENT DESCRIPTOR

P - present

DPL - Descriptor Privilege Level

S - S=1 Code or Data, S=0 System Segment Descriptor or Gate Descriptor

A - Accessed

21

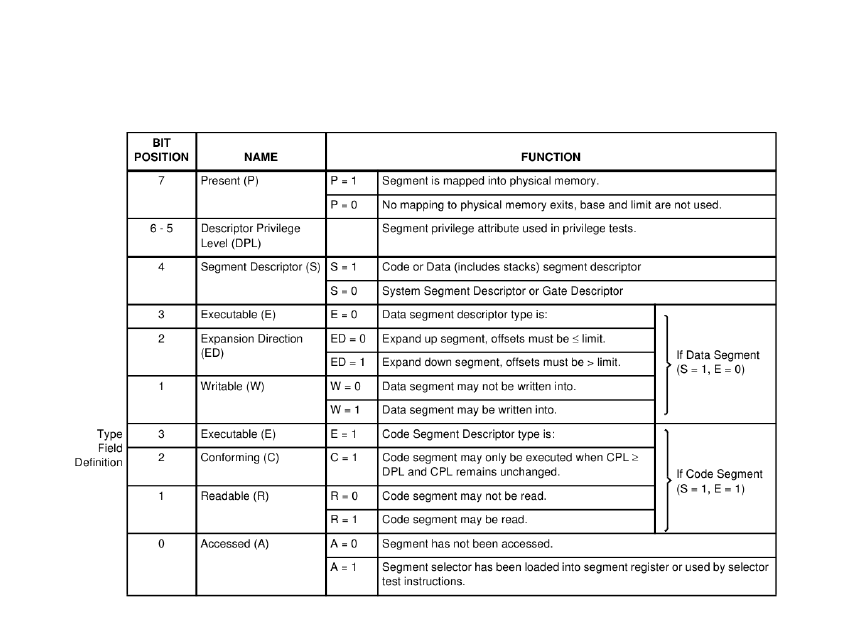

§ CODE AND DATA SEGMENT DESCRIPTOR FORMATS - ACCESS RIGHTS BYTE DEFINI-

TION

22

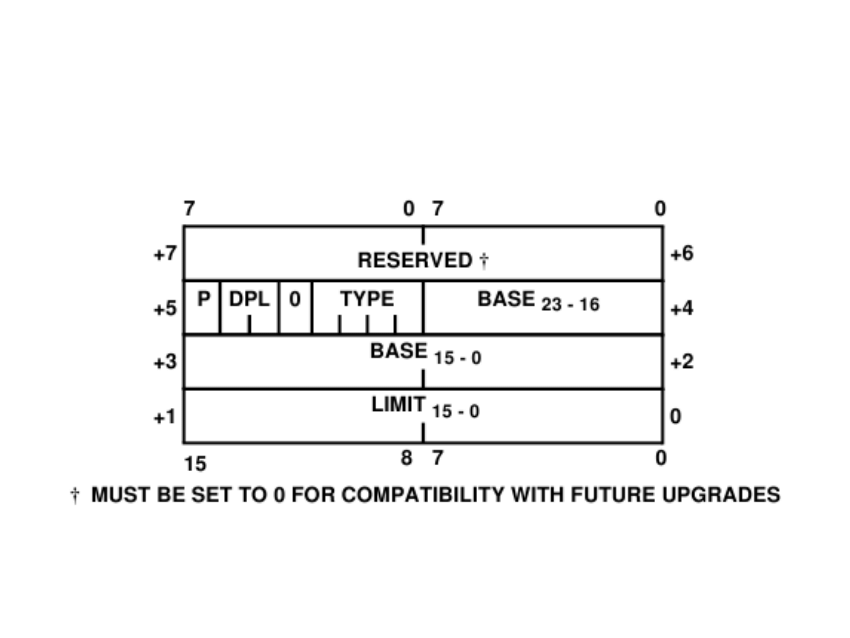

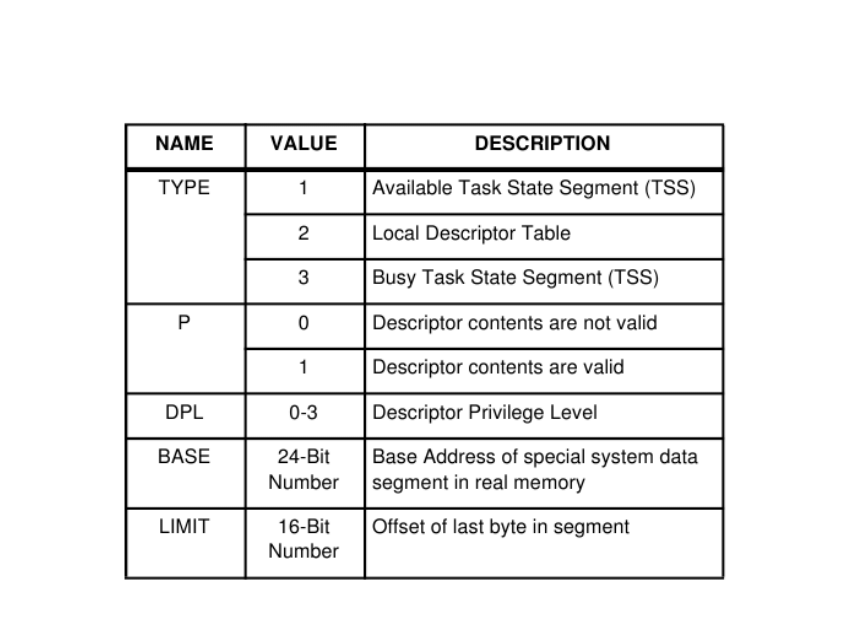

§ SYSTEM SEGMENT DESCRIPTOR

23

§ SYSTEM SEGMENT DESCRIPTOR FORMAT FIELDS

24

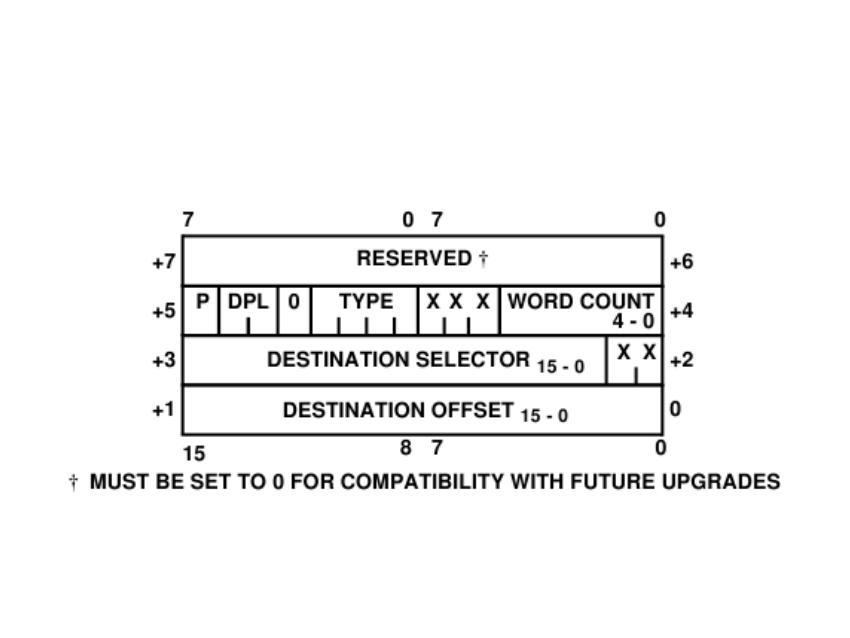

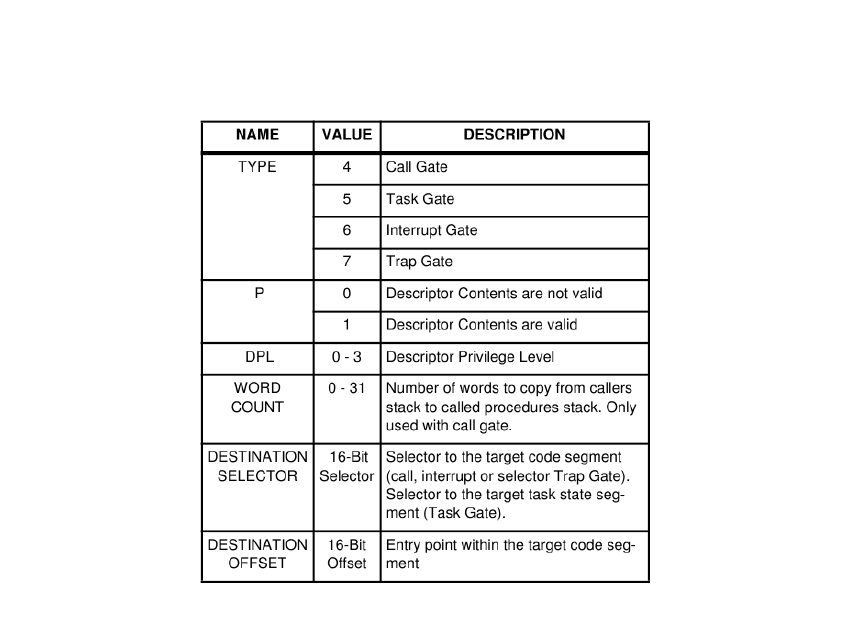

§ GATE DESCRIPTOR

25

§ GATE DESCRIPTOR FORMAT FIELD

26

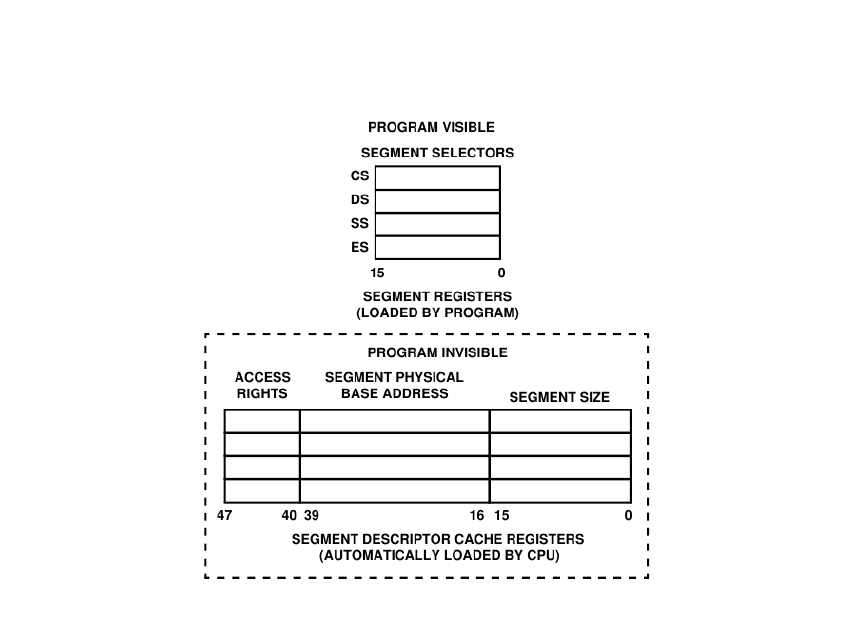

§ DESCRIPTOR CACHE REGISTERS

27

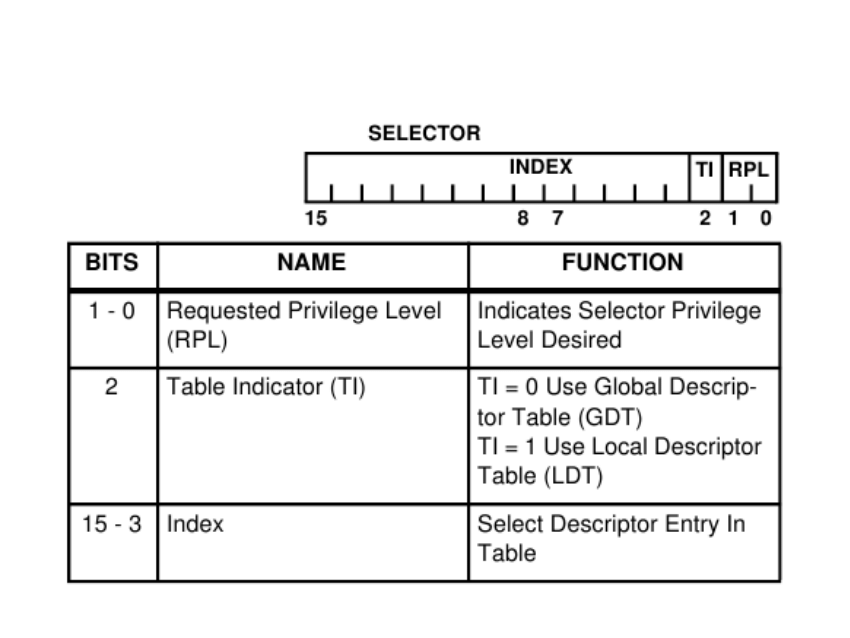

§ SELECTOR FIELDS

28

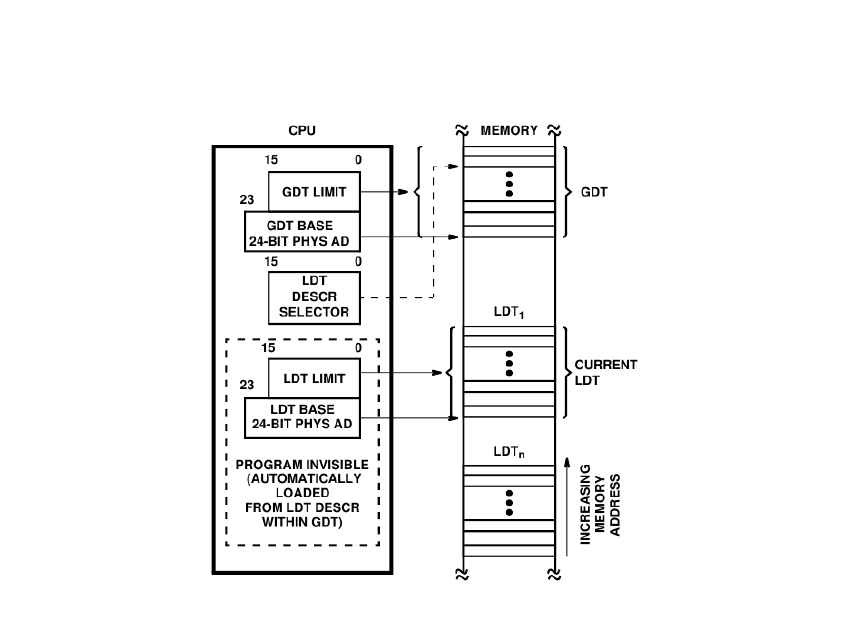

§ LOCAL AND GLOBAL DESCRIPTOR TABLE DEFINITION

29

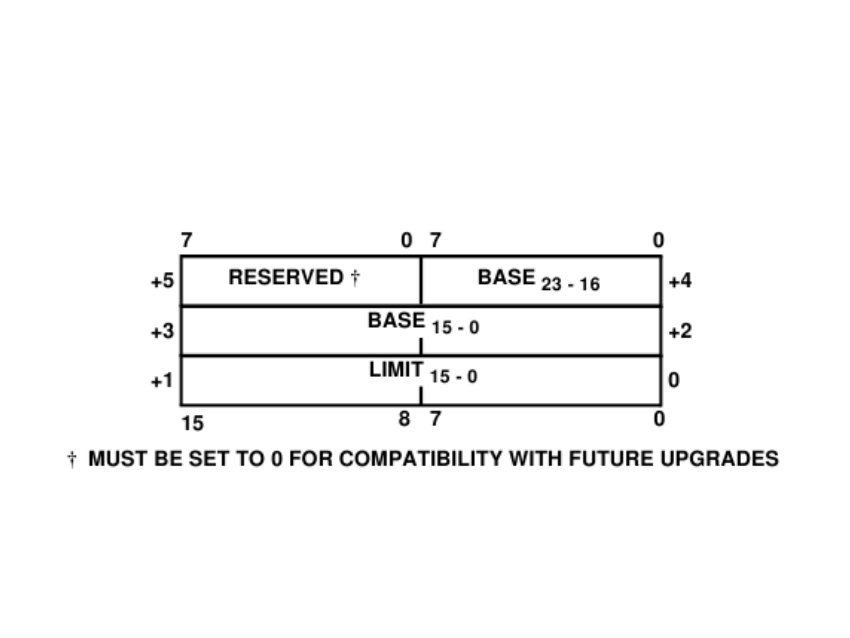

§ GLOBAL DESCRIPTOR TABLE AND INTERRUPT DESCRlPTOR TABLE DATA TYPE

30

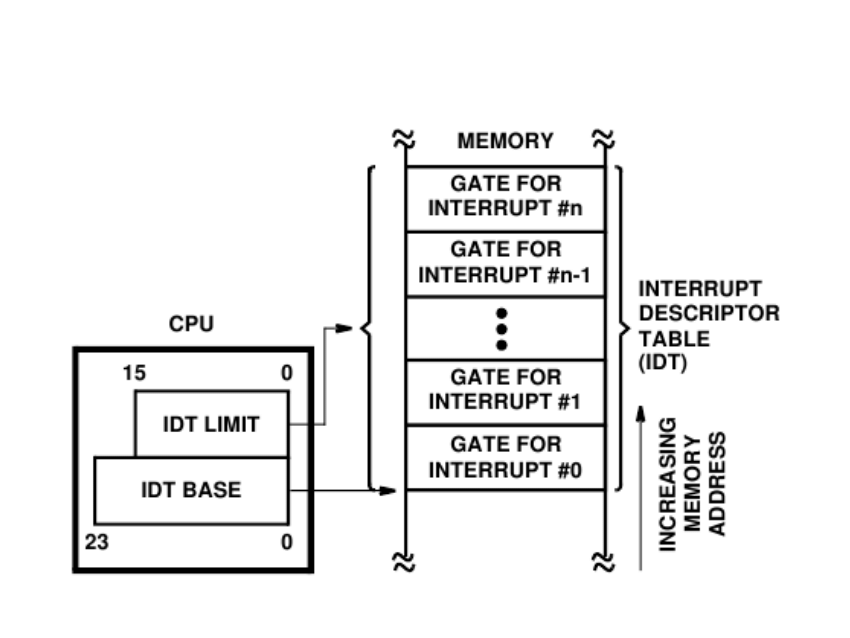

§ INTERRUPT DESCRIPTOR TABLE DEFINITION

31

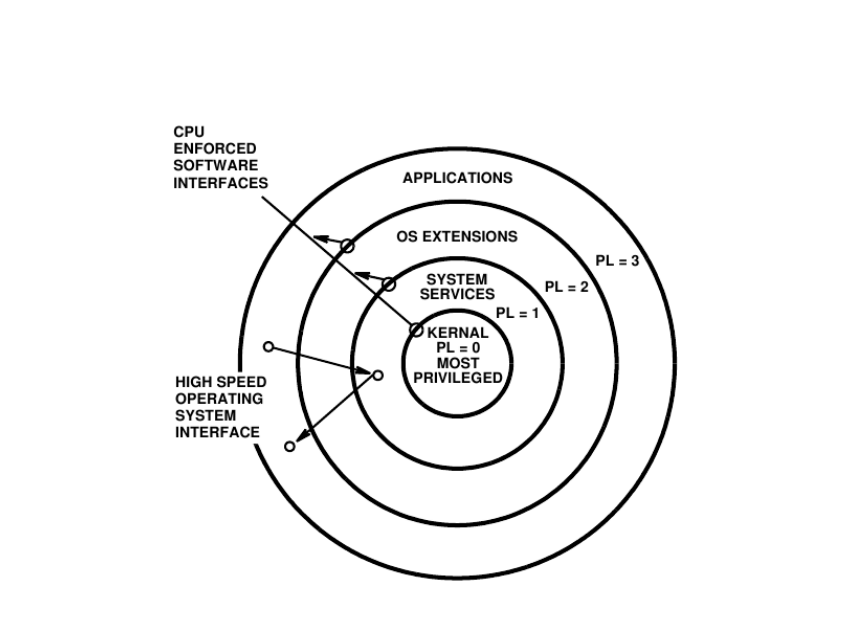

§ HIERARCHICAL PRIVILEGE LEVELS

32

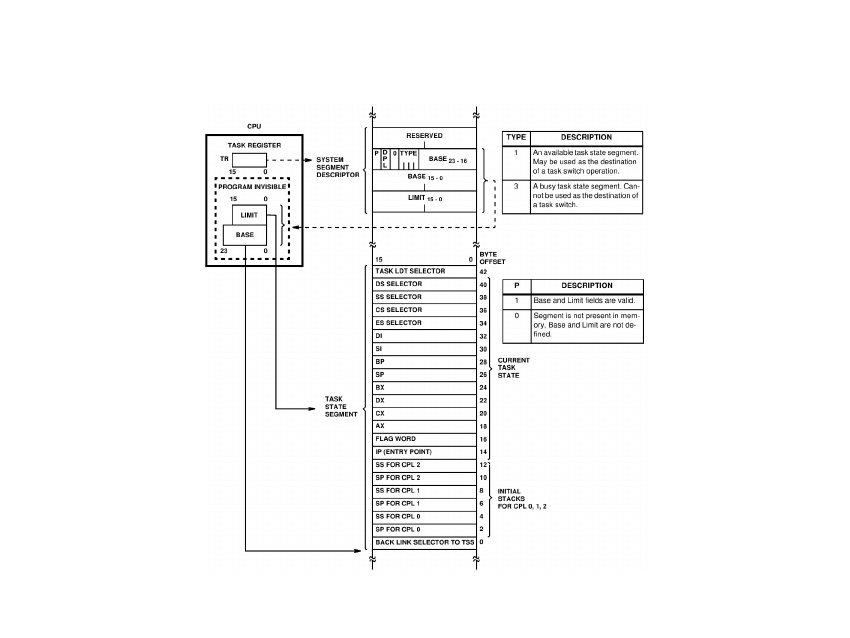

§ TASK STATE SEGMENT AND TSS REGISTERS

33

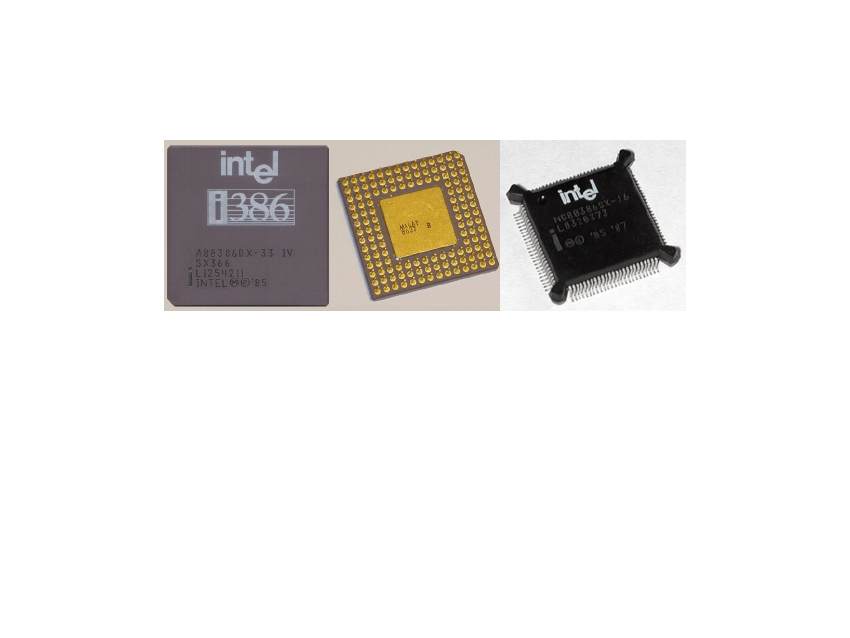

80386

§ Obudowa

§ Charakterystyka

+ dostępny od 1985

+ magistrala adresowa 32 bitowa (4 GB pamięci fizycznej)

+ magistrala danych 32 bitowa (SX zewnętrzna 16 bitowa)

+ częstotliwość pracy od 16 MHz do 33 MHz

+ praca w trybie rzeczywistym

+ praca w trybie chronionym (pamięć wirtualna 64 TB)

+ praca w trybie wirtualnym (V86 - ang. Virtual 86)

34

§ tryb Virtual-86

+ umożliwia uruchamianie jednocześnie wielu programów przeznaczonych dla trybu rzeczywistego

na jednym procesorze

+ pamięć 1MB

+ bezpośredni dostęp do rejestrów procesora

+ dostęp do portów procesora oraz obsługa przerwań są sankcjonowane przez system system ope-

racyjny

+ przykład

3 Windows - uruchamianie programów DOSowych

3 Linux - DOSemu

35

§ Technologia

§ 275000 tranzystorów

§ technologia 1(1.5) µm CMOS

§ pojedyncze zasilanie 5V

36

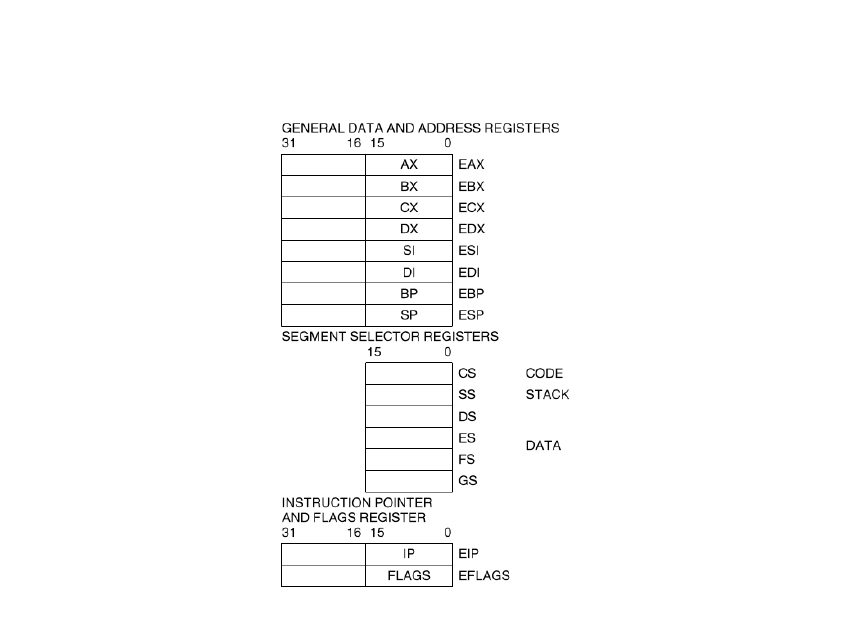

§ Base Architecture Registers

37

§ przykładowe instrukcje

+ MOV DL, 10101000B - przesłanie 8 bitowe

+ MOV AX, CX - przesłanie 16 bitowe

+ MOV EAX, 0FF00DA5AH - przesłanie 32 bitowe

+ PUSH EAX (brak wersji 8 bitowej)

+ POP EDX (brak wersji 8 bitowej)

+ IN AL/AX/EAX, DX

+ OUT DX, EAX/AX/AL

+ ADD AL/AX/EAX, CL/CX/ECX

38

§ Flags Register

39

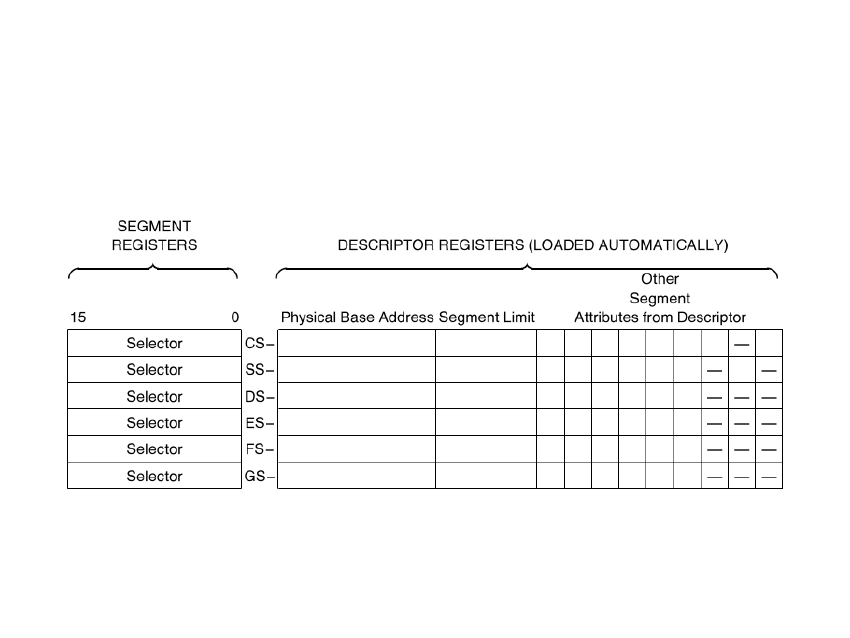

§ Segment Registers and Associated Descriptor Registers

40

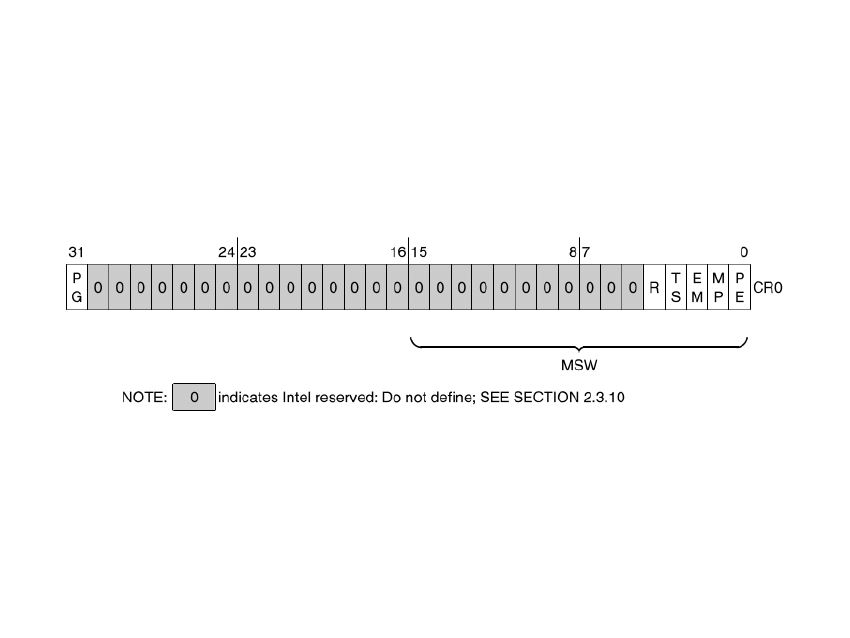

§ Control Register 0

R (reserved bit 4)

PG (Paging Enable bit 31)

41

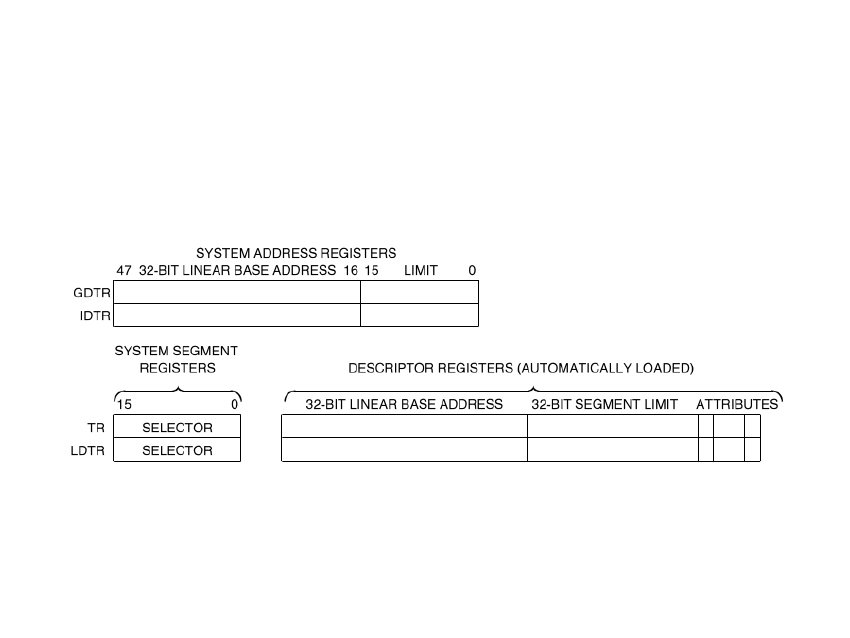

§ System Address and System Segment Registers

42

§ Segment Descriptors

43

Koprocesor arytmetyczny x87

44

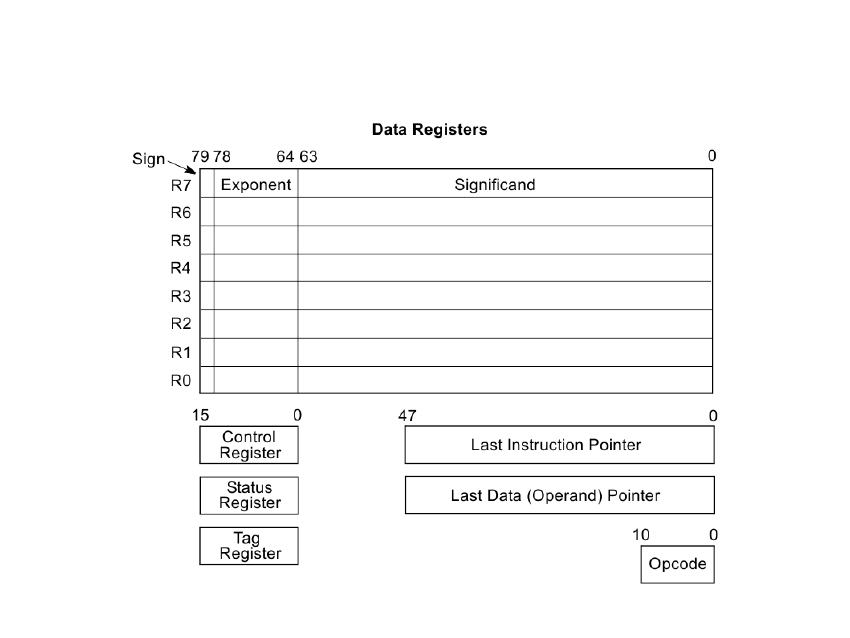

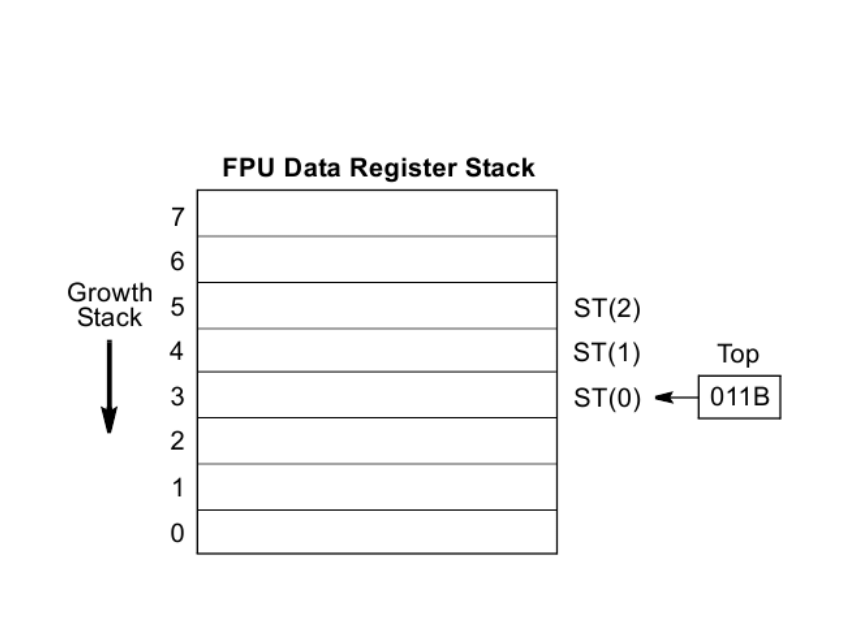

§ FPU Data Register Stack

45

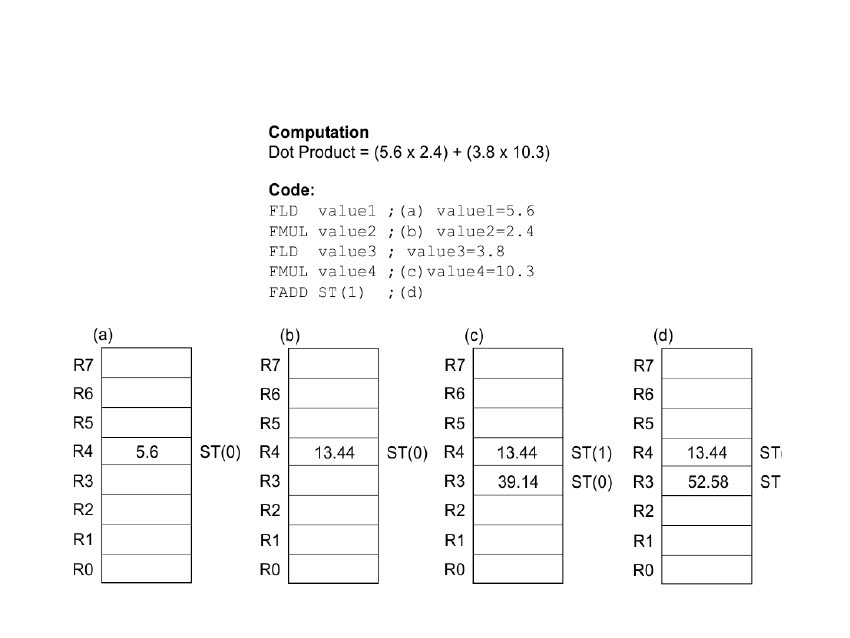

§ Example FPU Computation

46

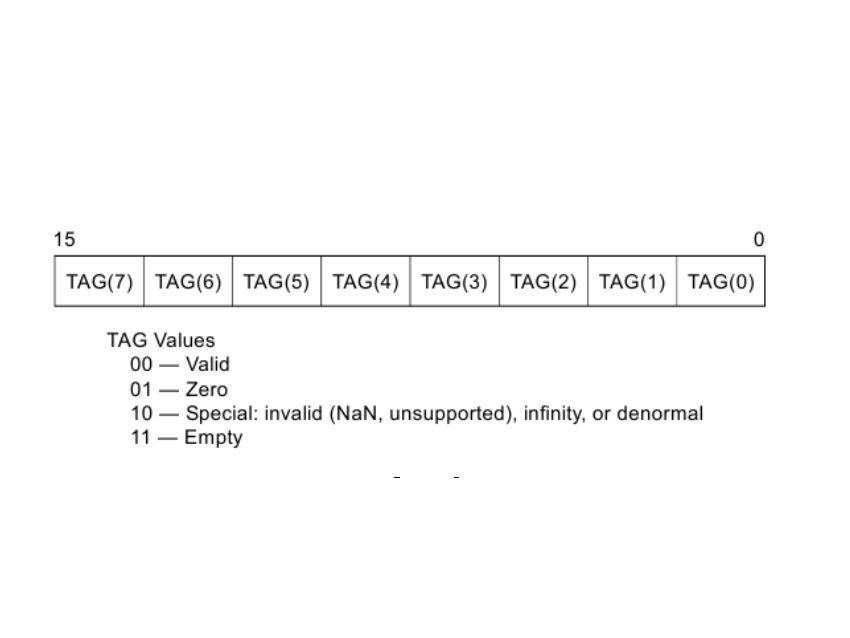

§ FPU Tag Word

x87-

precision control field.png

47

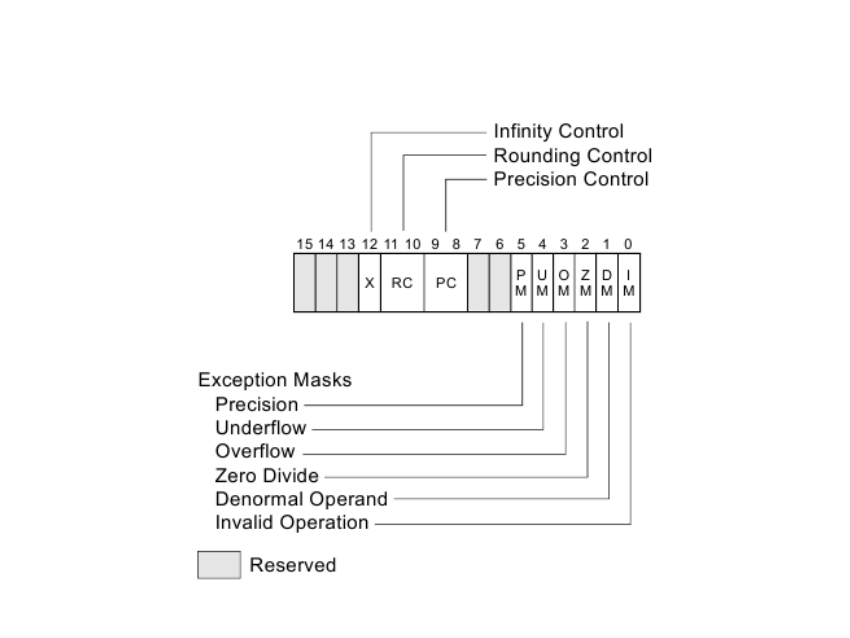

§ FPU Control Word

48

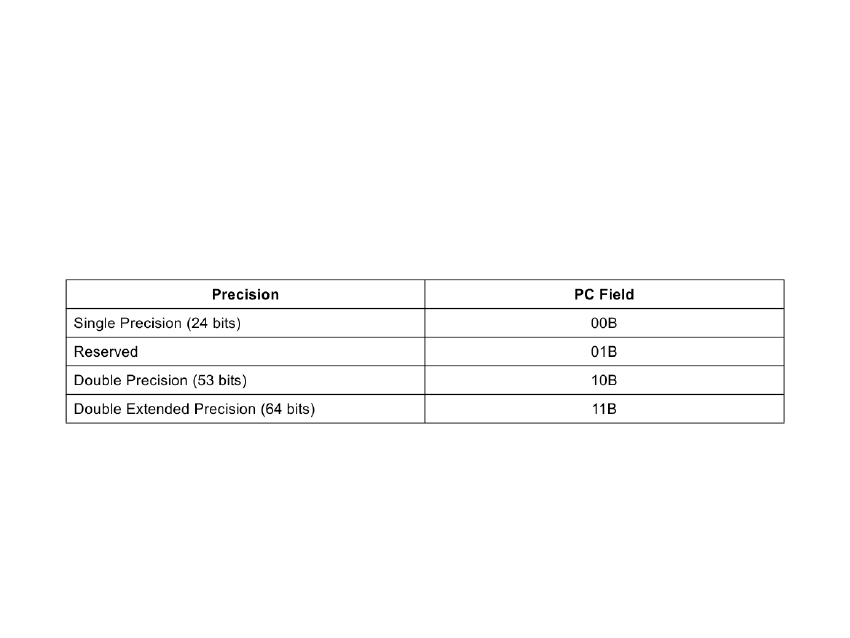

§ Precision Control Field

49

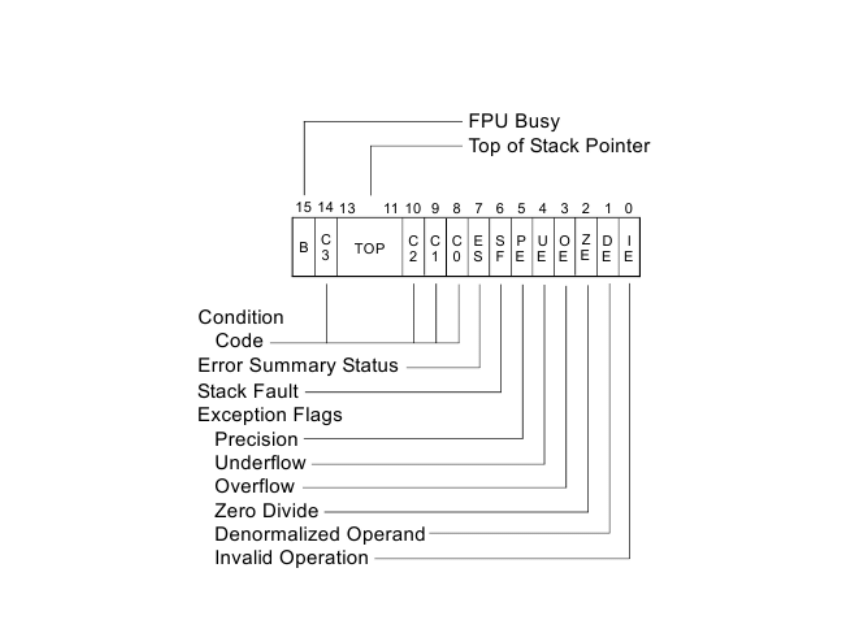

§ FPU Status Word

50

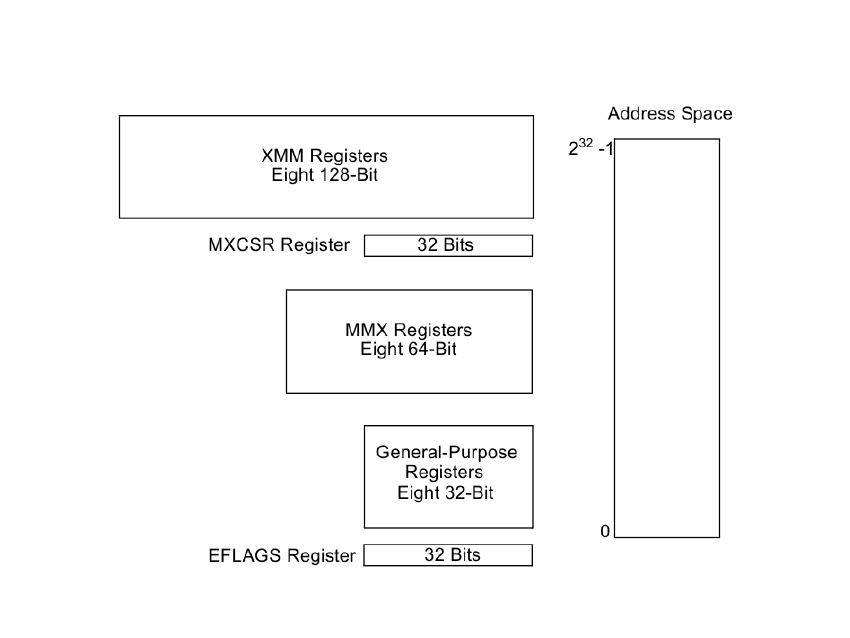

MMX

§ MultiMedia eXtensions, Matrix Math eXtensions

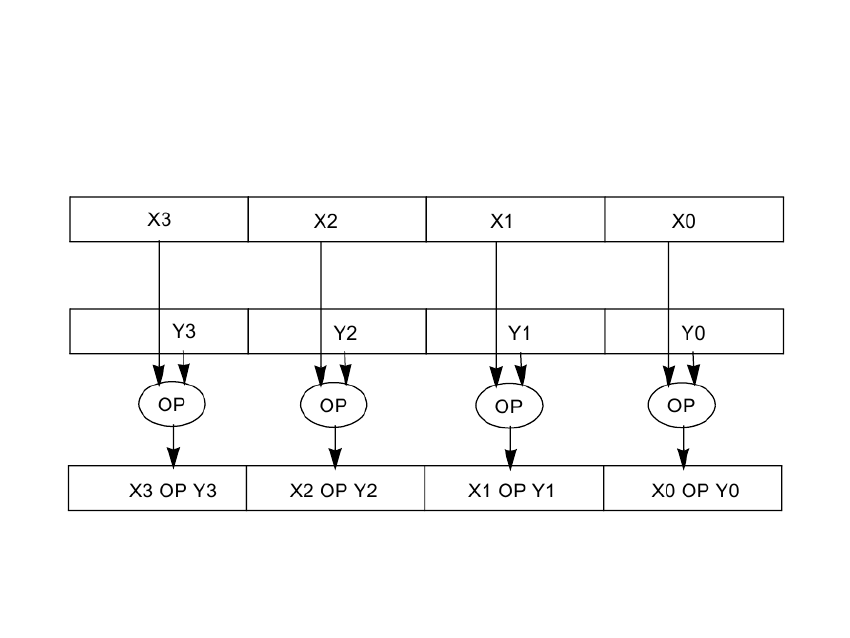

+ zestaw 57 instrukcji typu SIMD (ang. Single Instruction Multiple Data)

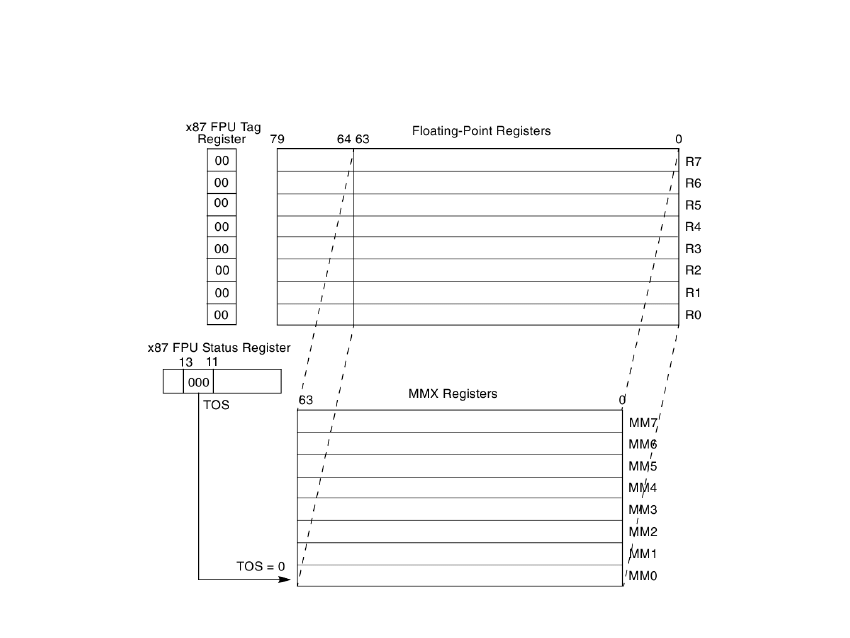

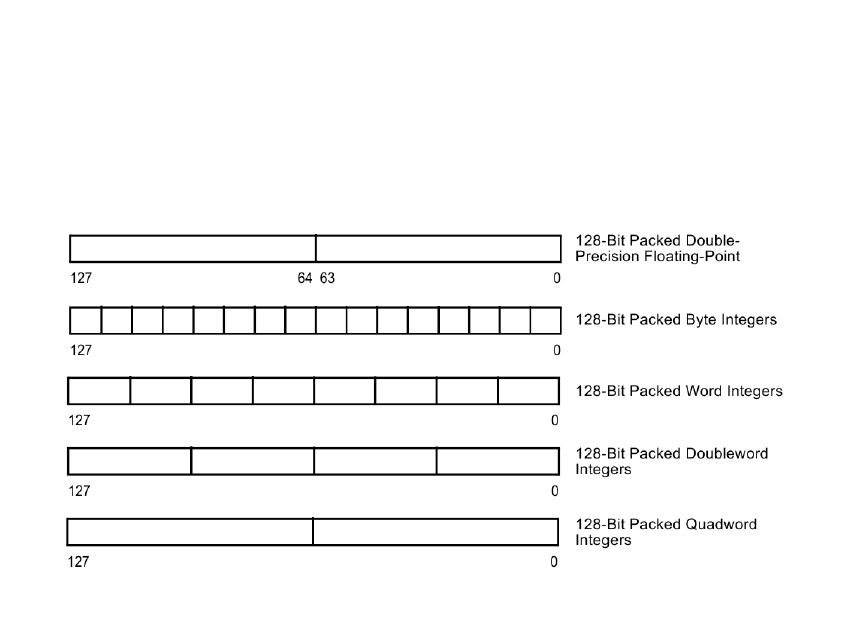

+ osiem 64 bitowych rejestrów (mm0, ... mm7)

3 zajmują wspólny obszar z rejestrami koprocesora arytmetycznego (mantysa)

· równoczesne obliczenia MMX i zmiennoprzecinkowe są niemożliwe

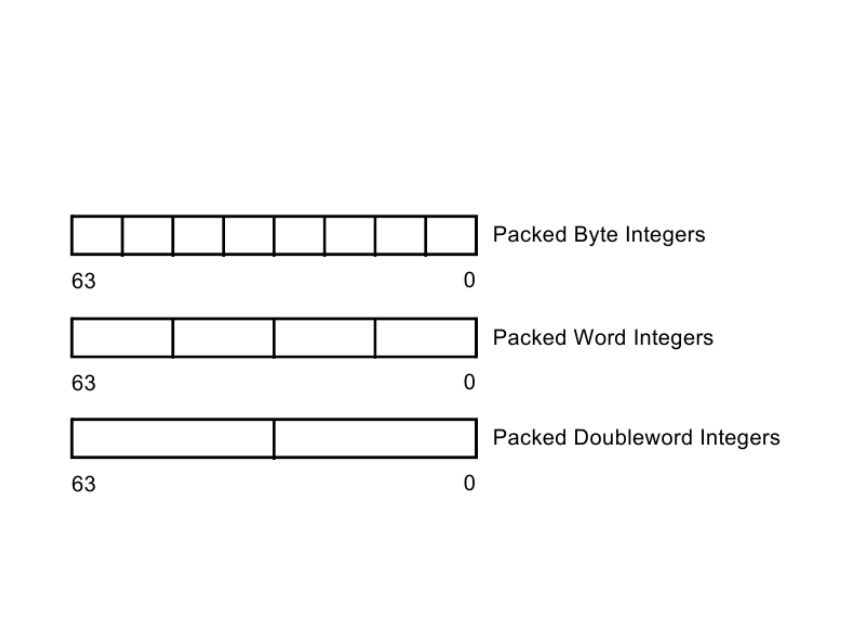

3 dostępne rejestry 8 × 8 bitów, 4 × 16 bitów, 2 × 32 bity

+ operacje na wektorach danych - istnieje mozliwość przy użyciu jednego rozkazu wykonania

jednocześnie 8/4/2 operacji na 8/4/2 32/16/8 bitowych rejestrach

51

§ Mapping of MMX Registers to Floating-Point Registers

52

§ Data Types Introduced with the MMX Technology

53

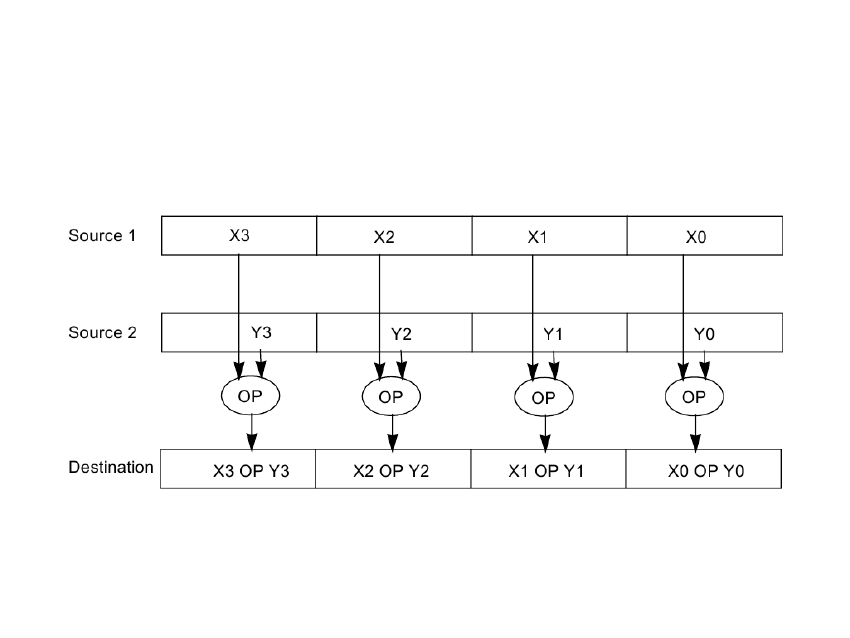

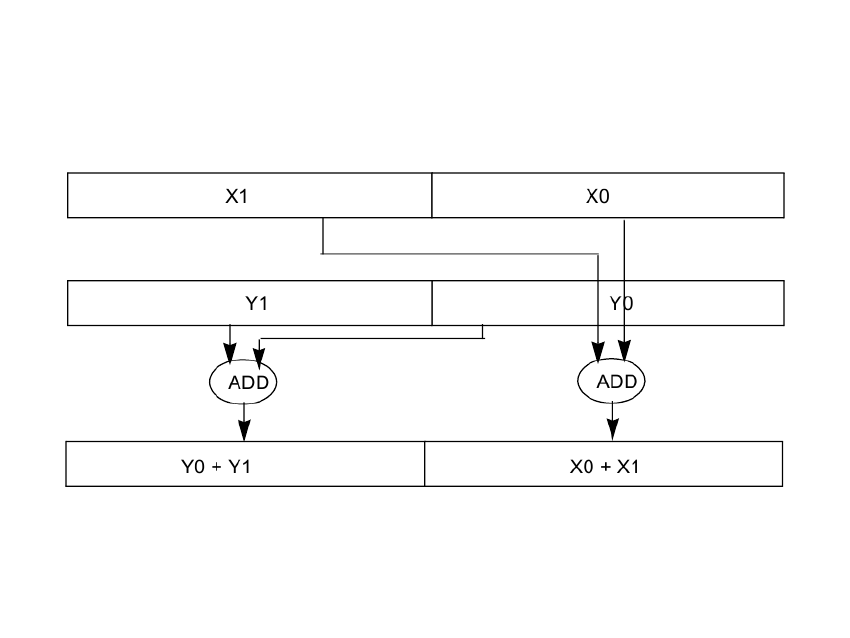

§ SIMD Execution Model

54

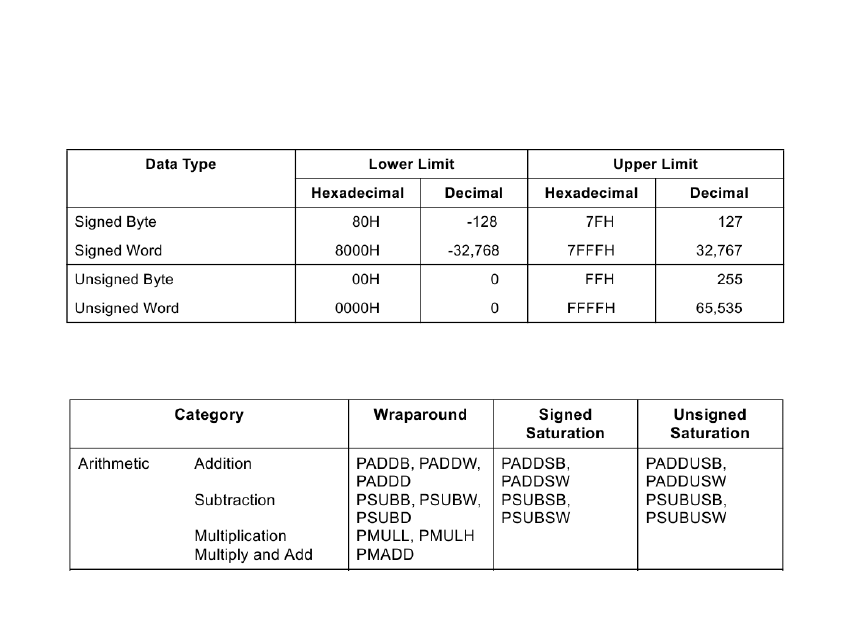

§ Data Range Limits for Saturation

§ MMX Arithmetic Instruction Set Summary

55

SSE

SSE - Streaming SIMD Extentension

56

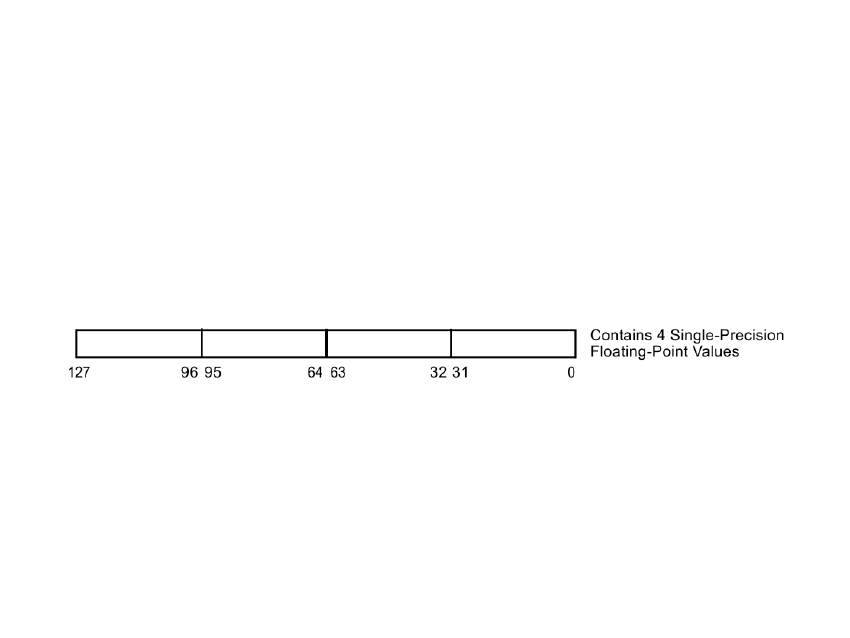

§ 128-Bit Packed Single-Precision Floating-Point Data Type

57

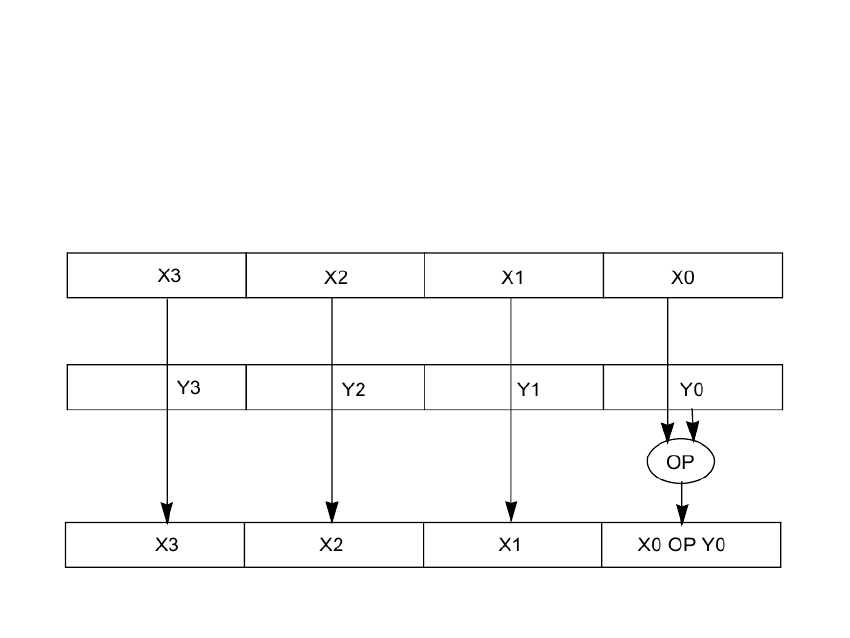

§ Packed Single-Precision Floating-Point Operation

58

§ Scalar Single-Precision Floating-Point Operation

59

SSE 2

60

SSE 3

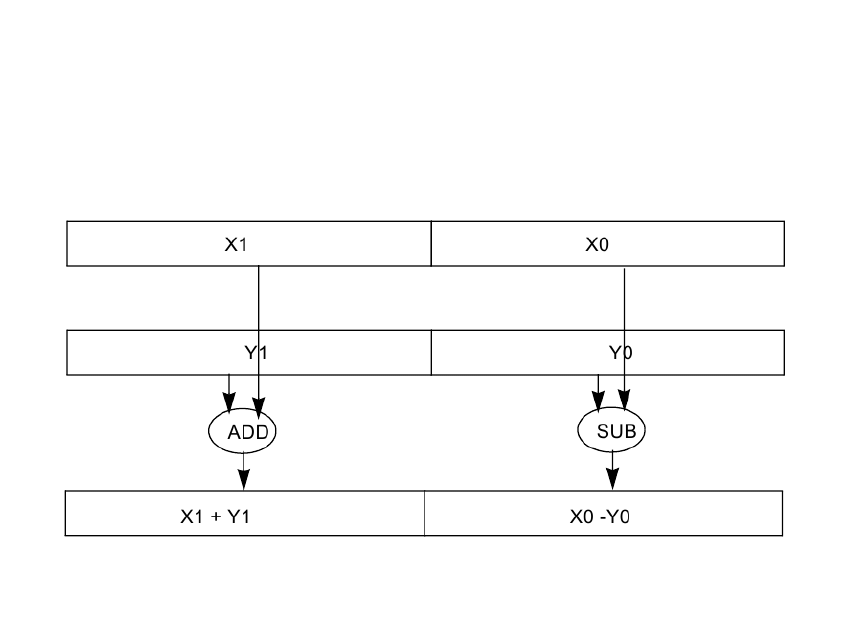

§ Asymmetric Processing in ADDSUBPD

61

§ Horizontal Data Movement in HADDPD

62

Wyszukiwarka

Podobne podstrony:

PRZEGLAD PROCESOROW RODZINY x86 FIRMY AMDd

20 Charakterystyka rodziny, szkoły, miejsca pracy, państwa ze względu na dystans władzy

20 glownych rodzinid 21352 Nieznany

Kodeks Rodzinny I Opiekunczy 20 Nieznany

Prawo rodzinne, prawo rodzinne i opiekuńcze 20.12.2008

Księga 1. Proces, ART 505(1) KPC, Uchwała z dnia 20 listopada 2003 r

MOJA RODZINA NA TLE PRZEOBRAŻEŃ DEMOGRAFICZNYCH, Procesy ludnościowe

Procesy wykład 20 maja, Zarządzanie Inwestycjami i Nieruchomościami UWM, Zarządzanie procesami

20 Gospodarka sciekami i osadami pochodzacymi z procesow o

FRANCUSKI słówka 20.04.2012 relacje międzyludzkie, rodzina

ISTOTA PODEJZCIA PROCESOWEGO 20 Nieznany

20 rola i zadania służb społecznych ds. p omocy dziecku i rodzinie - perspektywa europejska, socjol

ZAGADNIENIA TEORETYCZNE DO SAMODZIELNEGO PRZYGOTOWANIA NA KOLOKWIUM 20, uniwersytet warmińsko-mazurs

Rodzina w procesie rehabilitacji dziecka z mózgowym porażeniem dziecięcym. Typy postaw rodzicielskic

Pozew o przyczynianie się do zaspokajania potrzeb rodziny, Pisma procesowe - wzory

Przebieg procesu dydaktycznego w pierwszym etapie edukacji k, wrzut na chomika listopad, Informatyka

20.a powtórka I, Prawo karne procesowe

więcej podobnych podstron