Laboratorium 5a

Układy SERDES

SERDES (serialiser-deserializer) to rodzina technik przetwarzania szeregowo-równoległego i

równoległo-szeregowego. Zawsze oparte są one o rejestry przesuwne i systemy wykrywające

moment, gdy można wprowadzić lub pobrać nową porcję danych z/do rejestru równoległego.

W najprostszym (i nieco zawodnym) wariancie to wykrywanie może być oparte o zliczanie

bitów płynących w części szeregowej (czyli zliczanie cykli zegara). A zatem licznik, rejestr

przesuwny i zatrzaskujący się rejestr równoległy, odpowiednio połączone, tworzą

deserializer, czyli układ pobierający dane z wejścia szeregowego i przechowujący je w

docelowym rejestrze równoległym. Analogicznie powstaje układ wysyłający dane z rejestru

równoległego, przez rejestr przesuwny, na linię szeregową, czyli serializer.

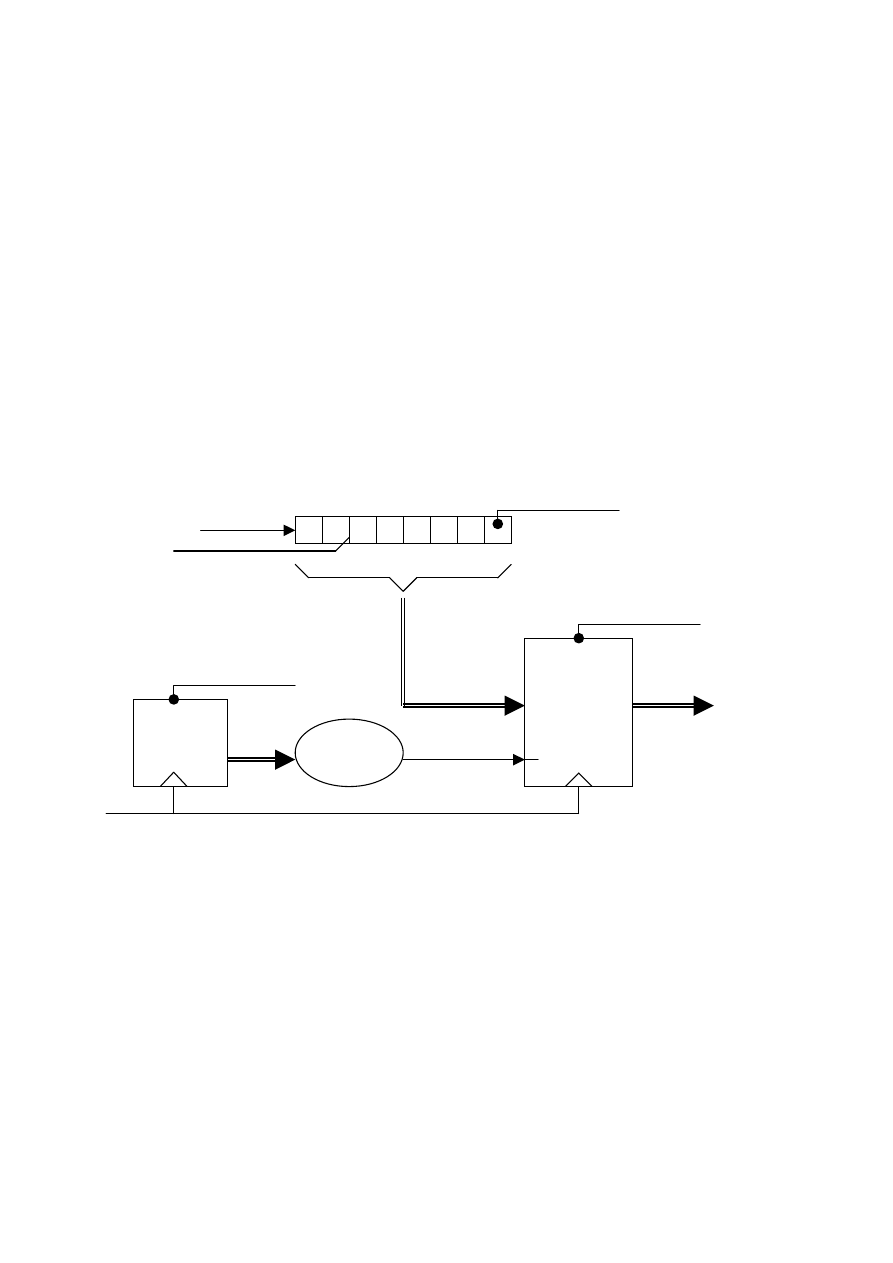

Układ równoległo–szeregowy poznaliśmy na poprzednich zajęciach. Schemat układu

szeregowo-równoległego przedstawiono poniżej.

Rys. 2. Układ szeregowo-równoległy (deserializer)

Zadania do wykonania

1. Zakodować i zweryfikować 8-bitowy układ szeregowo-równoległy.

2. Przeprowadzić wspólną symulację obydwu układów, przy założeniu że mamy

równoległo-szeregowy nadajnik, dalej łącze szeregowe i szeregowo-równoległy

odbiornik. Sprawdzić integralność danych na wyjściu systemu.

3. Dla pasjonatów. Zmodyfikować układ szeregowo-równoległy tak, by rozpoznawał w

rejestrze przesuwnym znacznik (np. ”01111110” czyli 7E, znany z ramek HDLC). Po

wykryciu znacznika licznik jest zerowany i od tego momentu jego stan wskazuje na

numer bitu wchodzącego właśnie do rejestru przesuwnego. Dzięki temu można ustalić

kiedy kompletny bajt jest gotowy do odebrania w rejestrze przesuwnym i w

konsekwencji utrzymać jaką-taką integralność struktury transmitowanych danych.

szeregowe

wej

ś

cie

licznik

0..7

en

=”000”

?

clk

nreset

równoległe

wyj

ś

cie

rejestr przesuwny

clk

nreset

nreset

Wyszukiwarka

Podobne podstrony:

Laboratorium 2 Uklady rownan

2 Instrukcja do laboratorium układy sekwencyjne

Laboratorium06 UkładySekwencyjneAutomatyStanów

Tranzystor bipolarny-gac, Szkoła, Politechnika 1- 5 sem, SEM IV, Elektronika i Energoelektronika. La

multiplekserPP, Polibuda, IV semestr, SEM IV, Elektronika i Energoelektronika. Laboratorium, 10. Ukł

Projekt do przedmiotu Układy Elektroniczne, Wzm Oper- lagarytmujący, Wyk: Paweł Góralski

Układy logiczne cz.2, Laboratorium układów elektronicznych

Elektronika- Układy polaryzacji i stabilizacji punktu pracy tranzystorów1.DOC, LABORATORIUM Z ELEKTR

template, Studia, Urządzenia i Układy Automatyki - laboratorium

uklady czasowe, Laboratorium Miernictwa Elektrycznego

układy impulsowe, Laboratorium, Elektronika

Tranzystor Bipolarny - Moje, Szkoła, Politechnika 1- 5 sem, SEM IV, Elektronika i Energoelektronika.

multiplekser, Polibuda, IV semestr, SEM IV, Elektronika i Energoelektronika. Laboratorium, 10. Układ

więcej podobnych podstron