Laboratorium

6

Temat: Układy sekwencyjne, automaty stanów.

1. Układ sekwencyjny - układ, w którym stan wyjść zależy od aktualnego stanu oraz od stanów

wejść poprzedzających aktualny stan

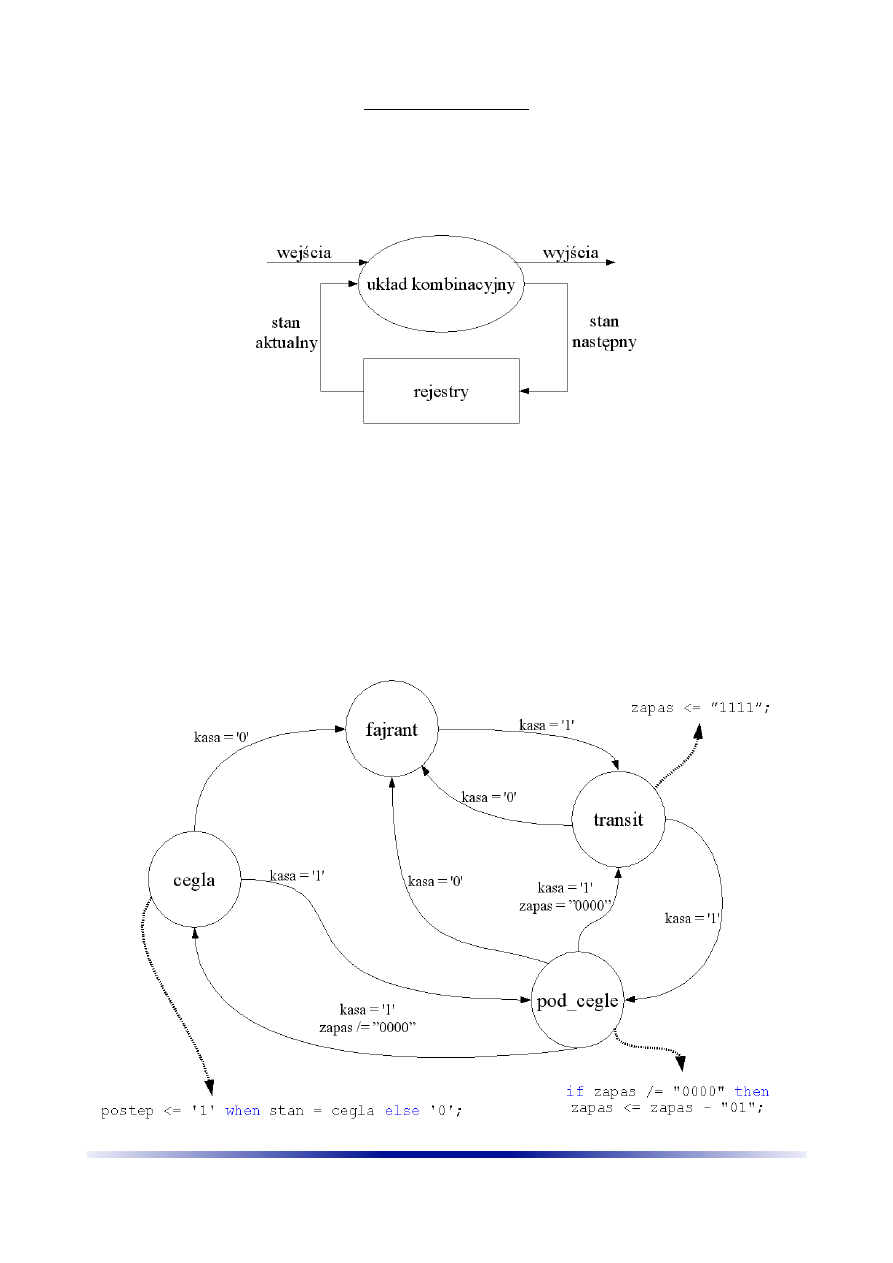

2. Ogólny schemat systemu sekwencyjnego

3. Przykładowy automat stanów: „budowa”

a) wejścia i wyjście układu:

clk, reset – wejścia: taktujące (zegarowe) i zerujące

kasa – wejście (budowa rusza gdy są fundusze, gdy brak kasy to fajrant)

postęp – wyjście ('1' gdy cegły są układane – stan: cegla, '0' w innych stanach)

b) stany automatu:

fajrant – stan spoczynkowy (jak sama nazwa wskazuje ;-) )

transit – dostarczenie cegieł na budowę (uzupełnienie zapasu: zapas<=”1111”)

pod_cegłę – „podaj cegłę” (zmniejszenie zapasu cegieł o 1)

cegla – budowanie muru (tu: postęp <= '1')

c) graf stanów budowy

Projektowanie układów VLSI

© 2005 Copyright by Tomasz Fałat

d) realizacja automatu w języku VHDL (fragmenty)

entity:

architecture:

4. Zadania do realizacji:

a) uzupełnić stany automatu według grafu (...), wykonać symulację

Projektowanie układów VLSI

© 2005 Copyright by Tomasz Fałat

port

( clk,reset

:

in

std_logic;

-- wejścia: zegarowe i zerujące

kasa

:

in

std_logic;

-- wejście - stan funduszy

postep

:

out

std_logic);

-- wyjście

type

STANY

is

(fajrant,transit,pod_cegle,cegla);

--deklaracja typu: STANY (typ

wyliczeniowy, możliwe wartości to: fajrant,transit,pod_cegle,cegla)

signal

stan,stan_nast : STANY;

-- sygnały: stan i stan_nast typu STANY;

signal

zapas :std_logic_vector(3

downto

0);

-- sygnał: zapas (ilość cegieł w mag.)

begin

reg:

process

(clk,reset)

begin

if

(reset='1')

then

stan <=fajrant;

elsif

(clk'Event

and

clk='1')

then

stan<=stan_nast;

end

if

;

end

process

reg;

komb:

process

(stan,kasa,zapas)

begin

stan_nast<= stan;

case

stan

is

when

fajrant=>

if

(kasa='1')

then

stan_nast<= transit;

end

if

;

when

transit=>

...

end

case

;

end

process

komb;

wynik:

process

(clk,reset)

begin

if

reset ='1'

then

zapas <= "0000";

elsif

(clk'event

and

clk='1')

then

if

(stan=pod_cegle

AND

zapas /="0000")

then

zapas<=zapas-"01";

elsif

(stan=transit)

then

zapas<="1111";

end

if

;

end

if

;

end

process

wynik;

postep <= '1'

when

stan = cegla

else

'0';

Wyszukiwarka

Podobne podstrony:

Laboratorium 2 Uklady rownan

2 Instrukcja do laboratorium układy sekwencyjne

Laboratorium05B UkładySERDE

Tranzystor bipolarny-gac, Szkoła, Politechnika 1- 5 sem, SEM IV, Elektronika i Energoelektronika. La

multiplekserPP, Polibuda, IV semestr, SEM IV, Elektronika i Energoelektronika. Laboratorium, 10. Ukł

Projekt do przedmiotu Układy Elektroniczne, Wzm Oper- lagarytmujący, Wyk: Paweł Góralski

Układy logiczne cz.2, Laboratorium układów elektronicznych

Elektronika- Układy polaryzacji i stabilizacji punktu pracy tranzystorów1.DOC, LABORATORIUM Z ELEKTR

template, Studia, Urządzenia i Układy Automatyki - laboratorium

uklady czasowe, Laboratorium Miernictwa Elektrycznego

układy impulsowe, Laboratorium, Elektronika

Tranzystor Bipolarny - Moje, Szkoła, Politechnika 1- 5 sem, SEM IV, Elektronika i Energoelektronika.

multiplekser, Polibuda, IV semestr, SEM IV, Elektronika i Energoelektronika. Laboratorium, 10. Układ

więcej podobnych podstron