ARCHITEKTURA PROCESORA

Listy rozkazów: własności i funkcje

Elementy rozkazu maszynowego

!"

Kod operacji. Określa operację, jaka ma być przeprowadzona (na

przykład, ADD);

!"

Odniesienie do argumentów źródłowych. Operacja może

obejmować jeden lub wiele argumentów źródłowych, są one danymi

wejściowymi operacji;

!"

Odniesienie do wyniku. Operacja może prowadzić do powstania

wyniku;

!"

Odniesienie do następnego rozkazu. Określa, skąd procesor ma

pobierać następny rozkaz po zakończeniu wykonania bieżącego

rozkazu.

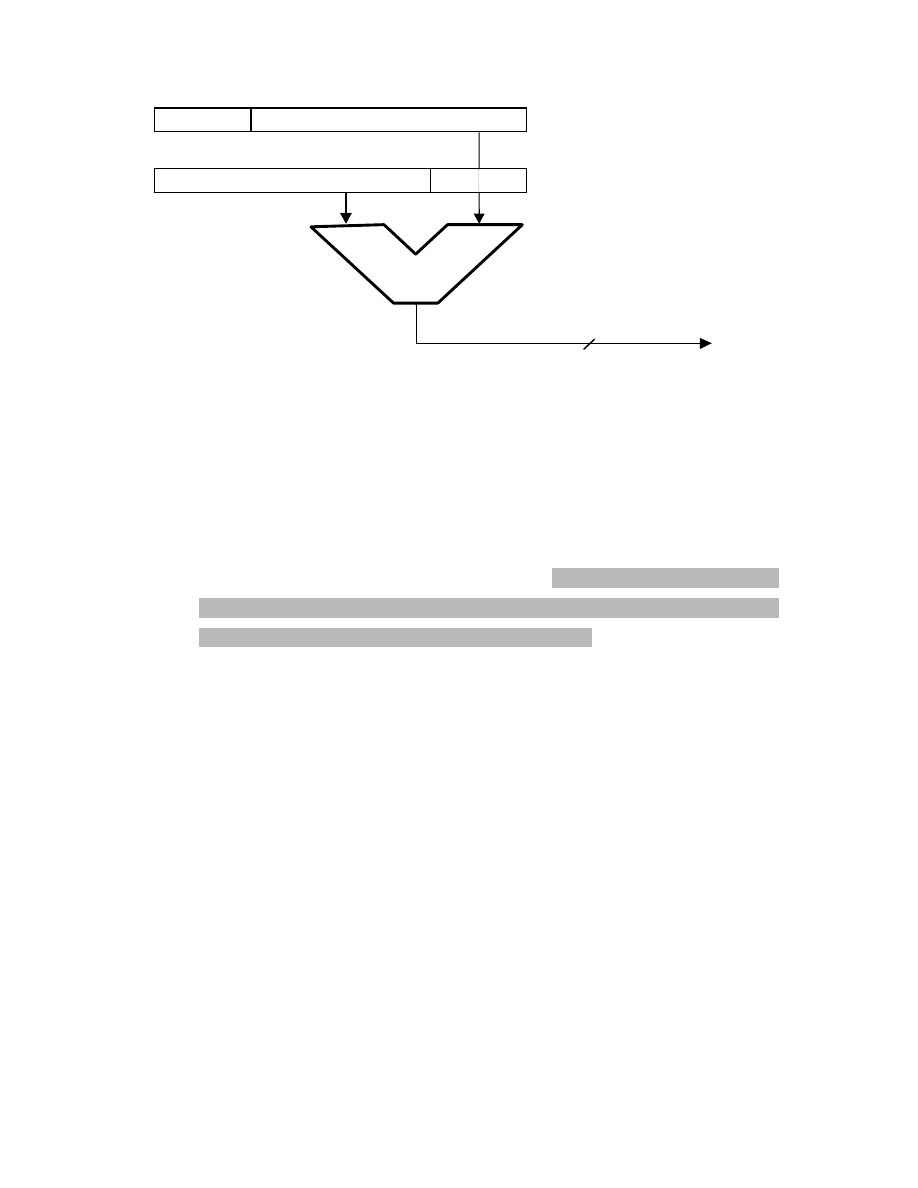

Reprezentacja rozkazu

Rozkaz jest reprezentowany wewnątrz komputera jako ciąg bitów.

Rozkaz dzielony jest na pola odpowiadające elementom składowym

rozkazu.

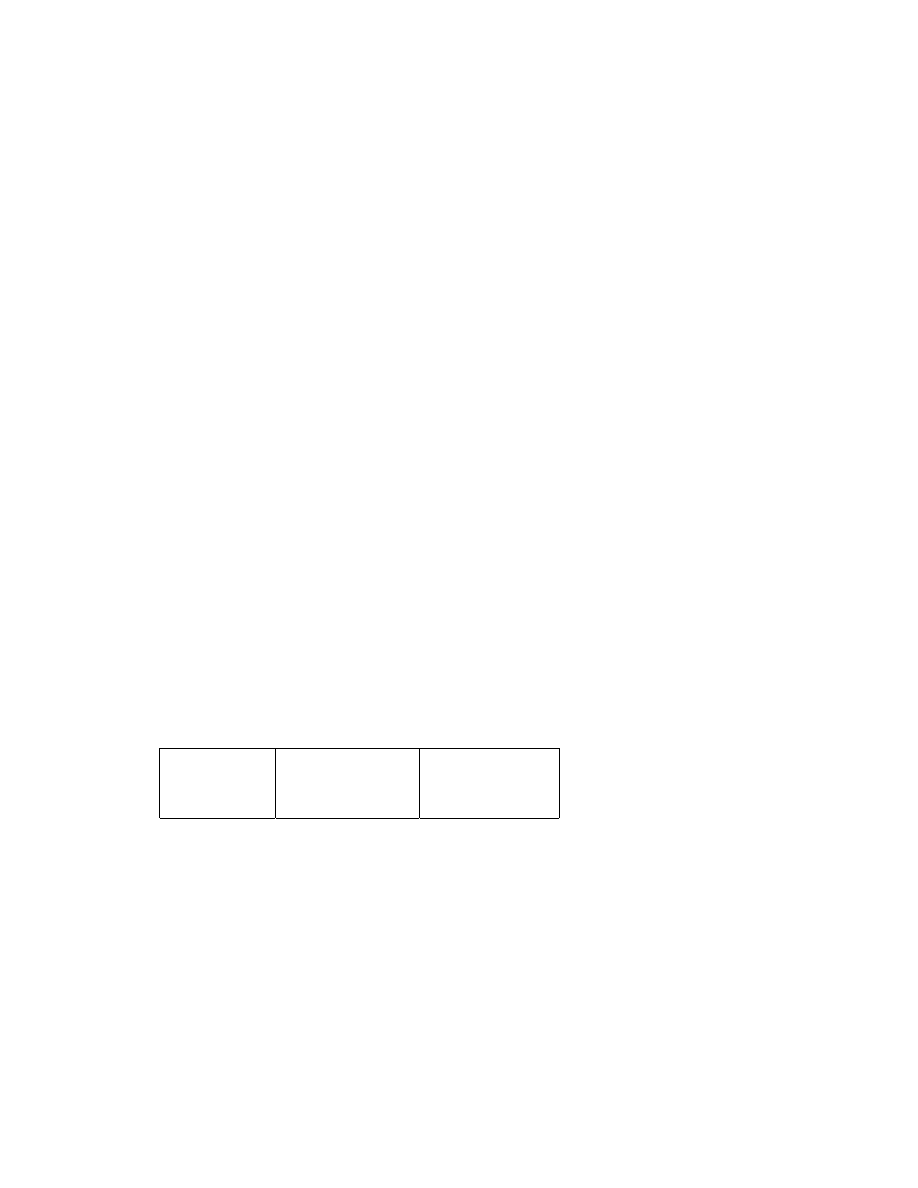

Prosty format rozkazu

Formaty rozkazów:

!"

sztywne

!"

swobodne

Rodzaje rozkazów:

!"

rozkazy arytmetyczne i logiczne (przetwarzanie danych),

!"

rozkazy pamięciowe (przechowywanie danych),

!"

rozkazy wejścia-wyjścia (przesyłanie danych),

Kod

operacji

Odniesienie do

argumentu

Odniesienie

do argumentu

!"

rozkazy testowania i rozgałęzienia (sterowanie).

Liczba adresów:

!"

rozkazy bezadresowe (działające na stosie),

!"

rozkazy jednoadresowe,

!"

rozkazy dwu- lub trzyadresowe.

Adres następnego rozkazu jest domyślny (uzyskiwany z licznika

programu).

Projektowanie listy rozkazów

Liczba adresów w rozkazie jest podstawową decyzją projektową.

Do najważniejszych problemów projektowania listy rozkazów należą:

Repertuar operacji

;

Rodzaje danych;

Format rozkazu

. Długość rozkazu, liczba adresów, rozmiary pól itp.;

Rejestry

. Liczba rejestrów procesora oraz ich zastosowanie.

Adresowanie

. Tryb lub tryby, w których są specyfikowane adresy

argumentów.

Rodzaje argumentów:

!"

adresy,

!"

liczby (całkowite lub stałopozycyjne, zmiennopozycyjne,

dziesiętne),

!"

znaki,

!"

dane logiczne (Prawda, Fałsz).

Rodzaje danych Pentium:

!"

Ogólne. Lokacje o dowolnej zawartości binarnej obejmujące bajt,

słowo (16 bitów), podwójne słowo (32 bity) lub poczwórne słowo.

!"

Całkowite. Wartości binarne ze znakiem, zawarte w bajcie, słowie lub

podwójnym słowie, w reprezentacji uzupełnienia do dwóch.

!"

Porządkowe. Liczby całkowite bez znaku (bajt, słowo, podwójne

słowo).

!"

Liczba dziesiętna nieupakowana BCD.

!"

Liczba dziesiętna upakowana BCD.

!"

Wskaźnik bliski. 32-bitowy adres efektywny, reprezentujący

przesunięcie wewnątrz segmentu.

!"

Łańcuch bajtów. Sekwencja sąsiadujących bajtów (od zera do 2

32

-1

bajtów).

!"

Zmiennopozycyjne:

pojedynczej precyzji – 32-bitowe słowo, mantysa 24-bity, cecha w

systemie z przesuniętym wykładnikiem;

podwójnej precyzji – 64-bity, mantysa 52-bity;

precyzja rozszerzona – 80-bitów, mantysa 64 bitowa.

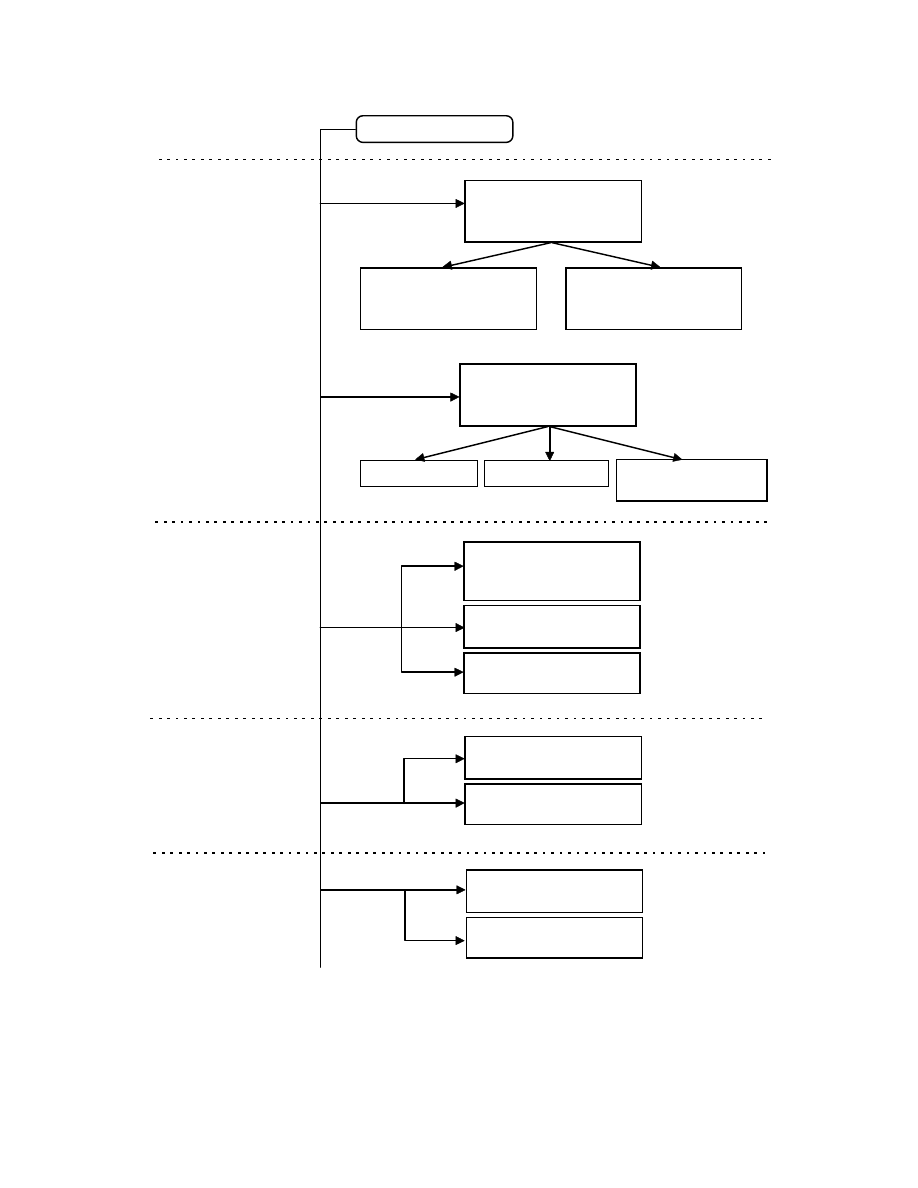

Organizacja procesora

Organizacja rejestrów

Rejestry w procesorze można podzielić na dwie grupy:

!"

Rejestry widzialne dla użytkownika;

!"

Rejestry sterowania i stanu.

Rejestry widzialne dla użytkownika:

!"

ogólnego przeznaczenia (ang. general purpose),

!"

danych,

!"

adresowe (wskaźniki segmentu, rejestry indeksowe, wskaźnik stosu).

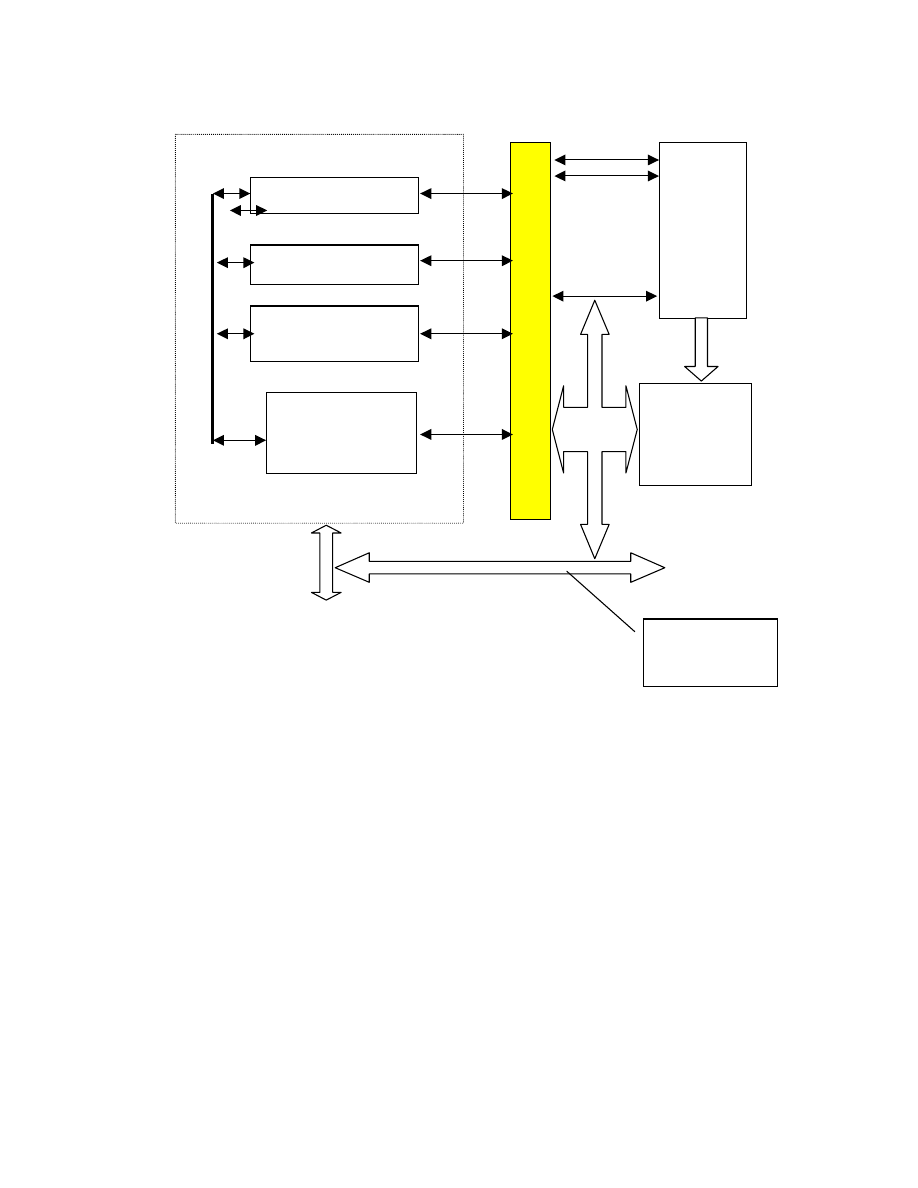

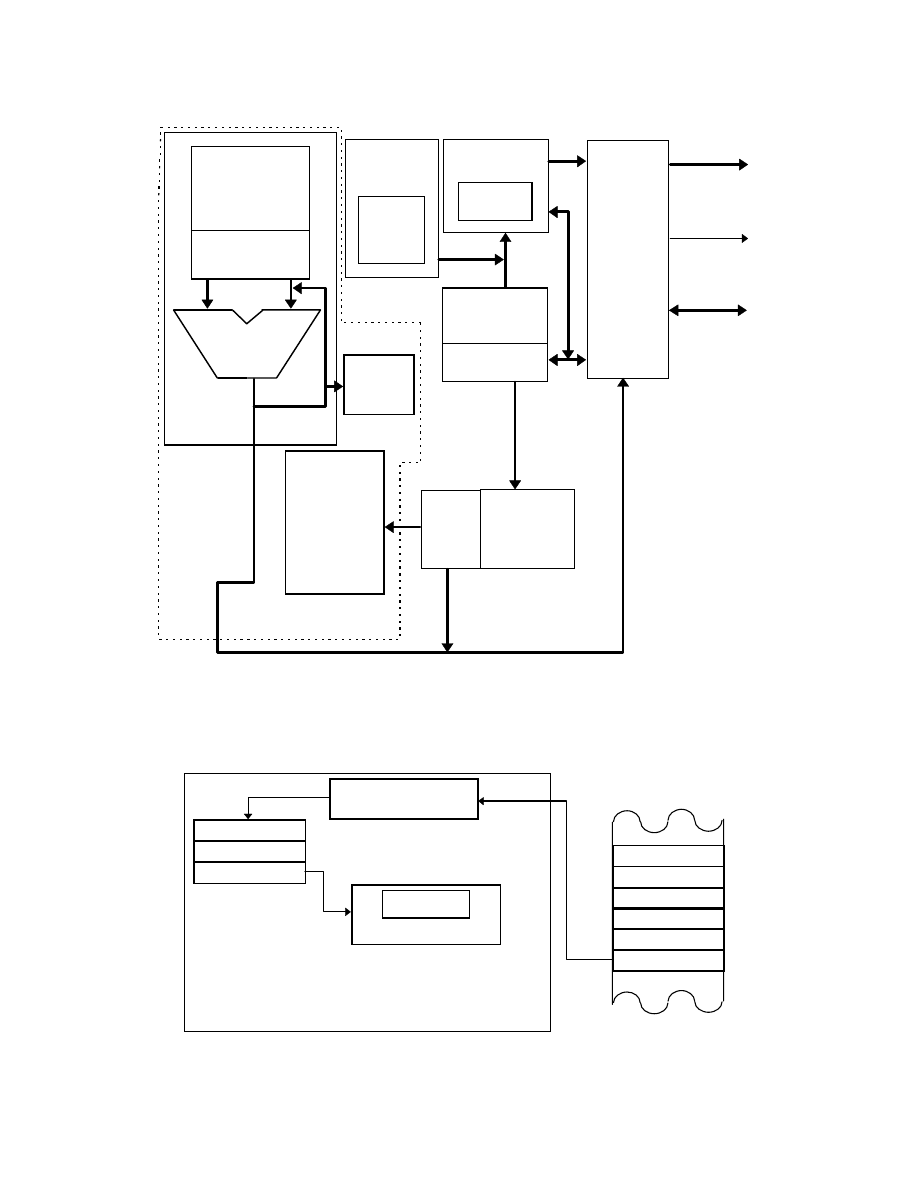

Znaczniki stanu

Układ przesuwny

Układ

dopełniania

Układy

logiczne i

arytmetyczne

Wew

n

ętrz

n

a

m

ag

is

tral

a

p

ro

ce

so

ra

Jednostka arytmet. - logiczna

Rejestry

Jednostka

sterująca

Ścieżki

sterowania

Rejestry sterowania i stanu

!"

Licznik programu (PC).

!"

Rejestr rozkazu (IR).

!"

Rejestr adresowy pamięci (MAR).

!"

Rejestr buforowy pamięci (MBR).

!"

Słowo stanu programu (ang. program status word – PSW).

W rejestrach PSW występują następujące pola (flagi):

Znak. Bit znaku ostatniej operacji arytmetycznej;

Zero. Flaga ustawiana, gdy wynik równy zeru;

Przeniesienie. Ustawiane, gdy wynikiem operacji jest przeniesienie do

kolejnego słowa (umożliwia realizacje wielokrotnej precyzji);

Przepełnienie. Nadmiar arytmetyczny.

Zezwolenie /blokowanie przerwania. Używane do obsługi przerwań.

Pułapka (ang. Trap).

Tryb procesora. Wskazuje , czy procesor pracuje w trybie nadzorcy,

czy użytkownika.

Wskaźnik do bloku sterowania procesem.

Wskaźnik tablicy stron. Dla systemu pamięci wirtualnej.

itp.

Przykładowe organizacje rejestrów w mikroprocesorach

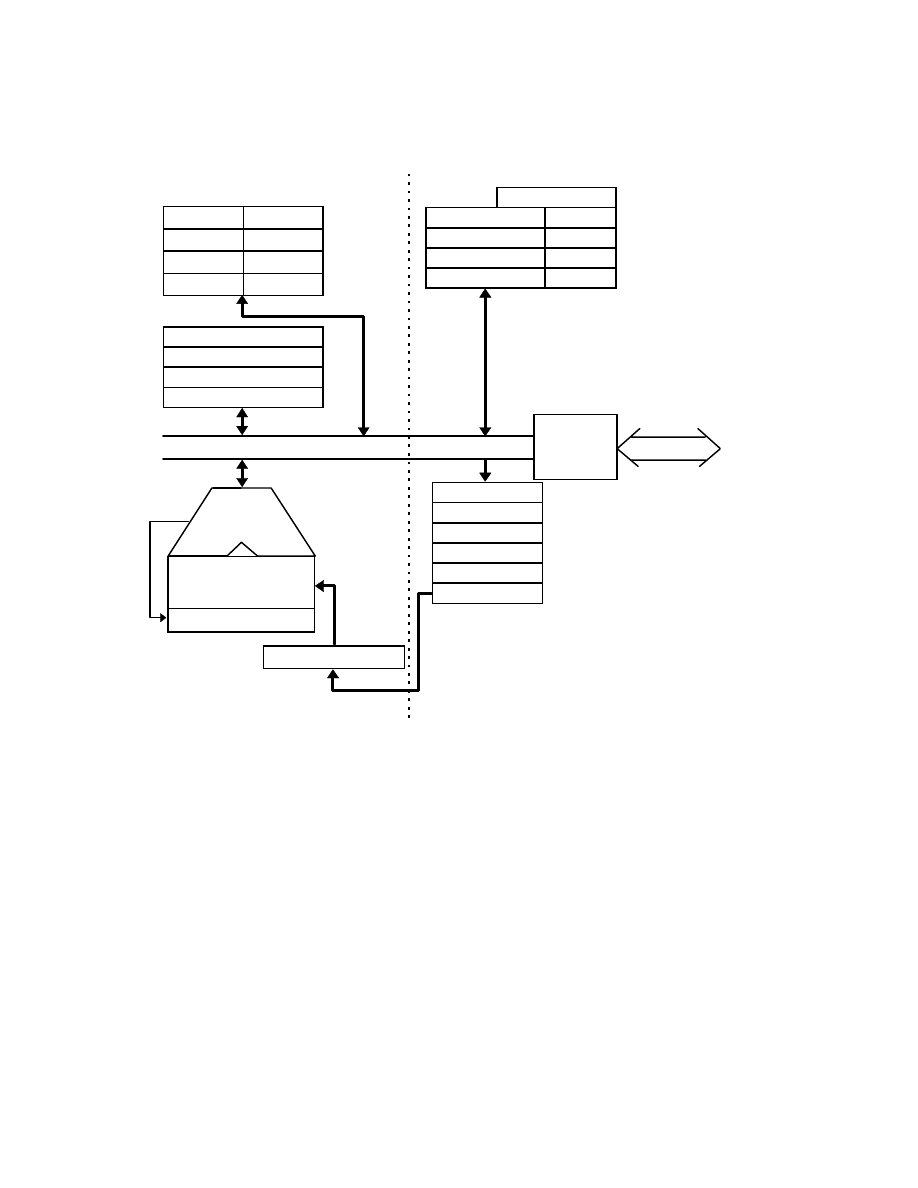

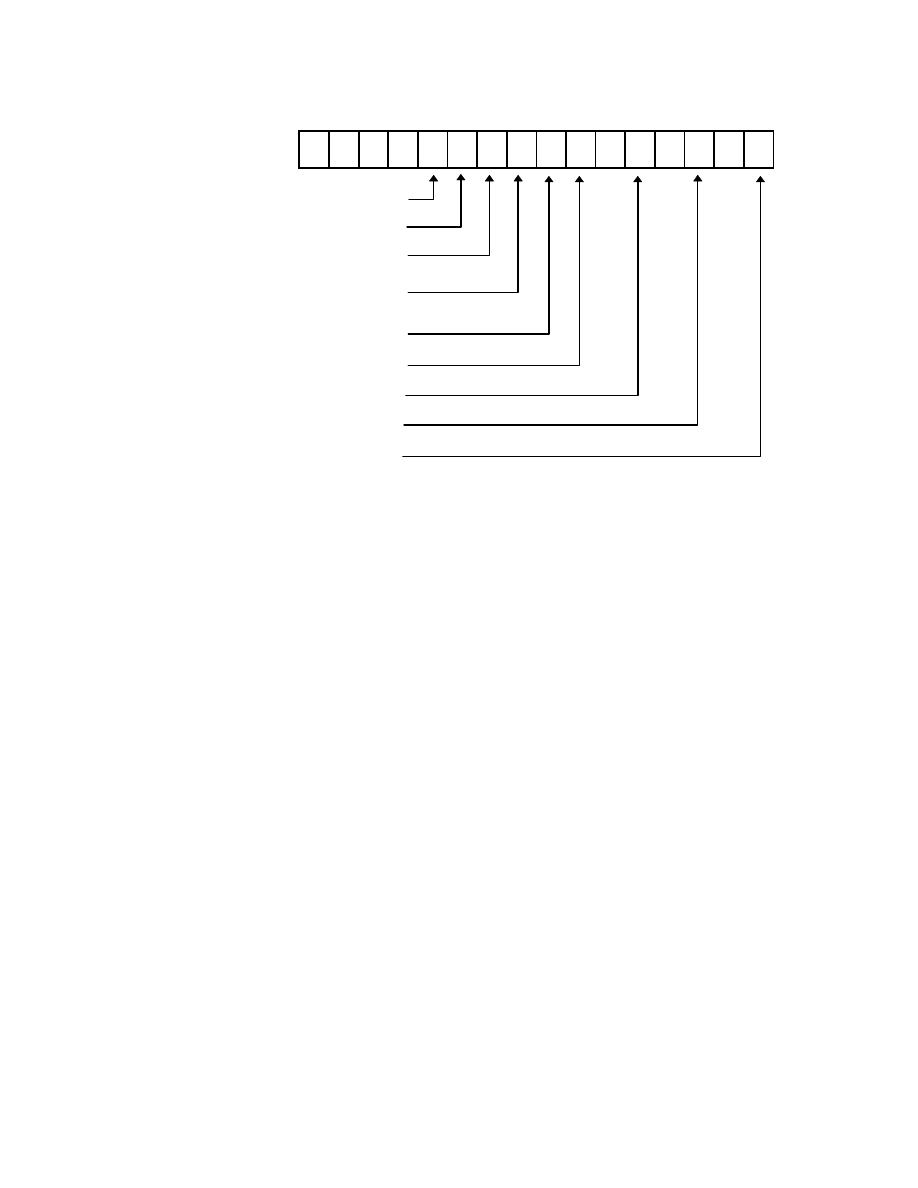

Architektura mikroprocesora 8086

AH

BL

BH

AL

CH

DL

DH

CL

SP

DI

SI

BP

CS

ES

SS

DS

0000

0000

0000

0000

PC

0

7

8

15

AX

BX

CX

DX

0

15

0

15

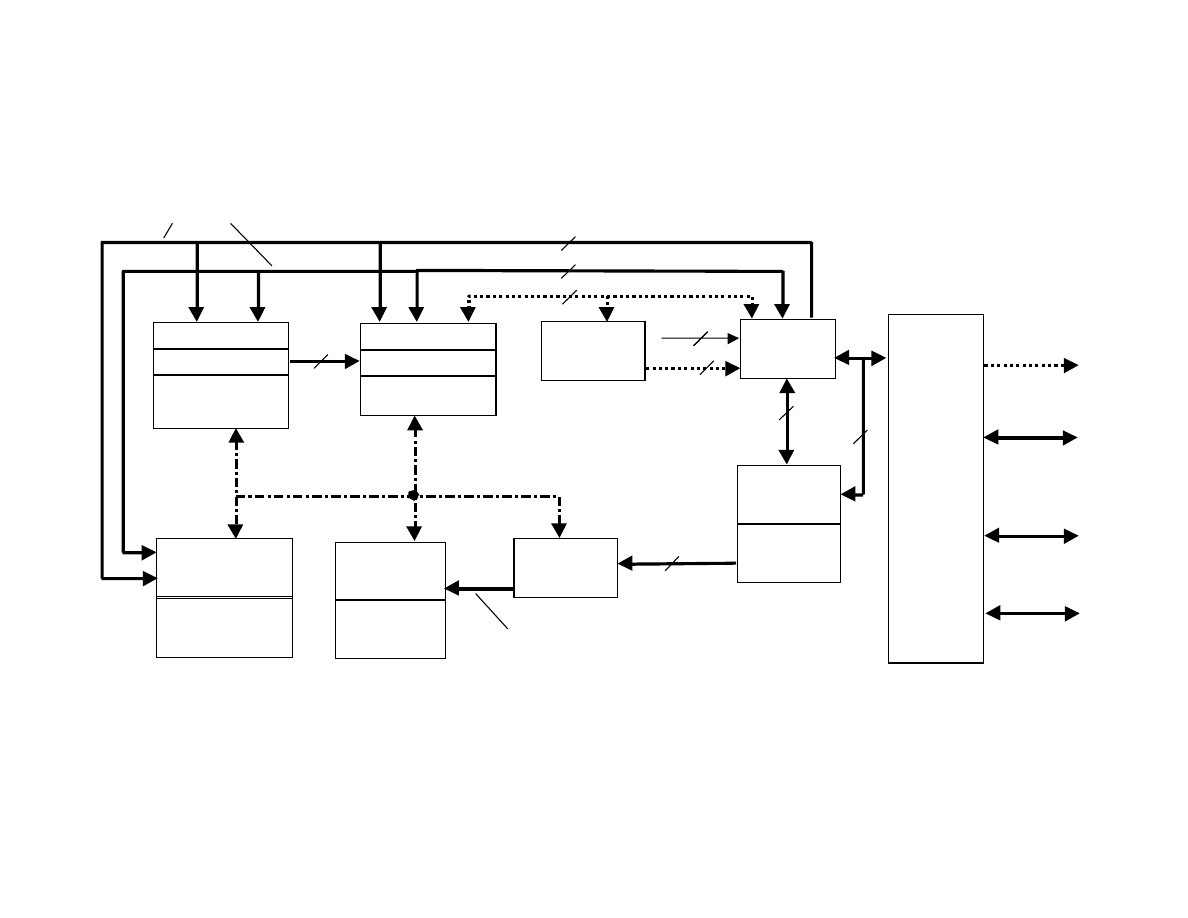

Magistrala wewnętrzna

Bufor

magistrali

zewnętrznej

6

3

4

5

2

1

Kolejka rozkazów

ALU

Jednostka sterująca

Rejestr znaczników

Rejestr rozkazów

Jednostka sterująca

BIU

Jednostka wykonawcza

EU

0

15

Rejestry mikroprocesora 8086

Mikroprocesor 8086 zawiera 14 szesnastobitowych rejestrów

widocznych dla programisty:

1. Rejestry ogólnego przeznaczenia, służące głównie do przechowywania wyników

pośrednich, ich zawartości mogą być argumentami większości rozkazów:

AX - akumulator; niektóre rozkazy dotyczące tego rejestru wykonują się szybciej

niż na innych rejestrach ogólnych lub są o 1 bajt krótsze.

BX - rejestr bazowy; dodatkowo może być wykorzystany do tzw. adresowania

bazowego - zawiera wówczas przesunięcie (OFFSET) argumentu.

CX - rejestr zliczający lub licznikowy; może być wykorzystywany w rozkazach jako

licznik wykonań - jest wówczas zmniejszany o 1 za każdym wykonaniem i

jego zawartość podlega badaniu, czy nie uległa wyzerowaniu.

DX - rejestr danych, jako jedyny może być wykorzystywany do adresowania

obiektów w przestrzeni adresowej wej/wyj (portów) w rozkazach wej/wyj, a

także w rozkazach o argumentach lub wynikach długości większej niż jedno

słowo (np. rozkazy mnożenia lub dzielenia).

Szesnastobitowe rejestry ogólnego przeznaczenia mogą być interpretowane

jako pary rejestrów ośmiobitowych stanowiących mniej i bardziej znaczącą część

rejestru szesnastobitowego. Identyfikator rejestru stanowiącego mniej znaczącą

część rejestru ogólnego kończy się na L, zaś identyfikator rejestru stanowiącego

bardziej znaczącą część rejestru ogólnego kończy się na H. Argumentami

rozkazów mogą być zarówno rejestry ogólne jako całość, jak i ich ośmiobitowe

części.

0

7

8

15

0

15

IP

SP

BP

SI

Rejestry adresowe

Wskaźnik rozkazu

Wskaźnik wierzchołka stosu

Wskaźnik bazy

Indeks źródła

DI

Indeks celu

0

15

CS

SS

DS

ES

Rejestry segmentowe

Segment kodu programu

Segment stosu

Segment danych

Segment dodatkowy

0

15

F

Rejestr znaczników (flag)

AH AX AL

BH BX BL

CH CX CL

DH DX DL

Rejestry ogólnego przeznaczenia

Akumulator

Rejestr bazowy

Rejestr zliczający

Rejestr danych

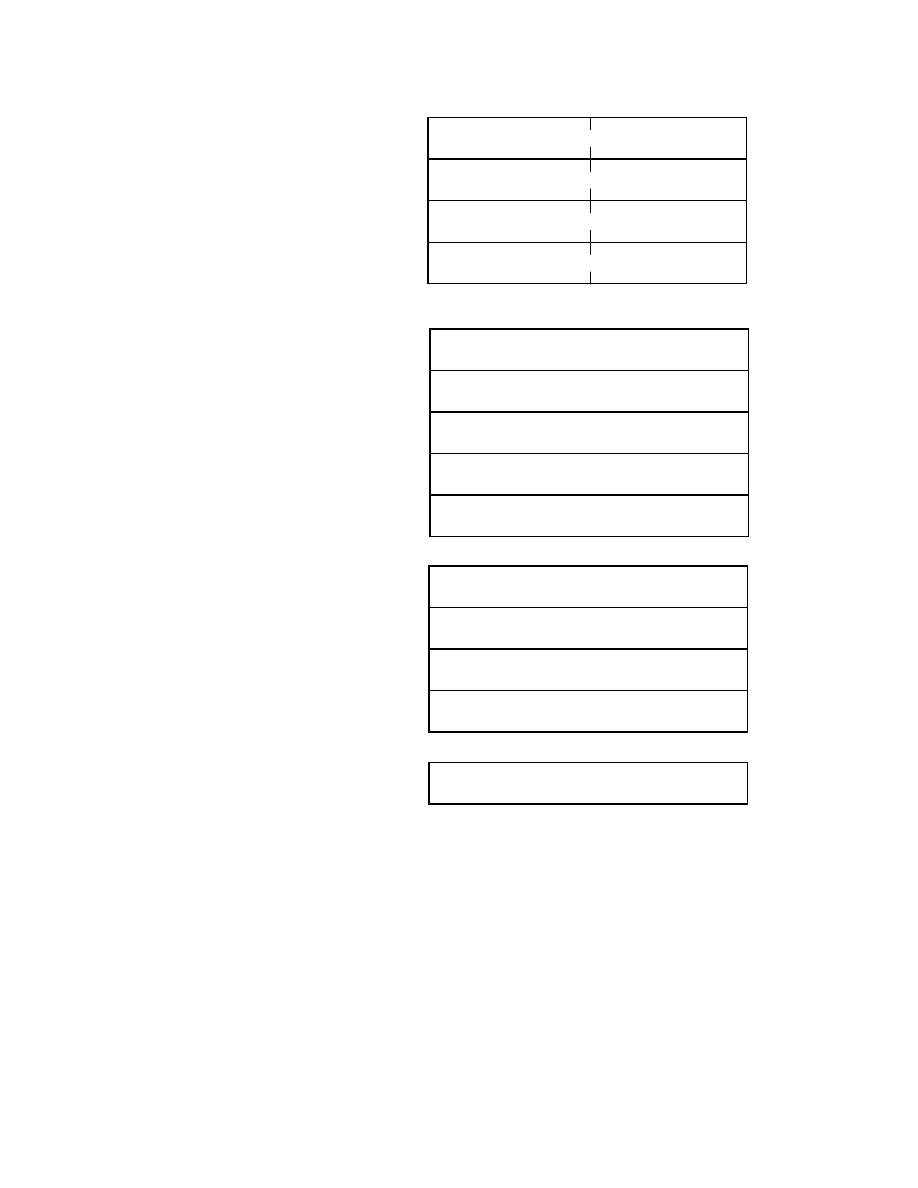

Rejestry mikroprocesora 8086

∑

Przemieszczenie

0 0 0 0

Segment

0 0 0 0

Adres efektywny

Adres bazowy segmentu

0

0

15

15

Adres fizyczny

20 bitowy

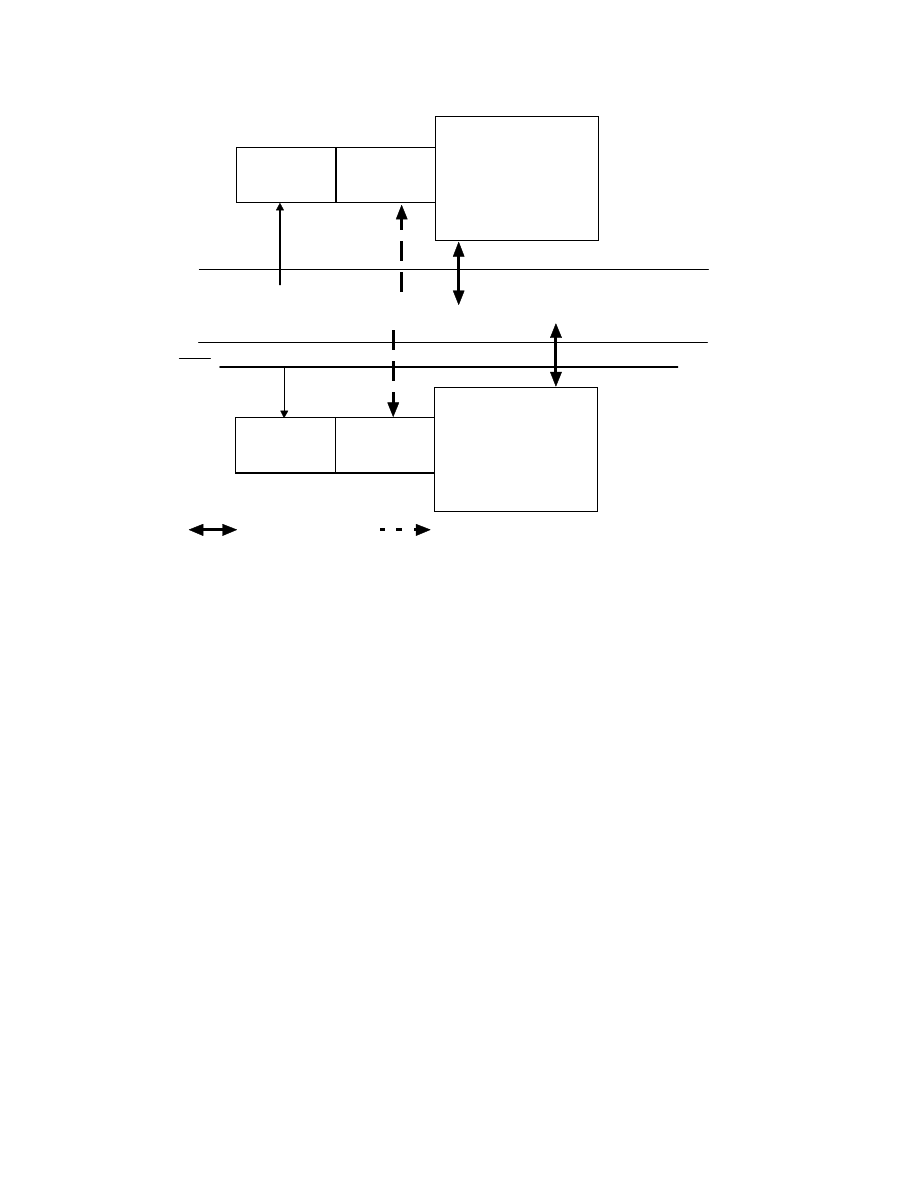

2. Rejestry adresowe, służące głównie do przechowywania adresów względnych

(OFFSET), chociaż mogą być też wykorzystywane jako rejestry robocze -

możliwości użycia ich zawartości jako argumentów rozkazów są tylko w niewielkim

stopniu ograniczone w porównaniu z rejestrami ogólnego przeznaczenia:

IP - wskaźnik rozkazu (ang. instruction pointer), zawiera zawsze adres względny

(względem początku segmentu określonego przez zawartość rejestru CS)

aktualnie pobieranego do wykonania rozkazu, rejestr ten stanowi z punktu

widzenia programisty (wraz z rejestrem CS) część licznika rozkazów;

rejestr IP nie może być zmieniany przez program.

SP - wskaźnik wierzchołka stosu; zwykle zawiera adres względny (względem

początku segmentu określonego przez zawartość rejestru SS) wierzchołek

stosu, tzn. adres ostatniego słowa odłożonego na stosie; w przypadku

pisania programów przeznaczonych do pracy pod kontrolą systemu

operacyjnego należy rejestrem SP posługiwać się ze szczególną

ostrożnością.

BP - rejestr wskaźnika bazy; zwykle zawiera adres względny (względem początku

segmentu określonego przez zawartość rejestru SS) parametrów odłożonych

na stosie (dla procedur w językach wysoko poziomowych); rejestr BP może

być wykorzystany także do innych celów.

SI - rejestr indeksu źródła (miejsca, z którego pobierane są dane w operacjach

przesyłania danych); zwykle zawiera adres danych względem początku

segmentu określonego zawartością rejestru DS; rejestr SI wykorzystywany

jest do tzw. adresowania indeksowego oraz w rozkazach łańcuchowych

(operacjach na ciągach znaków), może też być wykorzystany do innych

celów.

DI - rejestr indeksu celu; zwykle zawiera adres danych względem początku

segmentu określonego zawartością rejestru DS; rejestr DI wykorzystywany

jest do tzw. adresowania indeksowego oraz w rozkazach łańcuchowych - w

tym przypadku jednak zawiera adres względem początku segmentu

określonego zawartością rejestru ES, może też być wykorzystany do innych

celów.

3.

Rejestry segmentowe służą do przechowywania wartości (SEGMENT)

określających adresy początkowe segmentów przy odwołaniach do pamięci:

CS - rejestr segmentu kodu programu określa adres początku segmentu używany

w przypadku wszystkich dostępów do pamięci z adresowaniem względnym za

pomocą rejestru IP, tzn. pobierania rozkazów. Z punktu widzenia

programisty rejestr CS razem z rejestrem IP tworzy licznik rozkazów

mikroprocesora 8086 (CS:IP).

SS - rejestr segmentu stosu programu określa adres początku segmentu używany

w przypadku wszystkich dostępów do pamięci z adresowaniem względnym za

pomocą rejestru SP lub BP, jeśli zadano wykorzystanie tego rejestru, tzn. BP

specjalnym rozkazem.

DS - rejestr segmentu danych określa adres początku segmentu używany w

przypadku wszystkich dostępów do pamięci danych (np. za pomocą rejestrów

BX, SI, DI lub za pomocą adresu podanego bezpośrednio w rozkazie).

ES - rejestr segmentu danych określa adres początku segmentu używany w

przypadku wszystkich dostępów do pamięci danych w rozkazach

łańcuchowych - działania na ciągach adresowanych za pomocą rejestru DI.

Rejestry segmentowe mogą być argumentami wyłącznie rozkazów przesłania

MOV, PUSH i POP.

4. Rejestr znaczników F jest konstrukcją składającą się z szeregu jednobitowych

rejestrów określających stan procesora. Rejestr znaczników zawiera tzw. słowo

stanu. Słowo stanu ma postać jak na rys.

X

X

X

X OF DF IF TF

ZF

X

AF X

PF

X CF

SF

15 14 13 12 11 10

9

8

6

5

4

3

2

1

0

7

nadmiar

kierunek

maska przerwań

maska przerwań po każdym

rozkazie

wskaźnik ujemnego wyniku

wskaźnik wyniku zerowego

przeniesienie pomocnicze

wskaźnik parzystości

przeniesienie

Słowo stanu mikroprocesora 8086

Poszczególne bity rejestru wskaźnika dzielą się na dwie grupy:

1. Wskaźników określających sposób działania procesora:

TF - bit 8, powoduje (stan 1) przerwanie nr. 3, z jednoczesnym zgaszeniem TF, po

wykonaniu jednego rozkazu - wykorzystywany przez specjalistyczne

oprogramowanie uruchomieniowe;

IF - bit 9, zezwala (stan 1) na przyjmowanie przerwań zewnętrznych; wyzerowanie

tego bitu powoduje zablokowanie przyjmowania przerwań zewnętrznych, poza

tzw. przerwaniem niemaskowalnym (NMI);

DF - bit 10, określa czy zawartości rejestrów SI i DI w trakcie wykonywania

rozkazów łańcuchowych mają być zwiększane (DF=0), czy zmniejszane

(DF=1).

2. Wskaźników ustawianych w wyniku wykonywania różnych rozkazów:

CF - wskaźnik przeniesienia globalnego, zmieniany rozkazami arytmetycznymi i

przesunięć, zerowany rozkazami logicznymi;

OF - wskaźnik nadmiaru, zmieniany rozkazami arytmetycznymi i zerowany

rozkazami logicznymi; OF jest zmieniany również w rozkazach przesunięć,

których drugi argument jest równy 1;

Układ wyboru

banku pamięci

A0

Dekoder

adresów

A1...A19

1

Bank pamięci

zawierający mniej

znaczące bajty

D0...D7

Układ wyboru

banku pamięci

Dekoder

adresów

A1...A19

2

D0...D7

Bank pamięci

zawierający bardziej

znaczące bajty

Multipleksowana

szyna adresów i

danych

AD8...AD15

AD0...AD7

BHE

A1...A19

A1...A19

A0

Szyna danych

Szyna adresowa

Organizacja pamięci w systemie z mikroprocesorem 8086

SF - wskaźnik znaku (ujemnego wyniku), zmieniany rozkazami arytmetycznymi i logicznymi;

ZF - wskaźnik zera wyniku, zmieniany rozkazami arytmetycznymi i logicznymi;

PF - wskaźnik parzystej liczby jedynek w zapisie binarnym wyniku, zmieniany rozkazami arytmetycznymi i logicznymi;

AF - wskaźnik przeniesienia pomocniczego (z bitu 3 na 4) ustawiany na potrzeby rozkazów arytmetyki dziesiętnej.

Ste-

rowa-

nie

Sterowanie magistrali

S1, S0, COD/ INTA

LOCK, HLDA

Sumator

przemieszczenia

Sumator

adresów

fizycznych

Bazy

segmentów

Rozmiary

segmentów

Kontrola

ograniczeń

Blok

generacji

adresów

ALU

Blok

rejestrów

roboczych

Blok przetwarzania

Kolejka zdekodowanych

rozkazów

Dekoder

rozkazów

Blok

dekodera

Zatrzaskujące bufory adresów

Układ

wprowadzania

rozkazów

Interfejs

z układami

rozszerzającymi

(koprocesorami)

Bufory danych

6-bajtowa

kolejka

rozkazów

A23....A0

BHE,M / IO

PEACK

PEREQ

READY, HOLD

D15...D0

RESET

CLK

GND

U

CC

CAP

BUSY

ERROR

INTR

NMI

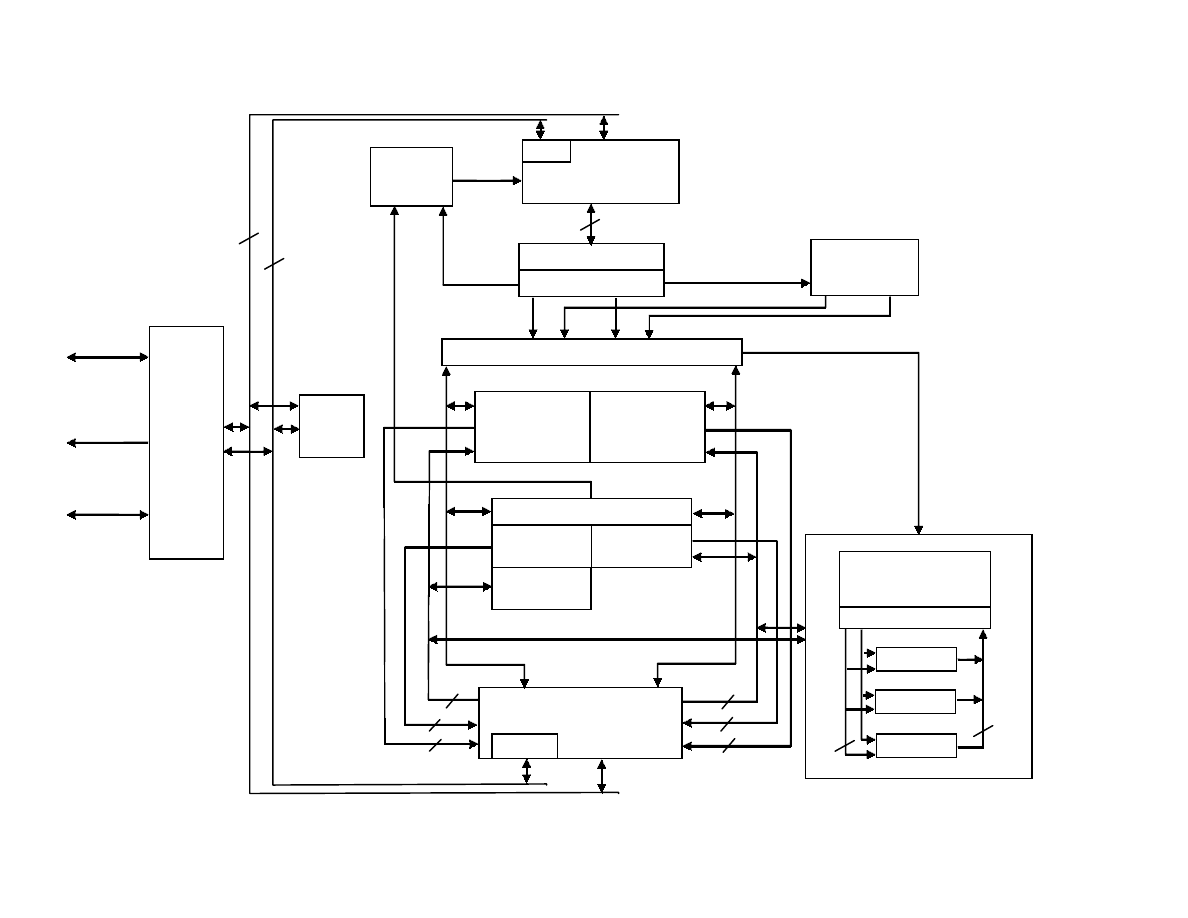

Blok

interfejsu

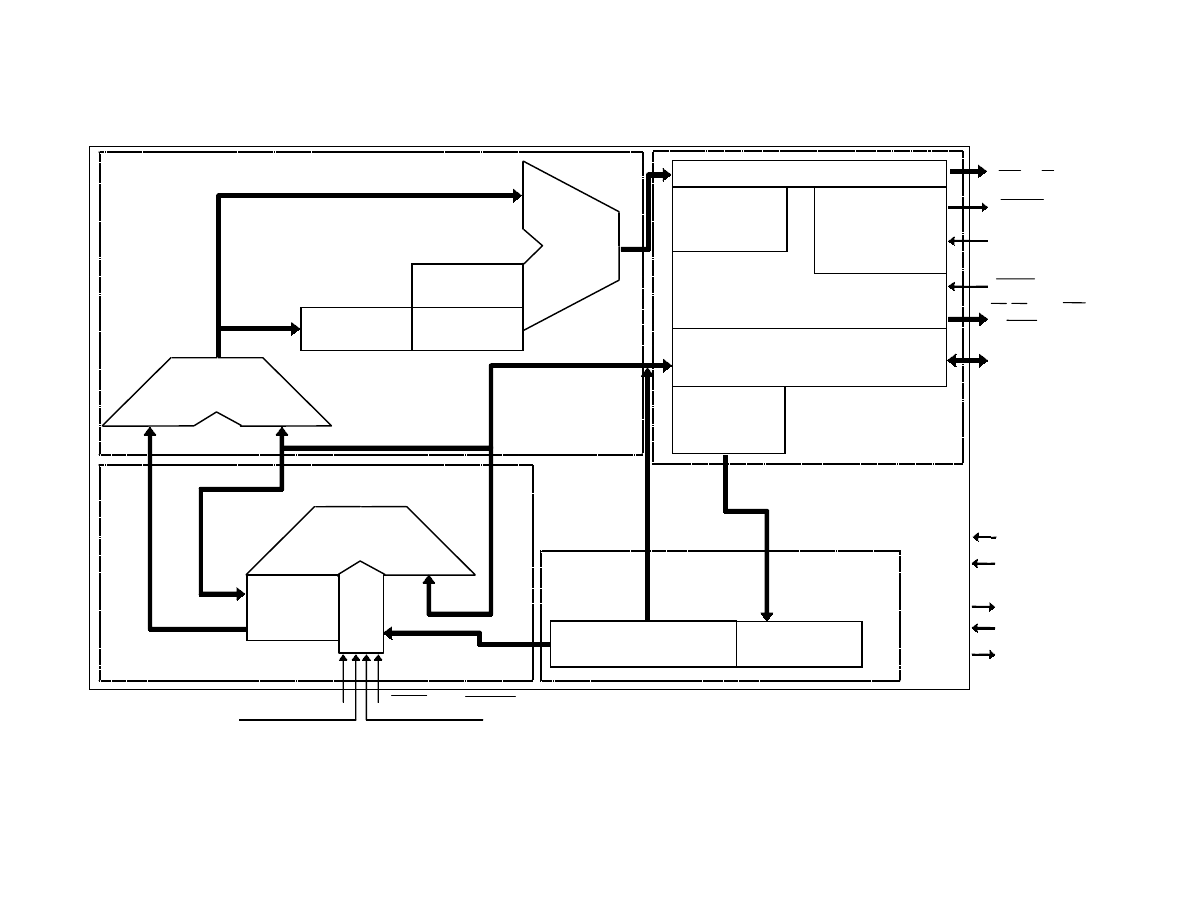

Schemat blokowy mikroprocesora 80286.

Dane

ALU

Zestaw

rejestrów

Rejestr

przesuwający

Blok

segmentacji

Tablica

deksry-

ptorów

Blok

interfejsu

Sterowanie

Adresy

Blok

wprowadzania

Kolejka

rozkazów

Dekoder

rozkazów

Kolejka

Sterowanie

Blok

kontroli

dostępu

Blok prze-

twarzania

danych

Blok programu

Blok

stronicowania

TLB

Schemat funkcjonalny mikroprocesora 80386.

Mikroprocesor

Rozkaz n+2

Rozkaz n

Rozkaz n+1

Blok wyprzedzającego

wprowadzania

Rozkaz n-1

Dekoder rozkazów

Rozkaz n-2

Rozkaz n

Rozkaz n-1

Rozkaz n+1

Rozkaz n+3

Rozkaz n+2

Pamięć programu

Mechanizm wyprzedzającego wprowadzania kodów rozkazów.

Układ przesuwania

Blok rejestrów

ALU

Blok segmentacji

Deskryptory

Długości segmentów

i prawa dostępu

Blok

stronnicowania

Blok pamięci

Cache

Kolejka

rozkazów

Blok

wprowadzania

Dekoder

instrukcji

Jednostka

zmiennopozycyjna

Blok rejestrów

zmiennopozycyjnych

Blok

interfejsu

szyny

Sterowanie

Pamięć

mikroprogramów

20

32

32

32

2

128

Adres fizyczny

Szyna adresu liniowego

32

24

Zdekodowane

instrukcje

Strumień

instrukcji

PCD, PWT

32

Adres A2..A31

Dane D0..D31

Sterowanie

JTAG

mikroinstrukcje

Szyna danych

Szyna danych

64-bitowa wewnętrzna szyna danych

Schemat blokowy mikroprocesora 80486.

Kolejka rozkazów

Dekoder instrukcji

Jednostka sterująca

Blok rejestrów

Bufor

kierunku

skoków

TLB

Cache programu

8 KB

Cache danych

8 KB

TLB

Układ generacji

adresów

(potok U)

Układ generacji

adresów

(potok V)

ALU

(potok U)

ALU

(potok V)

Rejestr

przesuwny

Blok

stroni-

cowania

256

Wskaźnik

instrukcji

Pamięć

mikroinstrukcji

ROM

Blok

interfejsu

64-bitowa

szyna

danych

32-bitowa

szyna

adresowa

Sterowanie

Jednostka zmienno-

przecinkowa

Blok rejestrów

Dodawanie

Dzielenie

Mnożenie

80

80

64-bitowa

szyna

danych

32-bitowa

szyna

adresowa

32

32

32

32

32

32

Schemat blokowy

mikroprocesora Pentium

18

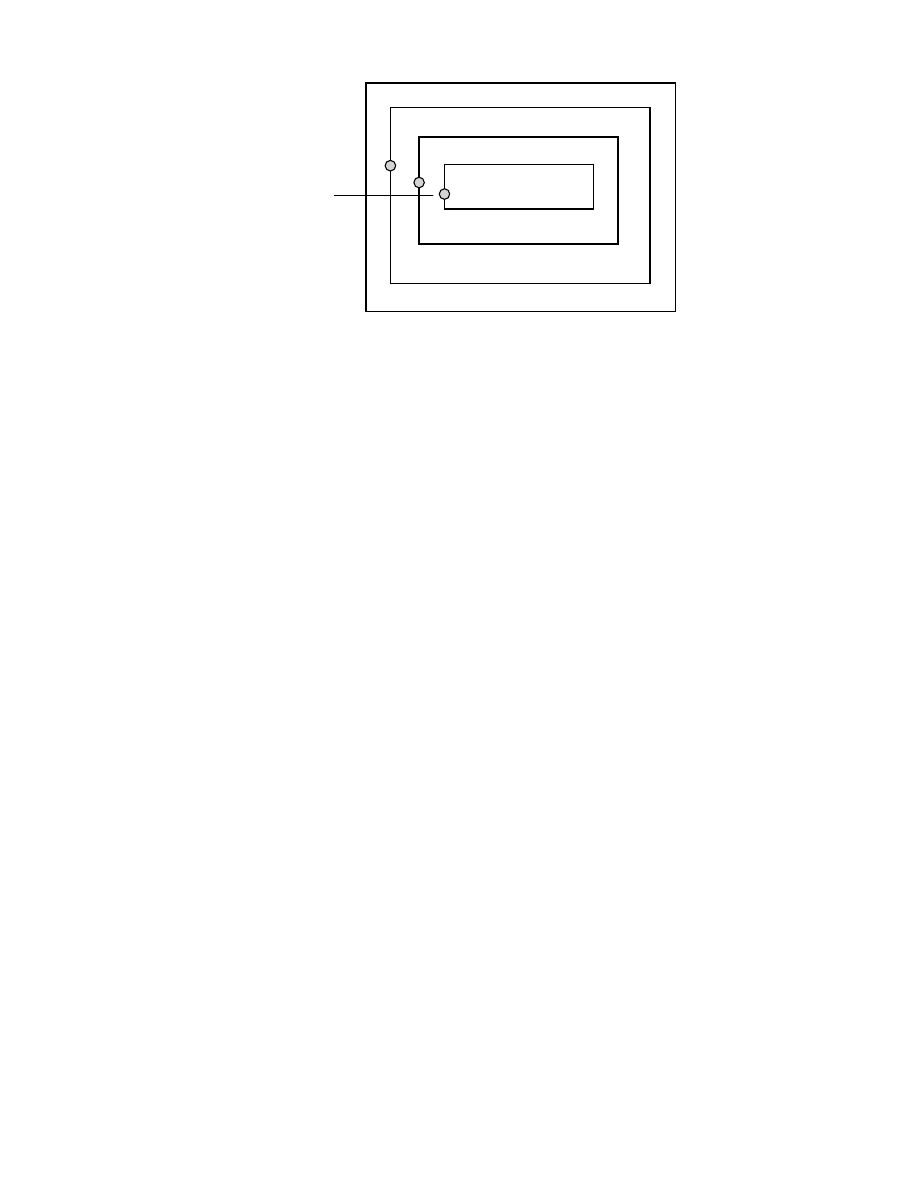

Rozszerzenie systemu operacyjnego

PL = 2

Jądro

PL = 0

Usługi systemowe

PL = 1

Zadania użytkowe

PL = 3

Interfejsy

programowe

realizowane

przez CPU.

Hierarchiczny system poziomów uprzywilejowania.

19

Organizacja rejestrów procesora PENTIUM

Rodzaje rejestrów:

!"

Ogólnego przeznaczenia (robocze). Występuje 8 32-bitowych

rejestrów ogólnego przeznaczenia;

!"

Segmentowe. Sześć 16-bitowych rejestrów segmentowych zawiera

selektory segmentu służące jako indeksy w tablicach segmentów.

!"

Znaczniki stanu. Rejestr EFLAGS zawiera kody warunkowe i różne

bity trybu.

!"

Wskaźnik rozkazu. Zawiera adres bieżącego rozkazu.

!"

Rejestry do współpracy z jednostką zmiennopozycyjną:

numeryczne – 8 rejestrów 80-bitowych, dostępnych jako stos; rejestr

sterowania – 16-bitowy rejestr sterowania;

rejestr stanu;

słowo wyróżników.

20

Rejestry sterowania

Pentium wykorzystuje cztery 32-bitowe rejestry sterowania CR0, CR2,

CR3, CR4.

Rejestr CR0 zawiera znaczniki stanu sterowania systemowego, które

sterują trybami lub wskazują stany odnoszące się raczej do procesora

niż do wykonywanego programu. Znaczniki te są następujące:

Zezwolenie ochrony (PE). Włącza lub blokuje tryb chroniony.

Monitorowanie koprocesora (MP).

Emulacja (EM). Ustawiany, gdy procesor nie ma jednostki

zmiennopozycyjnej.

Błąd numeryczny (NE). Umożliwia standardowy mechanizm zgłaszania

błędów zmiennopozycyjnych na zewnętrznych liniach danych.

Ochrona zapisu (WP). Gdy ten bit jest zerem, strony tylko do odczytu

na poziomie uprzywilejowania użytkownika mogą być zapisane przez

program nadzorczy (SO).

Brak zapisu jednoczesnego (NW). Wybiera tryb pracy pamięci

podręcznej danych. Gdy bit ten jest ustawiony, operacje zapisu

jednoczesnego pamięci podręcznej są zablokowane.

Blokowanie pamięci podręcznej (CD). Włącza lub blokuje mechnizm

zapełniania wewnętrznej pamięci podręcznej.

Rejestr CR2 służy do przechowania 32-bitowego adresu liniowego

ostatniej strony, która spowodowała błąd strony.

Rejestr CR3 (20 bardziej znaczących bitów) – adres podstawowego

katalogu stron.

W rejestrze CR4 jest zdefiniowanych 6 dodatkowych bitów kontrolnych.

21

Komputery o złożonej liście rozkazów (CISC)

Charakteryzowały się stosowaniem bogatej listy rozkazów, które

zawierały zarówno większą liczbę rozkazów, jak i rozkazy bardziej

złożone.

Powody takiej tendencji:

- dążenie do uproszczenia kompilatorów (architekci dążyli do

zaprojektowania maszyn, które zapewniałyby lepsze wsparcie

języków wysokiego poziomu),

- dążenie do poprawy wydajności

Własności architektur o zredukowanej liście rozkazów (RISC)

!"

Jeden rozkaz na cykl

!"

Operacje typu „z rejestru do rejestru”

!"

Proste tryby adresowania

!"

Proste formaty rozkazów

22

Układy wej / wyj

Układy współpracujące

z klawiaturami

i wskaźnikami

Układy sterujące

minitory ekranowe

Układy sterujące

dyski elastyczne

Programowane układy

sterowania przerwań

Układy sterowania

kanału DMA

Programowane

liczniki

Układy

wielofunkcyjne

Układy służące do

równoległego

przesyłania informacji

Programowane

układy wej / wyj

Proste układy typu:

- rejestr zatrzaskowy;

- bufor.

Układy służące do

szeregowego przesyłania

informacji

Synchroniczne

Asynchroniczne

Synchroniczne

i asynchroniczne

Podstawowe

uniwersalne

układy wej / wyj

Specjalizowane

układy wej / wyj

Układy

sterujące

Inne

układy

Układy wej / wyj współpracujące z monitorem

23

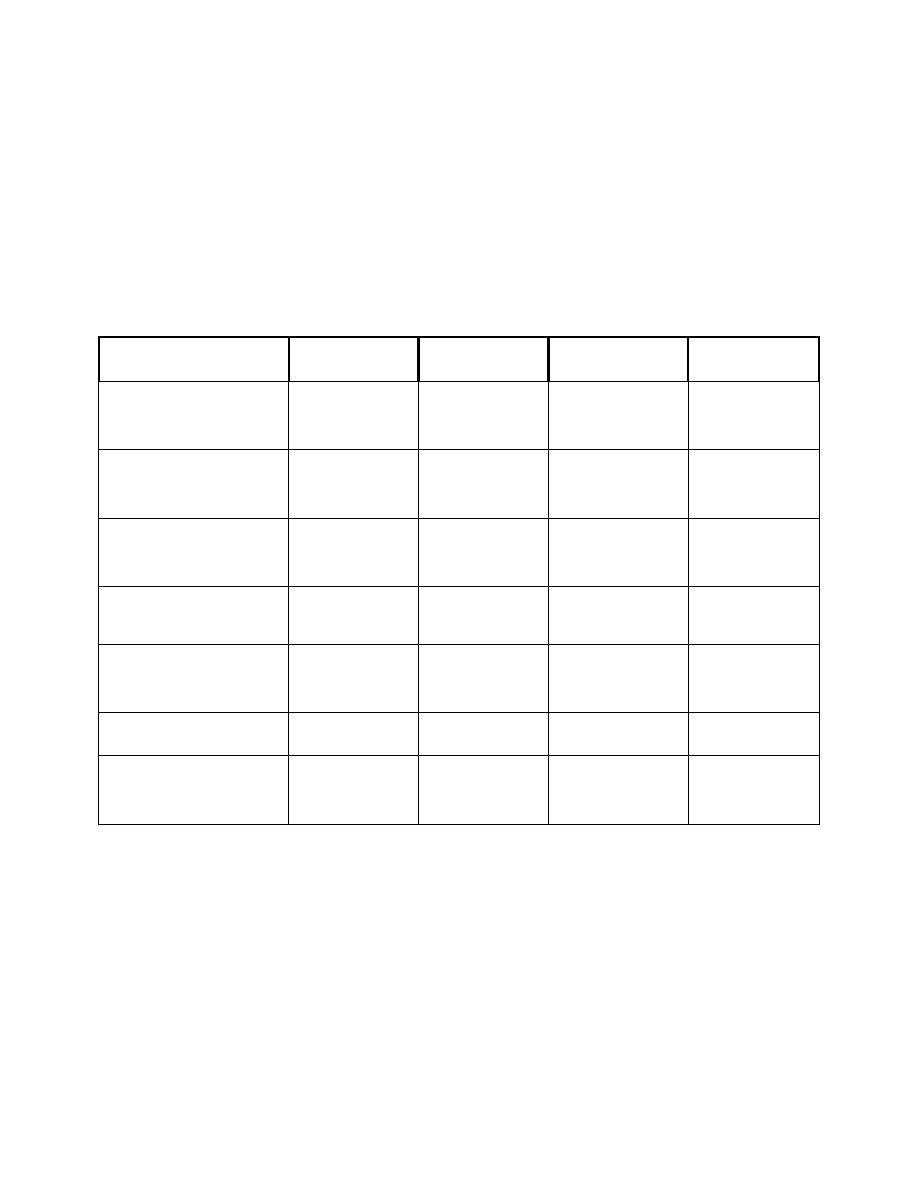

Porównanie parametrów procesorów PENTIUM

Wyszczególnienie

Pentium

Pentium Pro

Pentium MMX

Pentium II

Częstotliwość procesora

[MHz]

75 - 200

150 - 200

166/200/233 233-400

Częstotliwość magistrali

[MHz]

50/60/66 60/66

66

66

Szerokość magistrali

wewnętrznej

64-bity 64-bity 300-bitów 300

Pamięć podręczna L1 [KB]

8 + 8

/rozkazy+dane/

8 + 8

/rozkazy+dane/

16 + 16

/rozkazy+dane/

16 + 16

/rozkazy+dane/

Częstotliwość magistrali

pamięci L1 [MHz]

75 - 200

150-200

166/200/233 233-400

Pamięć podręczna L2 [KB]

----------- 256/512 ------------ 512

Częstotliwość magistrali

pamięci L2 [MHz]

-----------

150-200 ------------

Częstotliwość L1 /

2

24

Potokowe przetwarzanie danych (Pipelining).

Mechanizm ten pozwala procesorowi na rozbicie pojedynczego rozkazu na

kilka-kilkanaści części - etapów, które są następnie przetwarzane potokowo niczym

na taśmie produkcyjnej. Im więcej etapów, tym na pojedynczy etap przypada

mniejszy zakres zadań i może zostać zastosowana większa częstotliwość

taktowania. Każde z typów zadań ma przydzieloną oddzielną jednostkę do jego

wykonywania. Każda jednostka rozwiązuje tylko jeden, określony typ zadań i wyniki

przekazuje do następnego etapu. W rezultacie uzyskuje się wzrost prędkości

roboczej procesora.

Superskalarność

Jest to właściwość procesorów, w których jest więcej niż jeden potok. Procesor

przydziela realizację określonych instrukcji wolnym w danym momencie potokom,

przy jednoczesnym usuwaniu zależności pomiędzy poszczególnymi instrukcjami, aby

uniknąć zbędnego oczekiwania. W wyniku tego żaden z rozkazów znajdujących się

w potoku nie musi oczekiwać na wynik realizacji rozkazu w innym potoku i

wstrzymywać przetwarzania pozostałych poleceń.

Dynamiczne wykonywanie rozkazów (Dynamic Execution).

Pod tym pojęciem kryje się kombinacja trzech technik, po raz pierwszy

zastosowana w Pentium Pro, dzięki którym procesor osiąga znaczny wzrost

wydajności. Są to:

•

mechanizm prognozowania rozgałęzień,

•

analiza przepływu danych,

•

spekulacyjne wykonywanie rozkazów.

Mechanizm prognozowania rozgałęzień.

Zadaniem tego mechanizmu jest przewidywanie miejsca gdzie nastąpi skok po

wykonaniu rozkazu warunkowego. Działanie mechanizmu polega na porównywaniu i

analizie sekwencji rozkazów na poszczególnych etapach potoku. Dzięki czemu jest

on wstanie z dużym prawdopodobieństwem określić, które rozgałęzienie zostanie

wybrane oraz która sekwencja rozkazów będzie przetwarzana jako kolejna, po czym

kontynuuje wykonywanie programu od tego miejsca. Efektywność tego mechanizmu

w praktyce sięga 90%.

25

Analiza przepływu danych

Jest to jeden z mechanizmów dynamicznego wykonywania rozkazów w

procesorze. Polega na analizie i ustalaniu optymalnej kolejności wykonywania

instrukcji. Analizując przepływające dane procesor sprawdza i określa, czy kolejne

rozkazy są dostępne i czy mogą być wykonane, tzn. czy ich realizacja nie jest

zależna od wyników aktualnie wykonywanych rozkazów.

Spekulacyjne wykonywanie rozkazów (Speculation Execution).

Jest to mechanizm, który pozwala rozpocząć wykonywanie rozkazu wcześniej,

niż to wynika z normalnej sekwencji rozkazów. Procesor wykonuje następne rozkazy,

mimo że czeka na wynik realizowanej równolegle instrukcji skoku. Jeśli za pomocą

mechanizmu prognozowania skoków, procesor prawidłowo ocenił adres skoku,

przyjęta spekulacyjnie koncepcja jest właściwa i przynosi w efekcie duży wzrost

wydajności. Wyniki przetwarzania spekulacyjnego są przetrzymywane chwilowo w

buforze ROB (Re-Order Buffer).

Bufor translacji adresów TLB (Translation Lookside Buffer).

Jest to element pamięci podręcznej, w którym przechowywane są ostatnio

używane odwołania do tablicy pamięci podręcznej. Używany jest do przyspieszenia

wyznaczania adresu fizycznego pamięci. Jeżeli odwołanie do pamięci wykorzystuje

informację zawartą w TLB to czas translacji adresu wynosi tylko pół taktu zegara.

Łączny czas przetwarzania adresu logicznego na fizyczny (wyliczenie adresu

efektywnego, segmentacja i stronicowanie) zajmuje wówczas 2 takty zegara.

Procesor ma zwykle dwa bufory tego typu: jeden dla pamięci podręcznej danych,

drugi dla pamięci podręcznej rozkazów.

Bufor rozgałęzień (Branch target buffer).

Jest to pamięć skojarzeniowa o nie wielkiej pojemności (zwykle 128-512

pozycji) będąca elementem mechanizmu prognozowania rozgałęzień, której

zadaniem jest prognozowanie skoków w programie. Wykorzystując złożone

algorytmy śledzi ona zawartość pamięci podręcznej programu i wskazuje, opierając

się na historii skoków, który rozkaz powinien być pobrany w następnej kolejności.

26

Przekazywanie danych (Data forwarding).

Jest to mechanizm, którego działanie polega na przekazaniu danych

odczytanych z pamięci na żądanie jednej instrukcji wszystkim instrukcjom, które ich

żądają a są przetwarzane w innych potokach. Przekazaniem danych steruje

procesor. Dzięki niemu uzyskuje się dane dla kilku instrukcji, przy jednokrotnym

dostępie do pamięci. Mechanizm ten realizuje również czynność przekazania wyniku

operacji z jednego potoku do instrukcji przetwarzanej w drugim potoku w sposób

bezpośredni, tzn. bez zapisu do pamięci czy rejestrów. Mechanizm ten może być

stosowany w procesorach superskalarnych.

Wyszukiwarka

Podobne podstrony:

Architektura5 id 67923 Nieznany (2)

Architektura3 id 67919 Nieznany (2)

Architektura2 id 67918 Nieznany

ArchitekturaKomputera2 id 67926 Nieznany (2)

Architektura6 id 67924 Nieznany (2)

ArchitekturaKomputera id 67925 Nieznany

PEK PB OPIS ARCHITEKTURA id 354 Nieznany

Architektura1 id 67917 Nieznany (2)

Architektura5 id 67923 Nieznany (2)

Architektura3 id 67919 Nieznany (2)

architektura aplikacji id 67748 Nieznany (2)

Architektura Neutrino 1 id 6791 Nieznany (2)

Architektura Komp2 id 67910 Nieznany (2)

Architektura ekoczasu id 67766 Nieznany (2)

5 Architektura MCU 2010 id 4004 Nieznany (2)

ARCHITEKTURA KOMPUTEROW id 6779 Nieznany (2)

Architektura Renesansu id 67864 Nieznany (2)

Architektura Komp5 id 67913 Nieznany (2)

Architektura drewniana 2 id 677 Nieznany (2)

więcej podobnych podstron