J. U

łasiewicz Komputerowe systemy sterowania 1

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

1 Architektura PC

1.1.

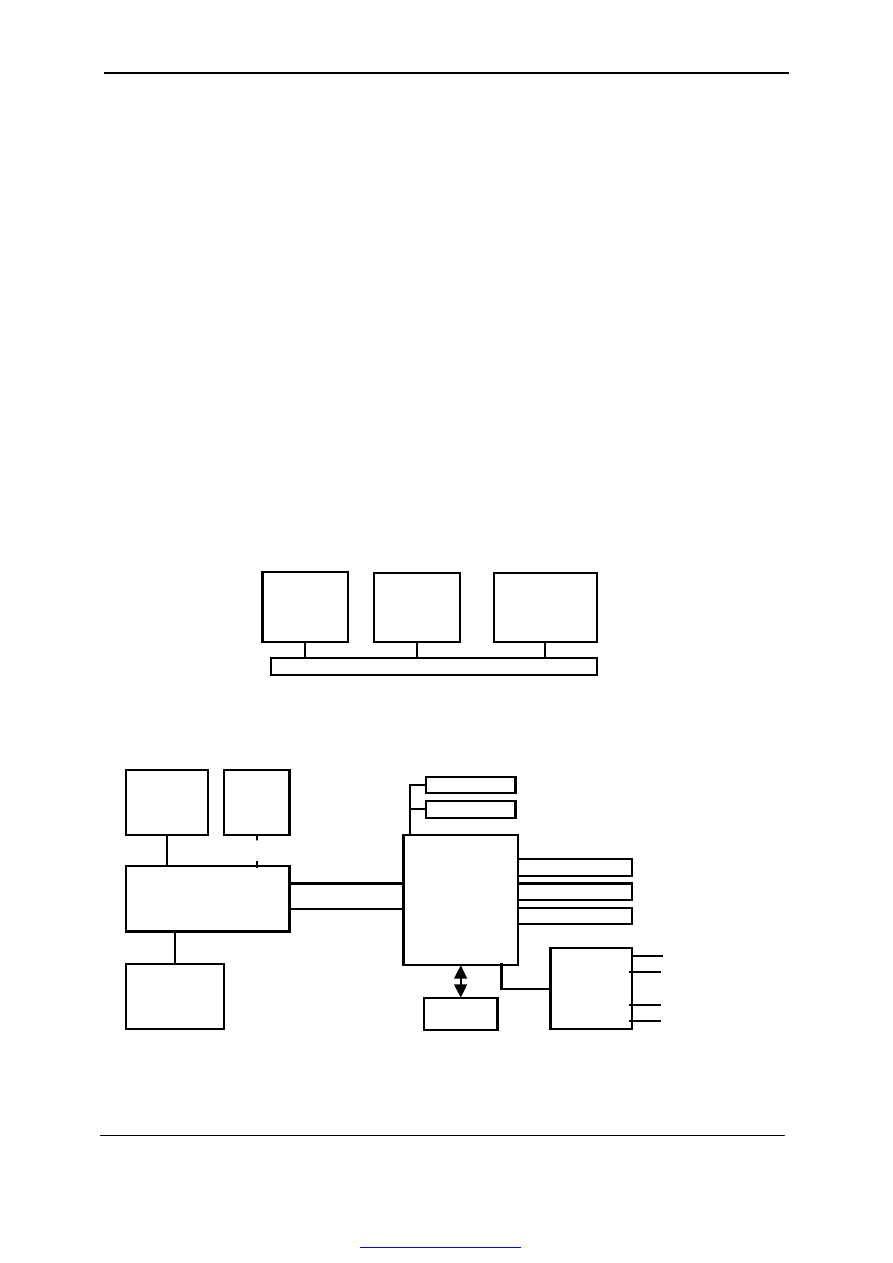

Ogólna struktura systemu jednoprocesorowego

Ju

ż systemy jednoprocesorowe mogą być środowiskiem, w którym

wykonywane jest wiele programów wspó

łbieżnych.

Omówione na przyk

ładzie komputera PC i architektury IA-32 - (80386,

80486 i Pentium).

Aby program móg

ł się wykonywać i komunikować z otoczeniem

niezb

ędny jest

•

procesor

•

pami

ęć

•

system wej

ścia wyjścia.

Procesor

Pami

ęć

RAM

system

we / wy

magistrala

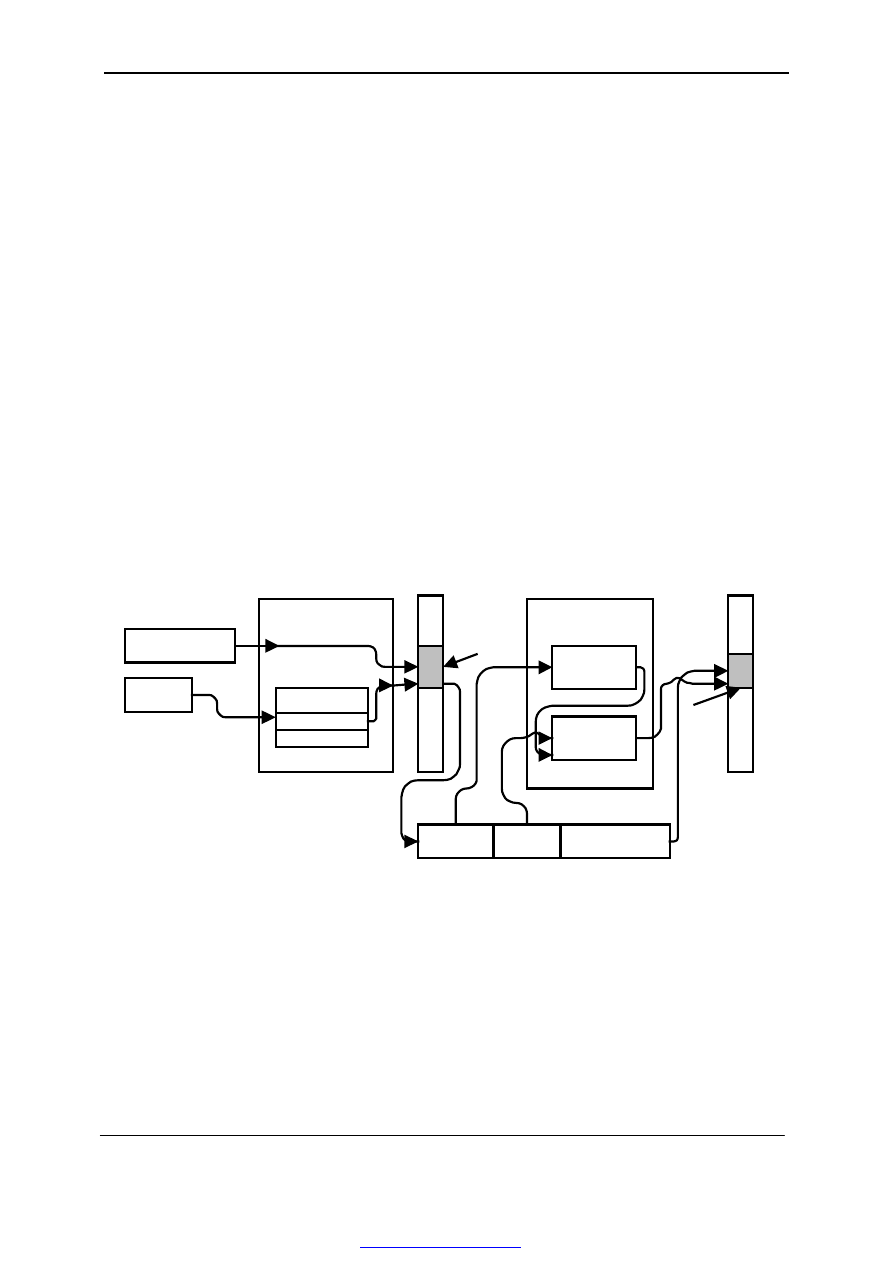

Rys. 1-1 Struktura systemu jednoprocesorowego

Procesor

Pami

ęć

Magistrala

Mostek pónocny

Mostek

poludniowy

AGP lub PCI

Express

FSB

PCI

SATA

ATA

USB

BIOS

Super IO

Mysz

Klawiatura

Porty COM

Port LPT

PCI

Rys. 1-2 Architektura komputera PC

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 2

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

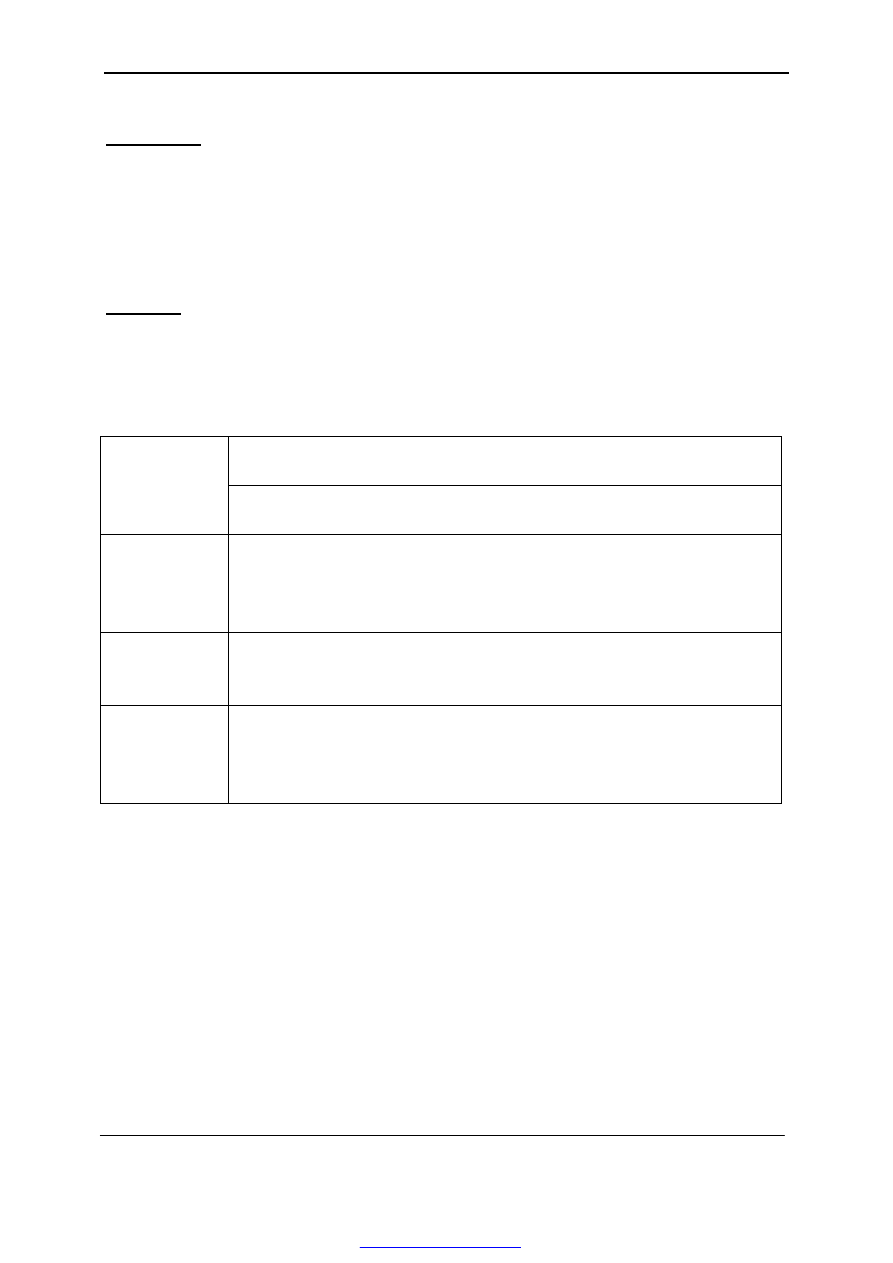

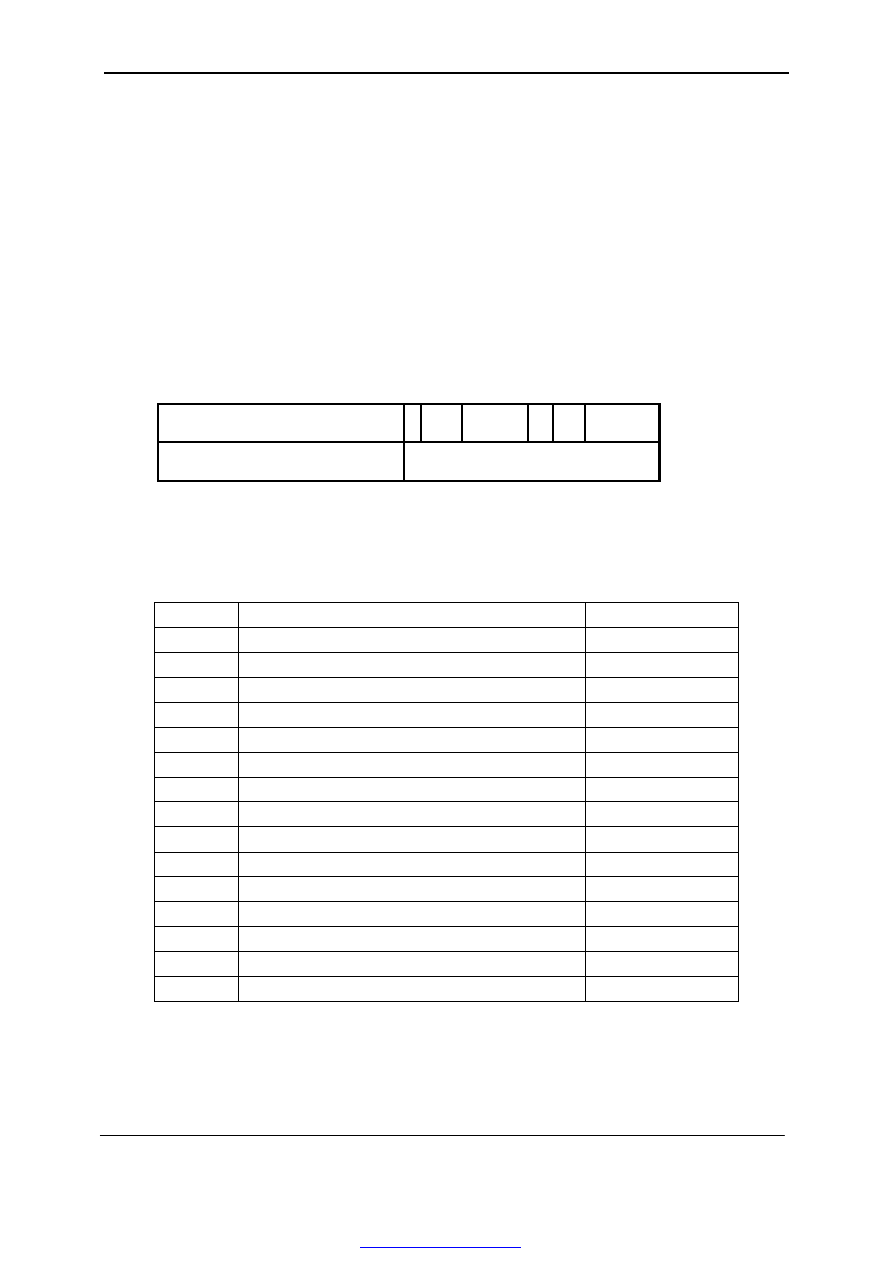

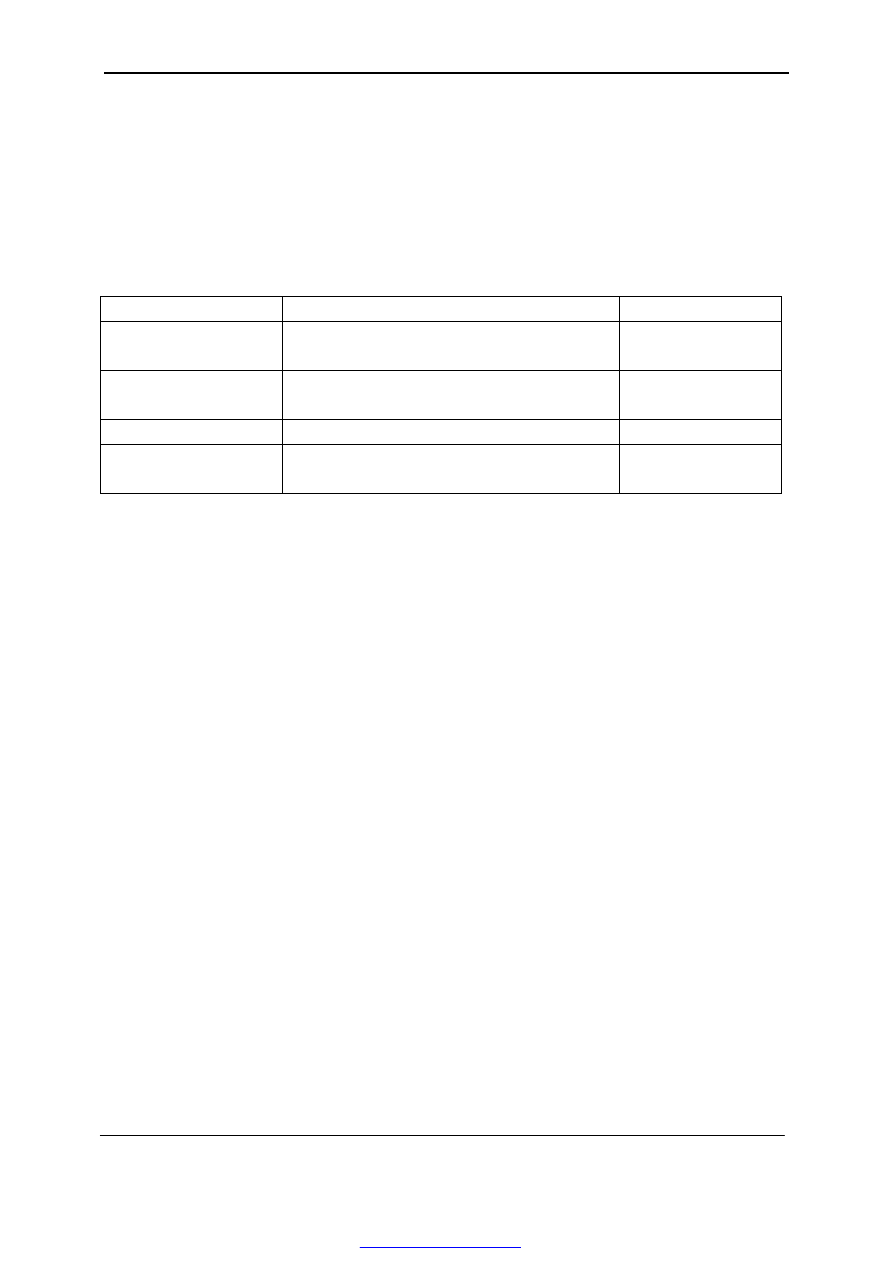

Szyny

Szyny mostka pó

łnocnego Szyny mostka południowego

Rodzaje

FSB, RAM, AGP,

PCI Express X16, CSA

ISA, PCI, PCI Express, USB,

ATA, SCSI, FireWire

Łączą

CPU, RAM, Wideo,

Ethernet

Wszystkie inne urz

ądzenia.

Cz

ęstotliwość

zegara

66 - 1066 MHz

Typowo 10-33 MHz.

Przepustowo

ść > 3 GB/sek

Typowo 20-500 MB/sec.

na magistral

ę

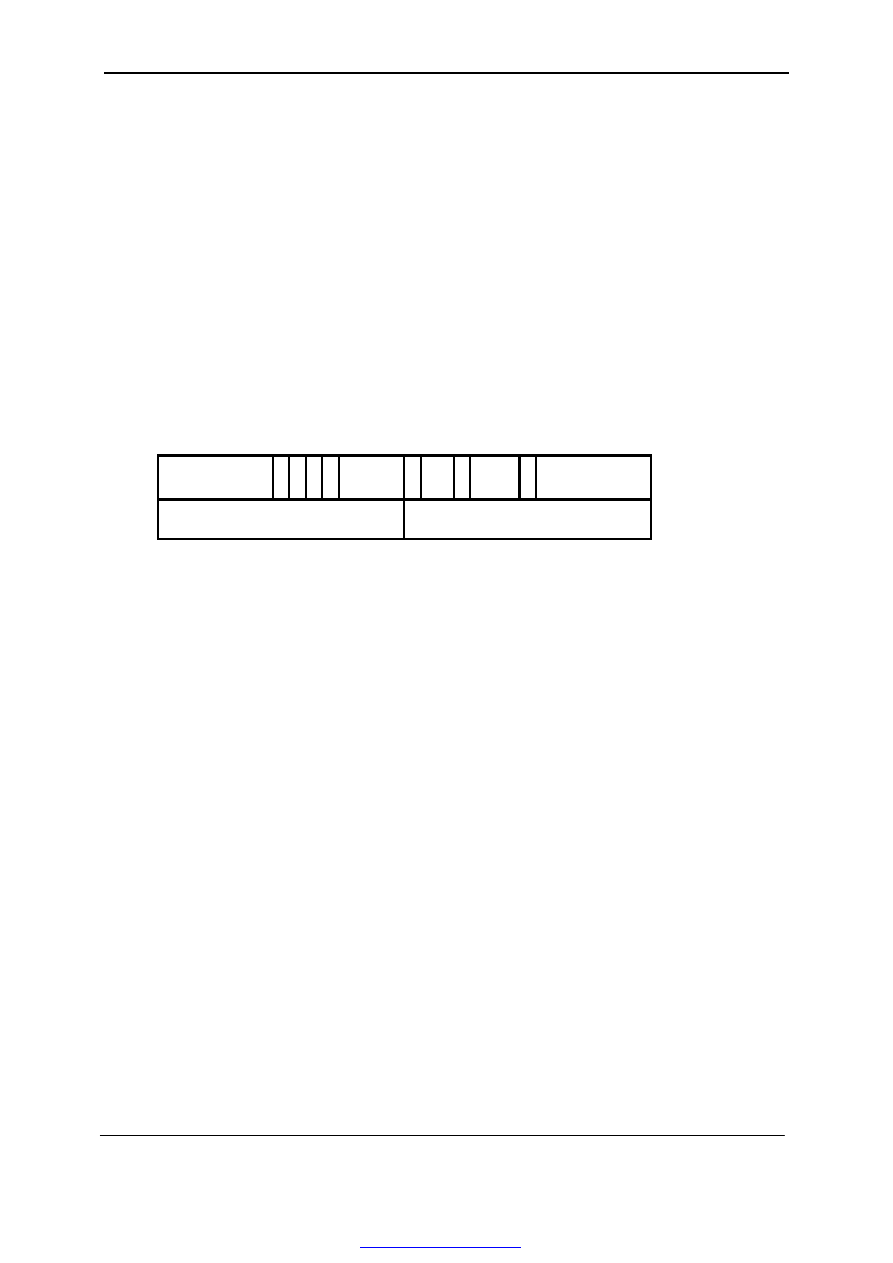

Tabela 1-1 Charakterystyka szyn komputera PC

1.2.

Procesor

Procesor wykonuj

ąc zawarty w pamięci operacyjnej program i

przekszta

łca zawarte tam dane.

Procesory rodziny IA-32 posiadaj

ą trzy tryby pracy:

•

tryb rzeczywisty,

•

tryb chroniony

•

tryb zarz

ądzania systemem.

W

łaściwym trybem normalnej pracy systemu jest tryb chroniony.

Najwa

żniejsze mechanizmy wspierające wieloprogramowość:

Wsparcie ochrony programów i systemu operacyjnego:

•

segmentacja

•

stronicowanie pami

ęci

•

poziomy ochrony procesora.

Wsparcie prze

łączania procesów i współbieżnego we/wy:

•

system przerwa

ń i wyjątków

•

autonomiczny system wej

ścia wyjścia

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 3

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

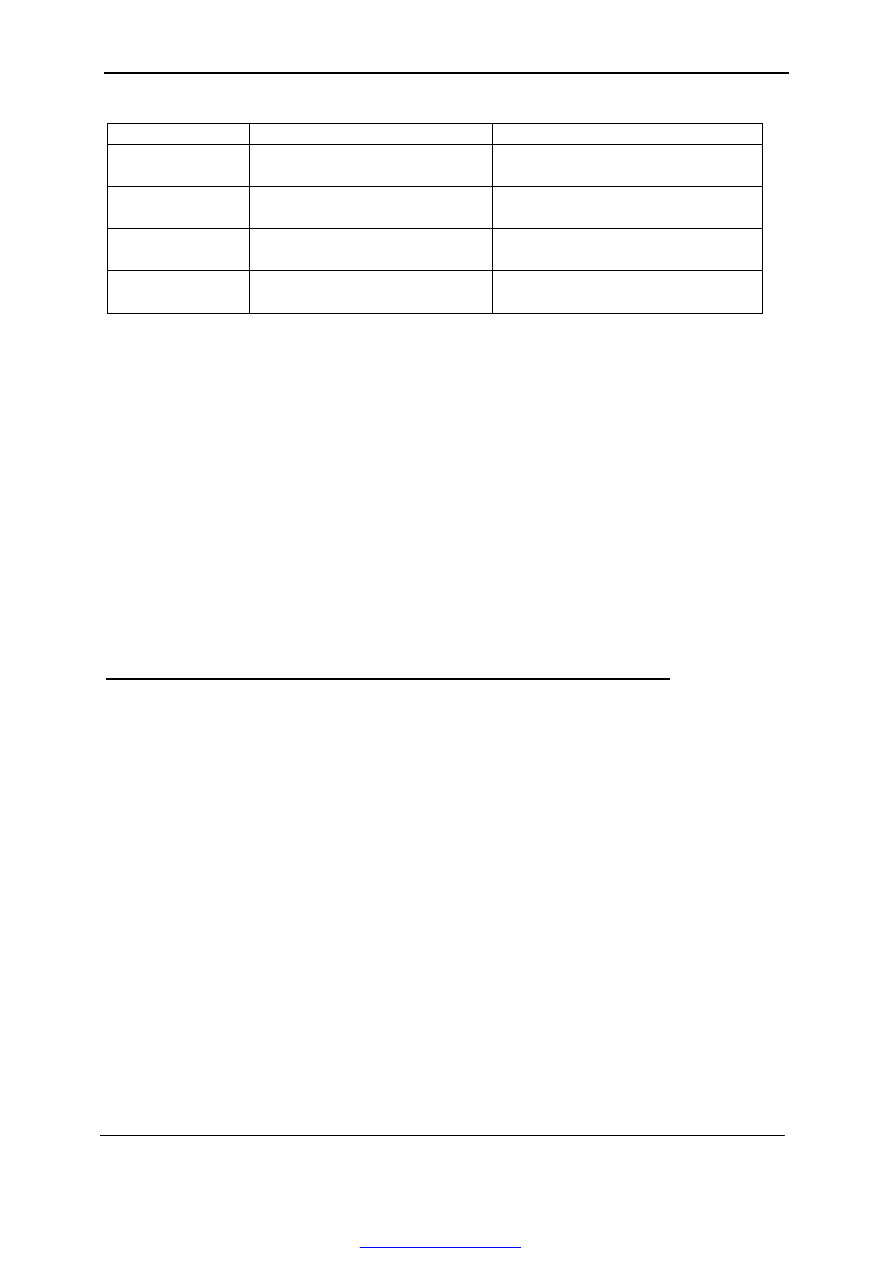

EAX

AH

AL

BH

BL

CH

CL

DH

DL

EBX

ECX

EDX

ESI

EDI

EPB

ESP

AX - akumulator

BX - rejestr danych

CX - rejestr p

ętli

DX - rejestr arytmetyczny

SI - wska

źnik żródla

DI - wska

źnik przeznaczenia

BP - wska

źnik bazy

SP - wska

źnik stosu

0

7

15

31

CS - segment kodu

DS - segment danych

SS - segment stosu

ES - segment dodatkowy

FS - segment dodatkowy

GS - segment dodatkowy

EIP

EFlags

IP - licznik rozkazów

PSW - flagi

selektory

segmentów

Rys. 1-3 Rejestry procesora w architekturze IA-32 dla trybu chronionego

Rys. 1-4 Zawarto

ść rejestru EFlags

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 4

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

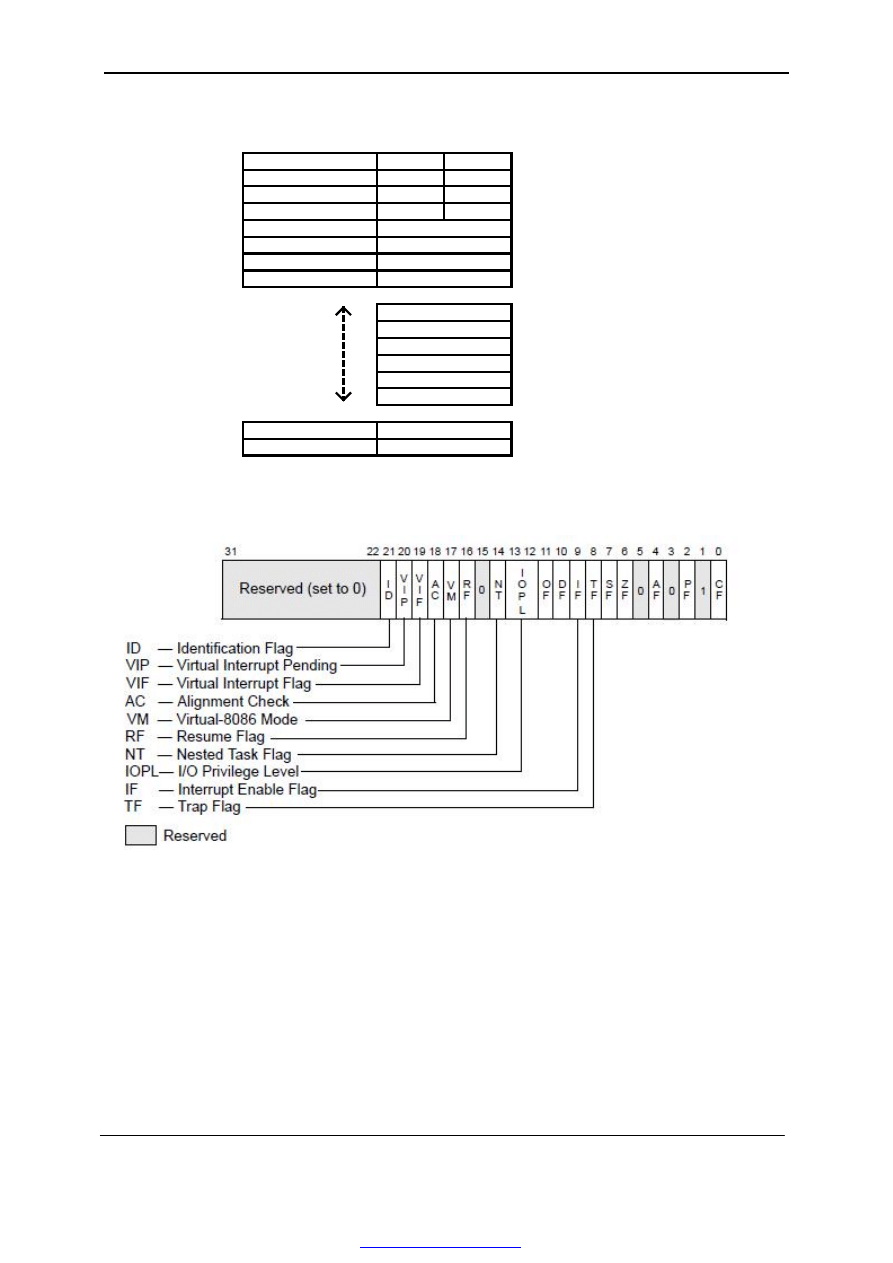

Rysunek z Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume

3 System Programming Guide

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 5

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

1.3.

Ochrona pami

ęci

Pami

ęć operacyjna - jednowymiarowa tablica bajtów.

Maksymalny wymiar pami

ęci dla procesorów 32 bitowych - 4 GB.

Procesory mog

ą wykonywać wiele procesów w trybie podziału czasu

procesora.

Mo

żliwa jest sytuacja gdy wystąpi błąd w programie – na skutek tego

proces dokonuje modyfikacji danych nale

żących do innego procesu lub

systemu operacyjnego.

Mechanizmem stosowanym do wzajemnego odizolowania procesów jest

mechanizm segmentacji. Umo

żliwia on również relokację.

W architekturze IA-32 dost

ępna jest tak segmentacja jak i stronicowanie

- mechanizm stronicowania mo

że być wyłączony.

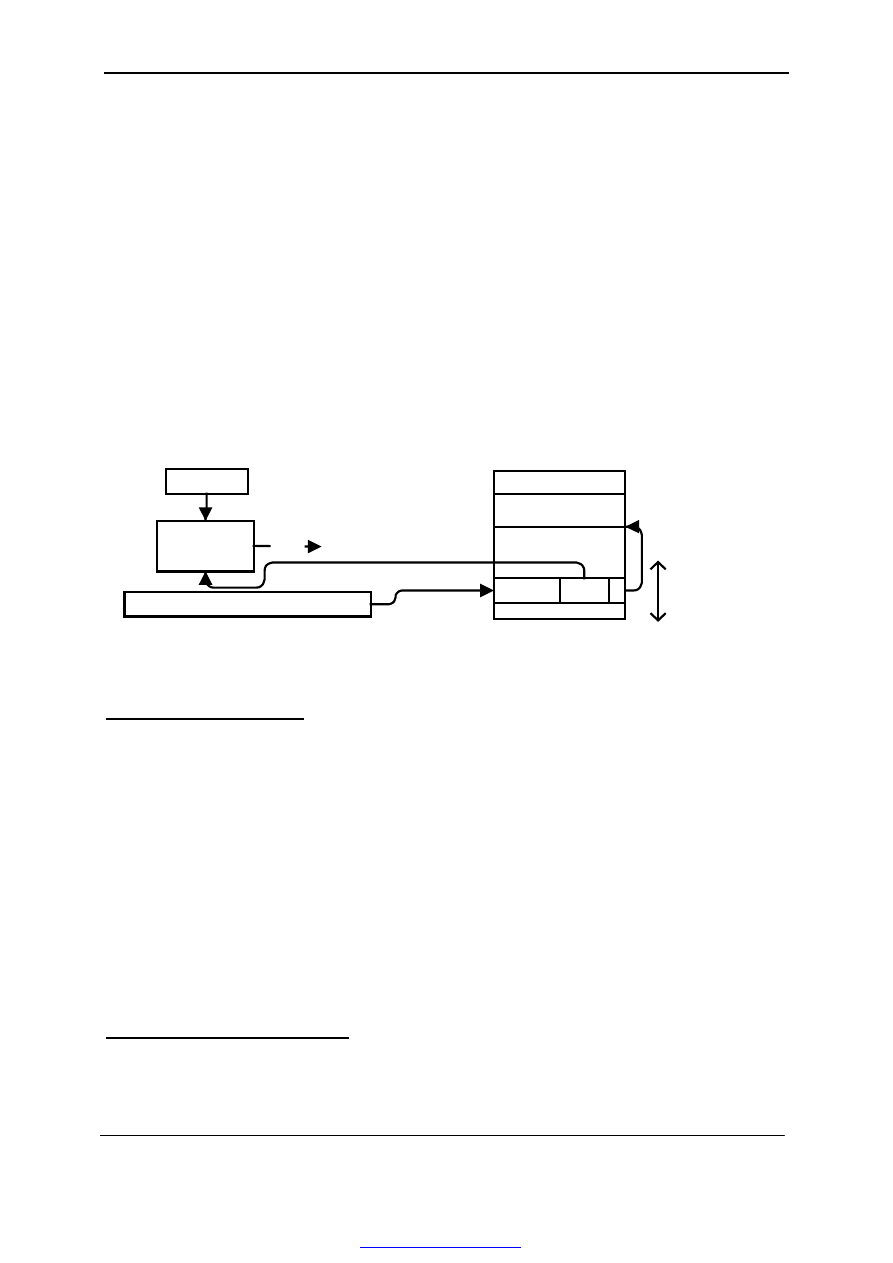

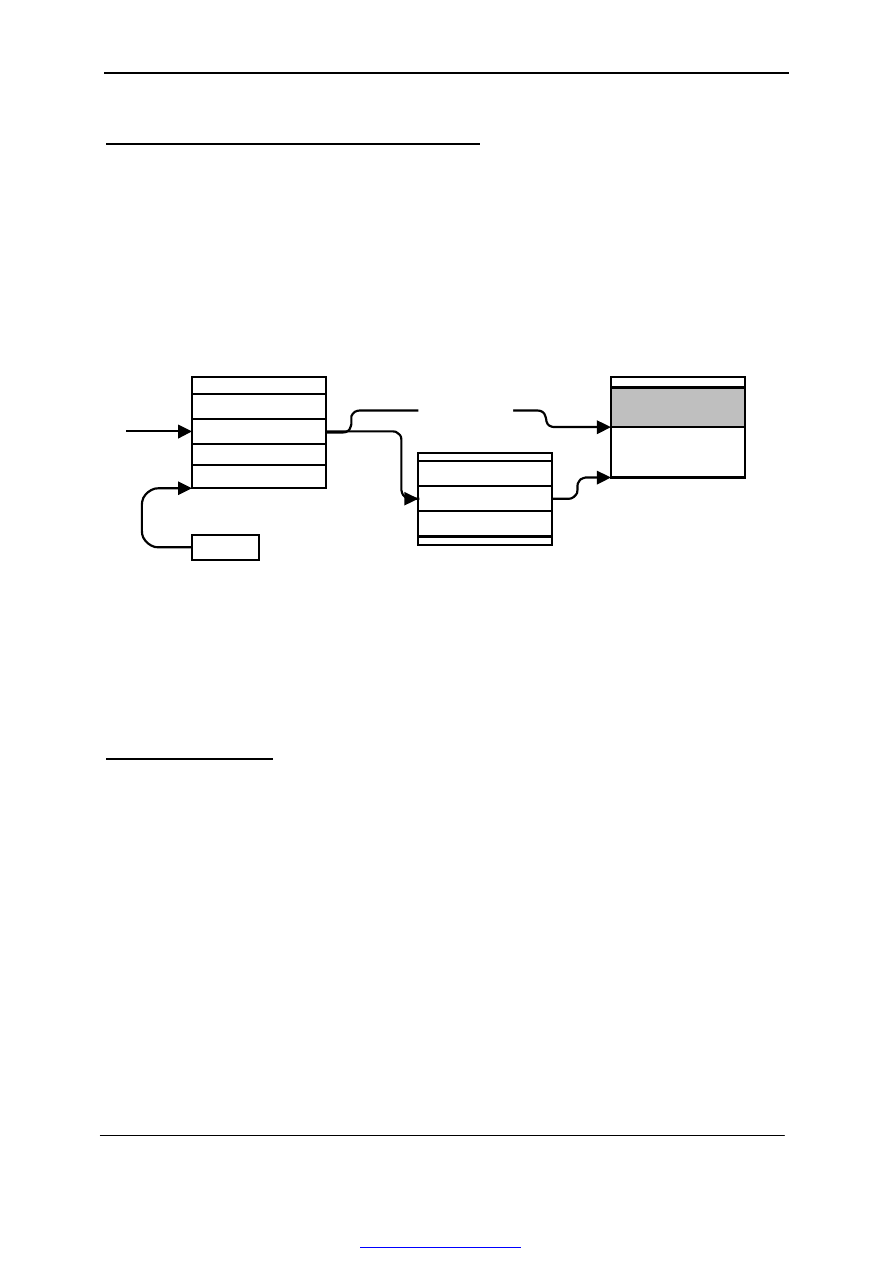

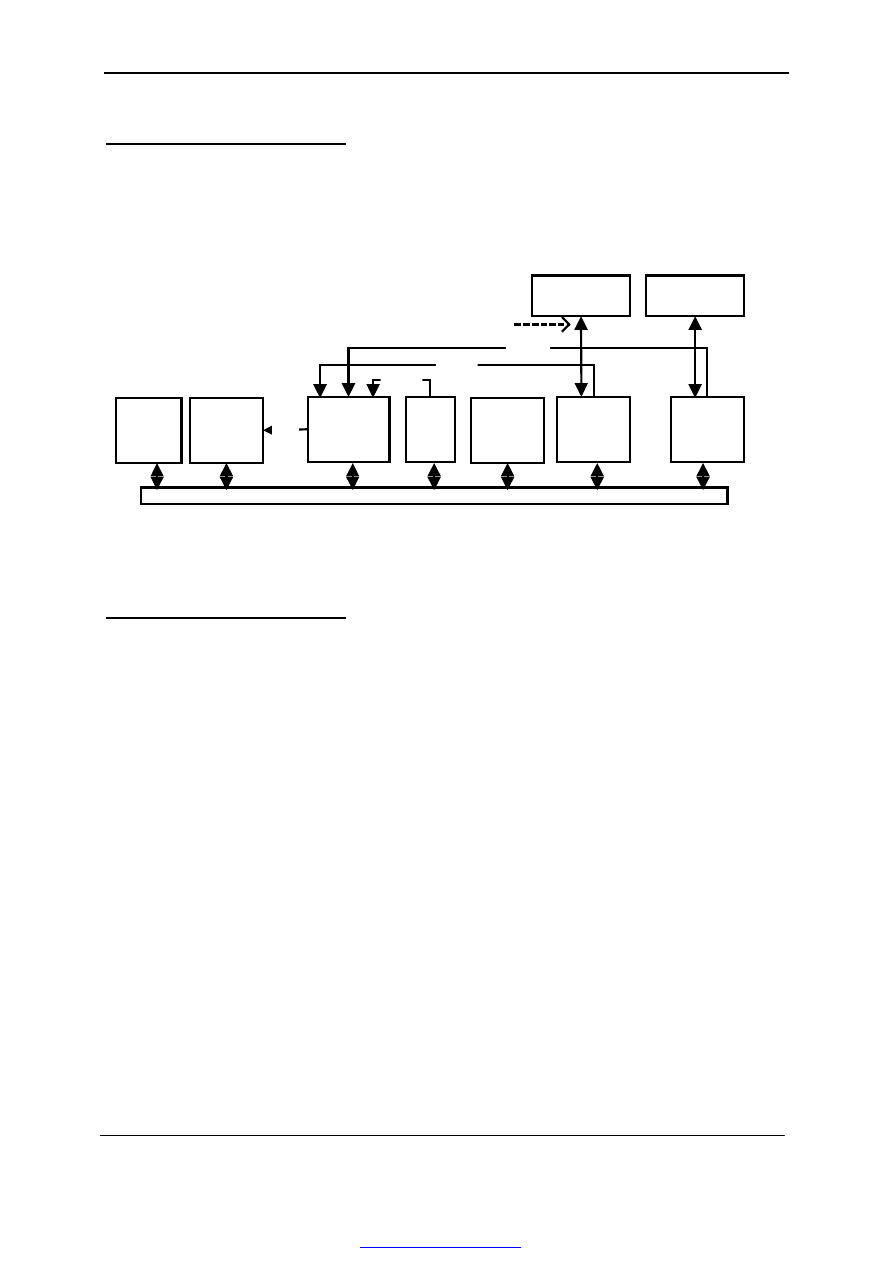

selektor

przesuni

ęcie

pami

ęc

RAM

mechanizm

segmentacji

mechanizm

stronicowania

Tablica

stron

adres

liniowy

numer

katalogu

przesuni

ęcie

adres

fizyczny

adres

logiczny

numer

strony

Katalog

stron

deskryptor

tabl. desktyptorów

segment

strona

Rys. 1-5 Mechanizm zarz

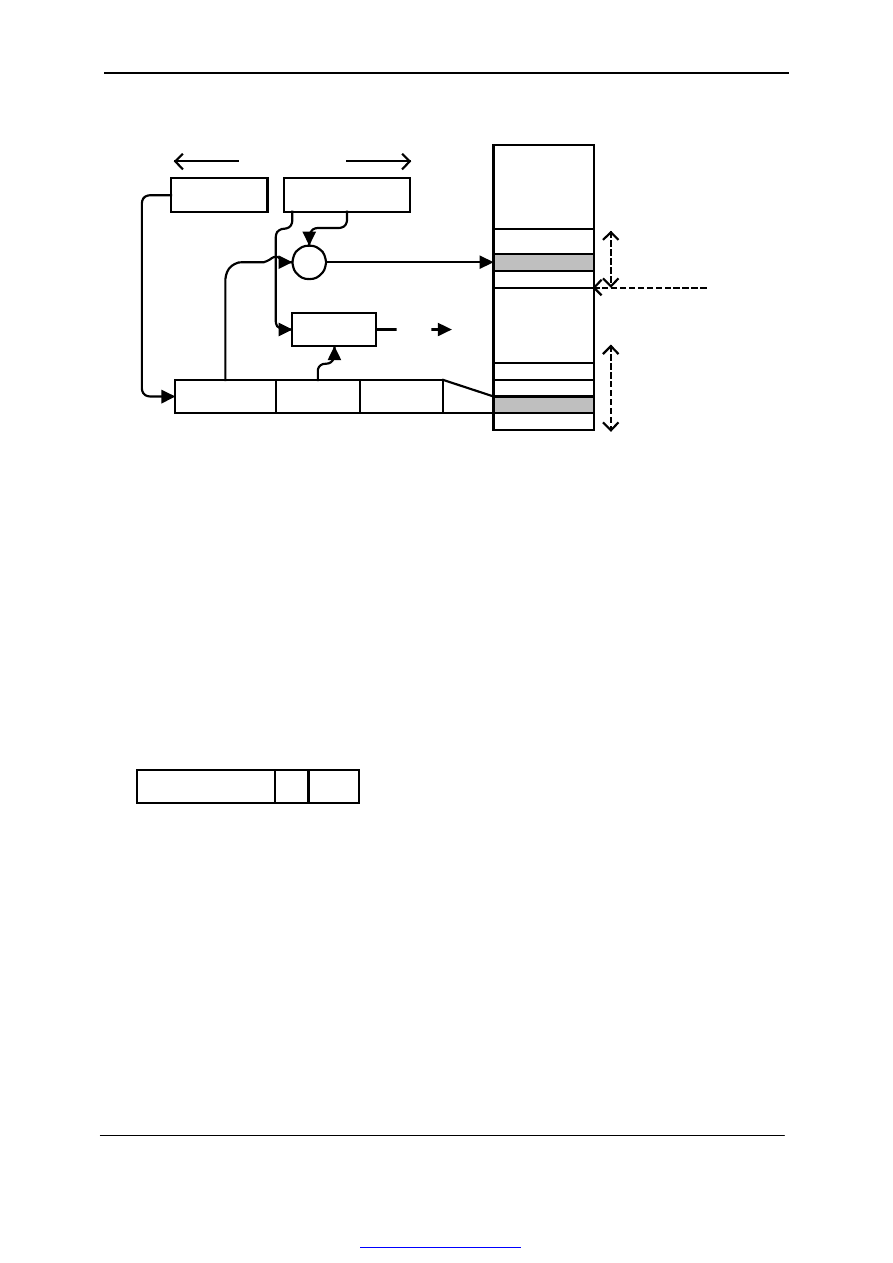

ądzania pamięcią w procesorach IA-32

Segmentacja - mechanizmem sprz

ętowym polegającym na podziale

pami

ęci operacyjnej na ciągłe bloki nazywane segmentami.

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 6

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

W procesorach IA-32 pami

ęć logiczna jest dwuwymiarowa. Adres składa

si

ę z:

•

selektora (ang. selektor) - okre

śla segment pamięci

•

przesuni

ęcia (ang. offset) - wyznacza adres wewnątrz segmentu.

Ka

żdy segment charakteryzuje się takimi parametrami

•

pocz

ątek bloku,

•

wielko

ść

•

atrybuty

Parametry segmentu przechowywane s

ą w 8 bajtowym rekordzie

nazywanym deskryptorem segmentu.

adres bazowy

31..24

G X 0

A

V

limit

19.16

B adres bazowy segmentu 15..0

P

DP

L

1

typ

A

B adres

bazowy 23..16

L limit segmentu 15..0

B

- adres bazowy segmentu

L

- d

ługość segmentu

G

- sposób interpretacji limitu segmentu (0 – bajty, 1 – strony 4KB),

DPL - poziom uprzywilejowania segmentu,

P

- bit obecno

ści segmentu (używany w pamięci wirtualnej),

AV - nie u

żywany,

A

- mówi czy deskryptor jest u

żywany.

Deskryptory s

ą przechowywane w dwóch rodzajach tablic:

•

globalnej tablicy deskryptorów GDT (ang. Global Descriptor Table)

•

lokalnej tablicy deskryptorów LDT (ang. Local Descriptor Table).

W systemie istnieje:

•

jedna tablica GDT - opisuje segmenty widoczne dla wszystkich

procesów

•

wiele lokalnych tablic deskryptorów LDT (ang. Local Descriptor

Table), opisuj

ących prywatne segmenty procesów

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 7

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

B - baza

L -dlugo

ść

A

-atrybuty

deskryptor segmentu

SE -selektor

D - przesuni

ęcie

+

pami

ęc RAM

segment S

czy D > L

EXC

wyj

ątek

komparator

...

tablica

desktyptorów

segmentów

adres liniowy

AL = B + D

L - dlugo

ść

segmentu

P - pocz

ątek

segmentu

adres logiczny

Rys. 1-6 Uproszczony schemat mechanizmu segmentacji

Adres logiczny sk

łada się z:

•

selektora segmentu SE

•

przesuni

ęcia D.

Funkcje selektora pe

łni jeden z rejestrów segmentowych:

•

dla kodu selektorem jest rejestr DS.,

•

dla danych rejestr DS.,

•

dla stosu SS.

indeks

deskryptora

TI

RPL

0

RPL - requested privilege level

TI - table indicator

2

3

4

15

Rys. 1-7 Zawarto

ść rejestru selektora segmentu

Selektor zawiera:

•

indeks deskryptora - po

łożenie segmentu znajdującego się w tablicy

deskryptorów,

•

TI

- okre

śla o którą tablicę chodzi (0 – GDT, 1 - LDT)

•

RPL

-

żądany poziom uprzywilejowania – określa poziom

uprzywilejowania procesu.

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 8

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

Adres liniowy - suma pobieranego z pola adresowego rozkazu

przesuni

ęcia D i adresu początku segmentu B pobieranego z

deskryptora.

Komparator sprawdza czy przesuni

ęcie D nie wykracza poza długość

segmentu L zapisanego w deskryptorze. Gdy tak si

ę zdarzy generowany

jest wyj

ątek EXC który powoduje wywołanie systemu operacyjnego.

System operacyjny podejmuje decyzj

ę, co zrobić z naruszającym

przydzielony segment procesem.

Adres liniowy mo

że być poddany przetwarzaniu przez mechanizm

stronicowania.

Ochrona obszarów pami

ęci używanych przez procesy

przed dost

ępem przez inny proces

Segmentacja

Zapewnienie przemieszczalno

ści programów

Realizacja pami

ęci wirtualnej większej niż fizyczna

Rozwi

ązanie problemu fragmentacji

Stronicowanie

Ochrona obszarów pami

ęci

Tab. 1-1 Mechanizmy sprz

ętowe zarządzania pamięcią

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 9

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

1.4.

Ochrona procesora

Aby system operacyjny móg

ł wykonywać swe funkcje powinien mieć on

dost

ęp do wszystkich istotnych zasobów procesora, mechanizmu

zarz

ądzania pamięcią, kontrolera przerwań i kontrolerów wejścia wyjścia.

Procesy aplikacyjne nie mog

ą mieć dostępu do tego typu zasobów, gdyż

czy to na skutek b

łędów czy intencjonalnie mogłyby zdestabilizować

prac

ę systemu.

We wspó

łczesnych mikroprocesorach wprowadza się dwa (lub więcej)

tryby pracy procesora:

•

tryb u

żytkownika (ang. User Mode)

•

tryb systemowy (ang. System Mode).

•

Tryb systemowy - proces mo

że wykonywać wszystkie instrukcje

procesora, si

ęgać do wszystkich obszarów pamięci i przestrzeni

wej

ścia wyjścia.

•

Tryb u

żytkownika - nie jest dozwolony dostęp do rejestrów:

zwi

ązanych z zarządzaniem pamięcią, obsługą przerwań

zarz

ądzaniem pracą procesora.

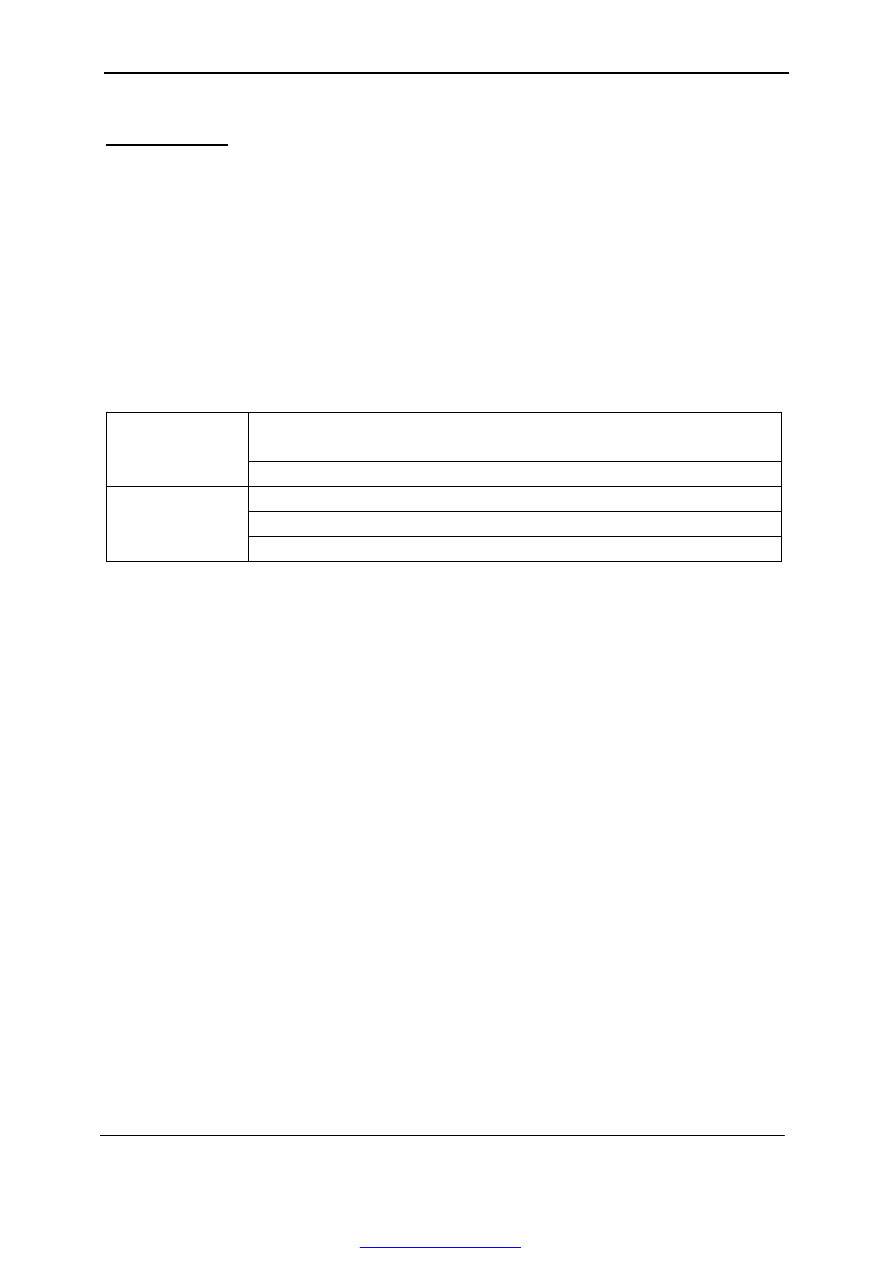

Poziomy uprzywilejowania

W mikroprocesorach o architekturze IA-32 ochrona procesora oparta jest

o koncepcj

ę poziomów ochrony (ang. Privilege Level).

Poziom 3 - procesy aplikacyjne

Poziom 2 - procesy zaufane

Poziom 1 - system operacyjny

Poziom 0 - j

ądro systemu

operacyjnego

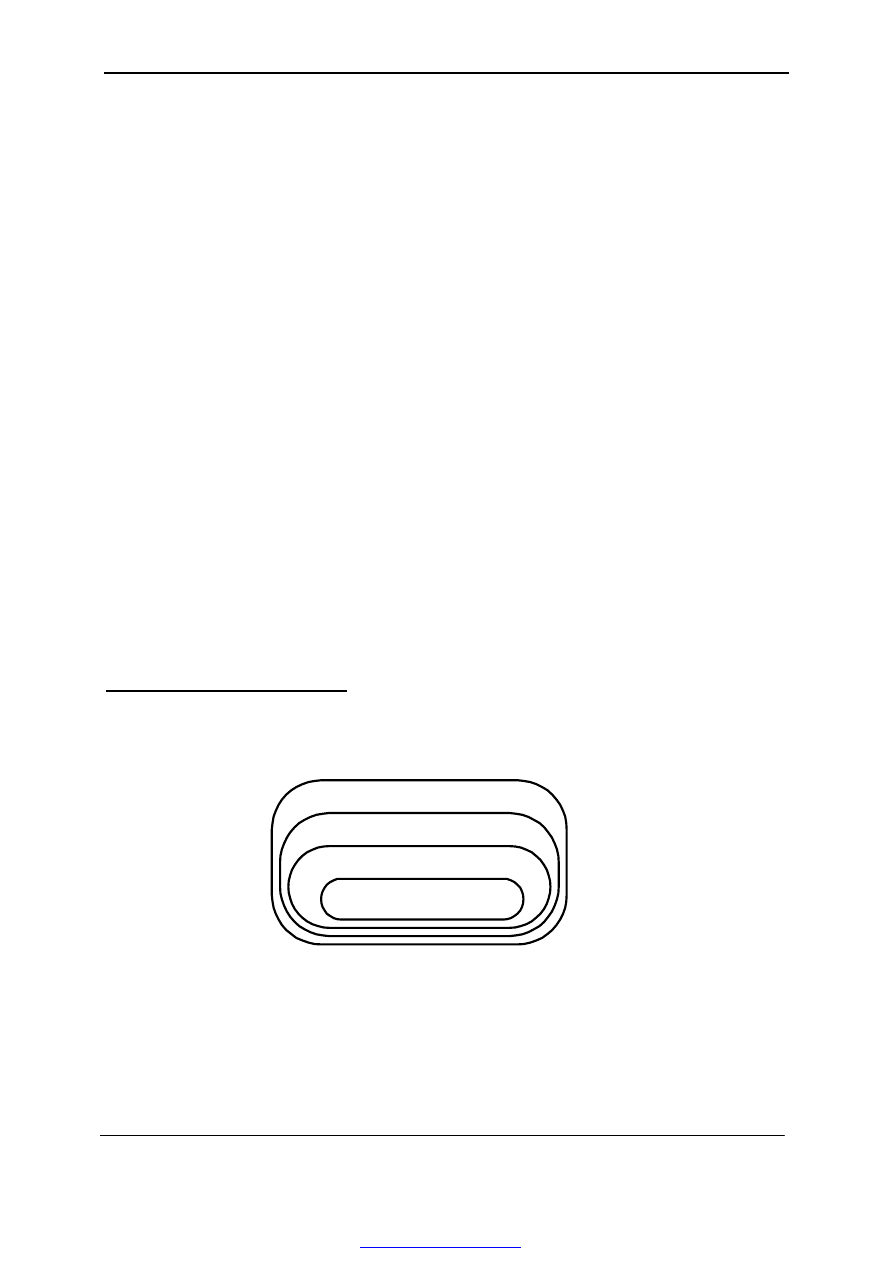

Rys. 1-8 Poziomy ochrony w mikroprocesorach Intel

Wykonywany w danej chwili proces charakteryzuje si

ę aktualnym

poziomem ochrony CPL (ang. Current Privilege Level) uzyskiwanym z

pola RPL selektora segmentu w którym zawarty jest kod bie

żącego

procesu.

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 10

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

Ka

żdy segment pamięci ma przyporządkowany poziom ochrony

zapami

ętany w polu DPL (ang. Descriptor Privilege Level) deskryptora

segmentu do którego odnosi si

ę żądanie.

Procesor ocenia prawa dost

ępu do segmentu poprzez porównanie

obecnego poziomu uprzywilejowania CPL do poziomu uprzywilejowania

jaki ma deskryptor segmentu do którego przyznany ma by

ć dostęp.

•

Przyznawany jest dost

ęp do danych o tym samym lub niższym

poziomie ochrony (mniej wa

żnych).

•

Dopuszczane jest wywo

ływanie procedur o tym samym lub wyższym

poziomie ochrony (bardziej godnych zaufania)

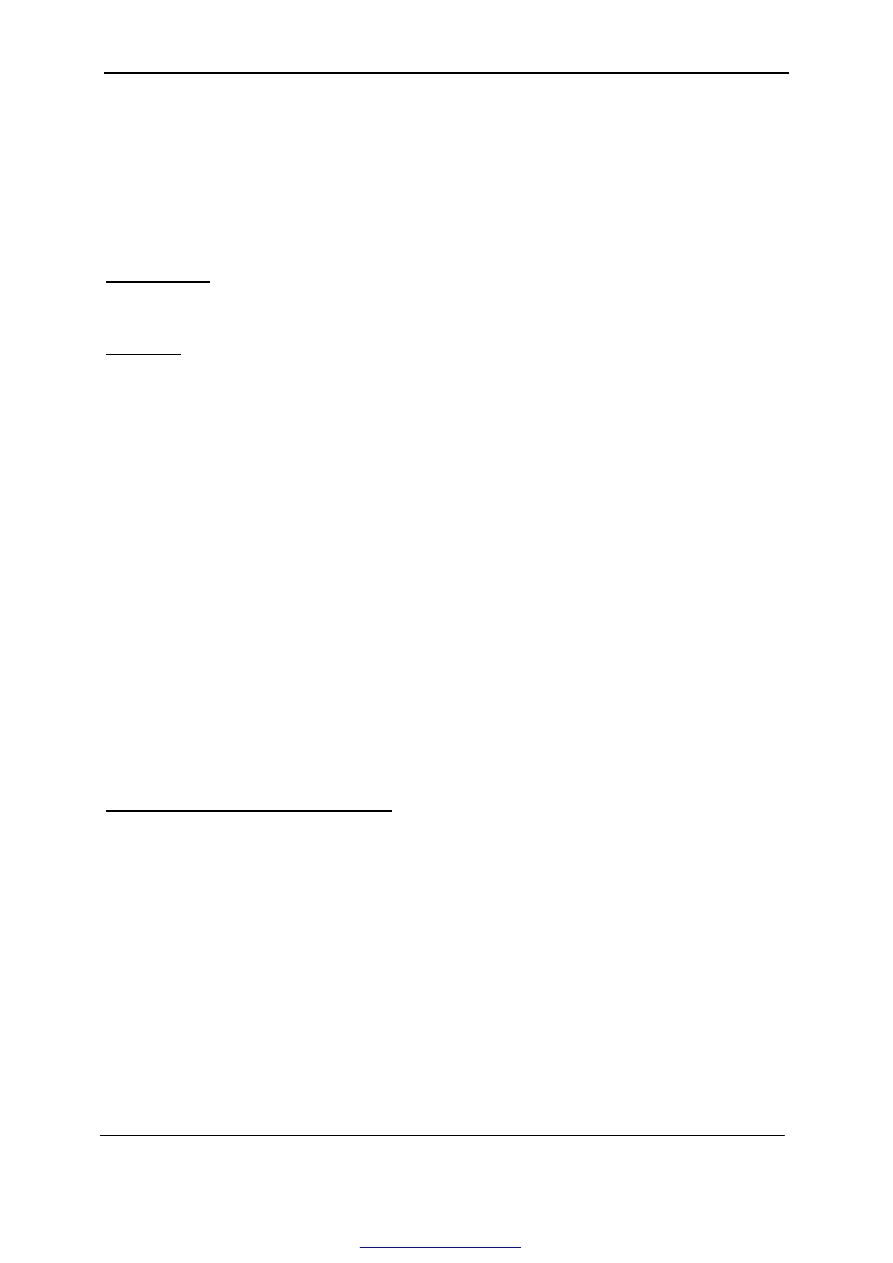

CPL

pami

ęc RAM

porównanie

CPL i DPL

EXC

wyj

ątek

tablica

desktyptorów

segmentów

selektor segmentu

DPL

segment

bie

żący poziom uprzywilejowania

poziom

uprzyw.

żądanego

segmentu

Rys. 1-9 Kontrola dost

ępu do żądanego segmentu kodu lub danych

Instrukcje systemowe

W

śród wszystkich instrukcji procesora wyróżnia się instrukcje

zarezerwowane dla systemu. S

ą to:

•

instrukcje dost

ępu do rejestrów systemowych,

•

ładowania tablic deskryptorów,

•

zatrzymywanie procesora,

•

zmiany niektórych flag.

Instrukcje systemowe mog

ą być wykonywanie tylko w trybie

uprzywilejowania CPL = 0. Gdy CPL procesu wykonuj

ącego instrukcję

systemow

ą jest różny od zera zostanie wygenerowany wyjątek.

Ochrona wej

ścia – wyjścia

•

pole IOPL

•

bitmapy

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 11

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

Pole IOPL

Pozwolenie na wykonywanie operacji wej

ścia wyjścia zależy od

zawarto

ści pola IOPL (ang. Input Output Privilege Level) wartość 0-3

zapisanego w rejestrze flag procesora. Gdy poziom uprzywilejowania

CPL procesu bie

żącego jest niższy od zawartości pola IOPL i następuje

próba wykonania instrukcji wej

ścia wyjścia generowany jest wyjątek.

Bitmapy

Dla ka

żdego zadania określona jest bitmapa zezwoleń dostępu (ang. I/O

Permission Bitmap). Okre

śla ona który adres z 64 KB przestrzeni wejścia

wyj

ścia może być przez bieżący proces użyty.

Kontrola dost

ępu do danych zawartych w innych niż

bie

żący segmentach

Poziomy

ochrony

Kontrola wywo

ływania procedur zawartych w innych niż

bie

żący segmentach

Instrukcje

systemowe

Zabezpieczenie istotnych funkcji procesora jak

zarz

ądzanie pamięcią, pamięcią, zatrzymywanie. Funkcje

dost

ępne tylko dla procesów wykonywanych z poziomu

j

ądra systemu operacyjnego (CLP= 0).

Pole IOPL

w rejestrze

znaczników

Okre

ślenie poziomu uprzywilejowania w którym mogą być

wykonywane instrukcje wej

ścia wyjścia.

Bitmapy

zezwole

ń

dost

ępu we

/ wy

Okre

ślenie adresów portów z przestrzeni wejścia wyjścia

które mog

ą być użyte przez proces.

Tab. 1-2 Zestawienie mechanizmów ochrony architektury IA-32

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 12

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

1.5.

Obs

ługa przerwań i wyjątków

Sekwencja wykonywanych rozkazów okre

ślona jest poprzez program.

Mo

że być ona jednak zmieniana na skutek zewnętrznego zdarzenia

zwanego przerwaniem, lub wewn

ętrznego zwanego wyjątkiem.

Przerwanie - reakcja na asynchroniczne zdarzenie powsta

łe na zewnątrz

procesora.

Wyj

ątek - powstaje przez detekcję przez procesor nienormalnego stanu

wewn

ętrznego.

W procesorze Intel 386 wyró

żnia się dwa źródła przerwań i dwa źródła

wyj

ątków.

Przerwania:

•

Przerwania maskowane które sygnalizowane s

ą procesorowi poprzez

sygna

ł na nóżce INTR. Odpowiadają one przerwaniom zgłaszanym

przez urz

ądzenia zewnętrzne.

•

Przerwania niemaskowalne (ang. Non-maskable Interrupt) które

sygnalizowane s

ą procesorowi poprzez sygnał na nóżce NMI.

Wyj

ątki :

•

Wyj

ątki wykryte przez procesor które dzielimy na błędy (ang. fault),

pu

łapki (ang. trap) i zaniechania (ang. abort).

•

Wyj

ątki wygenerowane programowo określane są jako pułapki i

nazywane te

ż przerwaniami programowymi.

Tablica deskryptorów przerwa

ń

Procesor

łączy z każdym przerwaniem i wyjątkiem pewien numer

identyfikacyjny z zakresu 0 do 255 nazywany numerem przerwania.

•

Dla cz

ęści wyjątków i przerwań numer identyfikacyjny jest z góry

zdefiniowany

•

Dla przerwa

ń maskowalnych nadawany jest przez zewnętrzny układ

programowalnego kontrolera przerwa

ń.

Przerwania 0-31 s

ą zarezerwowane dla wyjątków.

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 13

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

Powi

ązanie numeru identyfikacyjnego wyjątku czy przerwania z

procedur

ą jego obsługi następuje przez tablicę deskryptorów przerwań

IDT (ang. Interrupt Descriptor Table) nazywan

ą też tablicą wektorów

przerwa

ń. Położenie tej tablicy zawarte jest w rejestrze systemowym

IDTR (ang.

Interrupt Descriptor Table Register)

Tablica IDT zawiera

ć może trzy rodzaje deskryptorów:

•

bramk

ę przerwania (ang. Interrupt Gate),

•

bramk

ę pułapki (ang. Trap Gate)

•

bramk

ę zadania (ang. Task Gate).

przesuni

ęcie 31..16

selektor

P DPL

0001

nie

u

żywane

przesuni

ęcie 15..0

000

T/I

Rys. 1-10 Format deskryptora bramki przerwania i pu

łapki

Gdy bit T/I jest ustawiony to deskryptor odnosi si

ę do bramki pułapki a

gdy nie do bramki przerwania.

Wektor Opis

Typ

0

Dzielenie przez 0

B

łąd

1

Zarezerwowane

B

łąd, pułapka

2

Przerwanie NMI

Przerwanie

3

Punkt wstrzymania INT3

Pu

łapka

4

Nadmiar

Pu

łapka

...

...

8

Podwójny b

łąd

Zaniechanie

10

B

łędny segment stanu zadania TSS Błąd

11

Segment nieobecny

B

łąd

12

B

łąd segmentu stosu

B

łąd

13

Ogólny b

łąd ochrony

B

łąd

14

B

łąd strony

B

łąd

...

...

20-31

Zarezerwowane

32-255 Przerwanie zewn

ętrzne

Przerwanie

Tab. 1-3 Niektóre przerwania i wyj

ątki trybu chronionego dla

architektury IA-32

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 14

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

Przebieg obs

ługi przerwania lub wyjątku

Wyst

ąpienie przerwania lub wyjątku któremu odpowiada umieszczona w

tablicy IDT bramka przerwania lub wyj

ątku powoduje działanie podobne

do wywo

łania procedury wykonywanej w kontekście zadania bieżącego.

Umieszczony w deskryptorze selektor wskazuje na segment w którym

zawarta jest procedura obs

ługi wyjątku lub przerwania.

Przesuni

ęcie wskazuje na adres procedury która ma się wykonać.

Po zako

ńczeniu handlera następuje powrót do przerwanego zadania.

tablica GDT lub LDT

deskryptor segm.

segment kodu

procedury

obs

ługi

przerwania lub

wyjatku

bramka przerw.

IDT tablica

deskryptorów przerwa

ń

numer

przerwania

selektor

segmentu

przesuni

ęcie

handler obs

ługi

przerwania

adres

bazowy

IDTR

Rys. 1-11 Wywo

łanie procedury obsługi przerwania lub wyjątku

Gdy numer przerwania wskazuje na deskryptor IDT który jest bramk

ą

zadania to obs

ługa przerwania podobna jest do wywołania zadania na

które wskazuje umieszczony w deskryptorze selektor.

Obs

ługa wyjątków

Wyj

ątki powodowane są przez wykonywany właśnie program.

Architektura IA-32 wyró

żnia następujące źródła wyjątków:

•

b

łąd w programie,

•

przerwania programowe

•

wyj

ątek powodowany przez błąd sprzętowy.

Wyj

ątki dzielimy na:

•

b

łędy ,

•

pu

łapki,

•

zaniechania.

B

łąd wykrywany jest zanim instrukcja go powodująca zostanie

wykonana. Procedura obs

ługi błędu może poprawić błąd i program może

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 15

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

by

ć kontynuowany. Po zakończeniu procedury obsługi wyjątku

sterowanie wraca do instrukcji która go spowodowa

ła.

Przerwanie programowe INT n (pu

łapka) powoduje zgłoszenie wyjątku

zaraz po wykonaniu instrukcji INT. Po zako

ńczeniu procedury jego

obs

ługi sterowanie przekazywane jest do instrukcji następnej.

Zaniechania zg

łaszane są gdy nie da się precyzyjnie zlokalizować

po

łożenia błędu i program nie może być kontynuowany (błędy sprzętowe

i b

łędy w tablicach systemowych).

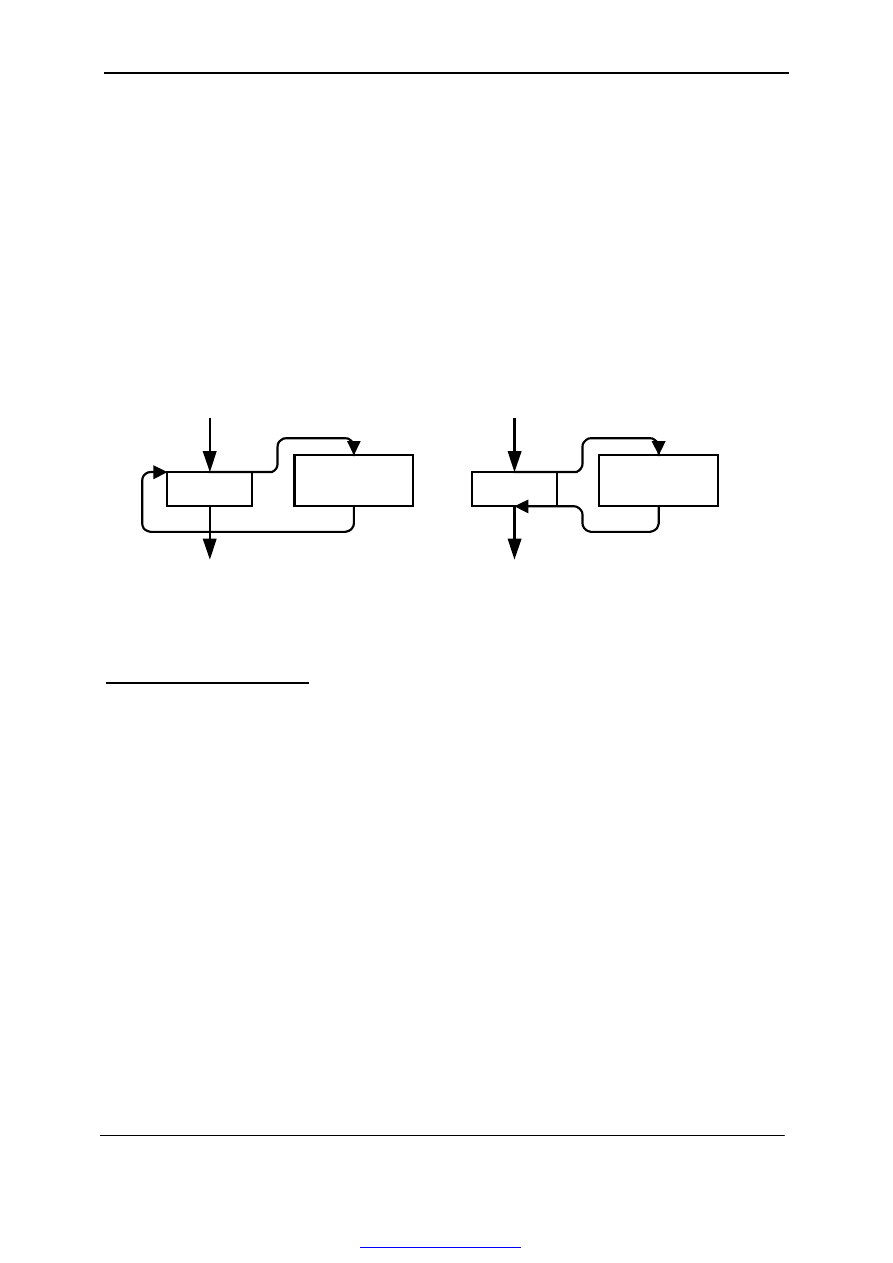

sekwencja instrukcji okre

ślona programem

instrukcja

Obs

ługa

wyj

ątku

INT n

Obs

ługa

pu

łapki

A) obs

ługa

wyj

ątku

B) obs

ługa

pulapki

Rys. 1-12 Obs

ługa wyjątku i przerwania programowego (pułapki)

Przerwania sprz

ętowe

Przerwania sprz

ętowe dzielimy na

•

maskowalne

•

niemaskowalne.

W komputerze wyst

ępuje konieczność obsługi wielu przerwań, podczas

gdy procesor zazwyczaj zawiera tyko jedno wej

ście przerywające.

Wyst

ępuje konieczność użycia urządzenia nazywanego kontrolerem

przerwa

ń (ang. Interrupt Controller).

Funkcje kontrolera przerwa

ń:

•

Rozstrzyganie konfliktu w przypadku wyst

ąpienia wielu przerwań.

•

Tworzenia powi

ązania pomiędzy nóżkami układu na których pojawiają

si

ę przerwania a numerami identyfikacyjnymi przerwań.

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 16

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

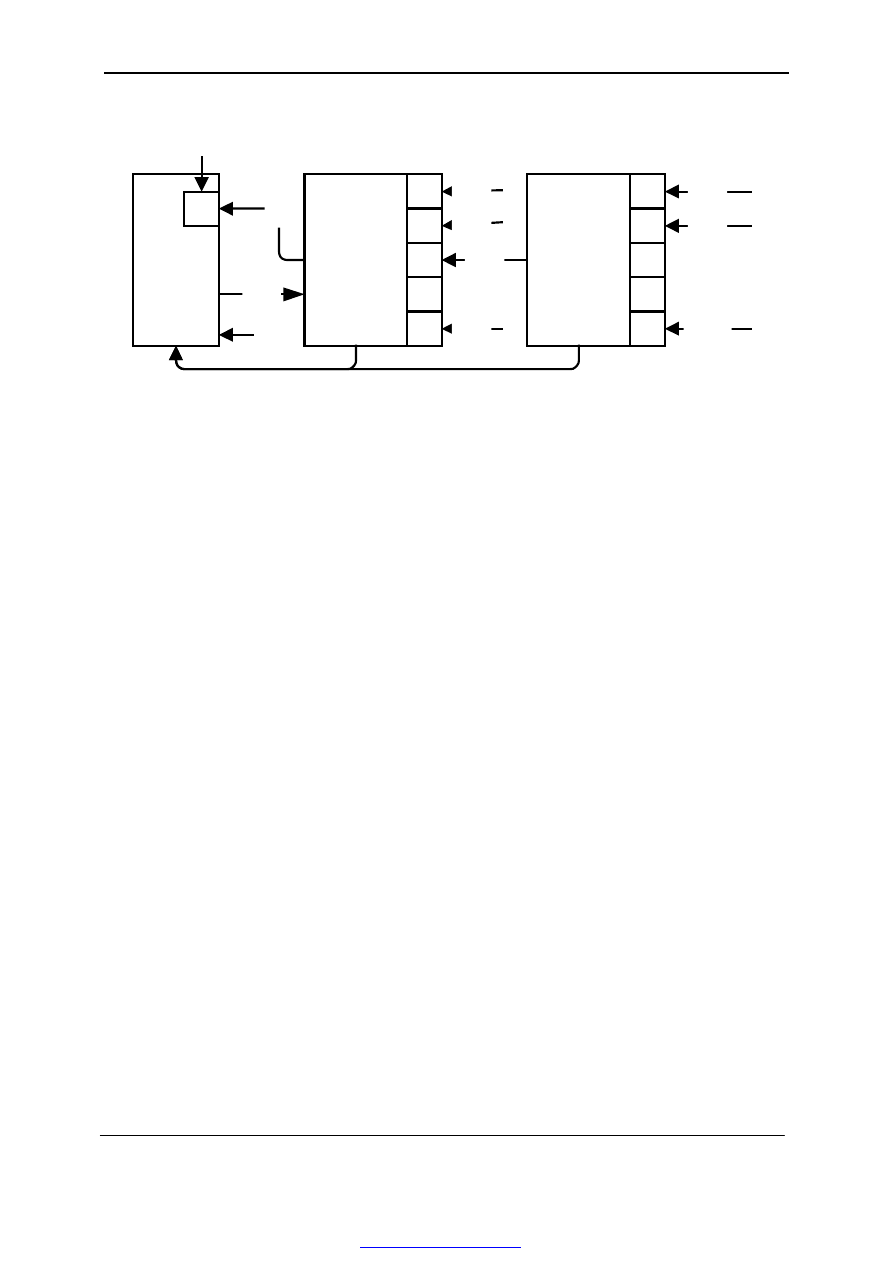

Procesor

Kontroler

przerwa

ń

Master

M7

IRQ0

IRQ1

IRQ7

IRQ0 - IRQ15 linie zg

łaszania przerwań

M0

M1

M2

Kontroler

przerwa

ń

Slave

M7

IRQ8

IRQ9

IRQ15

M0

M1

M2

IRQ2

blokowanie przerwa

ń

M0 - M7 bity rejestru maski przerwa

ń

INTA

IF

INT

NMI

numer przerwania

Rys. 1-13 Kontroler g

łówny i podrzędny w komputerze PC

Kontroler przerwa

ń posiada dwa rejestry umieszczone w przestrzeni

wej

ścia wyjścia:

•

rejestr steruj

ący CR (ang. Control Register)

•

rejestr maski przerwa

ń M (ang. Interrupt Mask Register).

Rejestr steruj

ący CR służy do programowania kontrolera a rejestr maski

M umo

żliwia indywidualne blokowanie poszczególnych linii zgłaszania

przerwa

ń.

Obs

ługa przerwania:

•

Urz

ądzenie sygnalizuje przerwanie poprzez wystawienie sygnału na

linii zg

łaszania IRQ

i

.

•

Kontroler przerwa

ń decyduje czy przerwanie i może być przyjęte. Gdy

jest ono zamaskowane nie b

ędzie przyjęte. Gdy właśnie obsługiwane

jest przerwanie o tym samym lub wy

ższym priorytecie to zgłoszenie

musi poczeka

ć do zakończenia obsługi bieżącego przerwania. Gdy

przerwanie mo

że być przyjęte kontroler wystawia do procesora sygnał

INTR.

•

Po zako

ńczeniu bieżącego cyklu rozkazowego procesor sprawdza

stan nó

żki INTR. Gdy flaga IF jest ustawiona przerwanie będzie

przyj

ęte. Procesor potwierdza przerwanie sygnałem INTA w

odpowiedzi na co kontroler przesy

ła numer przerwania n = baza + i.

•

Procesor sprawdza zawarto

ść wektora n tablicy IDT. W zależności od

jej zawarto

ści uruchamia zadanie obsługi przerwania lub procedurę

obs

ługi przerwania.

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 17

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

•

W ramach obs

ługi przerwania testowane są rejestry urządzeń

skojarzonych z danym przerwaniem. Znajdowana jest przyczyna

przerwania i wykonywana jest jego obs

ługa.

•

Po zako

ńczeniu obsługi przerwania procesor wysyła informację o tym

do kontrolera w postaci polecenie EOI (ang. End Of Interrupt).

•

Przywracany jest kontekst przerwanego procesu.

Typ przerwania

Funkcja

W

łasności

Przerwania

maskowalne

Obs

ługa zdarzeń zewnętrznych

Asynchroniczne

Przerwania

niemaskowalne

Obs

ługa zdarzeń awaryjnych

Asynchroniczne

Wyj

ątki

Obs

ługa błędów programów

Synchroniczne

Pu

łapki

Wywo

łania systemu, programy

uruchomieniowe operacyjnego

Synchroniczne

Tab. 1-4 Rodzaje przerwa

ń w mikroprocesorach architektury IA-32

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 18

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

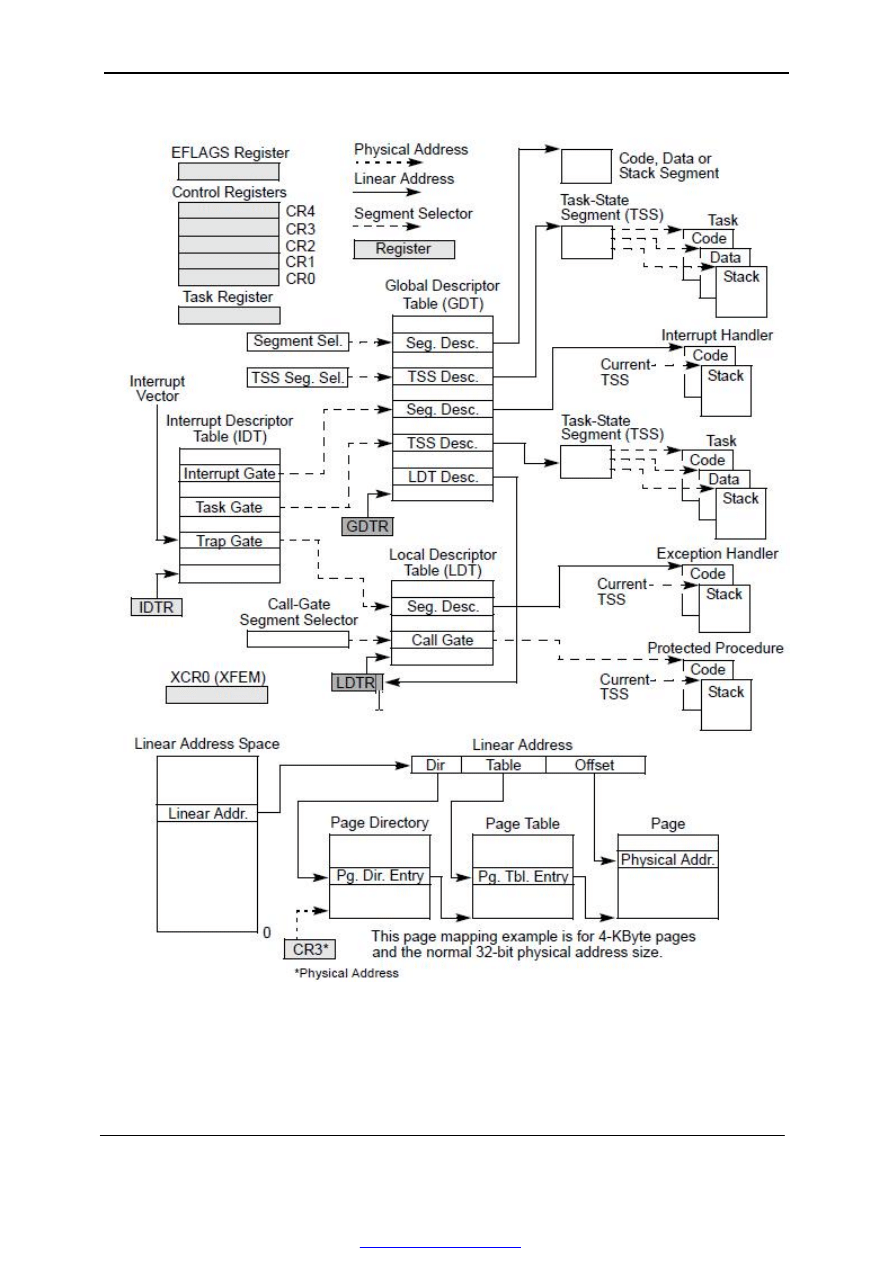

Kontrolery wej

ścia wyjścia

System wej

ścia wyjścia zapewnia dostęp do urządzeń zewnętrznych.

Zapewnia on tak

że komunikację z użytkownikiem.

System wej

ścia wyjścia składa się z urządzeń i obsługujących je

kontrolerów pod

łączonych do magistrali komputera.

Procesor

Pami

ęć

Kontroler

przerwa

ń

Zegar

Kontroler

we / wy

K

Kontroler

we / wy

1

IRQ 0

IRQ 1

IRQ K

INT

Magistrala

urz

ądzenie 1

urz

ądzenie K

. . .

Kontroler

DMA

magistrala urz

ądzenia

Rys. 1-14 Uproszczony schemat komputera jednoprocesorowego.

Kontrolery wej

ścia wyjścia

Kontroler wej

ścia wyjścia pełni rolę pośrednika pomiędzy urządzeniem,

procesorem i pami

ęcią operacyjną:

•

z jednej strony do

łączony jest on zwykle do magistrali komputera (np.

magistrali PCI)

•

z drugiej strony do magistrali urz

ądzenia (np. magistrali USB czy

SCSI)

Kontroler sk

łada się z kilku rejestrów umieszczonych w przestrzeni

wej

ścia wyjścia. Zwykle jest to:

•

rejestr wej

ściowy,

•

wyj

ściowy,

•

statusowy,

•

danych.

Przyk

ład - kontroler transmisji szeregowej zgodnego z układem 8250

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 19

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

Wi

ększość stosowanych obecnie kontrolerów wejścia wyjścia może

sygnalizowa

ć przerwaniem takie zdarzenia jak:

•

pojawienie si

ę nowych danych do odczytu,

•

zako

ńczenie wysyłania danych zapisywanych,

•

zmiana statusu,

•

wyst

ąpienie błędu.

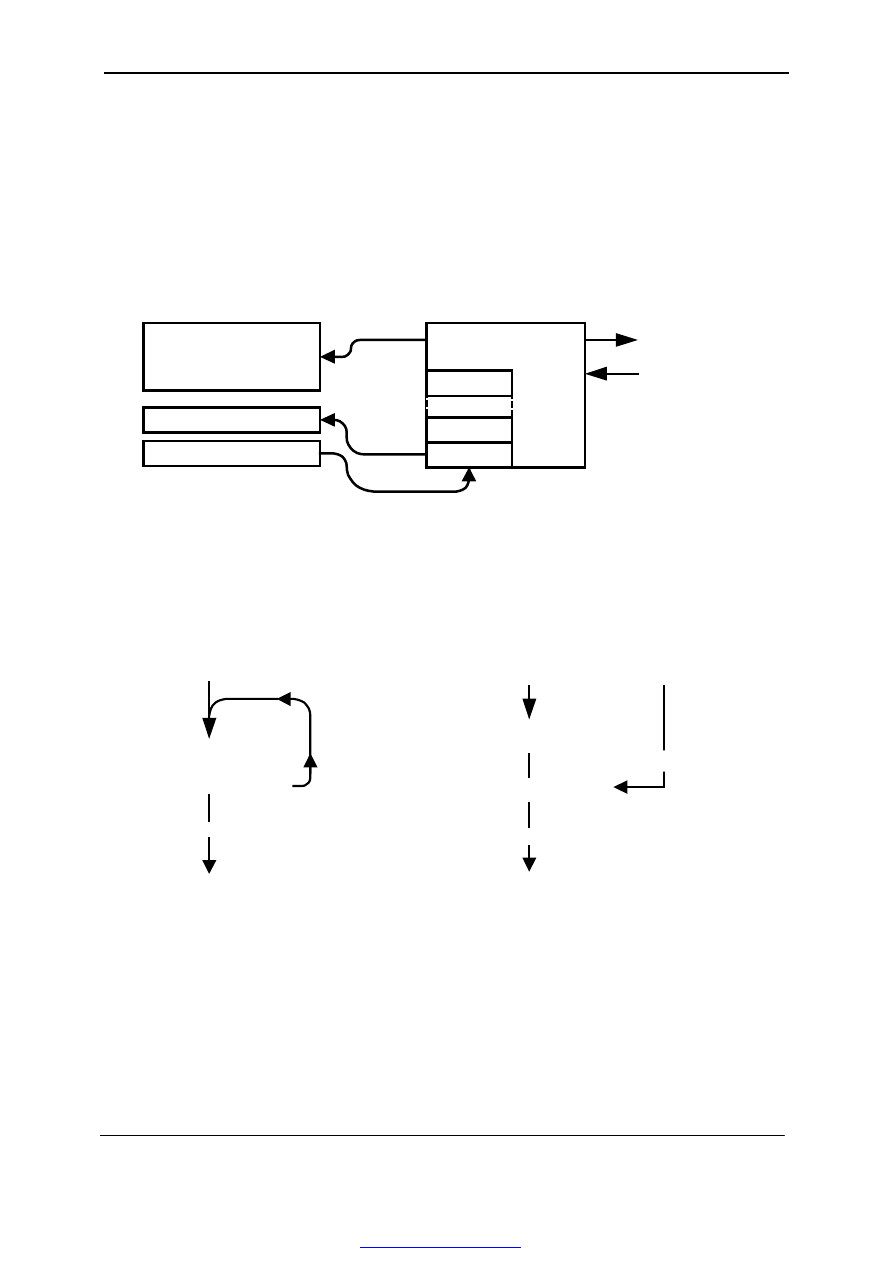

Bufor odbiorczy

Bufor nadawczy

RX

TX

R0

...

R7

znaki wysy

łane

znaki odbierane

kontroler

przerwa

ń

uk

ład 8250

IRQ3

R1

Rys. 1-15 Kontroler transmisji szeregowej

Odczyt znaku z kontrolera mo

żliwy jest w dwóch trybach:

•

trybie odpytywania,

•

trybie przerwa

ń.

czy znak dost

ępny ?

odczyt statusu

nie

odczyt znaku

tak

programowanie

kontrolera

czekaj na

przerwanie

INT

odczyt znaku

a) Tryb odpytywania

b) Tryb przerwa

ń

Rys. 1-16 Odczyt znaku z kontrolera wej

ścia wyjścia

PDF created with pdfFactory trial version

J. U

łasiewicz Komputerowe systemy sterowania 20

Instytut Cybernetyki Technicznej Politechniki Wroc

ławskiej

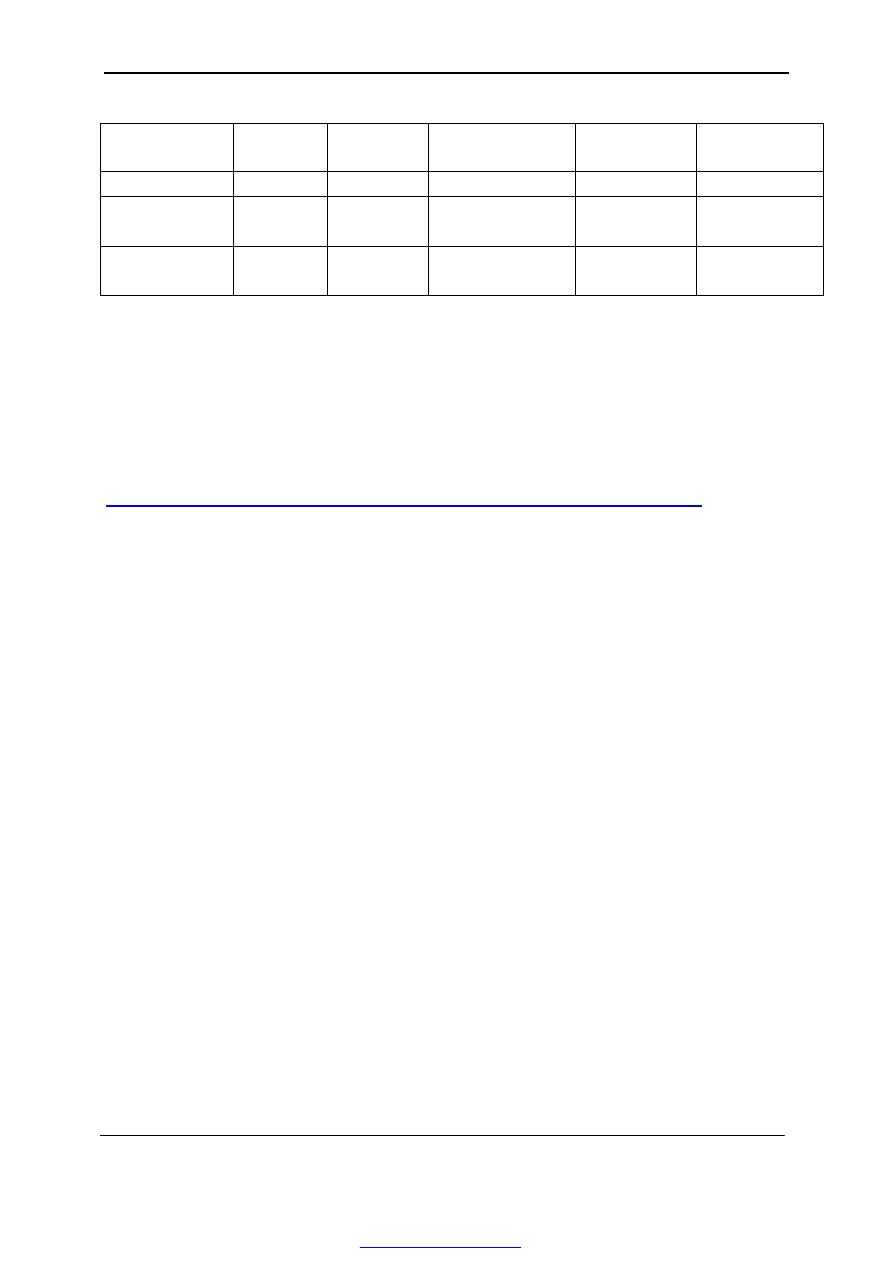

Tryb pracy

Procesor Szybko

ść Wykorzystanie

sprz

ętu

Wsparcie

sprz

ętowe

Wsparcie

programowe

Odpytywanie Zaj

ęty

Ma

ła

Ma

łe

-

-

Tryb

przerwa

ń

Wolny

Średnia Średnie

Przerwania Procesy

Transmisja

blokowa

Wolny

Du

ża

Du

że

Przerwania,

uk

ład DMA

Procesy

Tab. 1-5 Porównanie metod transmisji danych pomi

ędzy pamięcią a

kontrolerem urz

ądzenia wejścia wyjścia

2. Literatura

[1] Intel® 64 and IA-32 Architectures Software Developer’s Manual

Volume 3 System Programming Guide, Intel

http://download.intel.com/products/processor/manual/325384.pdf

PDF created with pdfFactory trial version

Wyszukiwarka

Podobne podstrony:

architektura aplikacji id 67748 Nieznany (2)

Architektura Neutrino 1 id 6791 Nieznany (2)

Architektura Komp2 id 67910 Nieznany (2)

Architektura ekoczasu id 67766 Nieznany (2)

ARCHITEKTURA KOMPUTEROW id 6779 Nieznany (2)

Architektura Renesansu id 67864 Nieznany (2)

Architektura drewniana 2 id 677 Nieznany (2)

architektura aplikacji id 67748 Nieznany (2)

Architektura5 id 67923 Nieznany (2)

Architektura3 id 67919 Nieznany (2)

Architektura4 id 67920 Nieznany (2)

Architektura2 id 67918 Nieznany

5 Architektura MCU 2010 id 4004 Nieznany (2)

ArchitekturaKomputera2 id 67926 Nieznany (2)

Architektura6 id 67924 Nieznany (2)

ArchitekturaKomputera id 67925 Nieznany

PEK PB OPIS ARCHITEKTURA id 354 Nieznany

Architektura1 id 67917 Nieznany (2)

Architektura5 id 67923 Nieznany (2)

więcej podobnych podstron