MAGISTRALE SYSTEMOWE

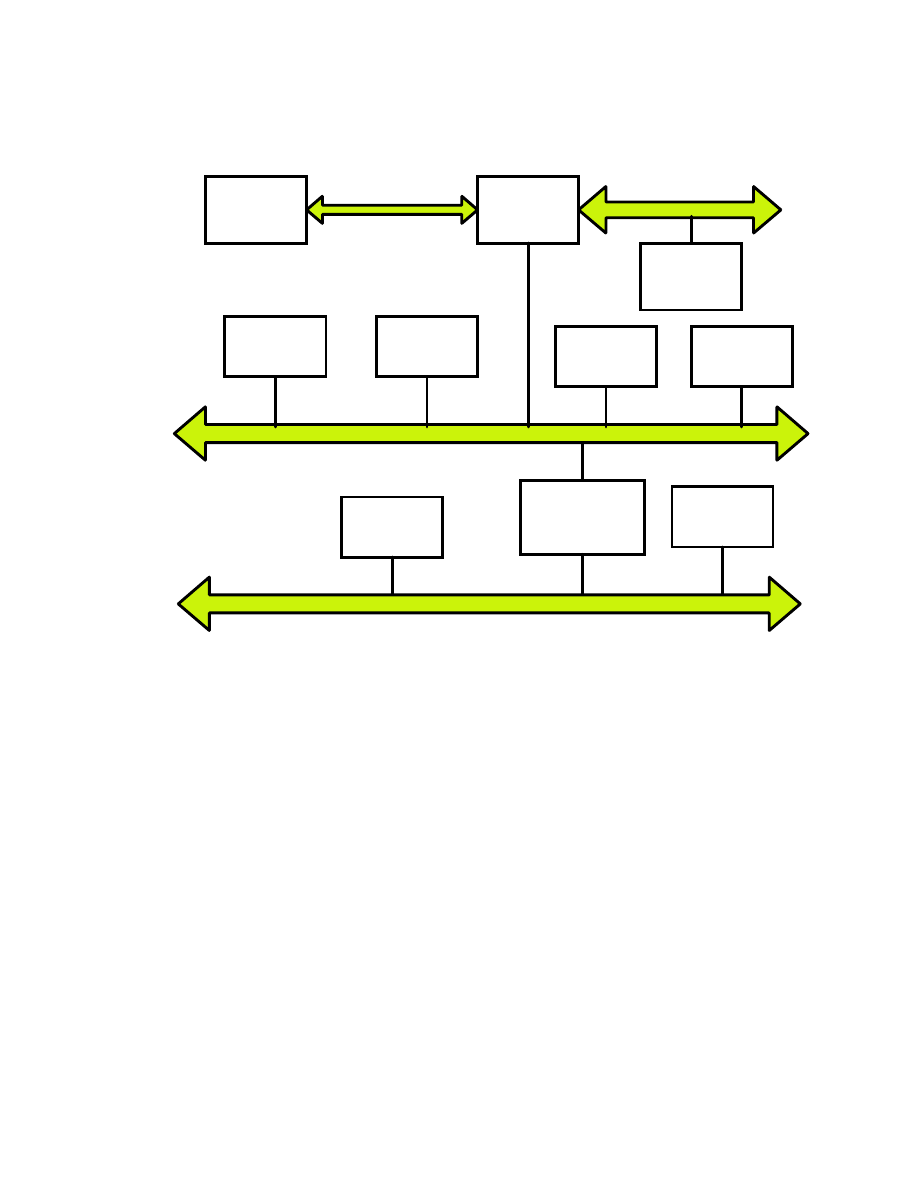

Struktura magistrali

Linie danych

MAGISTRALA

CPU

Wejście-

wyjście

Pamięć

Wejście-

wyjście

Linie sterowania

Linie adresowe

Linie danych są ścieżkami służącymi do przenoszenia danych między

modułami systemu. Wszystkie te linie łącznie określa się jako szyna danych.

Szyna składa się typowo z 8, 16, 32, 64 oddzielnych linii, liczba linii określa

szerokość tej szyny i jest kluczowym czynnikiem określającym wydajność.

Linie adresowe są wykorzystywane do określania źródła lub miejsca

przeznaczenia danych przesyłanych przez magistralę (adres słowa pamięci,

adres portu we-wy). Najczęściej najbardziej znaczące bity służą do wybrania

określonego modułu na magistrali, natomiast najmniej znaczące bity określają

lokację w pamięci lub port wejścia – wyjścia wewnątrz modułu.

Linie sterowania przeznaczone są do sterowania dostępem do linii danych

i linii adresowych, a także do sterowania ich wykorzystaniem. Sygnały sterujące

przekazywane między modułami systemu zawierają zarówno rozkazy, jak

i informacje regulujące czas (sygnały taktujące).

Typowe linie sterowania:

!"

Zapis w pamięci;

!"

Odczyt z pamięci;

!"

Zapis do wejścia – wyjścia;

!"

Odczyt z wejścia – wyjścia;

!"

Potwierdzenie przesyłania (transfer ACK);

!"

Zapotrzebowanie na magistralę (bus request);

!"

Rezygnacja z magistrali (bus grant);

!"

Żądanie przerwania (interrupt request);

!"

Potwierdzenie przerwania (interrupt ACK);

!"

Zegar;

!"

Przywrócenie stanu początkowego (reset).

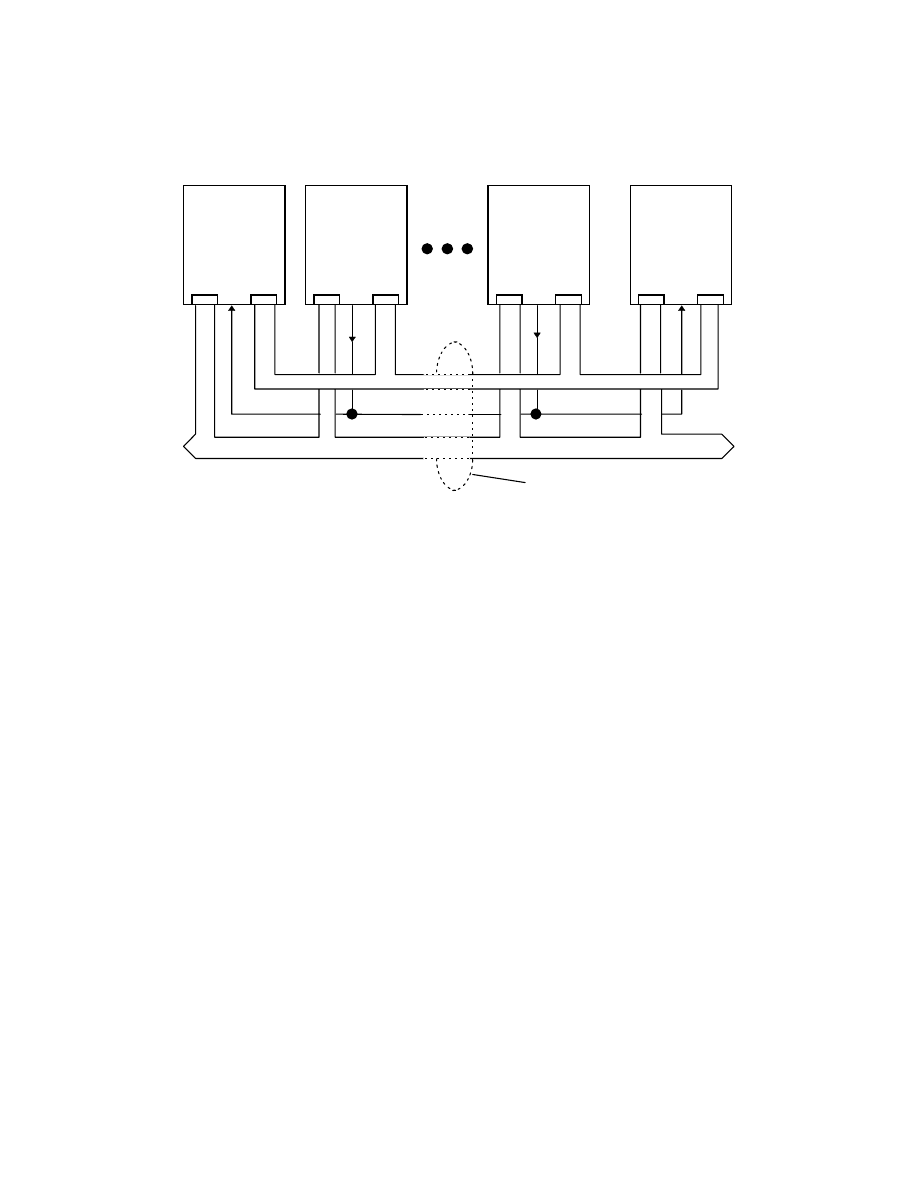

Magistrala typu wspólna szyna

Magistrala systemowa we / wy

ADAPTER

ADAPTER

ADAPTER

KLAWIATURA

MONITOR

DYSK

TERMINATOR

TERMINATOR

TERMINATOR

MIKRO-

PROCESOR

Wszystkie urządzenia dołączone są do wspólnej szyny poprzez adaptery -

jednostki sterujące. W tego typu systemach, każde urządzenie (a właściwie jego

adapter) ma wydzieloną grupę adresów występujących na liniach adresowych

magistrali. Pod tymi adresami dostępne są programowe rejestry urządzeń.

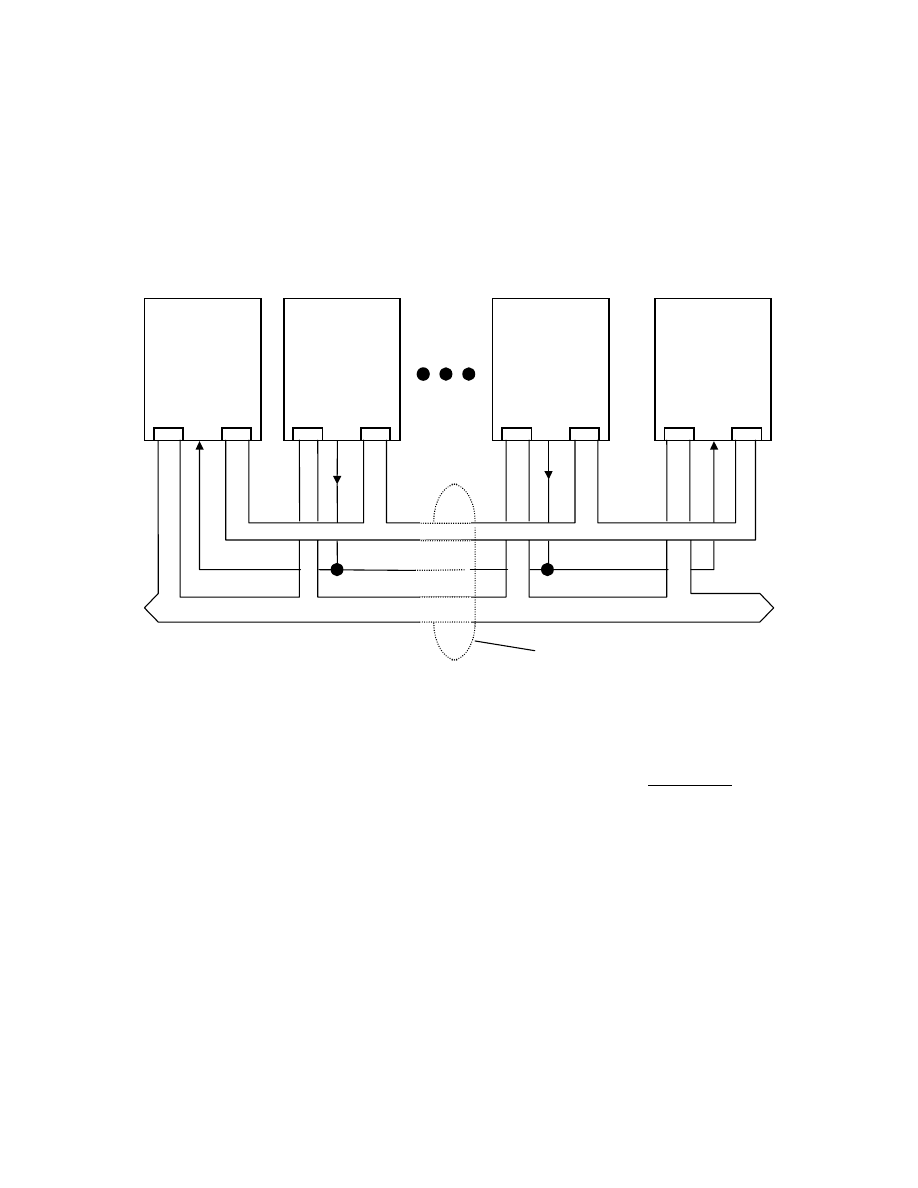

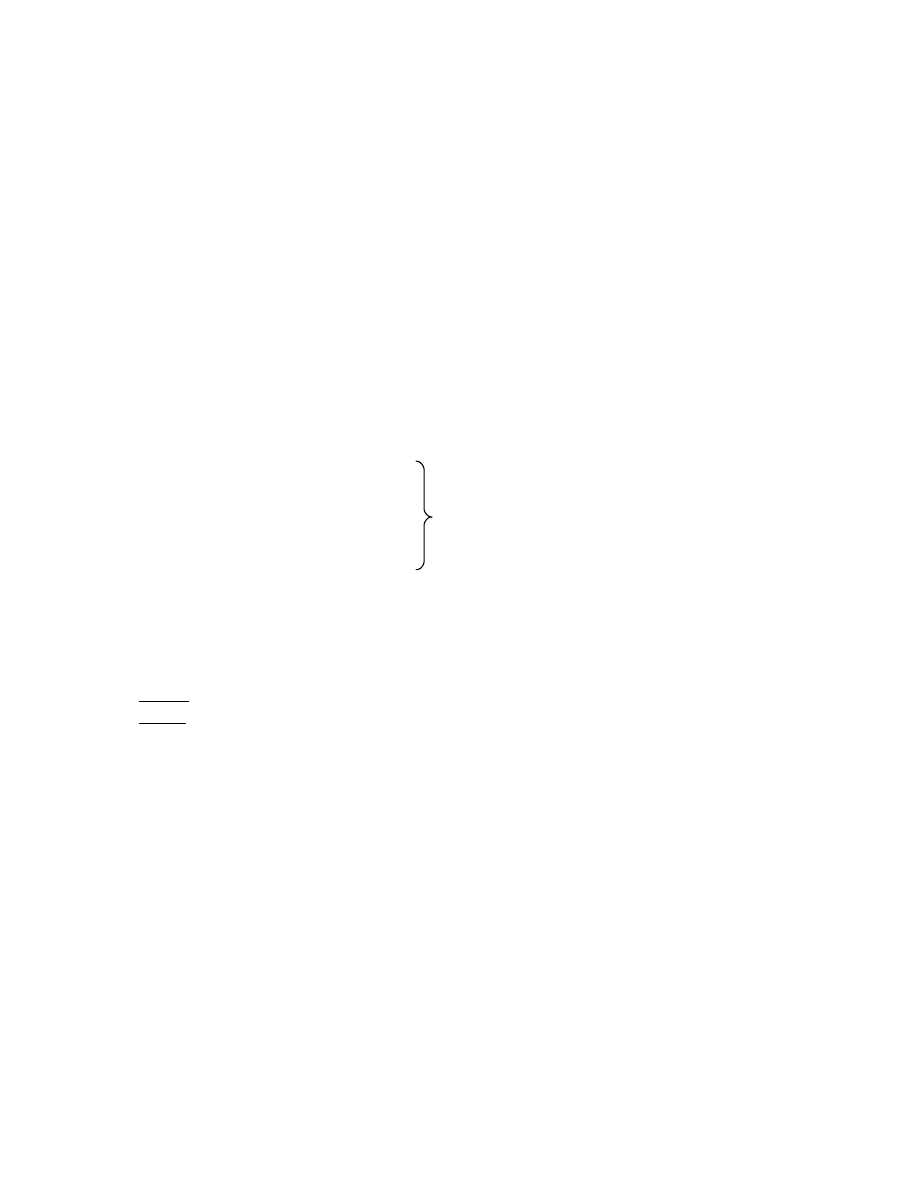

Magistrala VME

VMEbus

W skrócie: VMEbus

MASTER

1

P1

P2

MASTER

2

P1

P2

SLAVE

#1

P1

P2

SLAVE

#n

P1

P2

VMXbus

VMSbus

System szyn VME: MASTER 1, 2 - procesory główne; SLAVE 1...n - adaptery urządzeń we/wy,

pamięci dodatkowe, procesory podrzędne.

Ponieważ szyna VMEbus jest „najważniejszą” w systemie szyn VME i jest

w pełnie zdefiniowana, jej nazwa obejmuje również szyny VMSbus i VMXbus

i w takim znaczeniu jest używana. Szyna VMEbus jest szyną asynchroniczną,

wieloprocesorową, wykorzystywaną w systemach opartych na procesorach

rodziny MC6800. Układ arbitra szyny znajduje się na pakiecie jednego

z procesorów głównych (MASTER), udostępniając szynę również pozostałym

procesorom.

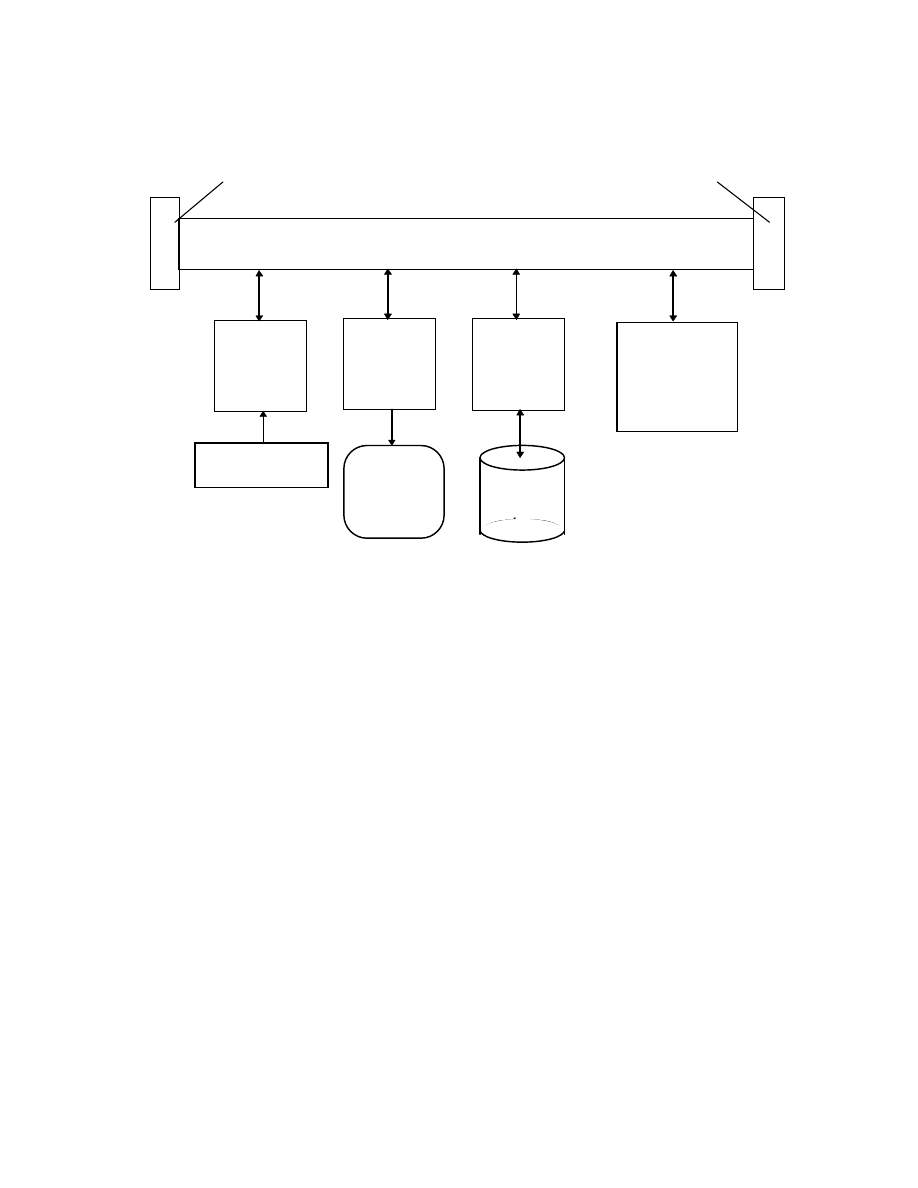

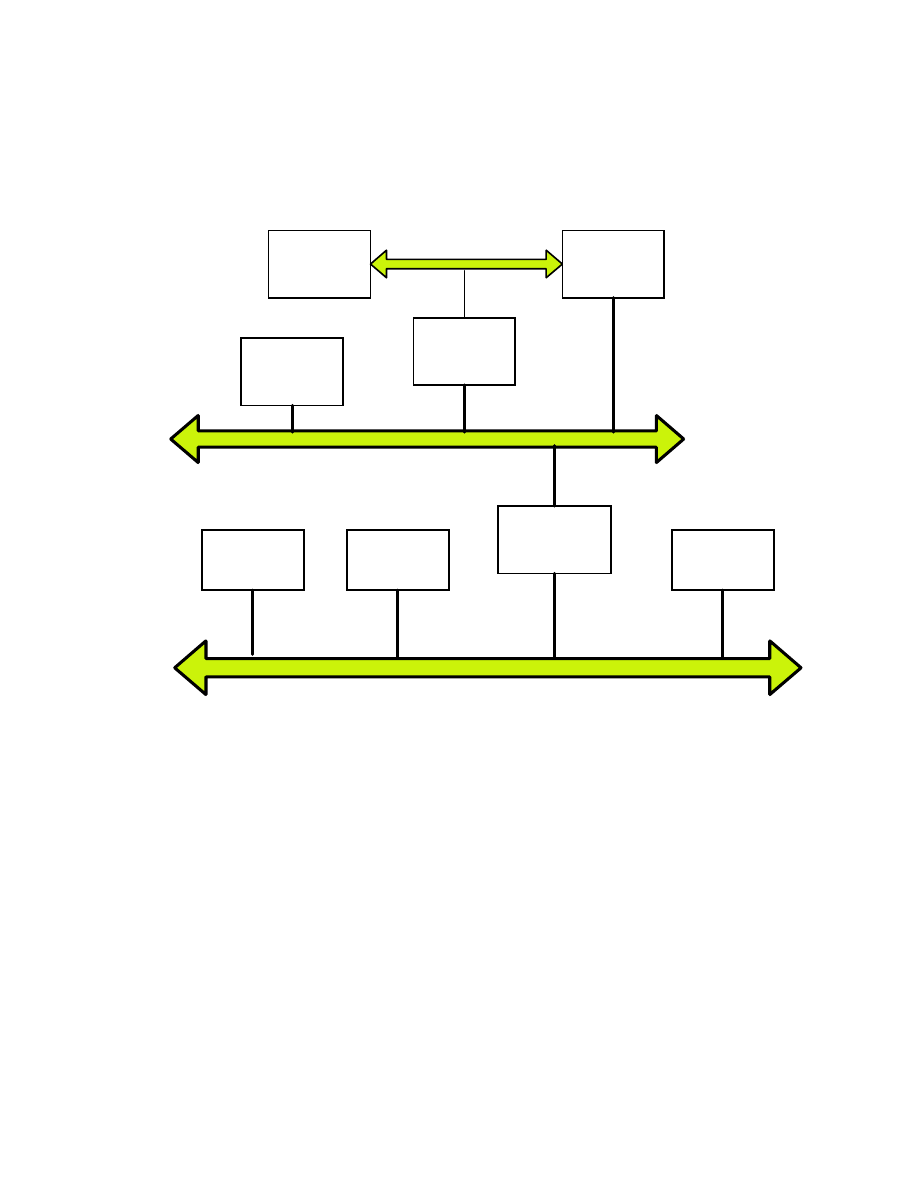

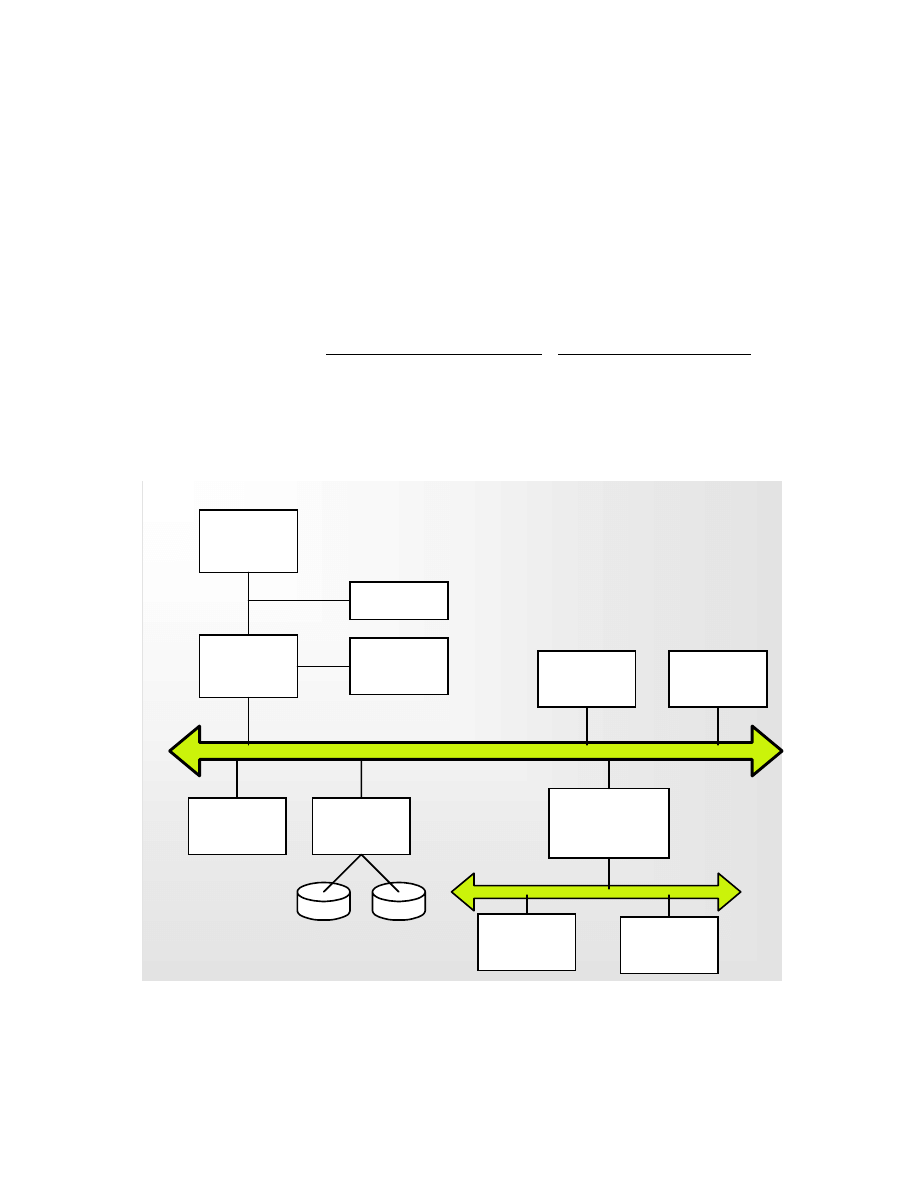

Hierarchiczne struktury wielomagistralowe

a) Tradycyjna architektura magistralowa

P rocesor

M agistrala system ow a

P am ięć

podręczna

M agistrala

lokalna

P am ięć

glów na

Lokalny

sterow nik

w ejścia-

w yjścia

S zyna rozszerzeń

S ieć

S C S I

Interfejs

szyny

rozszerzenia

P ort

szeregow y

b) Architektura magistralowa o zwiększonej wydajności

Procesor

M agistrala szybkiego przesylania

Pam ięć

podręczna/

m ost

M agistrala

lokalna

Pam ięć

glówna

Szyna rozszerzeń

G rafika

Sieć

Interfejs

szyny

rozszerzenia

Port

szeregowy

M agistrala system ow a

SC SI

Video

M odem

Parametry projektowe magistrali:

!"

Rodzaj:

specjalistyczna

multipleksowana

!"

Metoda arbitrażu:

centralna

rozproszona

!"

Koordynacja czasowa:

synchroniczna

asynchroniczna

!"

Szerokość magistrali

adres

dane

!"

Rodzaj transferu danych

odczyt

zapis

odczyt - modyfikacja - zapis

odczyt po zapisie

blokowy

Linie specjalistyczne są trwale przypisane albo jednej funkcji, albo fizycznie

określonym zespołom komputera.

Metoda używania tych samych linii do wielu celów jest znana jako

multipleksowanie czasowe.

Zalety: mniejsza liczba linii (oszczędza miejsce i koszt).

Wady: wymagane bardziej złożone układy, zmniejszenie wydajności.

W scentralizowanym układzie arbitrażu istnieje jedno urządzenie, zwane

sterownikiem magistrali albo arbitrem, które jest odpowiedzialne za

gospodarowanie czasem przydziału magistrali.

W rozproszonym układzie arbitrażu każdy moduł zawiera układy logiczne

sterujące dostępem, a moduły współpracują korzystając ze wspólnej magistrali.

operacje niepodzielne

Koordynacja czasowa

Koordynacja czasowa odnosi się do sposobu, w jaki porządkowane są zdarzenia

na magistrali.

Przy koordynacji synchronicznej występowanie zdarzeń na magistrali jest

wyznaczane przez zegar. Wszystkie urządzenia dołączone do magistrali mogą

odczytywać stan linii zegarowej, a wszystkie zdarzenia rozpoczynają się

równocześnie z cyklem zegara.

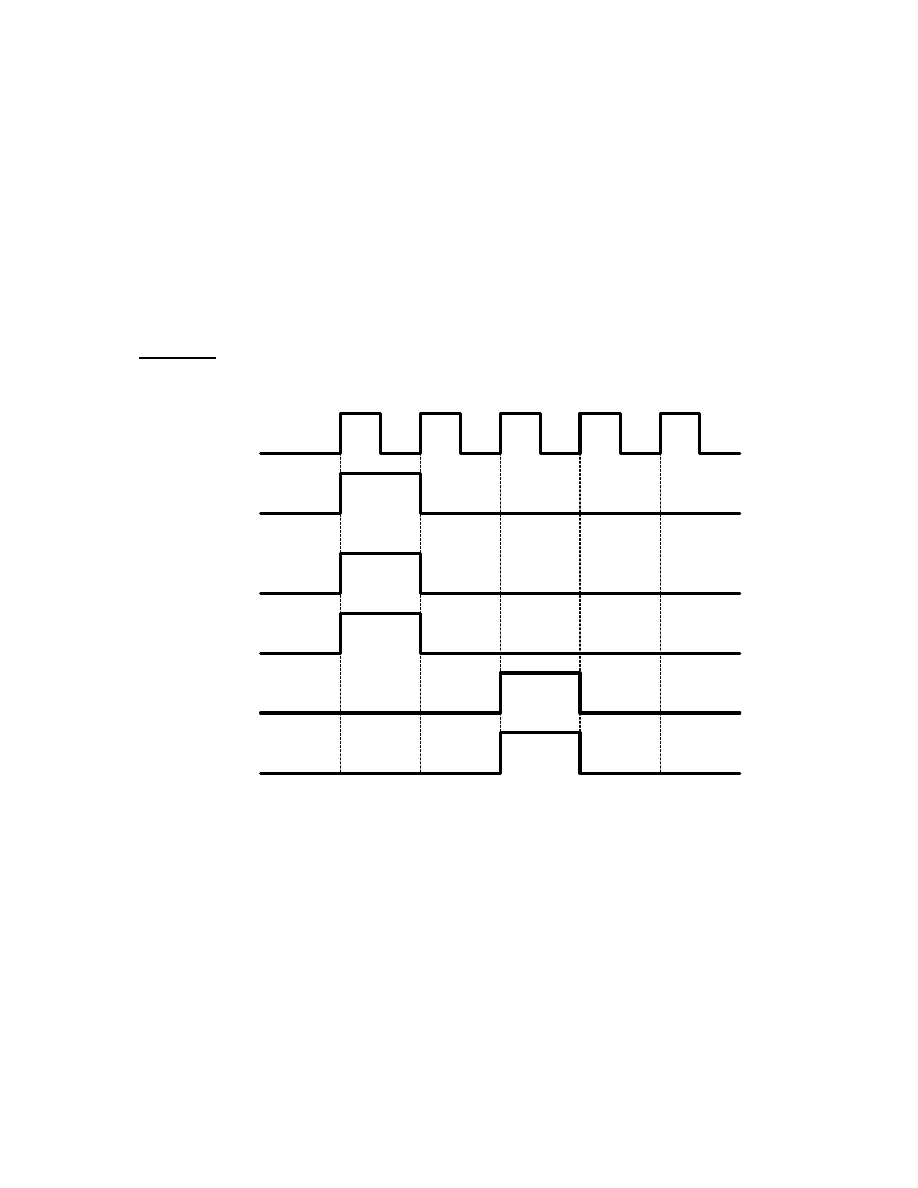

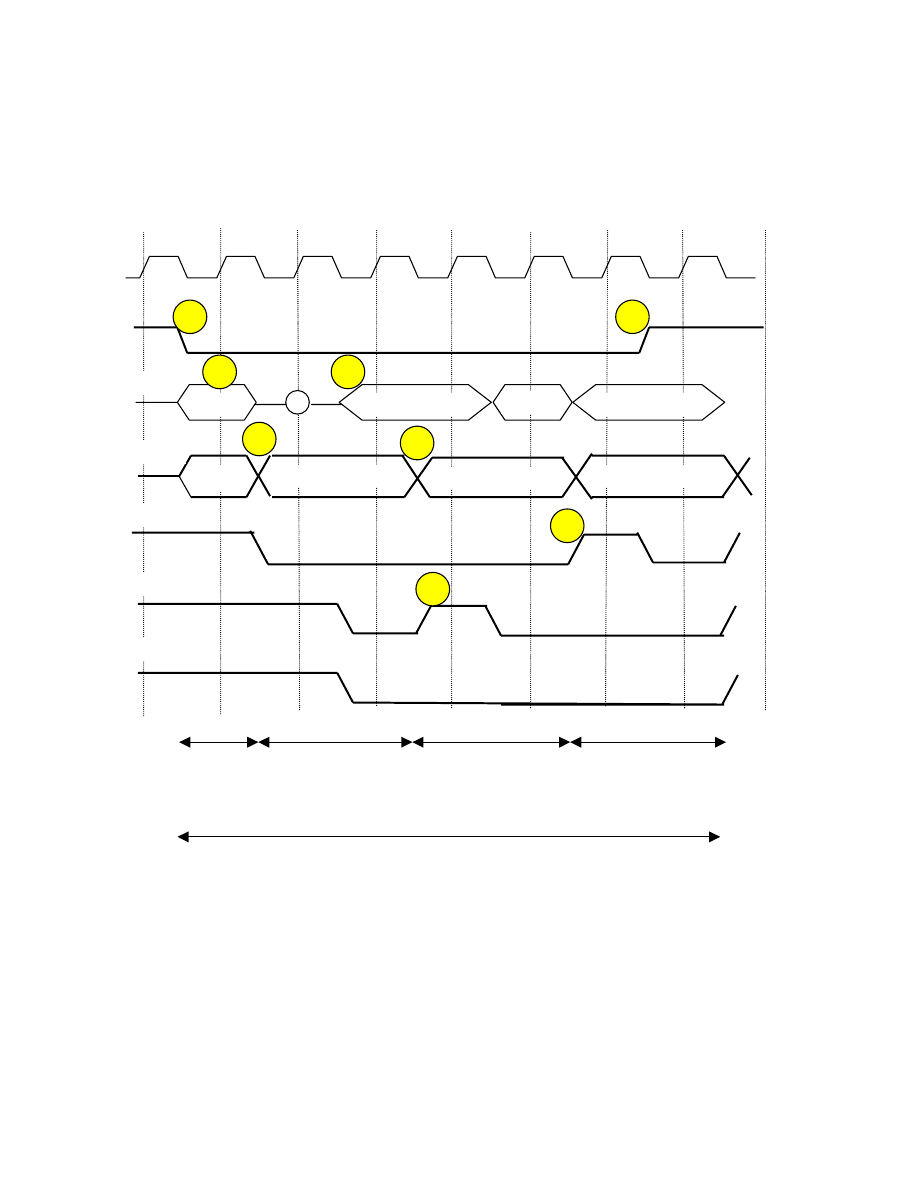

Przykład

Przebieg czasowy operacji odczytu (operacja synchronizowana)

Zegar

Start

Odczyt

Linie

adresowe

Linie

danych

Potwierdzenie

Koordynacja asynchroniczna

Występowanie zdarzeń na magistrali jest zależne od zdarzenia poprzedzającego.

Przykład.

Procesor umieszcza sygnały adresu i odczytu na magistrali. Po pewnym czasie

wymaganym do ustabilizowania sygnałów, wysyła sygnał synchronizacji

nadrzędnej (master sync – MSYN), wskazując na obecność ważnych sygnałów

adresu i sterowania. Moduł pamięci reaguje, wysyłając dane oraz sygnał

synchronizacji podrzędnej (slave sync – SSYN), wskazujący na odpowiedź.

MSYNC

SSYNC

Odczyt

Linie

adresowe

Linie

danych

Magistrala PCI (ang. Peripheral Component Interconnect)

Magistrala PCI została zaprojektowana jako ekonomiczne rozwiązanie,

spełniające wymagania wejścia – wyjścia w nowoczesnych systemach. Wymaga

niewielu mikroukładów i wspomaga działanie innych magistrali, które

połączone są z PCI.

Przeznaczone jest dla szerokiego zakresu konfiguracji wykorzystujących

mikroprocesory, łącznie z systemami jedno- i wielo-procesorowymi.

PCI wykorzystuje koordynację synchroniczną i arbitraż scentralizowany.

Do szyny PCI można podłączać karty graficzne, kontrolery SCSI czy też

karty sieciowe o ile są zgodne ze standardem PCI. Zasadniczą zaletą tego

standardu jest możliwość automatycznej konfiguracji nowo podłączanych

elementów, czyli wykorzystanie techniki plug-and-play - podłącz i działaj.

P ro ce sor

M a g is trala P C I

M o s t/

stero w n ik

p am ięc i

P a m ięć

D R A M

S zyn a ro zszerzeń

G ra fika

S ieć

M o st

szyny

ro zsze rze nia

P o rt

sze re go w y

S C S I

V ide o

M o de m

P a m ięć

po dręczna

Struktura magistrali PCI

Grupy funkcjonalne linii sygnałowych:

!"

Wyprowadzenia systemowe (zegar, reset);

!"

Wyprowadzenia adresu i danych (32 linie multipleksowane);

!"

Wyprowadzenia sterowania interfejsu;

!"

Wyprowadzenia arbitrażowe (nie są liniami wspólnymi, każda jednostka

nadrzędna ma własną parę linii arbitrażowych, które łączą ja bezpośrednio z

arbitrem magistrali PCI).

Ponadto specyfikacja PCI określa 50 opcjonalnych linii sygnałowych,

podzielonych na następujące grupy:

!"

Wyprowadzenia przerwania;

!"

Wyprowadzenia obsługi pamięci podręcznej;

!"

Wyprowadzenia rozszerzenia magistrali 64-bitowej (należą do nich 32

linie multipleksowane, w połączeniu z obowiązującymi liniami adresowymi

i danych tworzą 64-bitową magistralę adresowa i danych);

!"

Wyprowadzenia magistrali diagnostycznej JTAG (norma IEEE 1149.1).

Dane po szynie są przesyłane z częstotliwością 33MHz, niezależnie od częstotliwości

pracy mikroprocesora. Wynika to z faktu zastosowania układu kontrolera, który steruje

przepływem danych do urządzeń podłączonych do szyny PCI. Wszystkie przesłania są

przesłaniami blokowymi (burst). Takie rozwiązanie pozwala teoretycznie przesłać dane

w każdym cyklu zegara. Uwzględniając fakt, że szyna PCI może współpracować zarówno

w systemie 32-bitowym, jak również 64-bitowym daje to teoretyczną szybkość transmisji dla

pierwszego przypadku 132 MB/s i 264 MB/s dla drugiego przypadku. Magistrala PCI posiada

wprawdzie pojemność, która teoretycznie pozwala na transmisję danych video, ale musi ona

obsługiwać także inne urządzenia systemowe, jak karty we/wy, modemowe oraz sieciowe.

W pewnych sytuacjach magistrala ta może być więc tak obciążona, że nie będzie w stanie

przesłać napływających danych, i obraz video nie będzie odtwarzany w sposób płynny.

Zaczęto więc tworzyć rozwiązania, które polepszą jakość wyświetlania obrazu video.

Rozkazy PCI

Działanie magistrali odbywa się w formie transakcji między inicjatorem

(modułem nadrzędnym) a celem (modułem podrzędnym). Gdy inicjator żąda

dostępu do magistrali, określa typ transakcji, którą chce przeprowadzić. Do

sygnalizowania typu transakcji używane są linie C/BE. Wykorzystywane są

następujące rozkazy:

!"

potwierdzenie przerwania,

!"

cykl specjalny,

!"

odczyt wejścia-wyjścia,

!"

zapis wejścia-wyjścia,

!"

odczyt pamięci,

!"

linia odczytu pamięci,

!"

zwielokrotniony odczyt pamięci,

!"

zapis w pamięci,

!"

zapis w pamięci i unieważnienie,

!"

odczyt konfiguracji,

!"

zapis konfiguracji, cykl podwójnego adresu.

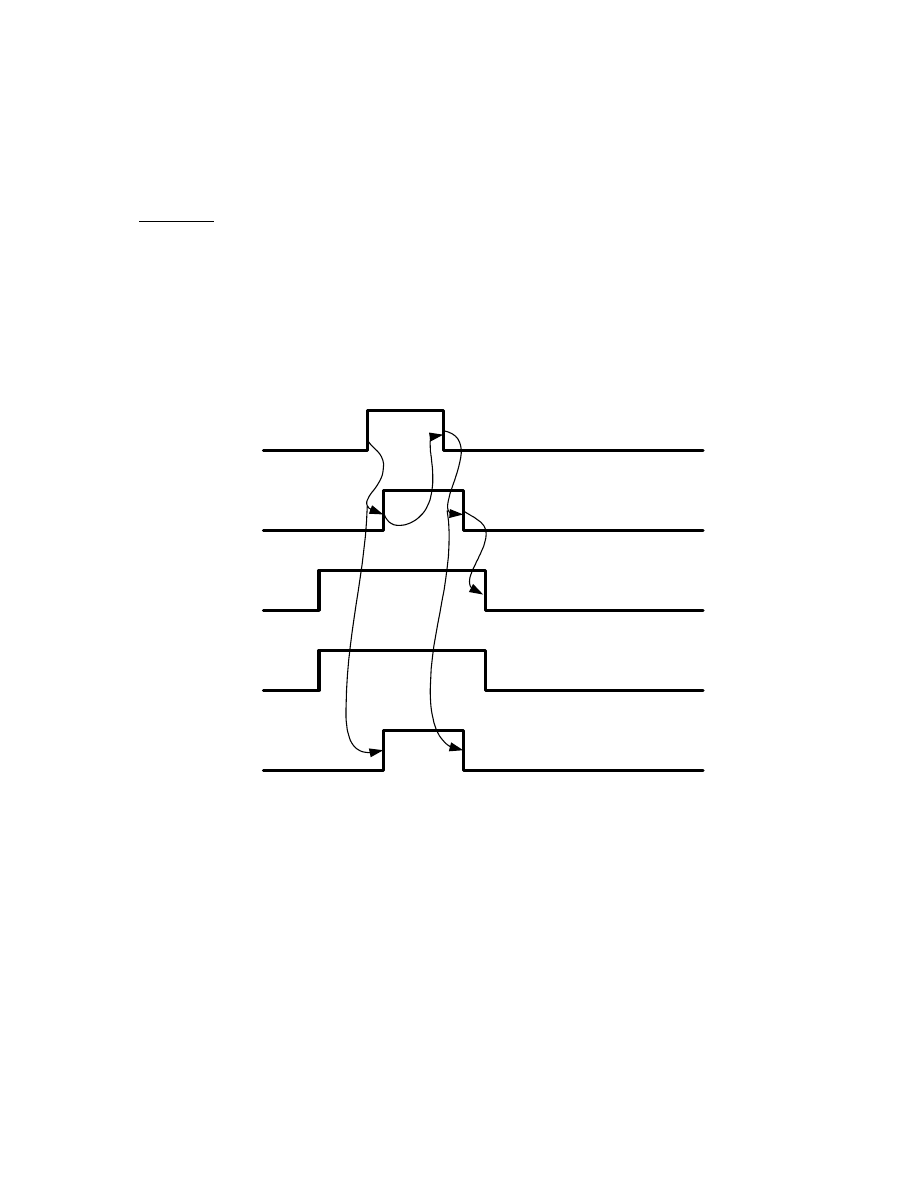

Przesyłanie danych

Każde przesyłanie danych magistralą PCI jest pojedynczą transakcją składającą

się z jednej fazy adresowej oraz jednej lub wielu faz danych.

FRAME#

Adres

Dane 1

Dane2

Dane 3

AD

Rozkaz

magistral

C/BE#

Zezwolenie bajtu

Zezwolenie bajtu

Zezwolenie bajtu

IRDY#

TRDY#

DEVSEL#

Faza adresu

Faza danych

Faza danych

Faza danych

Transakcja magistralowa

a

b

d

c

e

f

g

h

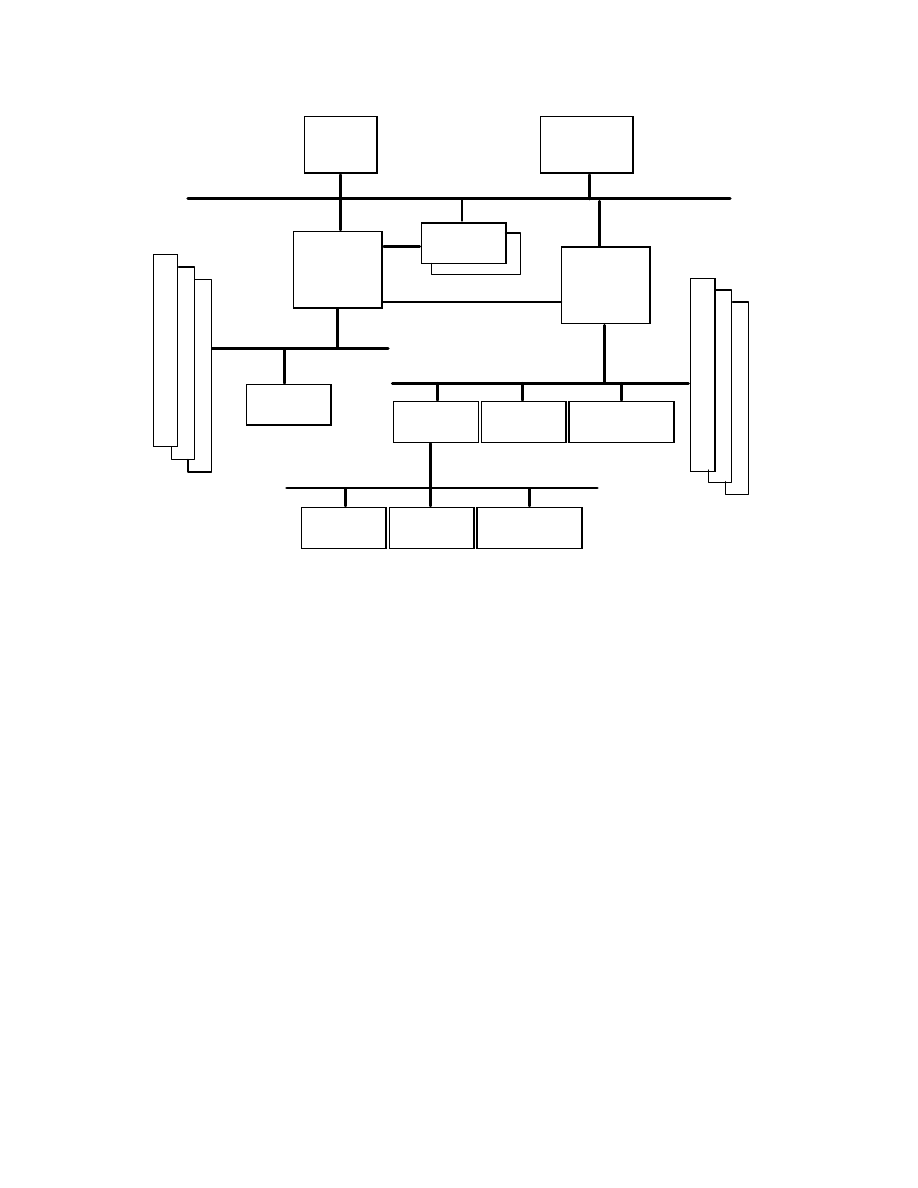

CONTROLS

ISA BUS

ISA SLOTS

PCI SLOTS

PCI BUS

HOST BUS

X BUS

CPU

CACHE

DRAM

PSC

82425EX

IB

82426EX

LB IDE

BUFOR

AIP

GP PORT 78

RTC

FLASH

KEYBORD

PSC - sterownik systemu PCI łączy w sobie:

•

sterownik DRAM;

•

sterownik CACHE;

•

interfejs lokalnej szyny IDE;

•

zarządza poborem energii.

IB - sterownik systemu ISA łączy w sobie:

•

sterownik 7-mio kanałowy DMA;

•

układ 8254 licznika/zegara;

•

2 układy 82C59 sterowników przerwań;

Struktura systemu mikroprocesorowego wykorzystującego standard PCI

Standard AGP

(Accelerated Graphics Port)

Standard ten został oparty na standardzie PCI wersji 2.1. Rozszerzono go

o trzy podstawowe elementy:

•

potokowość operacji zapisu i odczytu pamięci;

•

demultipleksowane magistrale danych i adresowa;

•

możliwość przesyłania danych z częstotliwością 133 MHz.

Szyna standardowo przesyła dane z częstotliwością 66 MHz, co daje jej

teoretyczną przepustowość przy 32-bitach 266 MB/s i wówczas szyna pracuje

w tzw. trybie „x1”. Przy pracy w trybie „x2” teoretyczna przepustowość szyny

dla 32-bitów wzrasta do 532 MB/s. Uzyskuje się to przez wykorzystanie

obydwu zboczy sygnały zegara taktującego, czyli 2 * 66MHz = 133 MHz.

Standard ten jest obecnie stosowany w najnowszych płytach głównych dla

Pentium.

Zestawienie parametrów omówionych standardów.

Typ

Szyny

Szybkość transmisji lub

szerokość pasma

Szerokość

szyny

Możliwość podłączenia

ISA

2,5 MB/s, 8 MHz

16 bitów

Wszystkie rodzaje kart

rozszerzających.

Local

Bus

132 MB/s, 33 MHz

32 bity

Głównie karty graficzne i kontrolery

HDD.

PCI

132 MB/s, 33 MHz

32 bity

Głównie karty graficzne i kontrolery

HDD.

PCI 2.1 264 MB/s, 33 MHz

64 bity

Głównie karty graficzne i kontrolery

HDD.

VMC

130 MB/s

16 i 32 bity

Karty graficzne i video.

VAFC

150 MB/s

Od 8 do 32

bitów

Karty graficzne i video.

AGP

266 MB/s lub 532 MB/s, 66

MHz

32 bity (128

bitów)

Karty graficzne i video.

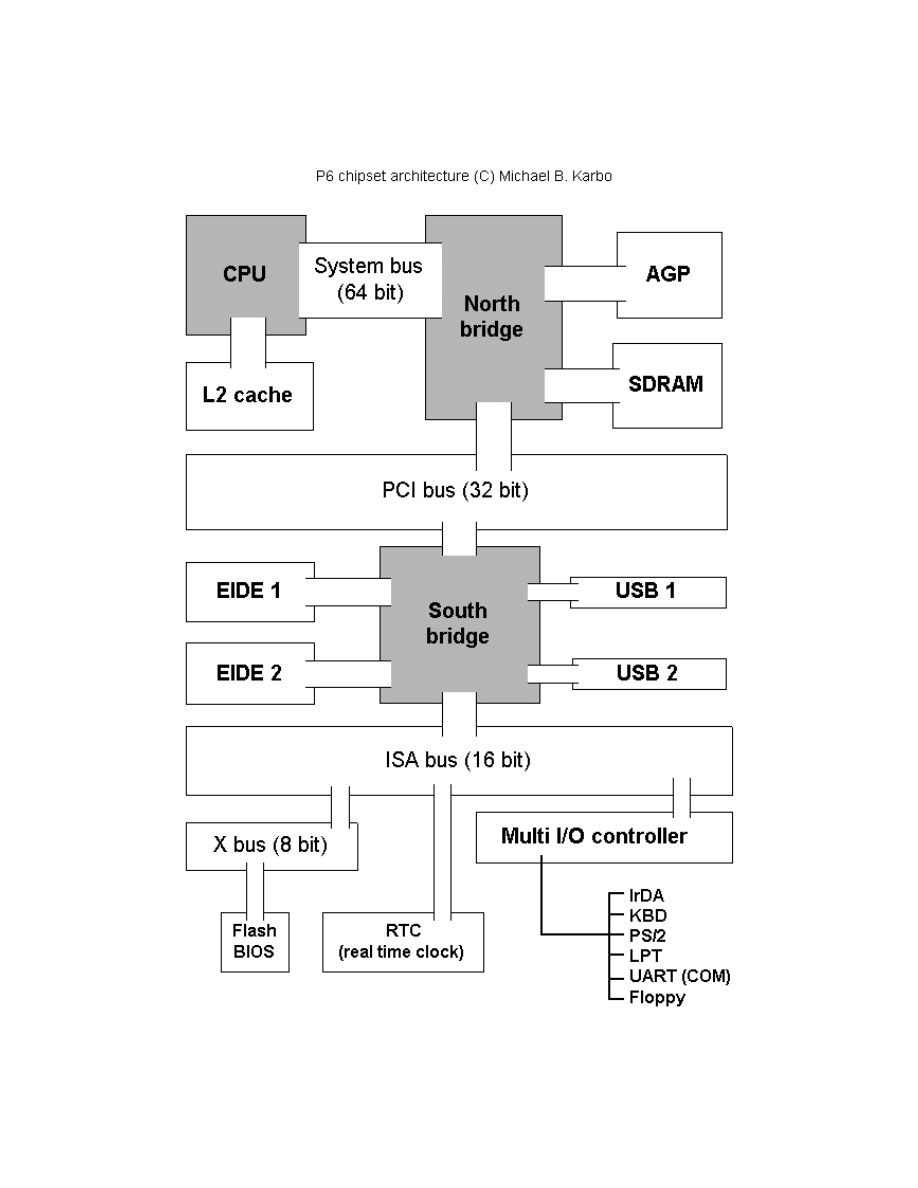

Chipset – architektura

Generacje chipsetów firmy INTEL

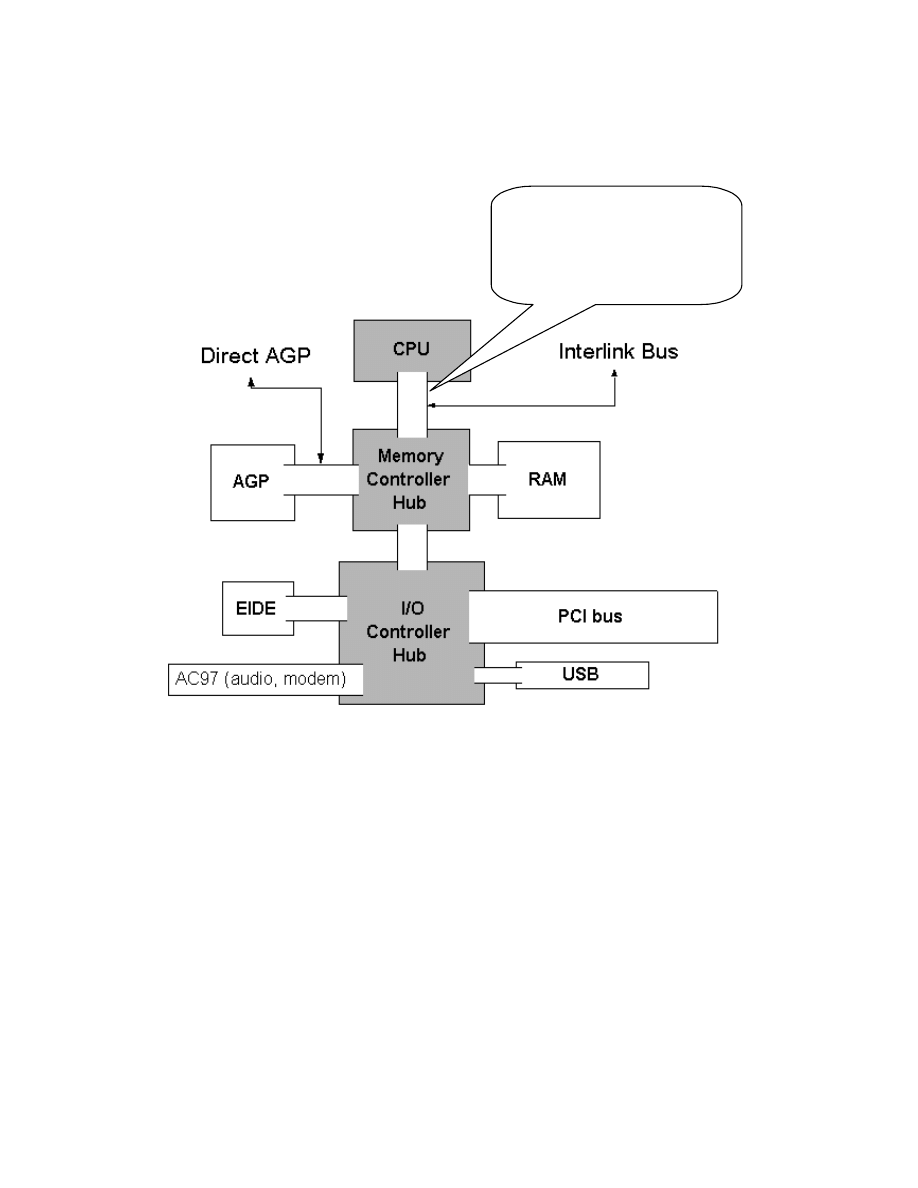

Szyna Interlink działa przy

częstotliwości 133 MHz w

trybie 2X, co przy szerokości

szyny 64-bity daje

przepustowość 266 MB/sek

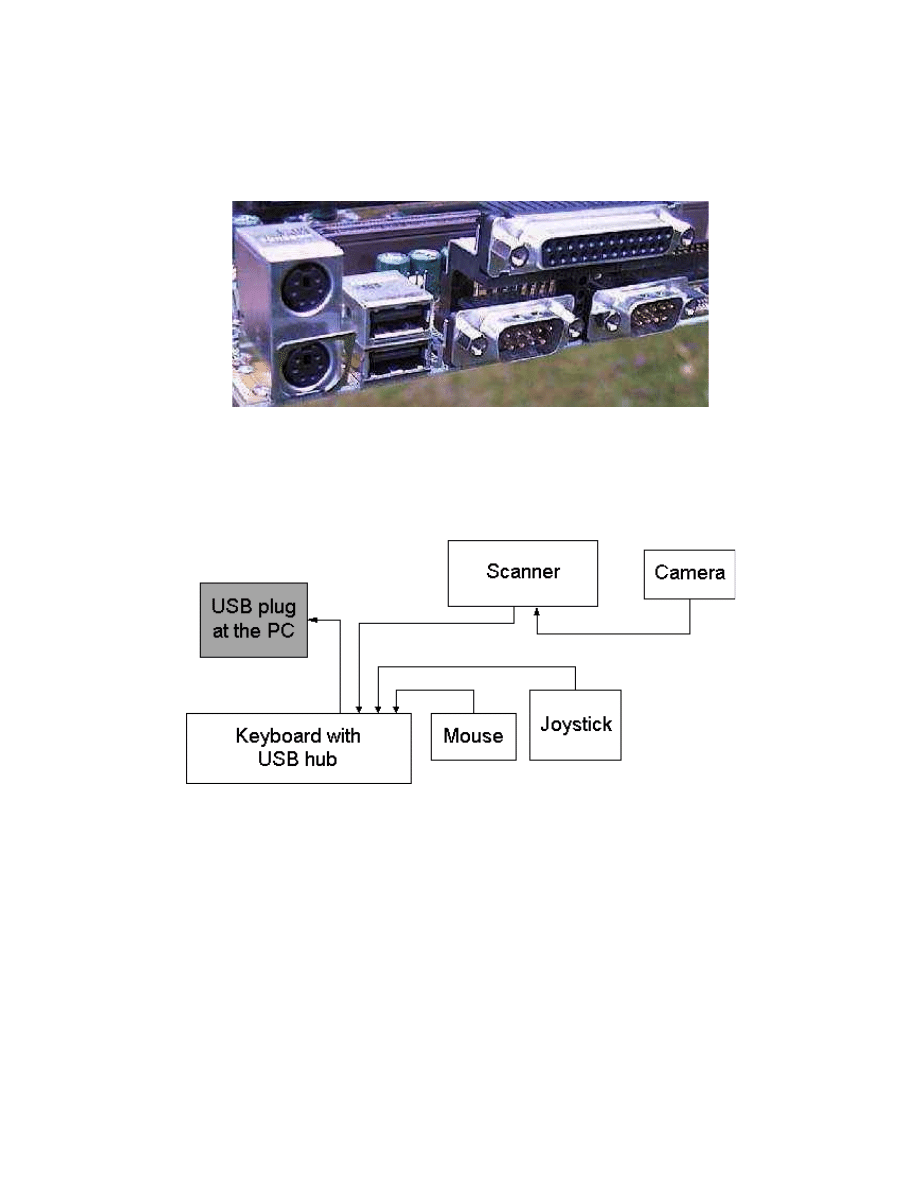

USB - Universal Serial Bus

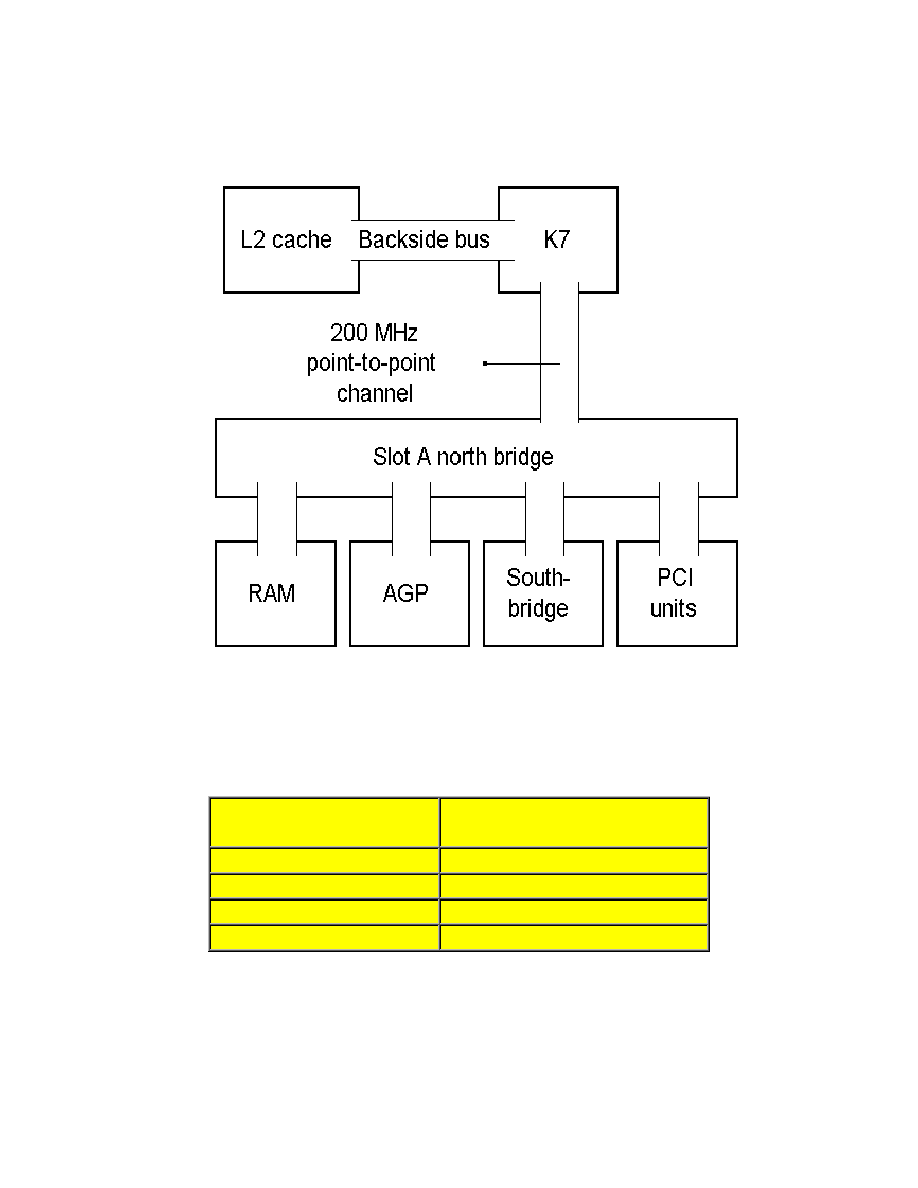

Procesor K7 Athlon

System

Maksymalna przepustowość

Intel 100 MHz

800 MB/sec.

Intel 133 MHz

1064 MB/sec.

AMD Athlon, 200 MHz

1600 MB/sec.

AMD Athlon, 400 MHz

3200 MB/sec.

Procesor Merced

Code name for a 7th. generation CPU, which Intel is developing together with

the HP company, HP has great experience in the manufacture of high end CPUs

(RISC). I will tell you about that, as the information becomes available.

•

64 bit CPU, will require a new 64 bit operating system (Windows 2003?).

•

Clock frequency: 1000 MHz (1 GHz).

•

>30 million transistors.

•

"Massive hardware units": 128 integer and 128 floating point registers

with multiple integer and floating point units all working in parallel.

•

0.18 or 0.13 micron technology.

•

Slot M cartridge.

After Merced follows a CPU with code name McKinley. Then Madison, then

Deerfield, and so on.

Wyszukiwarka

Podobne podstrony:

Architektura5 id 67923 Nieznany (2)

Architektura3 id 67919 Nieznany (2)

Architektura4 id 67920 Nieznany (2)

ArchitekturaKomputera2 id 67926 Nieznany (2)

Architektura6 id 67924 Nieznany (2)

ArchitekturaKomputera id 67925 Nieznany

PEK PB OPIS ARCHITEKTURA id 354 Nieznany

Architektura1 id 67917 Nieznany (2)

Architektura5 id 67923 Nieznany (2)

Architektura3 id 67919 Nieznany (2)

architektura aplikacji id 67748 Nieznany (2)

Architektura Neutrino 1 id 6791 Nieznany (2)

Architektura Komp2 id 67910 Nieznany (2)

Architektura ekoczasu id 67766 Nieznany (2)

5 Architektura MCU 2010 id 4004 Nieznany (2)

ARCHITEKTURA KOMPUTEROW id 6779 Nieznany (2)

Architektura Renesansu id 67864 Nieznany (2)

Architektura Komp5 id 67913 Nieznany (2)

Architektura drewniana 2 id 677 Nieznany (2)

więcej podobnych podstron