System mikroprocesorowy

i peryferia

Dariusz Chaberski

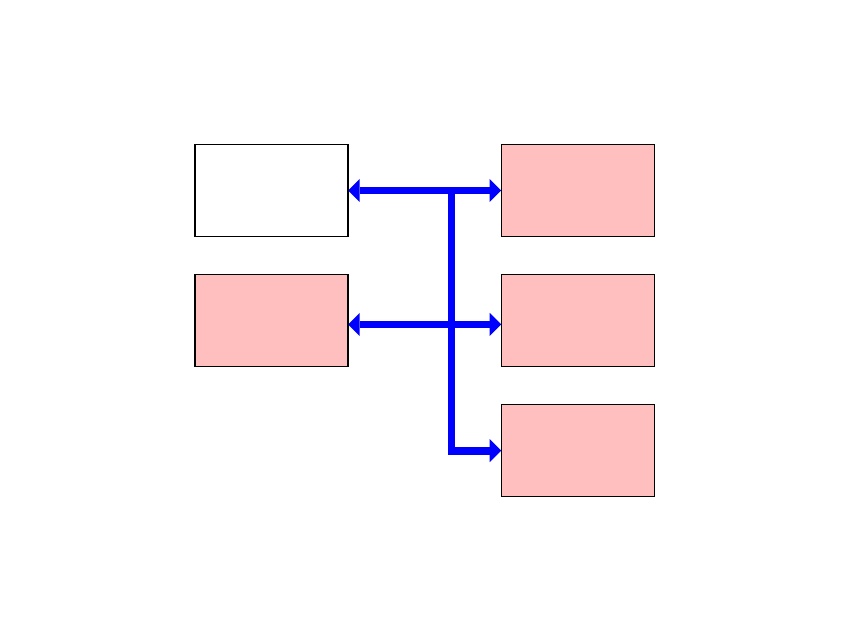

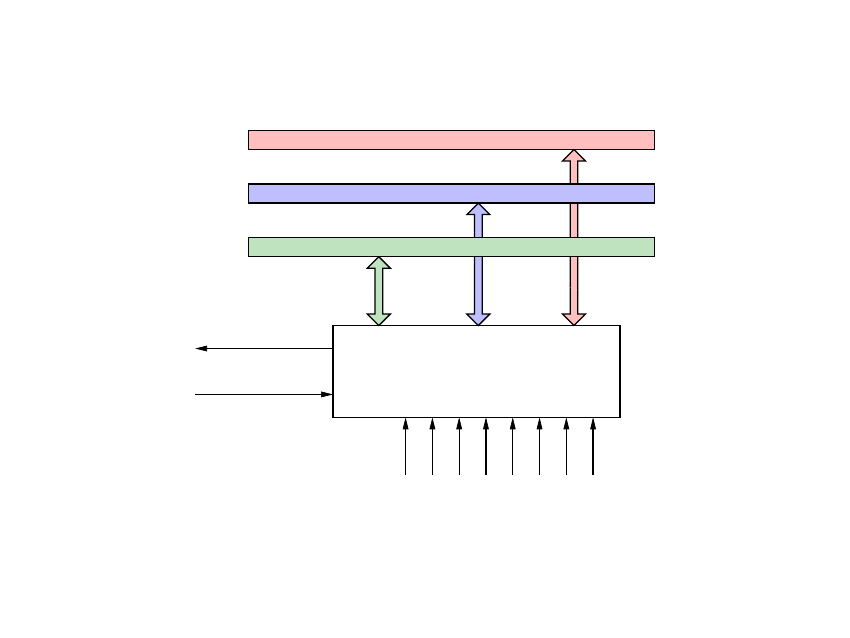

System mikroprocesorowy

mikroprocesor

pamięć

układy wejścia

wyjścia

kontroler DMA

kontroler

przerwań

2

Pamięć

§ rodzaje (podział ze względu na sposób programowania)

+ (S/D)RAM - (Static/Dynamic) Random Access Memory (pamięć o dostępie swobodnym),

+ ROM - Read Only Memory (pamięć tylko do odczytu),

+ OTP - One Time Programmable (pamięć jednokrotnie programowalna),

+ (UV)EPROM - Erasable Programmable ROM (pamięć tylko do odczytu kasowalna promienia-

mi UV),

+ EEPROM - Electrically EPROM (pamięć tylko do odczytu kasowalna elektrycznie),

+ Flash - pamięć EEPROM typu błyskowego (Pełka 1999),

+ NVRAM - Non Volatile RAM - pamięć nieulotna o dostępie swobodnym.

3

§ rodzaje (podział ze względu na sposób dostępu - interfejs)

+ szeregowa,

+ równoległa,

+ FIFO - First Input First Output (kolejka),

+ FILO - First Input Last Output (stos),

+ jednoportowa,

+ wieloportowa.

4

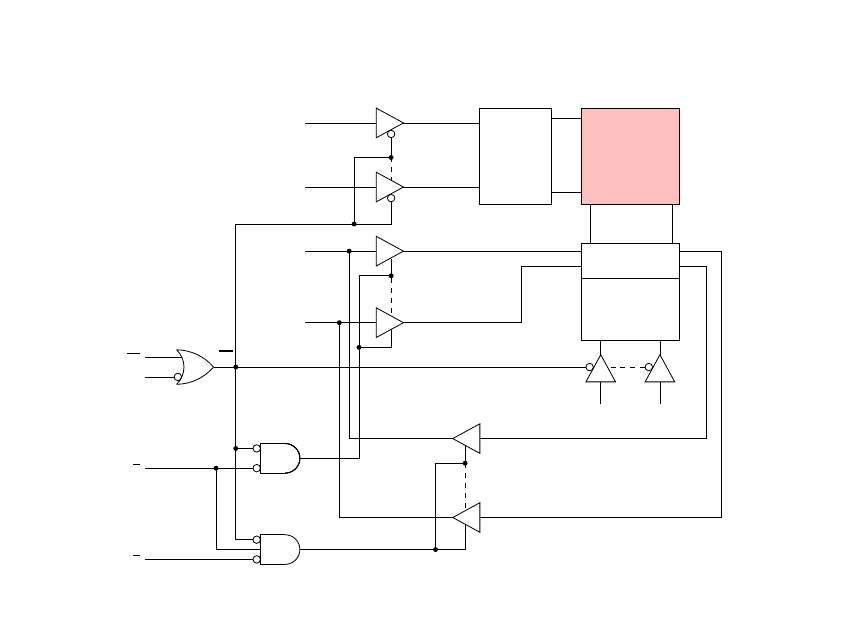

Pamięć RAM

§ schemat blokowy

macierz

pamięci

dekoder

wierszy

A0

A7

A16

DQ7

DQ0

W

G

dekoder

kolumn

układ wejścia

wyjścia

Ex

E2

E1

A6

5

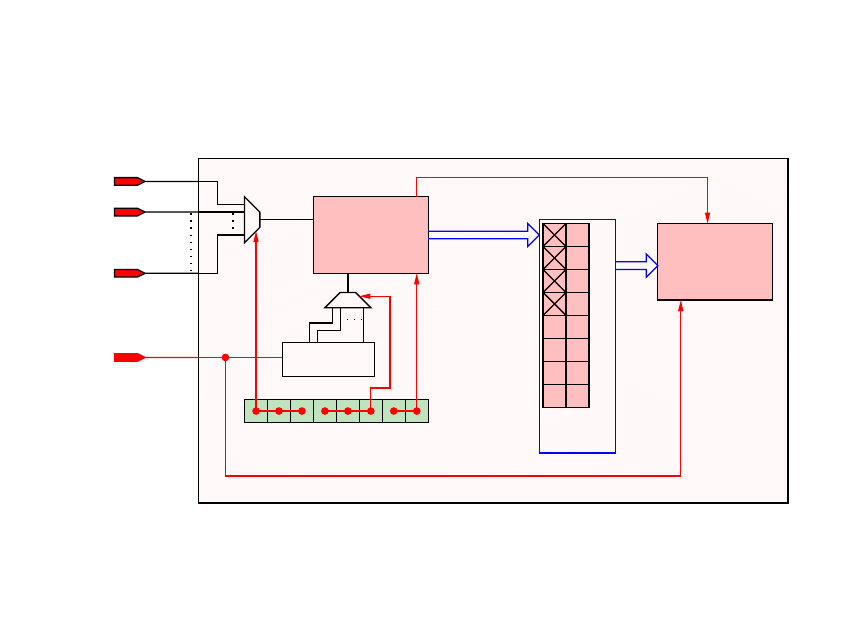

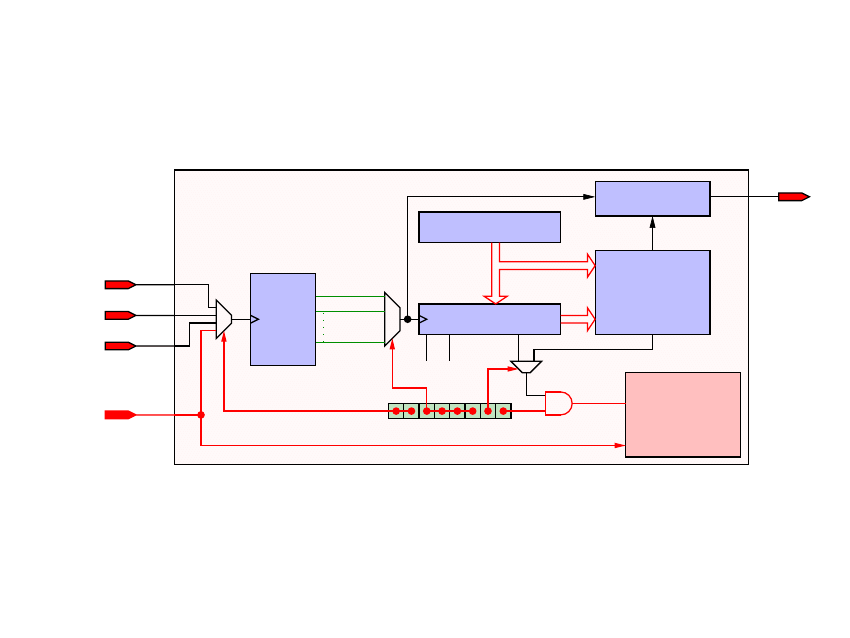

Przetworniki analogowo cyfrowe

ANIN

0

ANIN

1

przetwornik

A/C (SAR)

CLK

ANIN

7

bajt konfiguracyjny

D

0

. . .

D

11

preskaler

b

0

b

1

b

7

A

D

R

H

A

D

R

L

jednostka

centralna

INT

mikrokontroler

6

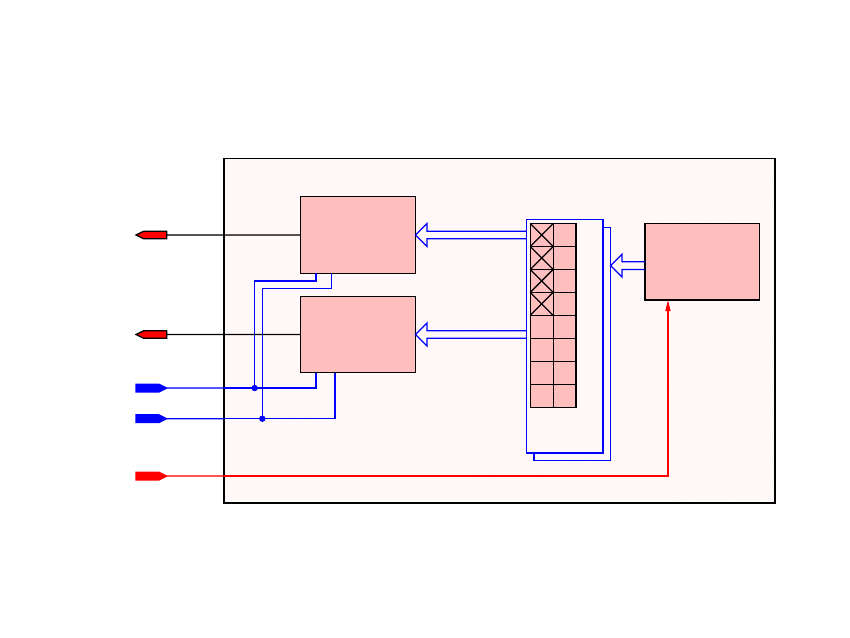

Przetworniki cyfrowo analogowe

b

0

b

1

b

7

A

D

R

H

A

D

R

L

jednostka

centralna

przetwornik

C/A

przetwornik

C/A

D

0

. . .

D

11

D

0

. . .

D

11

ANOUT

1

ANOUT

2

VREF

+

VREF

−

CLK

mikrokontroler

7

Liczniki i czasomierze

bajt konfiguracyjny

CNT0

CNT1

CNT2

f /1024

licznik binarny

f

komparator

jednostka

centralna

mikrokontroler

b

n−1

B

A

A = B

CLK

(T )

p

re

sk

al

er

rejestr

b

1

b

0

INT

f /16

f /2

PWM

PWM

D

8

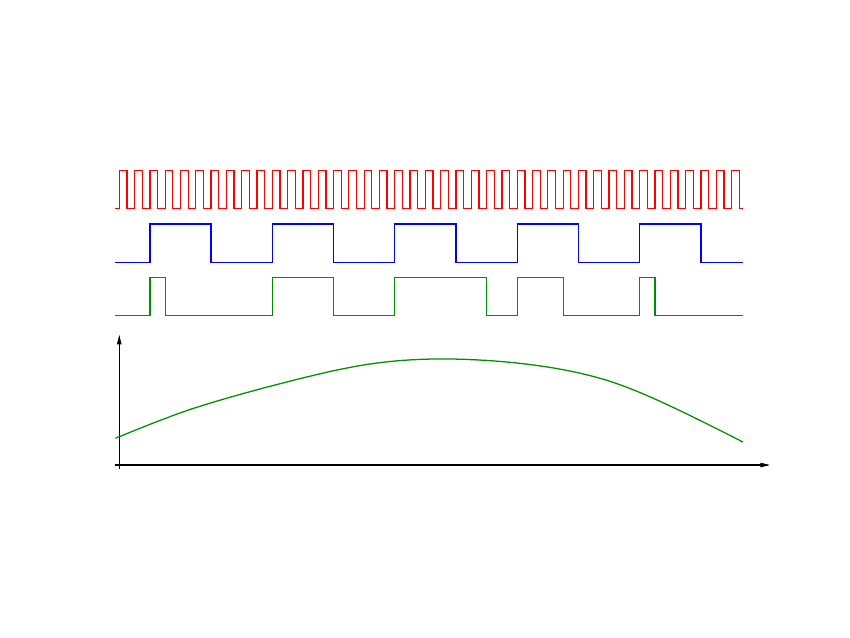

Modulacja szerokością impulsu

CLK1

CLK2

PWM

D

PWM

A

t

9

Interfejs komunikacji szeregowej

§ wyjście

słowo

konfiguracyjne

rejestr przesuwny

szyna danych

słowo stanu

rejestr wejściowy

programowalny

generator

sygnał

zegarowy

wyjście

szeregowe

danych

10

§ wejście

słowo

konfiguracyjne

rejestr przesuwny

szyna danych

słowo stanu

rejestr wyjściowy

programowalny

generator

układ

odzyskiwania

danych

sygnał

zegarowy

wejście

szeregowe

danych

przerwanie

11

Kontroler przerwań

magistrala sterująca

magistrala adresowa

magistrala danych

A2-A0

D7-D0

wejścia przerwań

potwierdzenie

przerwanie

W CS OE IO

kontroler przerwań

IO - żądanie dostępu do portów wejścia wyjścia

12

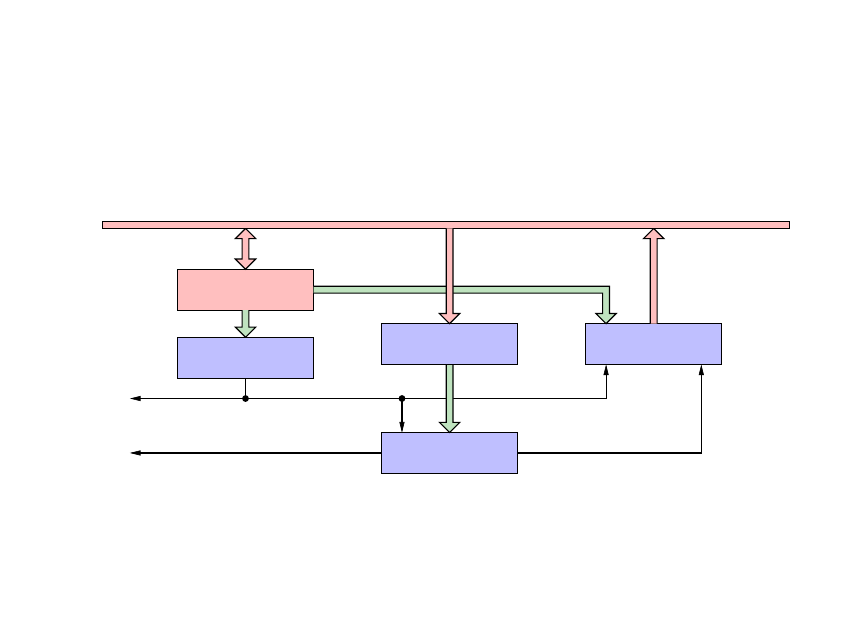

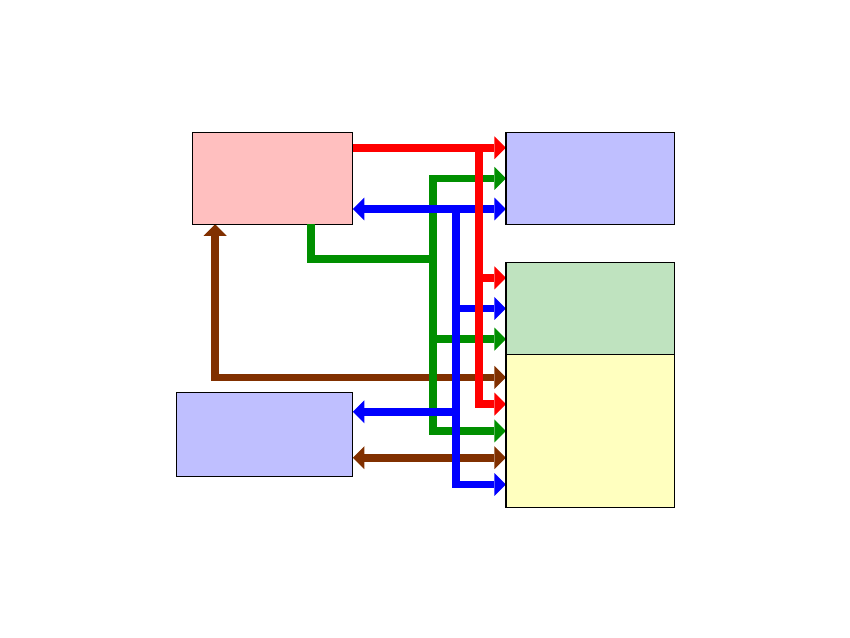

Bezpośredni dostęp do pamięci

D

A

C

A

A

D

D

C

C

mikroprocesor

układ

zewnętrzny

C

DMA

układy wejścia

wyjścia

pamięć

D

C

′

DMA

C

′

DMA

A

C

C

DMA

D

układ

bezpośredniego

dostępu do

pamięci

13

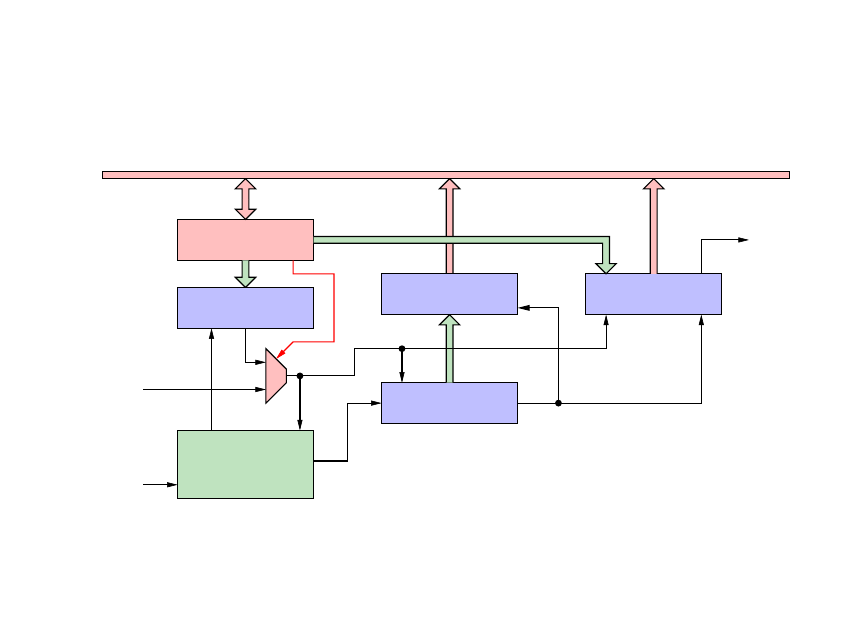

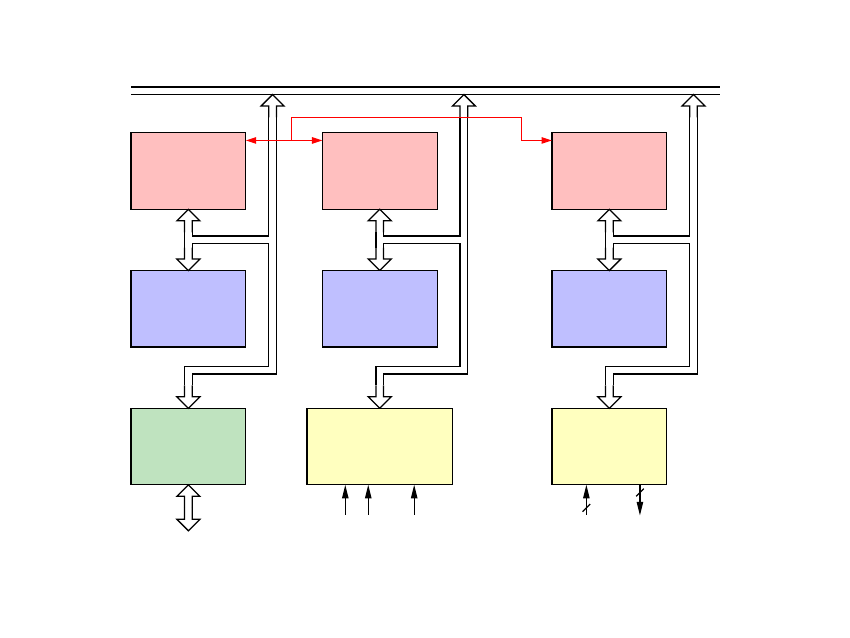

Kaskadowe połączenie kontrolerów DMA

kontroler

DMA

kontroler

DMA

kontroler

DMA

mikroprocesor

pierwszy poziom

drugi poziom

DACK

DREQ

DREQ

DREQ

DACK

DACK

DREQ

DACK

układ

zewnętrzny

sz

y

n

a

a

d

re

so

w

a

sy

g

n

a

ły

st

er

u

ją

ce

szyna

danych

DREQ - żadanie przesłania DMA

DACK - potwierdzenie / zgoda na przesłanie DMA

14

Porównanie

§ mikrokontroler

+ mała moc obliczeniowa (30 MIPSów)

+ na ogół brak instrukcji zmniennoprzecinkowych

+ przetwarzanie jedno potokowe

+ bogate peryferia

3 liczniki i układy czasowe

3 przetworniki A/C i C/A

3 duża liczba interfejsów

+ dostępne operacje bitowe

+ brak układu zarządzania pamięcią MMU

+ praca tylko w trybie rzeczywistym

+ rzadko obsługiwany bezpośredni dostęp do pamięci DMA

+ zastosowanie: aparatura kontrolno pomiarowa

15

§ mikroprocesor

+ duża moc obliczeniowa (10000 MIPSów obecnie)

+ wielordzeniowość oraz technologia HT

+ przetwarzanie wielo potokowe

+ dostępne instrukcje zmniennoprzecinkowe

+ do działania wymaga dodatkowych peryferiów

3 kontroler DMA

3 pamięć (programu i danych)

3 kontroler przerwań PIC (ang. Programmable Interrupt Controller)

+ dostępny układ zarządzania pamięcią MMU

+ adresowanie w trybie rzeczywistym i wirtualnym

+ z reguły architektura Von-Neumana

+ możliwość pracy w systemie wieloprocesorowym

+ zastosowanie: komputery (stacje robocze - komputery osobiste, serwery)

16

System wieloprocesorowy

§ podział ze względu na symetrię

+ wszystkie procesory traktowane są na równi - system bardziej wydajny - SMP (ang. Symmetric

Multi Processing)

+ niektóre procesory mają przypisane ścisłe zadania - łatwiejszy projekt, na przykład jeden pro-

cesor odpowiada na przerwania, drugi odpowiada za komunikację wejścia wyjścia - ASMP (ang.

Asymetric Mutli Processing)

§ podział ze względu na potok danych i programu

+ SISD (ang. Single Instruction, Single Data) - jeden strumień instrukcji, jeden strumień danych

+ MIMD (ang. Multiple Instruction, Multiple Data) - wiele strumieni instrukcji, wiele strumieni

danych

+ SIMD (ang. Single Instruction, Multiple Data) - jeden strumień instrukcj, wiele strumieni da-

nych

+ MISD (ang. Multiple Instruction, Single Data) - wiele strumieni instrukcji, jednej strumień

danych

17

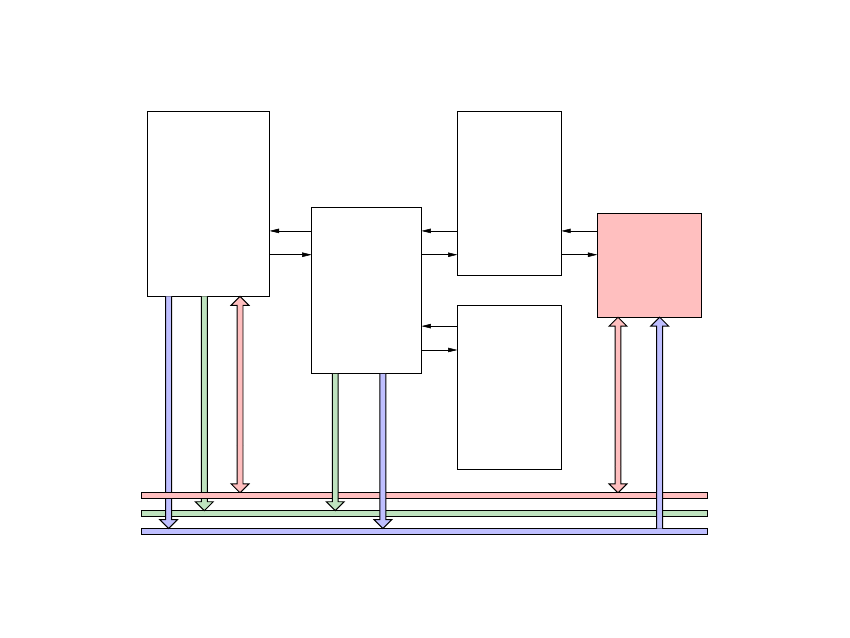

System wieloprocesorowy

Procesor 1

Pamięć 1

Procesor 2

Pamięć N

Pamięć 2

Porty wejścia

wyjścia 1

I/O

IR

Q

1

IR

Q

N

Kontroler

DMA 1

D

R

E

Q

D

A

C

K

m

ag

is

tr

al

a

lo

ka

ln

a

1

m

ag

is

tr

al

a

lo

ka

ln

a

2

m

ag

is

tr

al

a

lo

ka

ln

a

N

magistrala globalna

M

M

Procesor N

Kontroler

przerwań 1

IR

Q

0

18

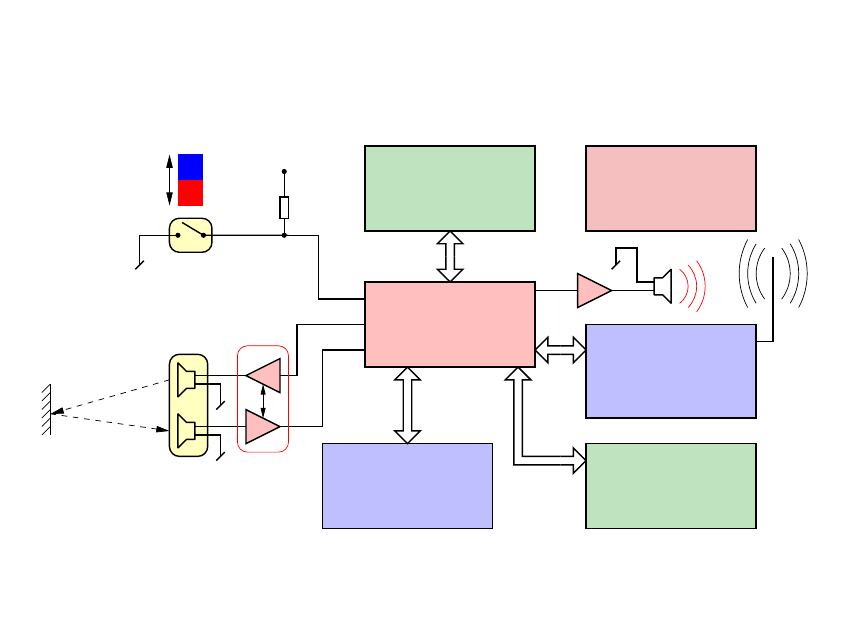

Przykładowy schemat blokowy aparatury kontrolnej

mikrokontroler

wyświetlacz

alfanumeryczny

moduł

transmisji

radiowej

czytnik kart

RFID

klawiatura

ultradźwiękowy

czujnik ruchu

blok zasilacza

z akumulatorem

magnes

trwały

Vcc

19

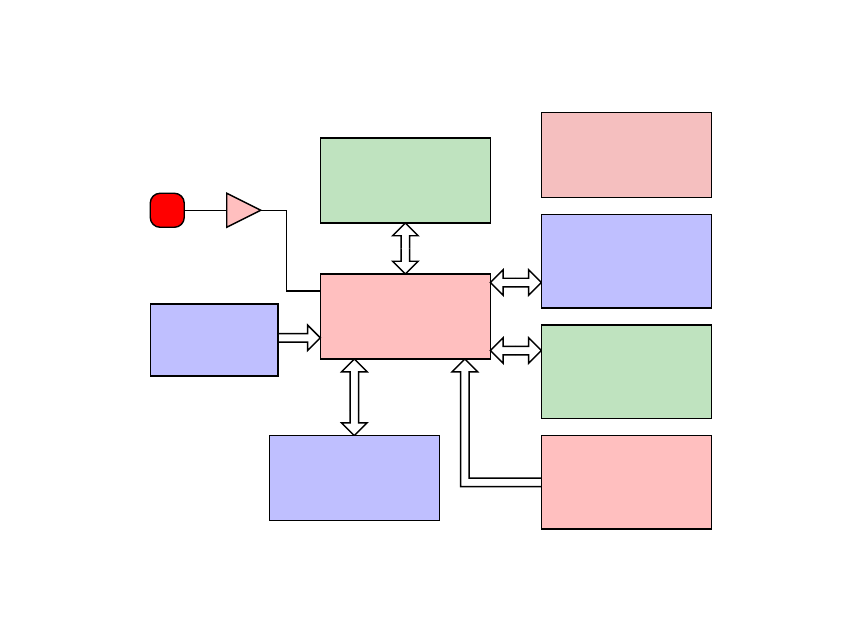

Przykładowy schemat blokowy aparatury pomiarowej

mikrokontroler

wyświetlacz

alfanumeryczny

blok zasilacza

pamięć danych

pomiarowych

interfejs

transmisji

danych

klawiatura

sygnały

wzorcowe

czujnik

głowica

pomiarowa

20

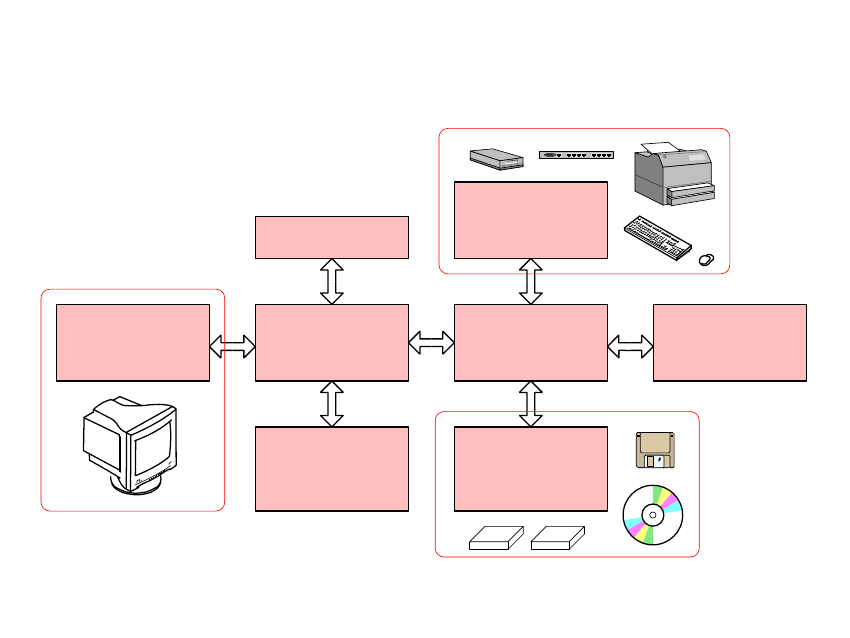

Przykładowy schemat blokowy komputera

mikroprocesor

zestaw układów

specjalizowanych

CHIPSET 1

karta

graficzna

zestaw układów

specjalizowanych

CHIPSET 2

pamięć operacyjna

interfejsy pamięci

masowej

interfejsy

komunikacyjne

magistrale

systemowe

21

Wyszukiwarka

Podobne podstrony:

04 System Operacyjny

04 systemy pamięci krótkotrwałejid 4865 ppt

Dydaktyczny system mikroprocesorowy DSM 51 Budowa systemu

cz%ea%9c%e6+4+ +unipolarne+uk%b3ady+scalone+i+uk%b3ady+systemu+mikroprocesorowego JAI3S2HWFFCL5ENM3S

04 Systemy odpadowe w UE dla ciekawskich

Mikroprocesory, Micro 03b, Laboratorium Podstaw System˙w Mikroprocesorowych

SYSTEM MIKROPROCESOROWY, Technik Informatyk, PROCESORY

2006 04 System pomiarowy audio, część 2

04 Systemy liczbowe

Projektowanie systemow mikroprocesorowych P Hadam

04. SYSTEM PODATKOWY teoria, Teorie opodatkowania i systemy podatkowe, Teorie opodatkowania i system

04 system3

pytania, systemy mikroprocesorowe, Pytanka dyplomowe

04 Systemy ekspertowe, politechnika infa 2 st, Projektowanie Systemów Informatycznych

Egzamin 04, System Informacji Terenowych SIT

więcej podobnych podstron