W artykule opisano nowe

rozwi¹zania firmy Texas

Instruments w dziedzinie

mikroprocesorów

i mikrokontrolerów.

Mikrokontrolery o bardzo

ma³ym poborze mocy typu

MSP430F13/14x

Wprowadzenie na rynek przez firmê Texas

Instruments procesora typu MSP430F133IPM

stanowi now¹ jakoæ pod wzglêdem sto-

sunku ceny do mocy obliczeniowej, w dzie-

dzinie mikrokontrolerów, wyposa¿onych

w system akwizycji danych. Rodzina mikro-

kontrolerów MSP430F13x/14x sk³ada siê

obecnie z piêciu uk³adów i w ka¿dym z nich

zosta³ zaimplementowany ten sam typ szyb-

kiego 12-bitowego przetwornika analogo-

wo-cyfrowego. Liczba przetworzeñ tego

przetwornika wynosi 200 tysiêcy próbek sy-

gna³u na sekundê. Przetwornik zosta³ wypo-

sa¿ony w osiem zewnêtrznych kana³ów

analogowych, czujnik temperatury wewnê-

trznej, uk³ad detekcji zbyt ma³ego napiêcia

zasilania, dwa wbudowane w uk³ad scalo-

ny (on-chip) ród³a napiêæ odniesienia, uk³ad

próbkuj¹co-pamiêtaj¹cy (sample-and-hold)

oraz bufor pamiêci o pojemnoci 16 s³ów 12-

bitowych, z mo¿liwoci¹ programowania

trybów jego pracy. Szczególnie wyposa¿e-

nie przetwornika analogowo-cyfrowego

w bufor pamiêci, umo¿liwia aplikacjom DSP

automatyczne zapisywanie w nim rezultatów

przetwarzania analogowo-cyfrowego, co

zwalnia jednostkê centraln¹ od konieczno-

ci ka¿dorazowego wydawania rozkazów

rozpoczêcia konwersji. Funkcja taka jest

nazywana auto-scan. Ponadto mikrokon-

trolery MSP430F13x/14x wyposa¿one s¹

tak¿e w system nadzorczy typu watchdog,

dwa 16-bitowe liczniki impulsów (timers),

komparator, pracuj¹cy w trybie synchro-

nicznym i asynchroniczny port szeregowy ty-

pu full-duplex. Mikrokontrolery s¹ umie-

szczone w obudowie o 64 wyprowadze-

niach. Aby rozwa¿ane mikrokontrolery mo-

g³y wspó³pracowaæ równie¿ z aplikacjami za-

PRZEGL¥D MIKROPROCESORÓW

i MIKROKONTROLERÓW

FIRMY TEXAS INSTRUMENTS

(1)

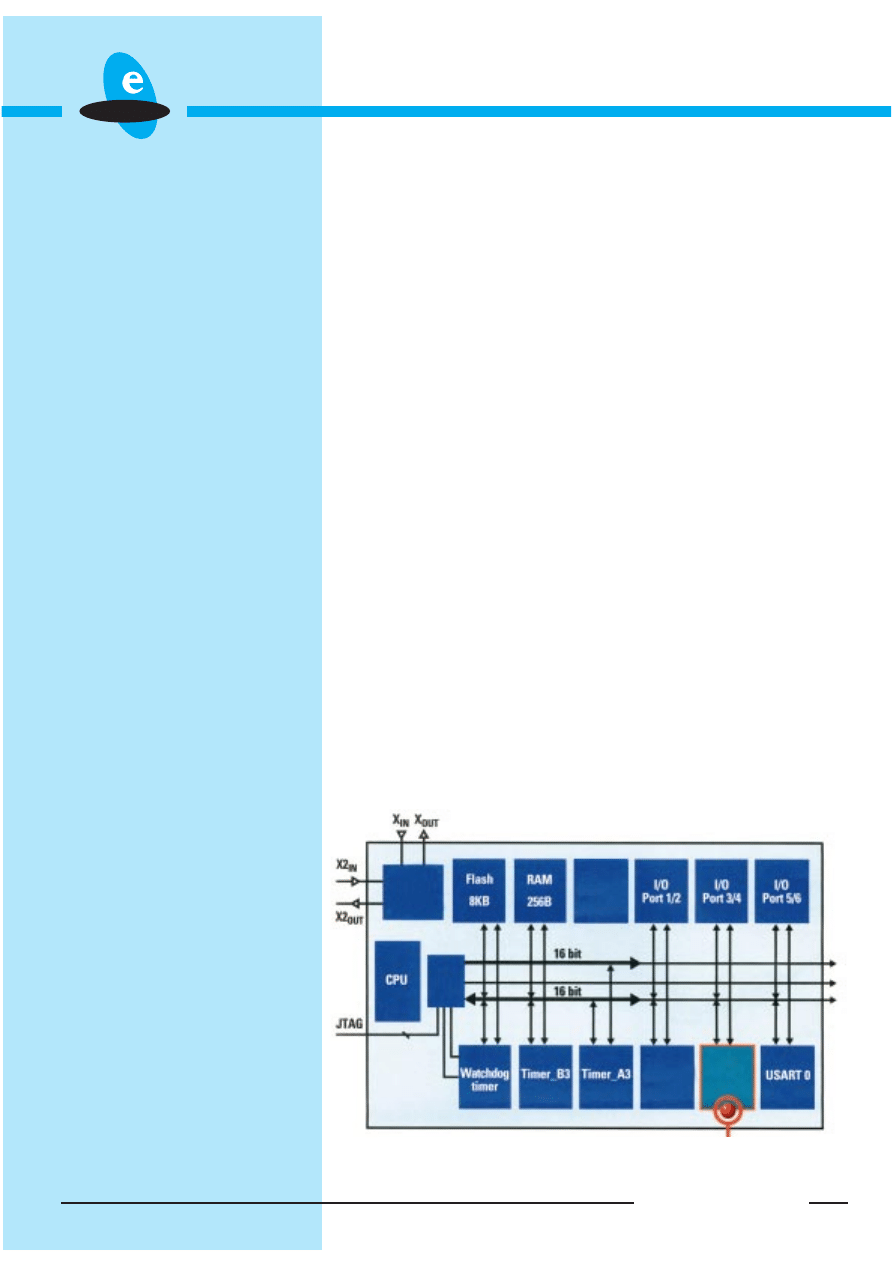

uk³adu mikrokontrolera MSP430F133, a na

rys. 2 _ schemat blokowy 12-bitowego prze-

twornika analogowo-cyfrowego wbudowane-

go w uk³ad MSP430F133.

Do typowych obszarów zastosowañ mikro-

kontrolerów typu MSP430F13x/14x mo¿na

zaliczyæ:

q

elektroniczne liczniki mediów: gazu, wo-

dy i energii elektrycznej

q

przyrz¹dy pomiarowe

q

przenone urz¹dzenia medyczne

q

aparaturê medyczn¹

q

systemy alarmowe i systemy bezpie-

czeñstwa (security systems).

Procesory DSP o wysokiej

mocy obliczeniowej

Niedawno firma Texas Instrument wprowa-

dzi³a na rynek trzy procesory DSP, s¹ to

odpowiednio TMS320C6414, C6415

i C6416, których moc obliczeniowa prze-

kracza dziesiêciokrotnie moc obliczeniow¹

najszybszych procesorów DSP dostêpnych

obecnie na rynku. Je¿eli wemie siê pod

uwagê aplikacje zwi¹zane z obróbk¹ obra-

zów cyfrowych, to czynnik ten jest jeszcze

wiêkszy, gdy¿ moc obliczeniowa wy¿ej wy-

mienionych urz¹dzeñ jest ponad piêtnasto-

krotnie wiêksza ni¿ dotychczas produko-

silanymi bateryjnie, wyposa¿ono je w 8 kB

pamiêci typu flash o bardzo ma³ym poborze

mocy. Uk³ady te zasilane s¹ napiêciem

2,2 V, przy czym ich pobór pr¹du w stanie

aktywnym wynosi 250

µ

A/MIPS, natomiast

w stanie oczekiwania (standby) pobór pr¹-

du spada poni¿ej 1

µ

A.

Mikrokontrolery MSP430F13x/14x mog¹

byæ zasilane napiêciem mieszcz¹cym siê

w zakresie 1,8

÷

3,6 V, przy czym ich moc

obliczeniowa wynosi 8 MIPS (milionów in-

strukcji wykonywanych na sekundê). Pa-

miêæ typu flash podzielona jest na 128- lub

512-bajtowe segmenty i mo¿e byæ progra-

mowana zarówno zewnêtrznie, jak i przez

sam¹ jednostkê centraln¹ mikrokontrolera.

Projektowanie aplikacji wykorzystuj¹cych mi-

krokontrolery MSP430F13x/14x wspierane

jest przez zestaw uruchomieniowy typu MSP-

FET430P140, w którego sk³ad wchodzi de-

bugger na poziomie kodu ród³owego, symula-

tor programowy uk³adów MSP430F13x/14x,

kompilator jêzyka C o ograniczonym zakresie,

modu³ z systemem uruchomieniowym wspó³-

pracuj¹cy z komputerem PC za porednic-

twem portu równoleg³ego z dwiema jednost-

kami MSP430F13x/14x, interfejs JTAG oraz

jednostka programuj¹ca pamiêæ mikrokon-

trolerów.

Na rys. 1 przedstawiono schemat blokowy

ZS

ITP

Komp-A

12-bit

a/c

UKP

Rys. 1. Schemat blokowy mikrokontrolera jednouk³adowego typu MSP430F133

ZS _ zegar systemowy, UKP _ uk³ad kontroli portów komunikacyjnych, ITP _ interfejs portu testowego typu JTAG

Radioelektronik Audio-HiFi-Video 8/2001

19

wanych tego typu urz¹dzeñ. Ponadto proce-

sory TMS320C6414, C6415 i C6416 cha-

rakteryzuj¹ siê najni¿szym w swojej klasie

stopniem zu¿ycia energii elektrycznej, o po-

nad jedna trzeci¹ ni¿szym ni¿ w przypadku

produktów konkurencyjnych. Równie¿ gê-

stoæ upakowania elementów jest w przy-

padku tych procesorów najwiêksza. Czêsto-

tliwoæ taktowania tych procesorów zosta-

³a zwiêkszona do 600 MHz, a procesor sta-

nowi szczytowe osi¹gniêcie w dziedzinie

szybkoci cyfrowego przetwarzania sygna-

³ów.

Procesor TMS320C6416 ma wbudowany

tzw. turbo koprocesor (turbo coprocessor)

oraz tzw. koprocesor Viterbiego (Viterbi co-

processor), a tak¿e interfejs z magistral¹

PCI oraz interfejs typu Utopia II obs³uguj¹-

cy komunikacjê I/O. Takie wyposa¿enie pro-

cesora TMS320C6416 sprawia, ¿e nadaje

siê on szczególnie do zastosowañ w sta-

cjach bazowych telefonii komórkowej.

Z kolei procesor TMS320C6415, przezna-

czony do zastosowañ w systemach szeroko-

pasmowych sieci teleinformatycznych, ma

wbudowane interfejsy PCI oraz Utopia II,

natomiast pozbawiony jest koprocesorów.

Natomiast procesor TMS320C6414 stanowi

tañsz¹ wersjê wy¿ej wymienionych urz¹-

dzeñ i mo¿e byæ wykorzystywany w celu

uzyskania wysokiej mocy obliczeniowej we

wszystkich aplikacjach nie wymagaj¹cych

wy¿ej wymienionych interfejsów i koproceso-

rów, których procesor ten zosta³ pozbawiony.

We wszystkich typach wymienionych proce-

sorów DSP zastosowano nowoczesne roz-

wi¹zanie polegaj¹ce na zastosowaniu tzw.

bardzo d³ugich s³ów kodu instrukcji VLIW

(Very Large Instruction Word). Rozwi¹zanie

to pozwala na osi¹gniêcie przez jednostkê

centraln¹ procesora potê¿nej mocy obli-

czeniowej, dziêki równoczesnemu stero-

waniu prac¹ omiu ró¿nych bloków funkcjo-

nalnych. Wród wy¿ej wymienionych bloków

funkcjonalnych mo¿na wyró¿niæ a¿ cztery

niezale¿ne jednostki mno¿¹ce, których za-

daniem jest maksymalne przypieszenie

przez zrównoleglenie algorytmów zwi¹za-

nych z cyfrow¹ obróbk¹ sygna³ów i obrazów.

Aby bardzo szybka jednostka obliczenio-

wa mog³a byæ na bie¿¹co zaopatrywana

w konieczne do wykonania obliczeñ dane,

procesory TMS320C6414, C6415 i C6416

wyposa¿ono w dwupoziomow¹ pamiêæ

podrêczn¹ (two-level cache memory) o ³¹cz-

nej pojemnoci 1056 kB. Aby pamiêæ

podrêczna tak du¿ych rozmiarów mog³a

wspó³pracowaæ z pamiêci¹ systemow¹, za-

stosowano 32-kana³owy tzw. wzbogacony

system bezporedniego dostêpu do pamiê-

ci EDMA (Enhanced Direct Memory Ac-

cess). Zastosowanie takiego uk³adu po-

zwala na zwiêkszenie przepustowoci stru-

mienia danych do 2 GB na sekundê.

n

Miros³aw Gajer

Artyku³ opracowano na podstawie:

Texas Instruments: Technology Innovations _ Analog

Edition, April 2001, Volume 8

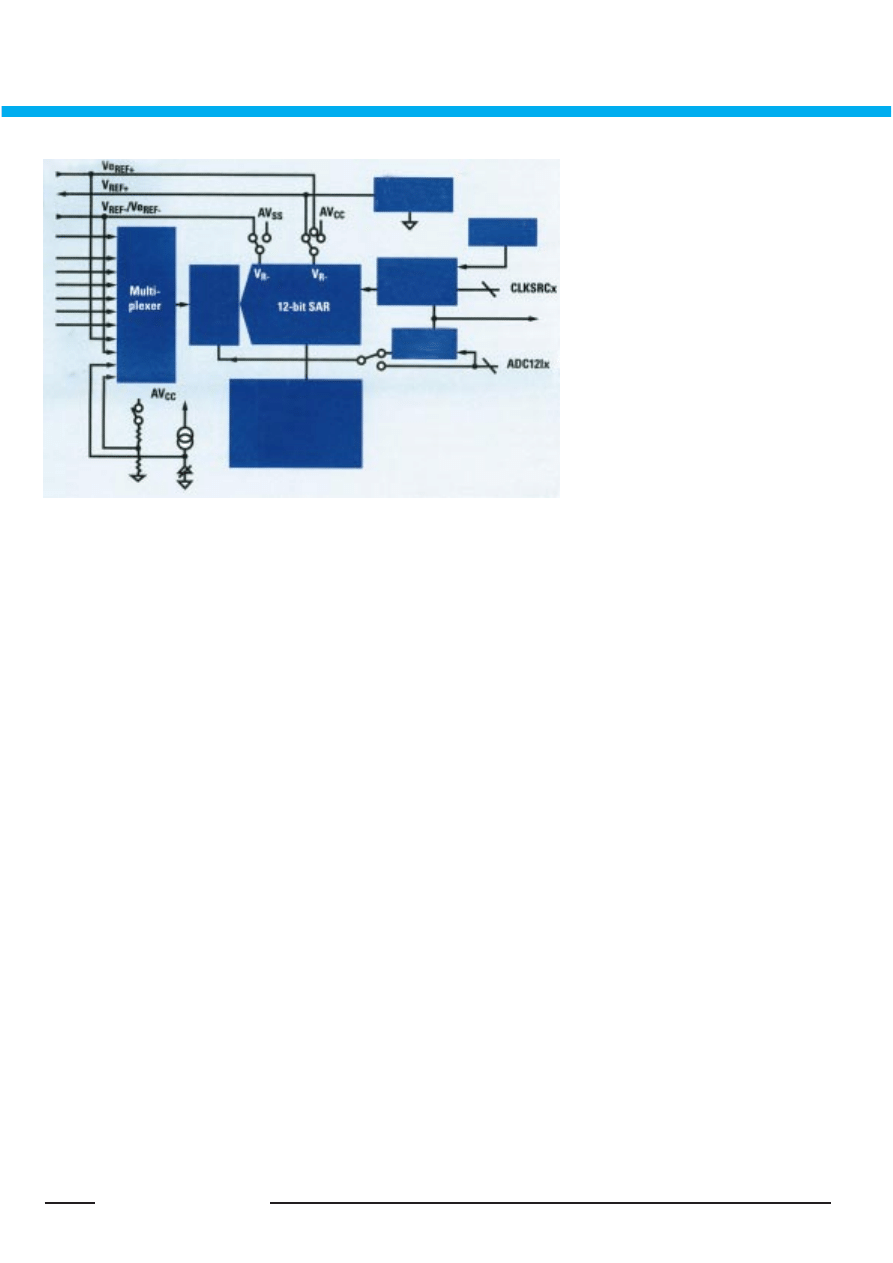

UP

UC

UK _ Uk³ad konwersji czêstotliwoci

sygna³u zegarowego

UC _ Uk³ad czasomierza

steruj¹cego uk³adem próbkuj¹cym

UP _ Uk³ad próbkuj¹co-pamiêtaj¹cy

SAR _ rejestr kolejnych przybli¿eñ

UK

Generator

U

REF

1,5 lub

2,5 V

12 x 16-bit

bufor pamiêciowy

Rys. 2. Schemat blokowy przetwornika analogowo-cyfrowego wchodz¹cego w sk³ad uk³adu MSP430F133

Radioelektronik Audio-HiFi-Video 8/2001

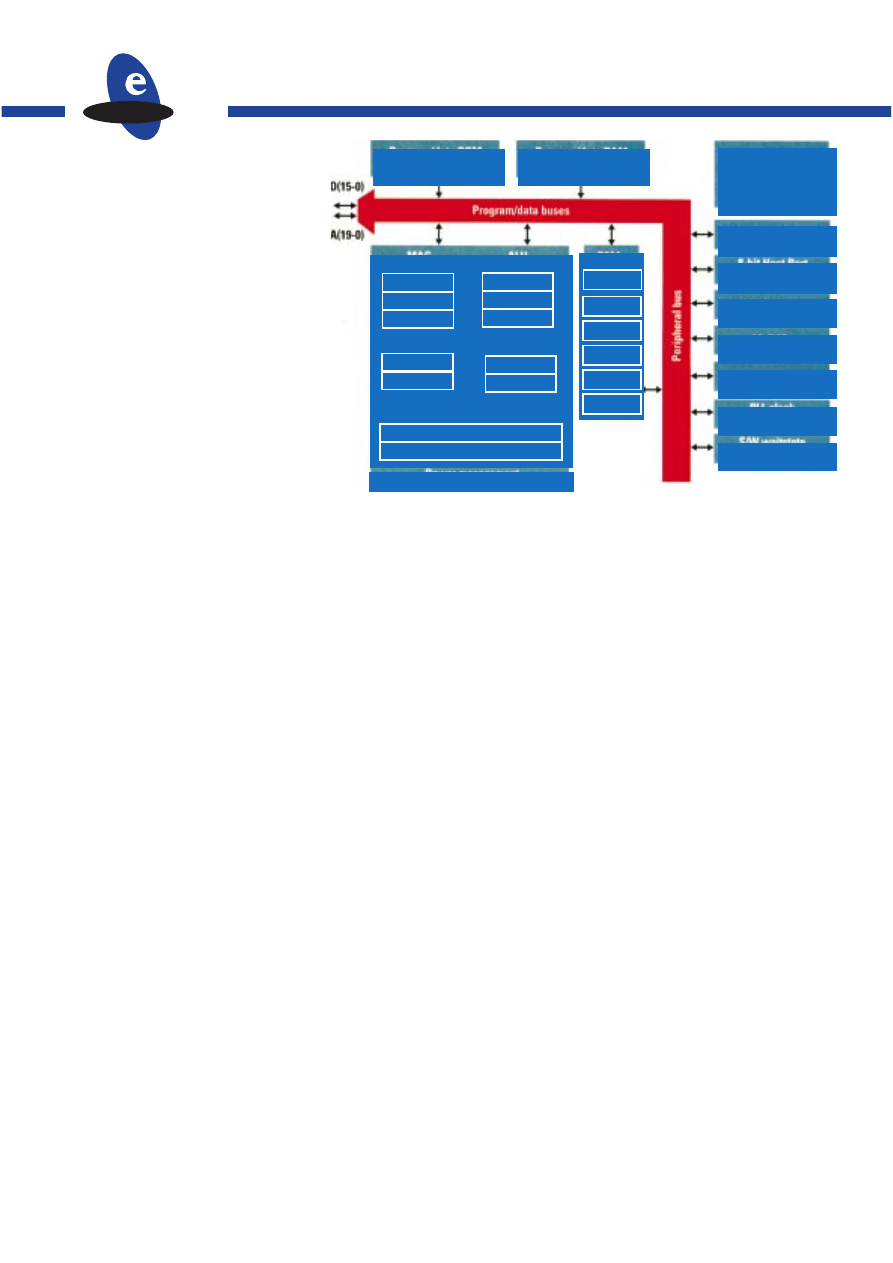

Dla potrzeb akwizycji danych w procesorach

TMS320C6414, C6415 i C6416 zastoso-

wano nastêpuj¹ce interfejsy:

* McBSP 0, McBSP 1 i McBSP 2 - interfej-

sy przeznaczone dla sygna³ów audio, zgod-

ny ze standardami: wielokana³owym

I2S oraz AC97

* EMIF 64 - kolejka FIFO s³u¿¹ca do po³¹-

czenia z pamiêci¹ zewnêtrzn¹

* EMIF 16 - dedykowana magistrala I/O

* PCI - interfejs z magistrali PCI o przepusto-

woci 133 MB na sekundê

Do typowych obszarów zastosowañ wy¿ej

wymienionych procesorów zalicza siê syste-

my telekomunikacyjne i teleinformatyczne,

a zw³aszcza stacje bazowe telefonii komór-

kowej, cyfrowe linie abonenckie (digital sub-

scriber line). Procesory te znajduj¹ równie¿

powszechne zastosowanie w wielu profesjo-

nalnych aplikacjach zwi¹zanych z cyfro-

wym przetwarzaniem obrazów, miêdzy inny-

mi w medycynie, nawigacji lotniczej, wojsko-

woci oraz w badaniach naukowych. Sche-

mat blokowy procesora TMS320C6415 zo-

sta³ zamieszczony na rys. 3.

Procesory DSP o zmniejszonym poborze

mocy

Nowy produkt firmy Texas Instruments typu

TMS320C5401 jest sta³oprzecinkowym pro-

cesorem DSP o mocy obliczeniowej 50

MIPS. Procesor ten zawiera wbudowan¹

pamiêæ o pojemnoci 8k s³ów oraz rozbudo-

wany zestaw bloków funkcjonalnych s³u-

¿¹cych do obs³ugi urz¹dzeñ peryferyjnych.

Zwrócenia uwagi wymaga szczególnie ma-

³e zapotrzebowanie procesora

TMS320C5401 na energie elektryczn¹,

które wynosi zaledwie 40 mW.

Procesor TMS320C5401 ma jedn¹ magi-

stralê s³u¿¹ca do pobierania z zewnêtrznej

pamiêci kodów rozkazów oraz trzy magistra-

le s³u¿¹ce do przesy³u danych. Wysoce

wyspecjalizowany zbiór instrukcji stanowi

podstawê elastycznego programowania te-

go procesora oraz jego du¿ej szybkoci

dzia³ania. Poniewa¿ kod programu i dane

umieszczone zosta³y w pamiêciach o roz-

³¹cznych przestrzeniach adresowych, mo¿-

liwe jest dokonywanie jednoczesnych dostê-

pów zarówno do danych, jak i do kodu pro-

gramu. Wprowadzenie takiej równoleg³o-

ci w dzia³aniu procesora TMS320C5401

decyduje o jego du¿ej szybkoci dzia³ania.

Ponadto procesor ten ma wbudowane me-

chanizmy kontrolne, które umo¿liwiaj¹ zarz¹-

dzanie przerwaniami, pêtlami programowy-

mi oraz wywo³aniami funkcji programowych.

Wbudowana w uk³ad scalony procesora

TMS320C5401 pamiêæ sk³ada siê z 8k s³ów

16-bitowej pamiêci RAM o tzw. podwójnym

dostêpie (dual-access). Pamiêæ taka ozna-

czana jest skrótem DARAM (Dual-Access

RAM) i jej cech¹ charakterystyczn¹ jest

umo¿liwienie jednoczesnego wykonania

podczas trwania jednego cyklu zegarowe-

go dwóch operacji odczytu lub jednej ope-

racji odczytu i zapisu.

Procesor TMS320C5401 zosta³ ponadto

wyposa¿ony w pamiêæ ROM o rozmiarze

4k s³ów 16-bitowych. W pamiêci tej zawar-

1

2

3

4

5

6

7

8

9

10

DMA

MAC ALU

Shifter Accumulators

Addressing unit

11

Ch 0

Ch 1

Ch 2

17 x 17 MPY

Ch 3

Ch 4

Ch 5

20

r

TELEKOMU

NIKCJA

Rys. 3. Schemat blokowy procesora TMS320C6415

Rys. 4. Schemat blokowy procesora TMS320C5401 (ze

wzglêdów technicznych opisy pozostawiono w jêzyku orygi-

na³u)

C:\Moje dokumenty\michal17\gaje-3.doc

1

7

C:\Moje dokumenty\michal17\podp.doc

ty jest tzw. program ³aduj¹cy (bootloader),

który jest wykorzystywany w celu automa-

tycznego za³adowania programu u¿ytkow-

nika, pochodz¹cego z zewnêtrznego ród³a,

do dowolnego obszaru pamiêci, w chwili

uruchomienia systemu.

Procesor TMS320C5401 jest pod wzglê-

dem programowym zgodny ze wczeniej-

szym procesorem firmy Texas Instruments

TMS320C5402, który zaledwie w ci¹gu ro-

ku po uruchomieniu produkcji sta³ siê praw-

dziwie wiatowym przebojem - najbardziej

popularnym procesorem DSP, którego licz-

ba sprzedanych sztuk osi¹gnê³a poziom 3

milionów.

Tworzenie aplikacji przeznaczonych dla pro-

cesora TMS320C5401 wspomagane jest

ze strony pakietu eXpressDSPTM (Real-

Time Software Technology), w sk³ad które-

go wchodzi:

* J¹dro systemu operacyjnego DSP/BIO-

STM (Real-Time Kernel)

* Zespó³ procedur implementuj¹cych algo-

rytmy cyfrowego przetwarzania sygna³ów

TMS320TM (DSP Algorithm Standard)

* rodowisko rozwoju oprogramowania Co-

de Composer StudioTM (Integrated Deve-

lopment Environment)

Procesor TMS320C5401 umieszczono

w obudowie o 144 wyprowadzeniach. Jego

schemat blokowy zamieszczono na rys. 4.

Procesor TMS320C5401 ponadto zintegro-

wano z nastêpuj¹cymi uk³adami peryferyj-

nymi, które zosta³y wbudowane w jego uk³ad

scalony:

* Programowalny z poziomu kodu programu

generator stanów oczekiwania (wait-state

generator), który umo¿liwia wstawienie do-

wolnej liczby stanów oczekiwania podczas

przeprowadzania operacji prze³¹czania ban-

ków pamiêci

* 8-bitowy interfejs komputera nadrzêdnego

HPI (Host-Port Interface) o rozszerzonych

mo¿liwociach

* Dwa wielokana³owe, buforowane porty

szeregowe McBSP (Multichannel Buffered

Serial Ports)

* Dwa sprzêtowe timery

* Generator przebiegu taktuj¹cego oparty na

pêtli synchronizacji fazowej PLL (Phase-

Lock Loop)

* Kontroler bezporedniego dostêpu do pa-

miêci DMA (Direct Memory Access)

Bardziej szczegó³owe informacje na temat

mikrokontrolerów z

rodziny

MSP430F13x/14x oraz omówionych pro-

cesorów DSP typu TMS320C6414, C6415,

C6416 oraz TMS320C5401 mo¿na znaleæ

na stronie internetowej firmy Texas Instru-

ments pod adresem http:// www.ti.com/sc/te-

chinnovations8

n

Miros³aw Gajer

Artyku³ opracowano na podstawie:

Texas Instruments: Technology Innovations

- Analog Edition, April 2001, Volume 8

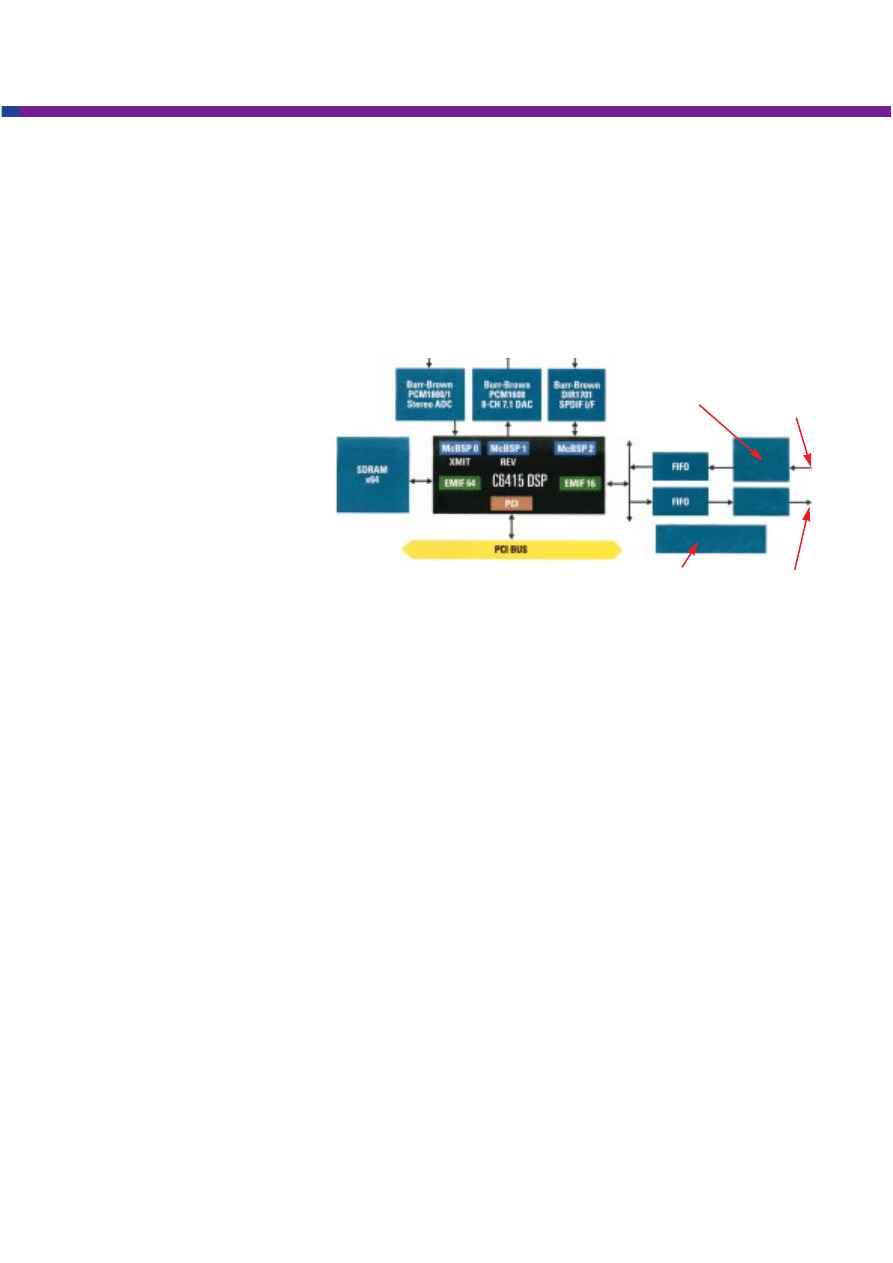

Stereo

we

7.1 Audio

wy

Wejcie

sygna³u

wizyjnego

Wyprowadzenie

sygna³u

wizyjnego

Uk³ad kontroli zasilania

i poboru mocy mikroprocesora

Uk³ad akwizycji danych

SPDIF

we

Wyszukiwarka

Podobne podstrony:

2001 08 28

2001 04 18

2001 08 42

2015 08 20 08 18 16 01

2001 04 18 0750

2001 08 38

2001 08 22 1680

2001 03 18

2001 08 14

2003 08 18

2001 08 26

2001 08 20

2001 08 Wykrywacz pluskiew

2015 08 20 08 18 49 01

2001 08 24

Everyday Practical Electronics 2001 08

2001 10 18

2001 08 16

więcej podobnych podstron