K U R S

Elektronika Praktyczna 11/2005

102

LiveDesign

w praktyce, część 9

W poprzedniej części cyklu

pokazaliśmy, w jaki sposób

rozpocząć projekt płyty

drukowanej pod układ FPGA.

Teraz, mając już skojarzone

ze sobą, projekt FPGA

i projekt PCB, pokażemy w jaki

sposób utrzymać ich spójność

i optymalizować projekt.

Przejście ze schematów do

PCB…

…wykonuje za nas automat, uru-

chamiany z menu Design>Update

PCB Document…

Wspomniany au-

tomat wykorzystuje potężny mecha-

nizm porównujący, zawarty w pro-

gramie Altium Designer, który wy-

krywa różnice pomiędzy dwoma

dowolnymi dokumentami i umożli-

wia synchronizację w obu kierun-

kach. W ten sposób synchronizuje

się np. zmiany na schemacie z PCB

i odwrotnie, porównuje dwa doku-

menty PCB lub PCB z listą połą-

czeń i wiele innych.

P i e r w s z e u r u c h o m i e n i e

funkcji Update PCB Docu-

ment…

z poziomu schematu,

powoduje przeniesienie wszyst-

kich elementów, połączeń i in-

nych informacji, ze schematu

na PCB. Przy każdej synchroni-

zacji, lista operacji jest widocz-

na w oknie Engineering Change

Order (ECO)

–

rys. 43.

W efekcie wykonania ECO,

na dokumencie PCB, obok

czarnego obszaru płyty, znaj-

dą się wszystkie elementy, po-

wiązanie pajęczyną linii, któ-

re symbolizują połączenia. Ele-

menty należy rozmieścić we-

wnątrz obszaru płyty, ręcznie

lub z pomocą automatu. Z na-

szego projektu nie zamierzamy

robić prawdziwej płyty dru-

kowanej, więc możemy sobie

pozwolić na odrobinę chaosu

i rozłożyć elementy w dowolny

sposób. Na przykład tak, jak

widać na

rys. 44.

Na potrzeby kursu, każ-

dą większą zmianę zapisujemy

w nowym pliku, pod własną na-

zwą, dlatego w naszym projek-

cie widać już kilka dokumen-

tów PCB. W rzeczywistych wa-

runkach pracujemy cały czas

z jednym dokumentem.

Dla nas istotny jest tyl-

ko związek pomiędzy powstałą

właśnie namiastką płyty druko-

wanej i projektem FPGA, któ-

ry na niej będzie uruchomio-

ny. Wspomnieliśmy już kilka-

krotnie, że Altium Designer

zapewnia synchronizację FPGA

z PCB na każdym etapie pro-

jektu. Aby się o tym upew-

nić, wystarczy otworzyć okien-

ko FPGA Workspace Map… do-

stępne z menu Project. Powin-

niśmy zobaczyć widok, jak na

rys. 45.

Zielone linie łączące ele-

ment U1 na płycie drukowa-

nej PCB_Placed.PcbDoc ze

schematem FPGA_U1_Auto.

SchDoc, a dalej ten schemat

z projektem Licznik_Johnso-

na.PrjFpga, oznaczają stan

synchronizacji pomiędzy pły-

tą PCB, schematem i projektem

FPGA. Dowolna zmiana w jed-

nym z tych elementów, któ-

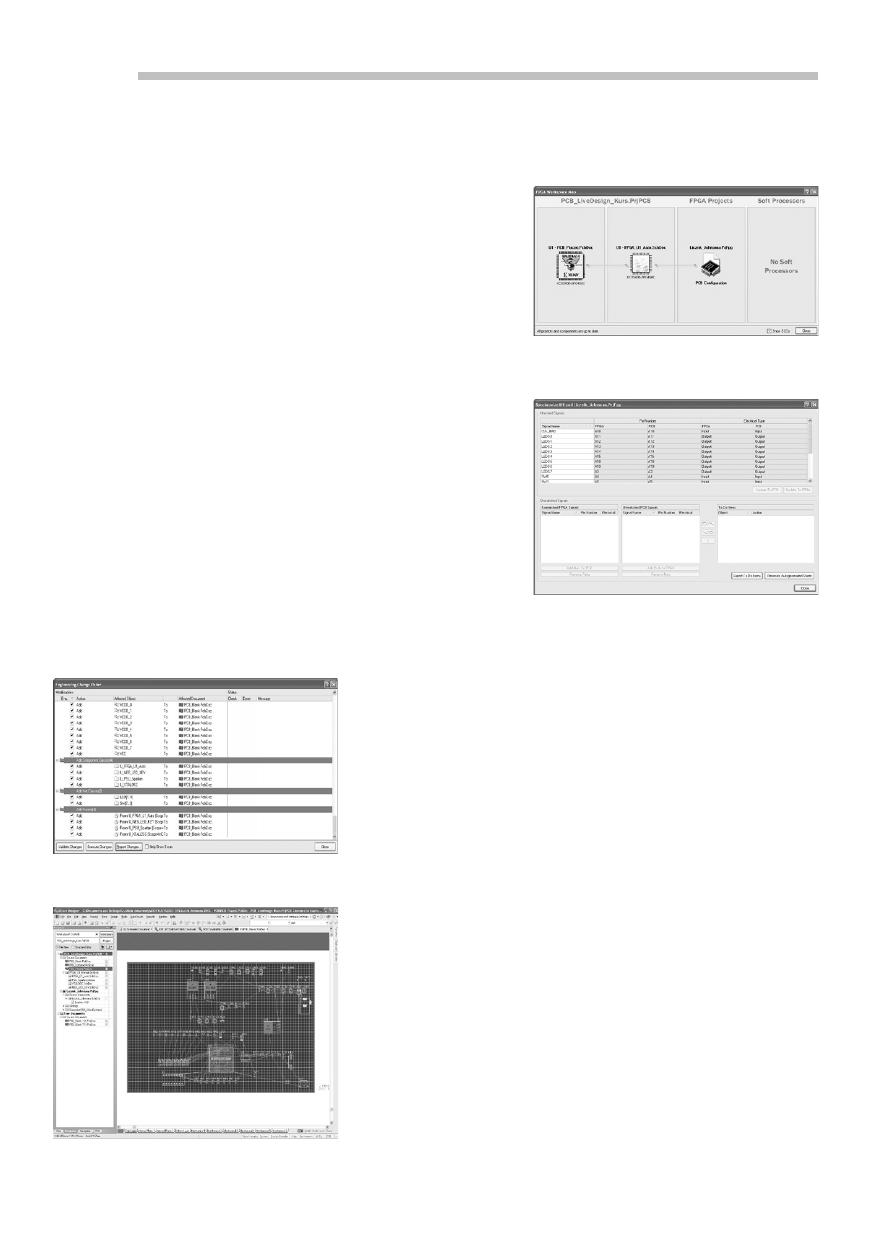

Rys. 43. Okno Engineering Change Order

przedstawia listę operacji i kierunek zmian

ra narusza spójność projektu, jest

wykrywana przez Altium Designer

i program pomaga nanieść zmia-

ny we wszystkich powiązanych do-

kumentach projektu. Jeśli kliknie-

my ikonę Licznik_Johnsona.PrjFp-

ga

w widoku FPGA Workspace Map,

pojawi się okno Synchronize U1

and Licznik_Johnsona.PrjFpga

, jak

na

rys. 46.

Widok pokazany na rys. 46

oznacza pełną synchronizację FPGA

z PCB. Nie ma żadnych sygnałów,

który wymagają zsynchronizowania,

więc obszar u dołu okna, oznaczo-

ny Unmatched Signals, jest pusty.

Dobrym przykładem na pokaza-

nie zagadnienia z praktycznej stro-

ny, jest optymalizacja projektu pły-

ty drukowanej pod kątem uprosz-

czenia przebiegu ścieżek i skrócenia

ich długości. Taki zabieg polega na

zamianie funkcji wyprowadzeń ko-

ści FPGA w projekcie PCB (tzw.

FPGA Pin Swapping

) i wymusza

przeniesienie tych zmian od pro-

jektu płyty drukowanej do projektu

FPGA. Ten i inne przykłady zmian

po stronie PCB, które wymuszają

modyfikacje projektu FPGA, pokaże-

my w kolejnej części kursu.

Grzegorz Witek, Evatronix

Rys. 44. Dokument PCB z rozmieszczonymi

elementami na płycie drukowanej

Rys. 45. Okno FPGA Workspace Map poka-

zuje łącza pomiędzy dokumentami projek-

tów FPGA i PCB

Rys. 46. Okno synchronizacji projektu FPGA

i PCB

Wyszukiwarka

Podobne podstrony:

psychozy alkoholowe 13.11.2005, Studia, Psychoprofilaktyka

Sadownictwo ćwicz 14.10.2005 i 04.11.2005, SADOWNICTWO

Programowanie obiektowe w PHP4 i PHP5 11 2005

11 2005 077 082

11 2005 043 047

11 2005 048

biuletyn 11 2005

rachunkowo 9c e6+bankowa+ +wyk b3ad+1+ 2816 11 2005 29 OLCPLSAV2E6GCT5FOI3SHOBIYYNTNVORFOT3BMY

analiza finansowa wyklad3 (9 11 2005) Q3TJYH3XOGYUT5L3CT63ZENJB6X6BQB2EENOY3I

rachunkowo 9c e6+zarz b9dcza+ w6 + 2822 11 2005 29 DKERWWEYLJDSOGBEW76AZUWYTXEOMOYROM5DUFA

Oznaczanie jonów chlorkowych oraz siarczków ver 1.0 beta, Gdańsk dnia: 21-11-2005

11 2005 089 093

EGZAMIN UZUPEŁNIAJĄCY& 11 2005

11 2005 100 101

11 2005 094 097

11 2005 029 032

11 2005 037 042

11 2005 063 070

więcej podobnych podstron