Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

1

Laboratorium

Techniki Cyfrowej i Mikrokomputerów

Sprawozdanie X

„Pamięci RAM i ROM”

Elbląg, 08.12.2006

Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

2

PAŃSTWOWA WYśSZA SZKOŁA ZAWODOWA W ELBLĄGU

INSTYTUT INFORMATYKI STOSOWANEJ

LABORATORIUM TECHNIKI CYFROWEJ I MIKROKOMPUTERÓW

Grupa dziekańska:

VII

Podgrupa ćwiczeniowa:

V

Tytuł ćwiczenia:

Pamięci RAM i ROM.

Data wykonania:

08.12.2006

Data oddania:

15.12.2006

Skład grupy:

1.

Sawicki Jarosław

2.

Szulc Dariusz

Ocena:

Pamięć jest elektronicznym układem scalonym, służącym do przechowywania danych. Znajduje się w

niej również program, wykonujący konkretne czynności, który składa się z podstawowych rozkazów

procesora. Procesor czyta z pamięci rozkazy, wykonuje je i zapisuje do niej wyniki pracy.

Funkcjonalność naszego komputera uzależniona jest w dużym stopniu właśnie od pamięci, ponieważ cała

praca procesora oparta jest na bitach znajdujących się w niej.

1. Pamięci RAM.

Pamięć RAM (ang. Random Access Memory) jest pamięcią o dostępie swobodnym, czyli przechowuje

aktualnie przetwarzane przez program dane oraz jego ciąg rozkazów. Z reguły pamięć ta jest uzależniona

od napięcia zasilającego, tzn., że w momencie wyłączenia komputera traci bezpowrotnie swoją

zawartość.

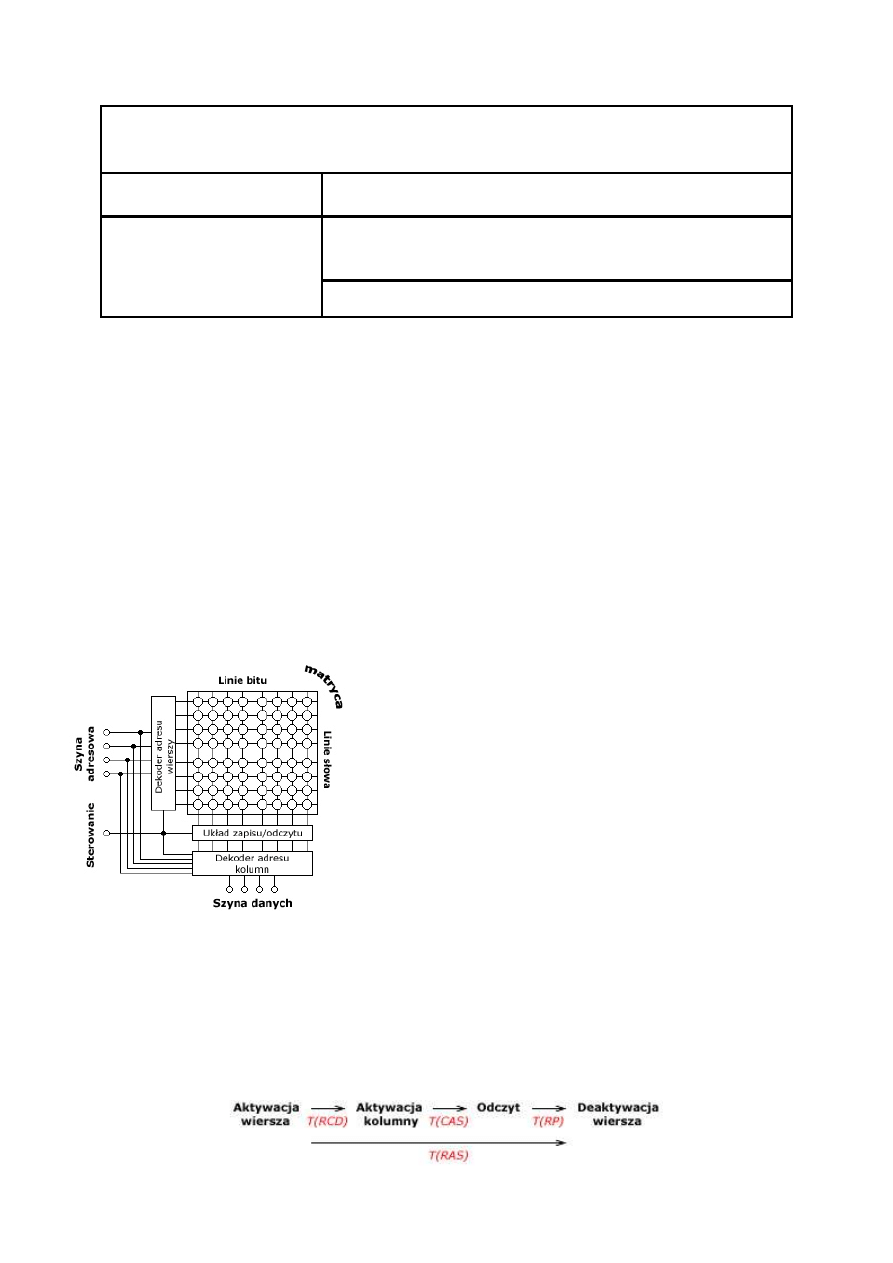

Układ pamięci RAM składa się z matrycy, dekodera i

układów zapisu (odczytu). Każda komórka tej pamięci

wchodzi w skład matrycy i zbudowana jest z pojedynczego

tranzystora i kondensatora. Potrafi ona przechowywać jeden

bit informacji. Poszczególne komórki posiadają swój adres,

czyli numer wiersza i kolumny.

Do poszczególnych komórek możemy odwoływać się w

dowolnej kolejności, dlatego pamięć ta została nazwana

pamięciom o dostępie swobodnym. Dekoder za pomocą

szyny adresowej, otrzymuje adresy komórek z kontrolera

pamięci. Docelowe komórki zostają odczytane i wówczas

ich zawartość jest wysyłana z powrotem do kontrolera szyną

danych.

Cykl pracy pamięci RAM jest wyznaczany za pomocą specjalnego zegara. Adresowanie i odczyt pamięci

zapoczątkowane zostają pojawieniem się sygnałów na szynie adresowej. Sygnał RAS (ang. Row Address

Strobe) informuje pamięć, że jest to adres rzędu matrycy, natomiast sygnał CAS (ang. Column Address

Strobe) informuje, że jest to adres kolumny matrycy. Na przecięciu wybranego rzędu i kolumny znajduje

się docelowa komórka, z której będą pochodzić dane.

Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

3

Na rysunku powyżej zaznaczono również parametr RP (ang. RAS Percharge), czyli czas upływający

pomiędzy odczytem komórki pamięci, a ponownym jej zapisem, oraz parametr RCD (ang. RAS to CAS

Delay), czyli czas upływający pomiędzy podaniem sygnału aktywacji wiersza, a podaniem sygnału do

aktywacji kolumny.

Pamięć RAM ma zastosowanie między innymi jako pamięć operacyjna komputera oraz jego

podzespołów (np. kart graficznych). Występuje w postaci układów scalonych oraz modułów.

1.1. Podział pamięci RAM.

A. Podział pamięci RAM ze względu na technologię wykonania układu scalonego:

•

SRAM (ang. Static RAM) – statyczna, nieulotna pamięć RAM, która do przechowywania danych nie

wymaga napięcia zasilającego. Dzięki krótkiemu czasowi dostępu, jest ona dużo szybsza od pamięci

dynamicznych. Wykorzystuje się ją do produkcji pamięci cache.

•

DRAM (ang. Dynamic RAM) – dynamiczna, ulotna pamięć RAM, która do przechowywania danych

wymaga napięcia zasilającego. Pamięć ta jest dużo wolniejsza od pamięci statycznych. Aby pamięć

nie utraciła danych, trzeba ją odświeżać. Odświeżanie może być realizowane sprzętowo lub

programowo, a w jego czasie odczyt zawartość komórki przez procesor staje się niemożliwy.

B. Podział pamięci RAM ze względu na rodzaje modułu:

•

SIMM (ang. Single In Line Memory Module) - pierwszy rodzaj modułu, zbudowany był z

krawędziowych złączy i pozwalał z łatwością na montaż i demontaż ze slotów. Konstrukcja pamięci

wyeliminowała potencjalne uszkodzenia pamięci przy jej montażu. Najszybsze moduły SIMM

posiadają czas dostępu 50 ns, natomiast najwolniejsze 120 ns.

•

DIMM (ang. Dual In Line Memory Module) – w tym module styki po obu stronach płytki drukowanej

nie są ze sobą powiązane. Najszybsze moduły DIMM posiadają czas dostępu poniżej 10 ns, natomiast

najwolniejsze 60 ns.

•

RIMM (ang. Rambus In Line Memory Module) – najszybsze i najdroższe układy na rynku, obecnie

już nie rozwijane. Wszystkie pamięci RIMM należy instalować parami.

C. Podział pamięci RAM ze względu na dostęp:

•

FPM RAM (ang. Fast Page Mode RAM) - pamięć ta zorganizowana jest w strony, przy czym

najszybciej realizowany jest dostęp do kolejnych komórek w obrębie strony.

•

EDO RAM (ang. Extended Data Output RAM) - jest to pamięć, w przypadku, której w czasie odczytu

danej komórki, może zostać pobrany adres następnej.

•

BEDO RAM (ang. Burst EDO RAM) - w przypadku tej pamięci zamiast jednego adresu pobierane są

cztery, przy czym na magistralę wystawiany jest tylko pierwszy, co znacznie zwiększa szybkość

dostępu.

Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

4

1.2. Symulacje pamięci RAM w programie MAX+PLUS II.

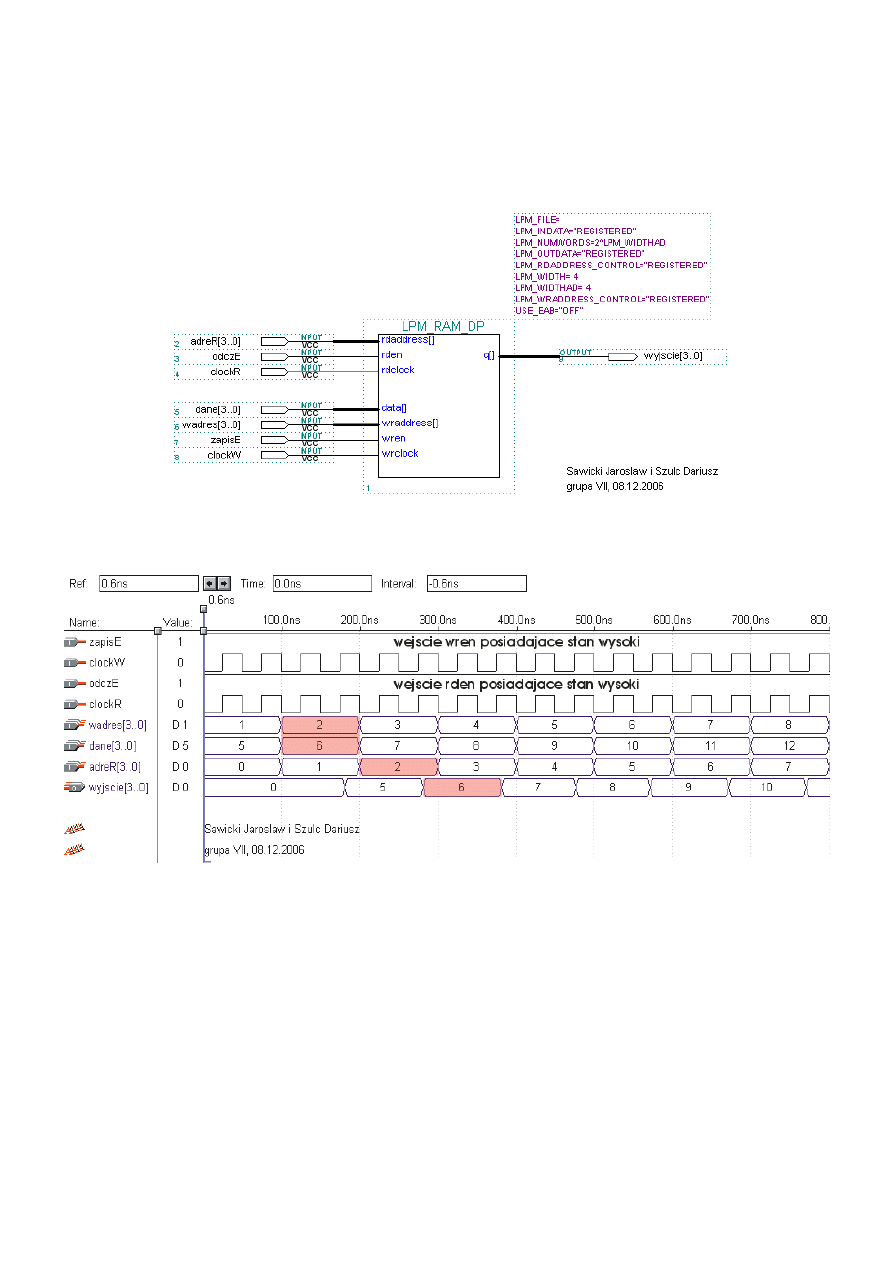

1.2.1. LPM_RAM_DP.

Schemat układu LPM_RAM_DP.

Symulacja układu LPM_RAM_DP.

Jednym z ważniejszych wejść jest wejście Rden (na symulacji odczE), które steruje operacją odczytu

danych z pamięci lub blokuje ten odczyt. Odczyt odbywa się, gdy na wejściu odczE ustawiony jest sygnał

wysoki, w przeciwnym wypadku odczyt jest blokowany. Obok wejścia Rden, uwagę należy również

zwrócić na wejście Wren (na symulacji zapisE), które steruje operacją zapisu danych do pamięci lub

blokuje ten zapis. Zapis odbywa się, gdy na wejściu zapisE ustawiony jest sygnał wysoki, w przeciwnym

wypadku zapis jest blokowany.

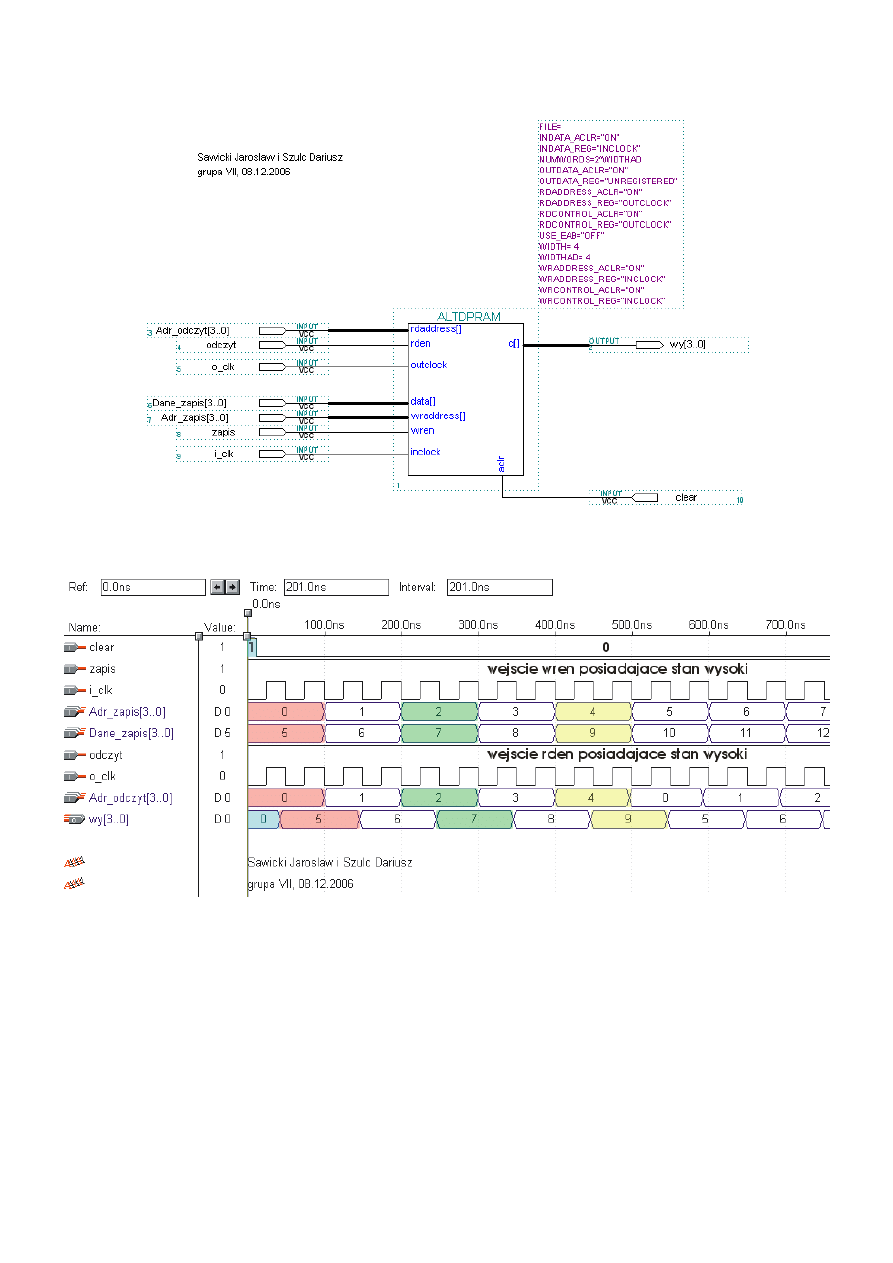

1.2.2. ALTDPRAM.

Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

5

Schemat układu ALTDPRAM.

Symulacja układu ALTDPRAM.

Wejście Aclr (na symulacji clear) umożliwia pracę całego układu lub blokuje tą pracę. Gdy na wejściu

clear ustawimy sygnał wysoki, wówczas praca układu zostanie zablokowana (zaznaczone kolorem

niebieskim). W przeciwnym wypadku układ będzie działał zgodnie z poniższymi zasadami. Sprawdzamy

adres 0 pamięci, na której wcześniej została zapisana wartość 5 (zaznaczone kolorem czerwonym) i tak

analogicznie.

1.2.3. LPM_RAM_DQ.

Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

6

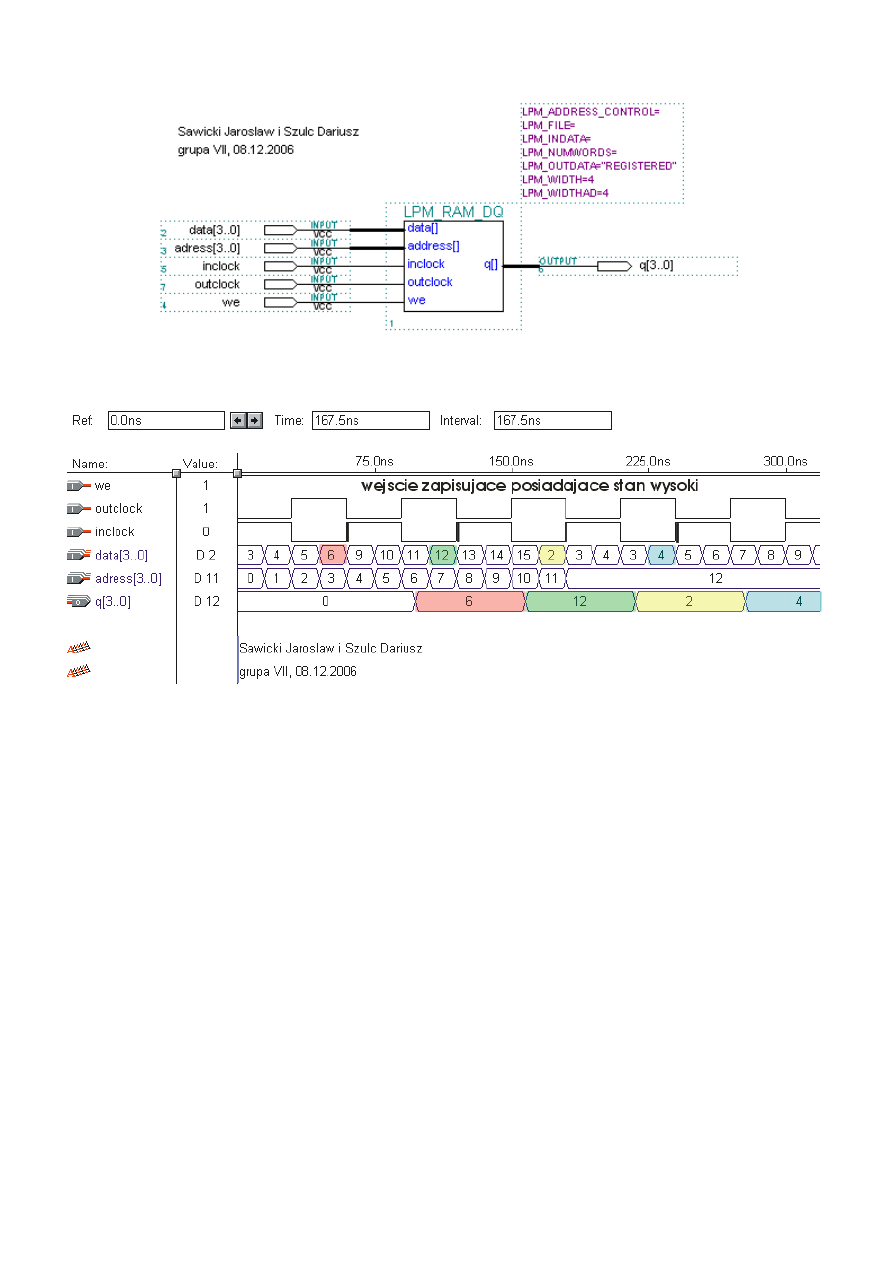

Schemat układu LPM_RAM_DQ.

Symulacja układu LPM_RAM_DQ.

Jak widać na powyższej symulacji wejście zapisujące we posiada stan wysoki. Wejście zegarowe inlock

synchronizuje się z wejściem zapisującym we. W momencie, gdy sygnał wejścia inclock zmienia swą

wartość ze stanu niskiego w wysoki (zaznaczone kolorem czarnym), na wyjście q podawana jest dana

wartość z szyny danych (zaznaczone odpowiednimi kolorami).

1.3. Porównanie pamięci RAM.

Dzięki programowi MAX+PLUS II, możemy zapoznać się z budową i działaniem kilku rodzajów

pamięci RAM, które różnią się od siebie ilością elementów, czy też działaniem. Jak widać pamięć

LPM_RAM_DP posiada największą ilość wejść, a jej symulacja charakteryzuje się największym

opóźnieniem. Pamięć ALTDPRAM charakteryzuje się wejściem Aclr, które może umożliwiać lub

blokować pracę całego układu. Dane są zapisywane po kolei i odczytywane na podstawie konkretnych

adresów. Natomiast pamięć LPM_RAM_DQ charakteryzuje się wejściem inclock, od którego zależy

moment wysyłania danych.

2. Pamięci ROM.

Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

7

Pamięć ROM (ang. Read Only Memory) jest pamięcią tylko do odczytu. Służy do przechowywania

danych potrzebnych do pracy danego urządzenia. Pamięć ROM nazywana jest pamięcią stałą, ponieważ

nie traci swej zawartości po zaniku napięcia zasilającego. Z tego powodu uznawana jest za najbardziej

niezawodny nośnik informacji o dużej gęstości. Zapis informacji w pamięci ROM, dokonuje się w

procesie produkcji lub podczas ich programowania. Pamięci typu ROM przeznaczone są głównie do

umieszczania w nich startowej sekwencji instrukcji, kompletnych programów obsługi sterowników i

urządzeń mikroprocesorowych, także ustalonych i rzadko zmienianych danych stałych.

2.1. Podział pamięci ROM.

•

PROM

(ang.

Programmable

ROM) - jest dostarczana przez producenta w stanie

niezaprogramowanym z możliwością jednokrotnego ustalania dowolnej zawartości bezpośrednio

przez użytkownika. Właściwą treść pamięci ustala się jednorazowo przez elektryczne przepalenie

odpowiednich połączeń wewnętrznych. Każda pomyłka w czasie programowania eliminuje

programowany układ.

•

EPROM (ang. Erasable Programmable ROM) - najpopularniejszy rodzaj pamięci kasowalnej i

programowalnej o nieulotnej zawartości informacji. Kasowanie zawartości dokonuje się przez

intensywne naświetlenie promieniem ultrafioletowym. Nie jest możliwe kasowanie pojedynczych

bajtów pamięci, natomiast proces przeprogramowania zawartości pamięci może być powtarzany

wielokrotnie. Przewidywany czas trwałości danych umieszczanych w pamięci EPROM wynosi co

najmniej 10 lat.

•

EEPROM (ang. Electrically Erasable Programmable ROM) - każdy bajt można kasować

elektrycznie i zapisać nową zawartością bezpośrednio w urządzeniu, w którym normalnie funkcjonuje

pamięć, a do zaprogramowania dowolnego bajtu wystarcza jeden cykl zapisu. Wykorzystanie tej

możliwości sprawia, że pamięć ta jest idealnym rozwiązaniem przy uruchamianiu nowego

oprogramowania, bądź modyfikacji zawartości istniejącej pamięci. Przyjmuje się, że pamięć

EEPROM powinna wytrzymać 100 tys. przeprogramowań.

2.2. Symulacje pamięci ROM w programie MAX+PLUS II.

2.2.1. LPM_ROM.

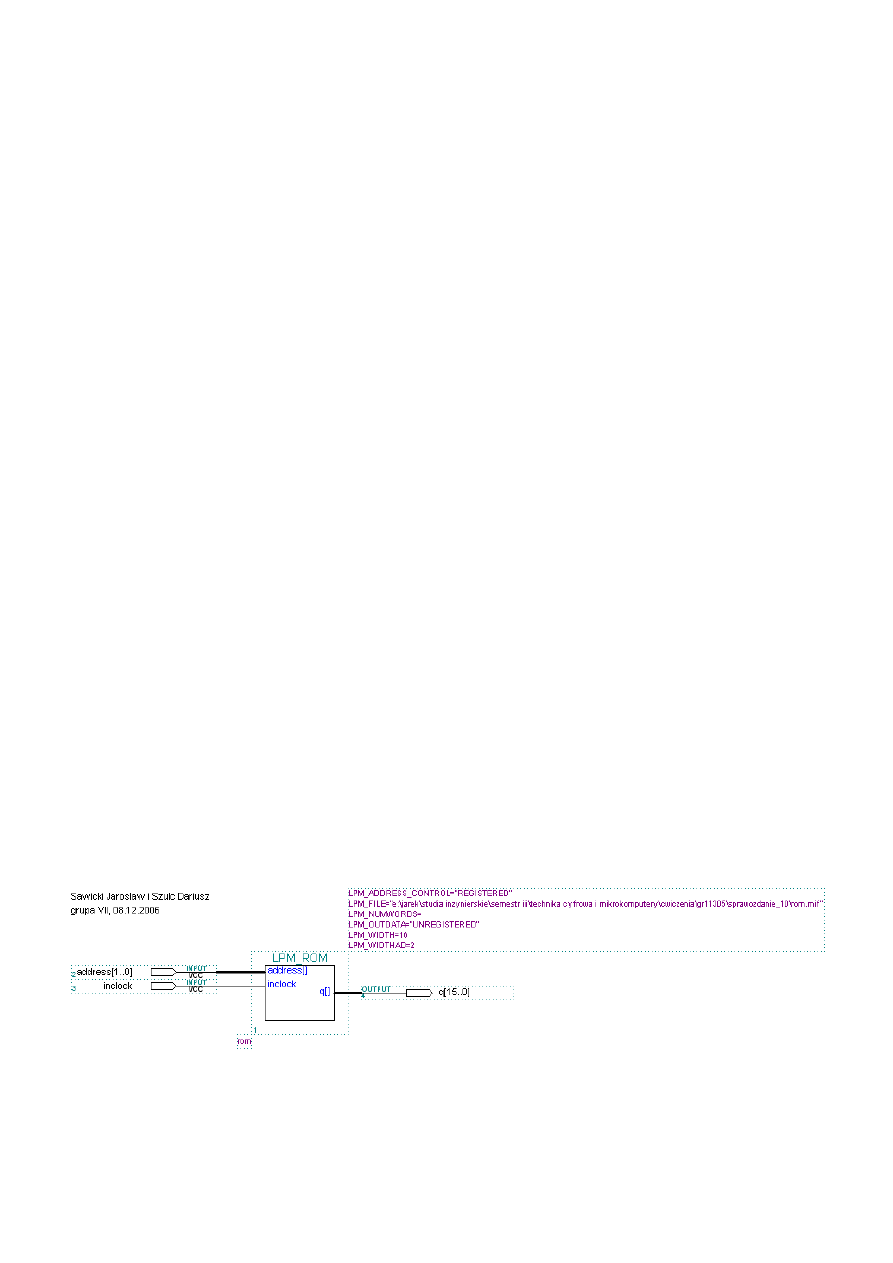

Schemat układu LPM_ROM.

Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

8

Plik rom.mif ma za zadanie wypełnić komórki pamięci danymi, czyli

zaprogramować pamięć. Jak można wyczytać z rysunku obok komórki

zaadresowane od 0 do 1 przyjmują wartość 2, natomiast komórki

posiadające adres 2 przyjmują wartość 4.

Symulacja układu LPM_ROM.

Jak widać na powyższej symulacji duże znaczenie odgrywa zmiana stanu niskiego w wysoki na wejściu

inclock (zaznaczone kolorem czarnym). Zmiana ta wskazuje nam adres, z którego wartość będzie

podawana na wyjście. Wartości te zostały już wcześniej zaprogramowane w pliku rom.mif. Przy odczycie

powyższej symulacji należy uwzględnić duże opóźnienie.

2.2.2. ROM.

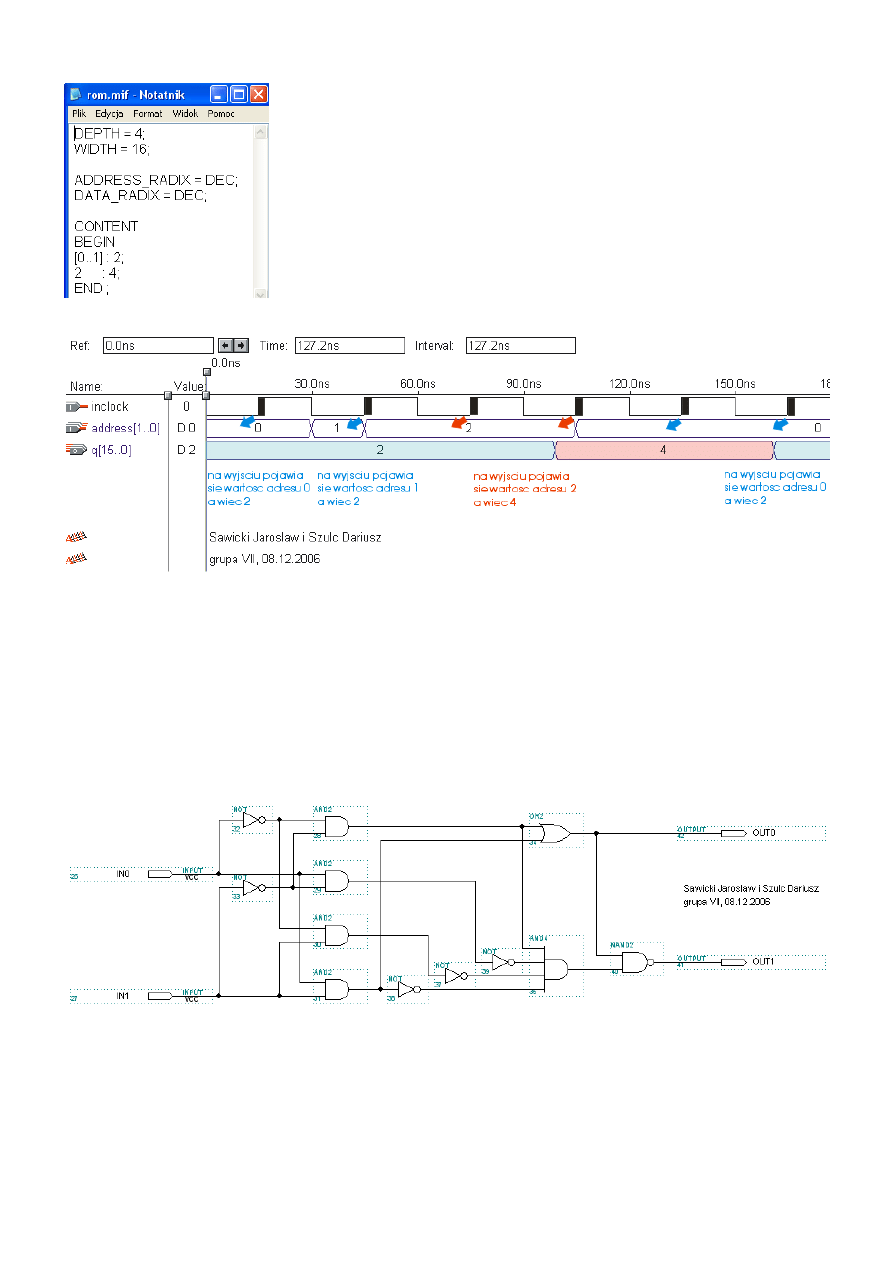

Schemat układu pamięci ROM.

Państwowa Wyższa Szkoła Zawodowa w Elblągu

Instytut Informatyki Stosowanej – Projektowanie Baz Danych i Oprogramowania Użytkowe

Sawicki Jarosław

Szulc Dariusz

9

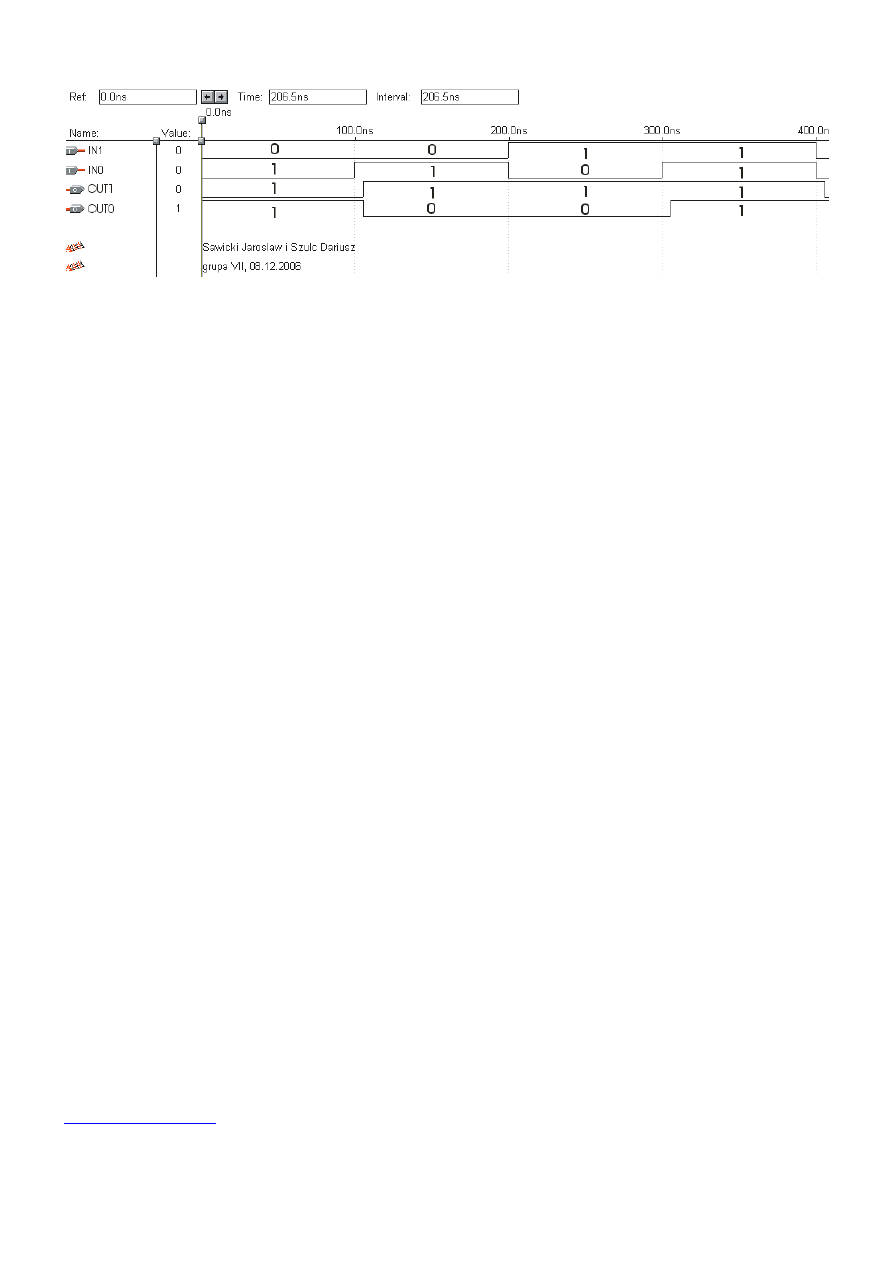

Symulacja układu pamięci ROM.

Pamięci ROM posiadają wejścia adresujące, dzięki którym można ustalić, z której komórki mają być

odczytywane dane.

3. Wnioski.

Program MAX+PLUS II firmy Altera jest doskonałym programem, służącym między innymi do

tworzenia i programowania różnego rodzaju pamięci. Jego dużą zaletą jest to, iż nawet człowiek

posiadający minimalną wiedzę na temat techniki cyfrowej jest w stanie zbudować prosty układ. Program

ten może jednak również służyć do budowy skomplikowanych układów. Staraliśmy się to pokazać w

przykładach wymienionych powyżej. Nie można w sposób definitywny określić, która z pamięci jest

najlepsza. Spowodowane jest to faktem, iż każda pamięć ma inne działanie, a także przeznaczenie.

4. Literatura.

http://www.timing.pl

Wyszukiwarka

Podobne podstrony:

Pamięć RAM ROM

co to jest pamięć ram, rom, hdd,?d, floppy, partycja, katalog, plik LHBD5E3LSXW26LJNUOWZ374VUUBOA5E

Pamięć RAM i ROM, Studia, Informatyka, Informatyka, Informatyka

pamięć RAM i ROM, Pomoce naukowe, studia, informatyka

Jak mieć wolną pamięć RAM, A TO POTRZEBNE

Jak sprawdzić ilość pamięci RAM (Windows 7 i Windows Vista)

Pamięci RAM

Pamiec RAM

pamiec RAM doświadczenie

pamiec RAM teoria

Testowanie modułów pamięci RAM

pamiec RAM tytuł

Pamieci RAM id 348388 Nieznany

Pamięć Ram

Pamiec-RAM, i inne

PODSTAWOWE WIADOMOŚCI NA TEMAT PAMIĘCI RAM, Studia, Informatyka, Informatyka, Informatyka

charakterystyka pamięci RAM, Pomoce naukowe, studia, informatyka

więcej podobnych podstron