LABORATORIUM

PODSTAWY

ELEKTRONIKI

PRZERZUTNIKI

2

Cel ćwiczenia

Zapoznanie się z budową i zasada działania przerzutników synchronicznych jak i

asynchronicznych. Poznanie przerzutników asynchronicznych odniesione jest do

przerzutników zrealizowanych na bramkach NAND i NOR, natomiast synchronicznych do

przerzutników typu JK, oraz D. Program ćwiczenia ma zostać zrealizowany na praktycznym

zestawieniu układów przerzutników do wymaganych zastosowań.

Przebieg ćwiczenia:

1.

Zapoznanie się z zasada działania przerzutników asynchronicznych RS wykonanych

jako układ bramek NAND oraz NOR. Następnie przerzutników synchronicznych D,

JK, T występujących na danym stanowisku laboratoryjnym, korzystając z instrukcji

2.

Przeprowadzić analizę stanów wyjściowych dla każdego przerzutnika

asynchronicznego.

3.

Ustalić odpowiedni poziom napięcia wejściowego oraz częstotliwość do prawidłowej

obserwacji sygnałów wyjściowych dla przerzutnika synchronicznego

4.

Przeprowadzić analizę stanów wyjściowych dla każdego przerzutnika

synchronicznego

5.

Zaprojektować i wykonać licznik modulo 2, oraz modulo 3 na przerzutnikach JK.

Liczniki maja zliczać w przód i tył. Przeprowadzić analizę stanów wyjściowych dla

każdego z liczników

6.

Zaprojektować i wykonać przerzutnik D zbodowany na przerzutnikach JK.

Przeprowadzić analizę stanów wyjściowych dla każdego z liczników

7.

Wyniki ćwiczenia umieścić w sprawozdaniu

3

Wiadomości podstawowe:

1.

Przerzutniki synchroniczne

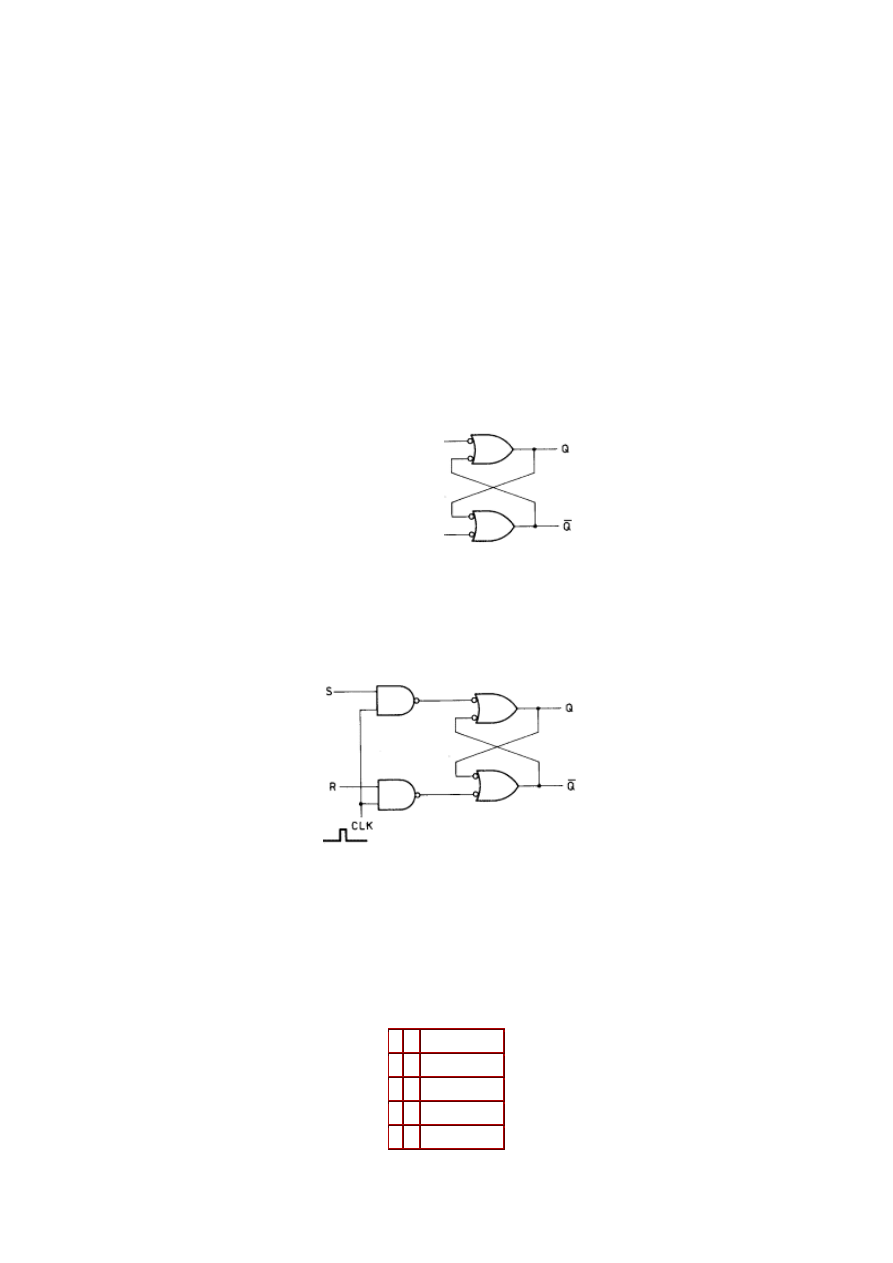

Przerzutniki zrobione z dwóch bramek, takie jak na rysunku 1, jest znany jako przerzutnik RS

(ang. set-reset) albo asynchroniczny (ang. jam loaded). Wymuszenie jednego lub drugiego

stanu takiego przerzutnika jest możliwe w dowolnej chwili przez doprowadzenie do

właściwego wejścia odpowiedniego sygnału wejściowego. Stosuje się je do usuwania drgań

zestyków i w wielu innych układach. Jednak najczęściej używane przerzutniki wyglądają

nieco inaczej. Zamiast dwóch wejść asynchronicznych mają dwa wejścia "danych" i jedno

wejście "zegarowe". Stan wyjścia może się zmieniać lub pozostać niezmieniony; zależy to od

stanu linii wejściowych (danych) tylko w czasie trwania impulsu zegara.

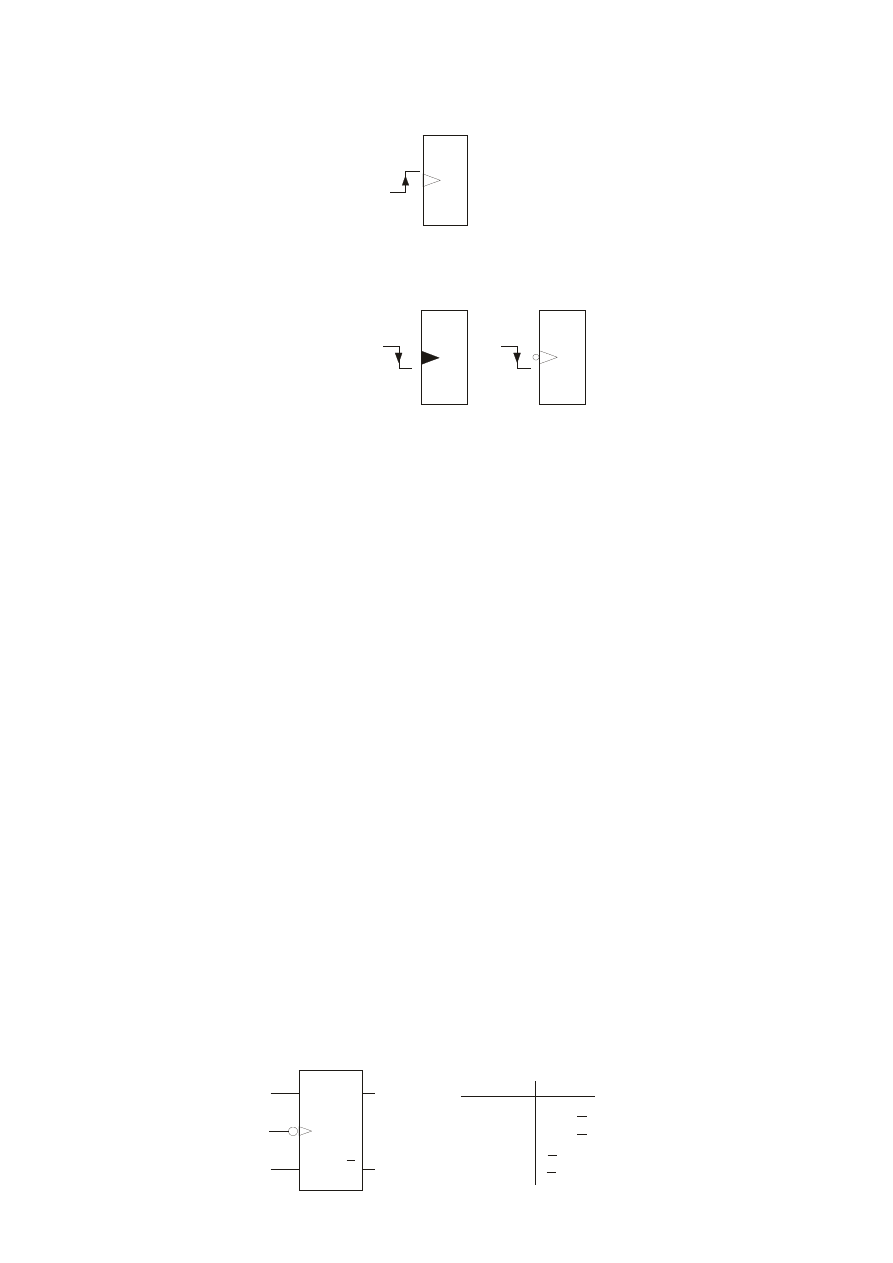

Rys. 1.

Schemat najprostszego przerzutnika taktowanego (synchronicznego)

.

Rys. 2.

Przerzutnik taktowany.

Jest to po prostu zwykły przerzutnik RS i para bramek (sterowanych przebiegiem

taktującym), które odblokowują wejścia zerujące i ustawiające. Łatwo sprawdzić, że jego

tablicą prawdy jest:

S

R

Q

n+1

0

0

Q

n

0

1

0

1

0

1

1

1

nieokreślony

R

S

4

gdzie Q

n+1

oznacza stan wyjścia po przejściu impulsu zegara, a Q

n

- stan wyjścia przed

pojawieniem się impulsu zegara. Podstawowa różnica między tym i poprzednimi

przerzutnikami polega na tym, że R i S mają teraz charakter wejść danych. Stan tych wejść w

czasie trwania impulsu zegara wymusza zachowanie się wyjścia Q. Przerzutnik ten ma jednak

jedną niewygodną właściwość. Stan wyjścia może zmieniać się w odpowiedzi na stan wejść,

gdy sygnał taktujący jest w stanie wysokim. W tym sensie jest to w dalszym ciągu przerzutnik

asynchroniczny (znany jest pod nazwą "przezroczystego zatrzasku", ang. transparent latch,

ponieważ jego wyjście "widzi" wejście, gdy sygnał taktujący jest w stanie wysokim)

5)

.

Prawdziwie pożyteczne przerzutniki to układy o nieco innych strukturach: przerzutnik

dwuzboczowy (ang. master-slave flip flop) i przerzutnik wyzwalany zboczem (ang. edge-

triggered flip-flop).

2. Przerzutniki dwuzboczowe i wyzwalane zboczem

Są to najbardziej popularne przerzutniki. Dane ustalone w liniach wejściowych tuż przed

zmianą stanu zegara, czyli jego "zboczem", wyznaczają stan wyjść ustalający się po przejściu

impulsu taktującego. Z uwagi na to, że są powszechnie dostępne w postaci tanich układów

scalonych, nie konstruuje się ich nigdy samodzielnie. Warto jednak zaznajomić się z ich

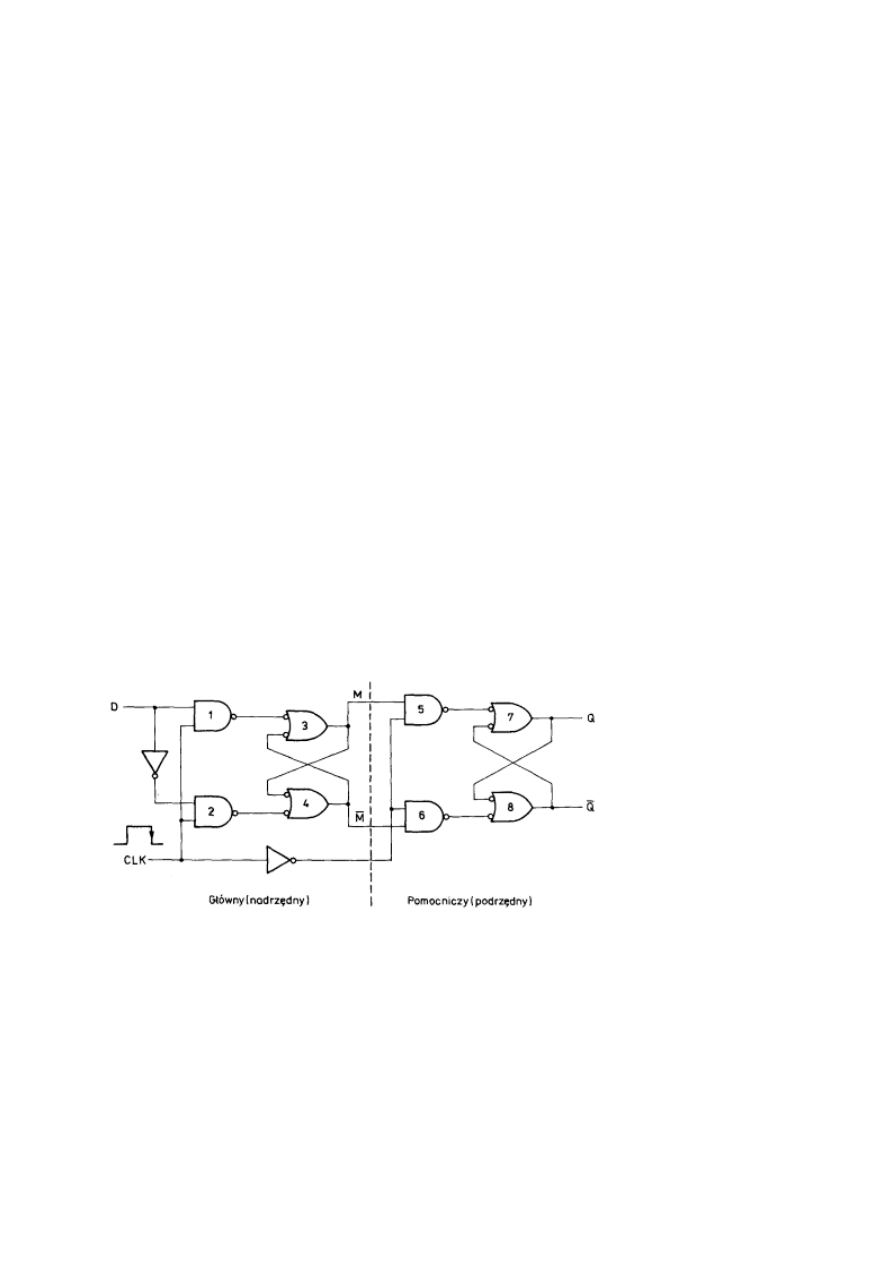

strukturą wewnętrzną, co pomoże zrozumieć zasadę ich działania. Na rys. 3a i 3b

przedstawiono odpowiednie schematy ideowe.

Rys. 3a.

5

Rys. 3b.

- Przerzutniki D wyzwalane zboczem

Oba układy to przerzutniki typu D. Stan wejścia D pojawi się na wyjściu po zakończeniu

impulsu zegara. Zasada działania przerzutnika dwuzboczowego będzie prawdopodobnie

łatwiejsza do zrozumienia. Oto jak on działa. Kiedy sygnał taktujący jest w stanie wysokim,

bramki 1 i 2 są odblokowane, wymuszając na pierwszym przerzutniku - wykonanym z

bramek 3 i 4 i nazywanym głównym (ang. master) - taki sam stan, jaki panuje na wejściu D:

M = D, M' = D'. Bramki 5 i 6 są zablokowane, więc drugi przerzutnik - wykonany z bramek 6

i 7 i nazywany pomocniczym (ang. slave) - zachowuje poprzedni stan. Kiedy na wejściu

zegarowym pojawia się opadające zbocze impulsu, wejścia przerzutnika głównego są

odłączone od wejścia D, jednocześnie wejścia przerzutnika pomocniczego są dołączone do

wyjść przerzutnika głównego. Wobec tego przerzutnik główny przekazuje swój stan

przerzutnikowi pomocniczemu. Na wyjściu nie zachodzą żadne inne zmiany, ponieważ

pierwszy przerzutnik został już "zatrzaśnięty". Przy następnym narastającym zboczu zegara

przerzutnik pomocniczy zostanie zablokowany i zachowa swój stan, podczas gdy przerzutnik

główny będzie ponownie reagował na stan wejścia. Przerzutnik wyzwalany zboczem

zachowuje się na zewnątrz tak samo, ale jego wewnętrzne działanie jest nieco inne. Analiza

pracy takiego przerzutnika nie jest trudna. Schemat przedstawiony na rysunku 3b pokazuje

uproszczoną strukturę wewnętrzną przerzutnika D wyzwalanego narastającym zboczem

impulsu zegara, którego dwa egzemplarze zamknięte w jednej obudowie tworzą popularny

układ scalony oznaczany symbolem '74. Wcześniej omówiony przerzutnik typu master-slave

przekazuje informację na wyjście zboczem opadającym. Istnieją przerzutniki wyzwalane

zarówno zboczem dodatnim, jak i ujemnym. Co więcej, większość przerzutników ma także

wejścia asynchroniczne typu SET (ustawiające) i CLEAR (zerujące). Zerowanie i ustawianie

może być wykonywane poziomem niskim lub wysokim, zależnie od typu przerzutnika. Kilka

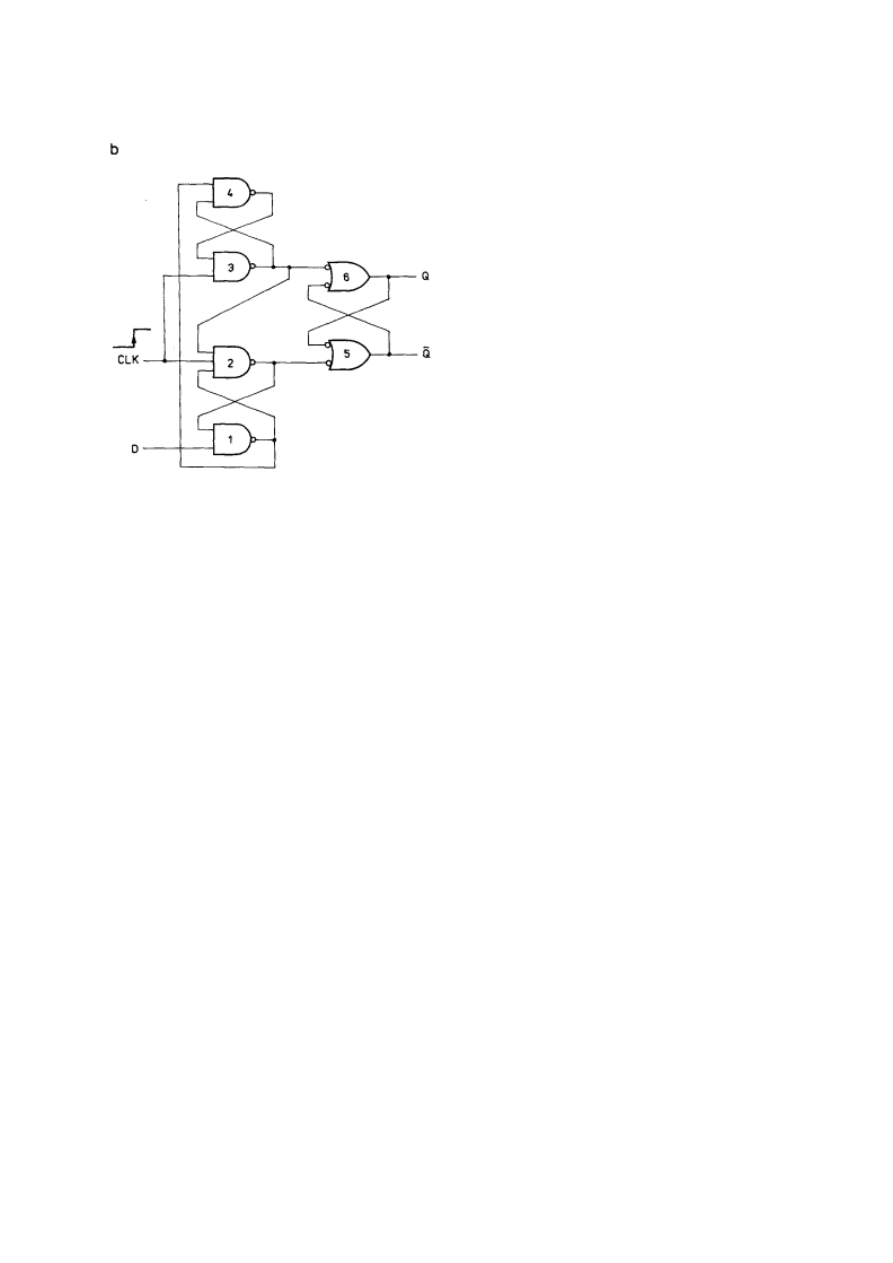

popularnych przerzutników pokazano na rysunku 4.

6

Rys. 4. - Przerzutnik D i JK

Mały klin oznacza "wyzwalany zboczem", małe kółeczko oznacza "negację" lub

uzupełnienie. Tak, więc układ '74 jest podwójnym przerzutnikiem typu D, wyzwalanym

zboczem narastającym, z wejściami asynchronicznymi SET i CLEAR aktywnymi poziomem

niskim. Układ 4013 (CMOS) jest podwójnym przerzutnikiem typu D, wyzwalanym zboczem

narastającym, z wejściami asynchronicznymi SET i CLEAR aktywnymi poziomem wysokim.

Układ '112 jest podwójnym przerzutnikiem typu JK, w którym przekazywanie danych na

wyjście odbywa się na zboczu opadającym i który ma wejścia asynchroniczne SET i CLEAR

aktywne poziomem niskim.

Przerzutnik JK. Zasada działania przerzutnika JK jest podobna do zasady działania

przerzutnika D z tą różnicą, że ma on dwa wejścia danych. Oto tablica prawdy:

J

K

Q

n+1

0

0

Q

n

0

1

0

1

0

1

1

1

Q'

n

Wynika z niej, że jeżeli stany na wejściach J i K są różne, to przy następnym aktywnym

zboczu zegara wyjście Q znajdzie się w stanie określonym, przez J. Jeżeli J i K są w stanie

niskim, to stan wyjścia się nie zmieni. Jeżeli J i K są w stanie wysokim, to stan wyjścia będzie

się zmieniał na przeciwny przy każdym kolejnym impulsie zegara

3. Przerzutniki JK

Przerzutnik jest to najprostszy układ sekwencyjny. Przerzutniki dzielimy na

synchroniczne tzn. takie, w których występuje, (co najmniej jeden) wyróżniony sygnał

zwany przebiegiem zegarowym, taktującym lub synchronizującym. Przebieg ten

wyznacza cykl pracy układu, a jego okres stanowi umowną jednostkę czasu. Sygnał

zegarowy określa chwile, w których stany wejść oddziałują na układ. Chwile te są

wyznaczane przez zbocze dodatnie bądź ujemne przebiegu taktującego, dlatego mówimy

o synchronizacji układu zboczem narastającym lub opadającym. W chwilach tych stan

innych wejść nie powinien się zmieniać. Odcinek czasu pomiędzy dwoma kolejnymi

zboczami aktywnymi sygnału zegarowego jest nazywany okresem.

Dla oznaczania sposobu wyzwalania danego przerzutnika stosuje się symbole

przedstawione na poniższym rysunku:

7

a)

wyzwalanie zboczem dodatnim.

b)

wyzwalanie zboczem ujemnym.

Są także przerzutniki synchroniczne wyzwalane poziomem.

Drugą grupę stanowią przerzutniki asynchroniczne, w których każda zmiana stanu

wejść układu oddziałuje na układ, powodując jego reakcję.

Układy synchroniczne z racji oddziaływania wejść na wyjścia tylko w chwilach

określonych przez sygnał zegarowy są układami bardziej odpornymi na zakłócenia niż

układy asynchroniczne.

Badany przez nas przerzutnik JK jest właśnie układem synchronicznym z racji

posiadania wejścia taktującego. Reaguje więc on na informację tylko w obecności

impulsu zegarowego, przy czym stan wejść informacyjnych powinien być wówczas już

ustalony i nie zmieniać się.

Każdy przerzutnik używany w technice cyfrowej jest układem, o co najmniej dwóch

wejściach i z reguły dwóch wyjściach. Wejścia mogą być:

-

zegarowe (inaczej: synchronizujące, wyzwalające). Wejście to oznaczane jest literą C

lub oznaczeniami: CK, CL, CP, CLK. (przy czym występuje ono tylko w

przerzutnikach synchronicznych).

-

informacyjne.

-

programujące, przygotowujące.

Wejścia programujące są wejściami asynchronicznymi i nadrzędnymi w stosunku do

pozostałych wejść. Ich nadrzędność wraża się tym, że przy sterowaniu przerzutnika od strony

pozostałych wejść o stanie przerzutnika decydują wyłącznie wejścia programujące.

Działanie przerzutnika w naszym przypadku opisaliśmy za pomocą tzw. tablicy

wzbudzeń, która określa, jaki powinien być stan wejść informacyjnych, aby przerzutnik

przeszedł z jednego stanu do drugiego.

3.1. Przerzutnik synchroniczny typu JK.

Symbol graficzny oraz tablicę wzbudzeń przedstawia rysunek:

J

K

C

Q

Q

Q J K

0 0 0

0 1 1

1 0 1

1 1 0

Q

+

8

Przerzutnik ma dwa wejścia informacyjne oznaczone literami J i K oraz wejście

zegarowe C. Wejście J = 1 ustawia przerzutnik w stan 1, a wejście K = 1 ustawia

przerzutnik w stan 0. Dla stanu J = 0 i K = 0 przerzutnik ten pamięta stan poprzedni.

Podanie stanu J = 1 i K = 1 sprawia, przerzutnik zmienia swój stan na przeciwny w

stosunku do poprzedniego.

Wszystkie zmiany wyjść zachodzą w obecności aktywnego zbocza impulsu

zegarowego podanego na wejście C (dla oznaczenia na rys. jest to zbocze opadające).

Działanie dynamiczne przerzutnika wyzwalanego opadającym zboczem impulsu

zegarowego obrazuje przebieg zdjęty z wejść i wyjść układu.

C

J

K

Q

Q

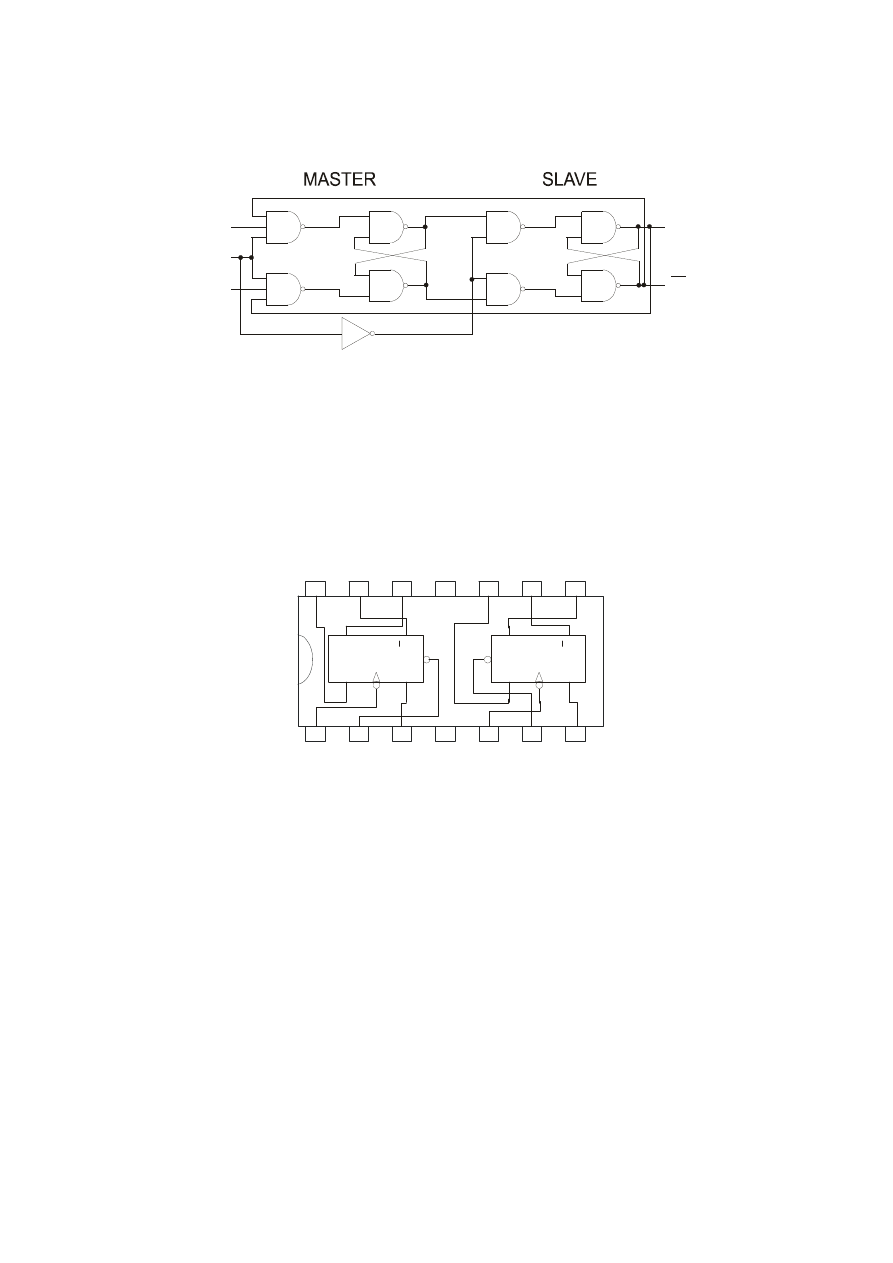

3.2. Przerzutnik synchroniczny typu JK – MS.

Przerzutnik typu JK może być synchronizowany zboczem ujemnym, dodatnim

lub poziomem, a także może być przerzutnikiem dwutaktowym, co oznacza, że do

ustawienia stanu przerzutnika są wymagane dwa kolejne zbocza impulsu zegarowego

tzn. cały pojedynczy impuls prostokątny.

Przerzutnik taki nazywamy przerzutnikiem kategorii Master – Slave, w skrócie

MS (master – pol. Pan, slave - pol. sługa).

Przerzutnik dwutaktowy (MS) działa w ten sposób, że w czasie pierwszego zbocza

(narastającego) są próbkowane stany wejść J i K, drugie zbocze (opadające) powoduje

zgodną z tablicą przejść zmianę stanu przerzutnika. W rezultacie zmianę stanu

obserwujemy przy opadającym zboczu impulsu zegarowego i dlatego symbol

graficzny takiego przerzutnika mówi nam, że jest to przerzutnik reagujący na

opadające zbocze impulsu zegarowego. Ogólnie rzecz biorąc kolejność zboczy może

być odwrócona, czyli czytanie wejść może być przy zboczu ujemnym, a zmiana stanu

wyjść przy zboczu dodatnim.

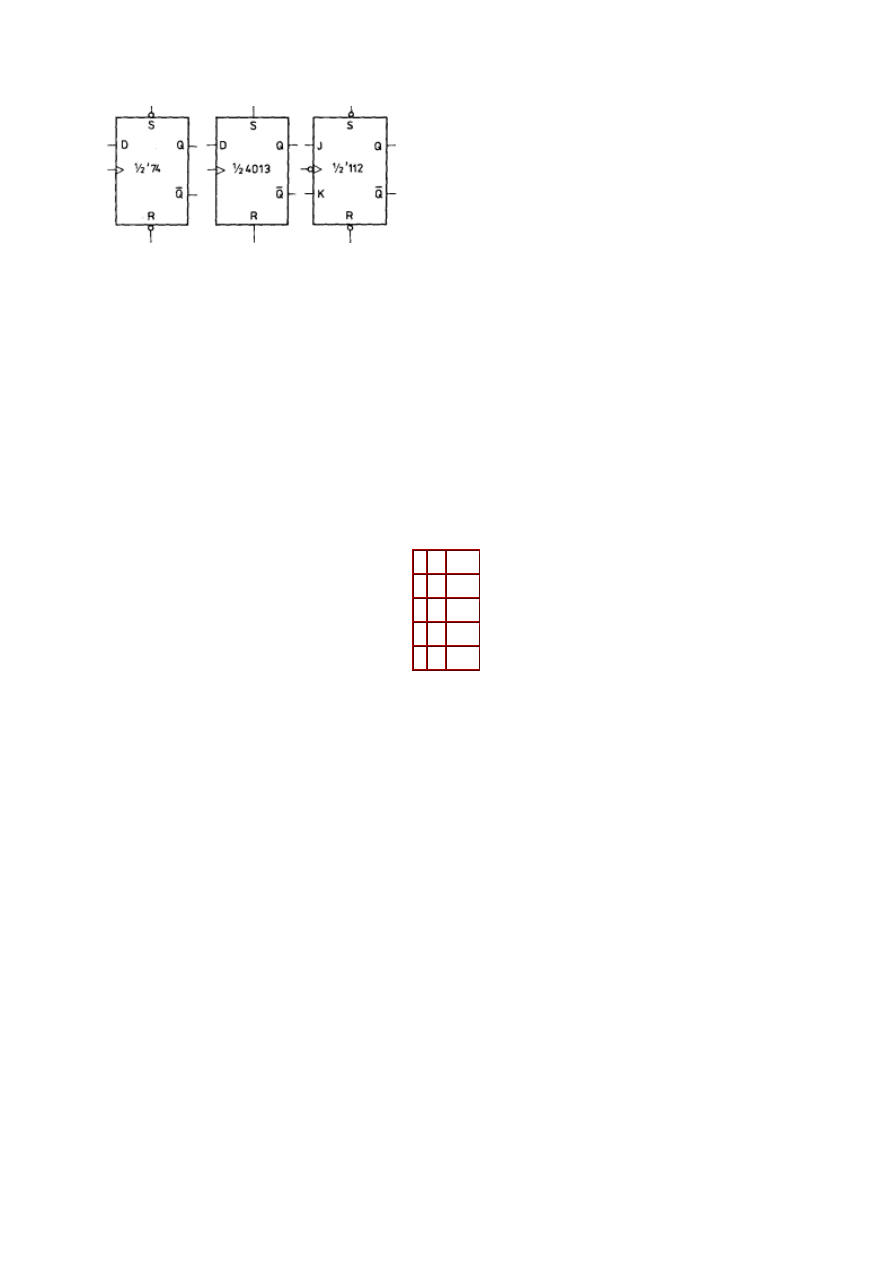

Jak przedstawia poniższy rysunek, przerzutnik dwutaktowy składa się z dwu

przerzutników połączonych kaskadowo. Pierwszy z nich nazywany jest Master (M),

drugi Slave (S).

J

K

C

Q

Q

J

K

C

Q

Q

9

Schemat logiczny takiego rozwiązania:

Dla zapewnienia poprawnej pracy przerzutnika sygnały na wejściach informacyjnych

powinny być ustalone przez cały czas trwania impulsu zegarowego. Zmiana stanu wejść JK

podczas aktywnego zbocza impulsu zegarowego może spowodować niezgodne z tablicą

przejść działanie przerzutnika.

Przykładem scalonego przerzutnika typu JK – MS może być układ 7473 zawierający

w swej strukturze dwa niezależne przerzutniki z wyprowadzonym wejściem zerującym

reagującym na stan niski (CLR).

W układach cyfrowych zawierających przerzutniki należy liczyć się z możliwością

przypadkowego ustalenia stanu układu po włączeniu zasilania. Wobec tego na ogół wymaga

się sprowadzenia układu do stanu początkowego przed rozpoczęciem pracy. Takie wstępne

przygotowanie układu osiąga się za pomocą wejść zerujących wprowadzających wyjście

przerzutnika w stan niski lub wejść ustawiających wprowadzających wyjście przerzutnika w

stan wysoki na wyjściu, przy czym niedozwolona jest jednoczesna aktywacja obu tych wejść.

J

K

C

Q

Q

1

14

7493

GND

Vcc

J

K

C

Q

Q

J

K

C

Q

Q

C

L

R

C

L

R

10

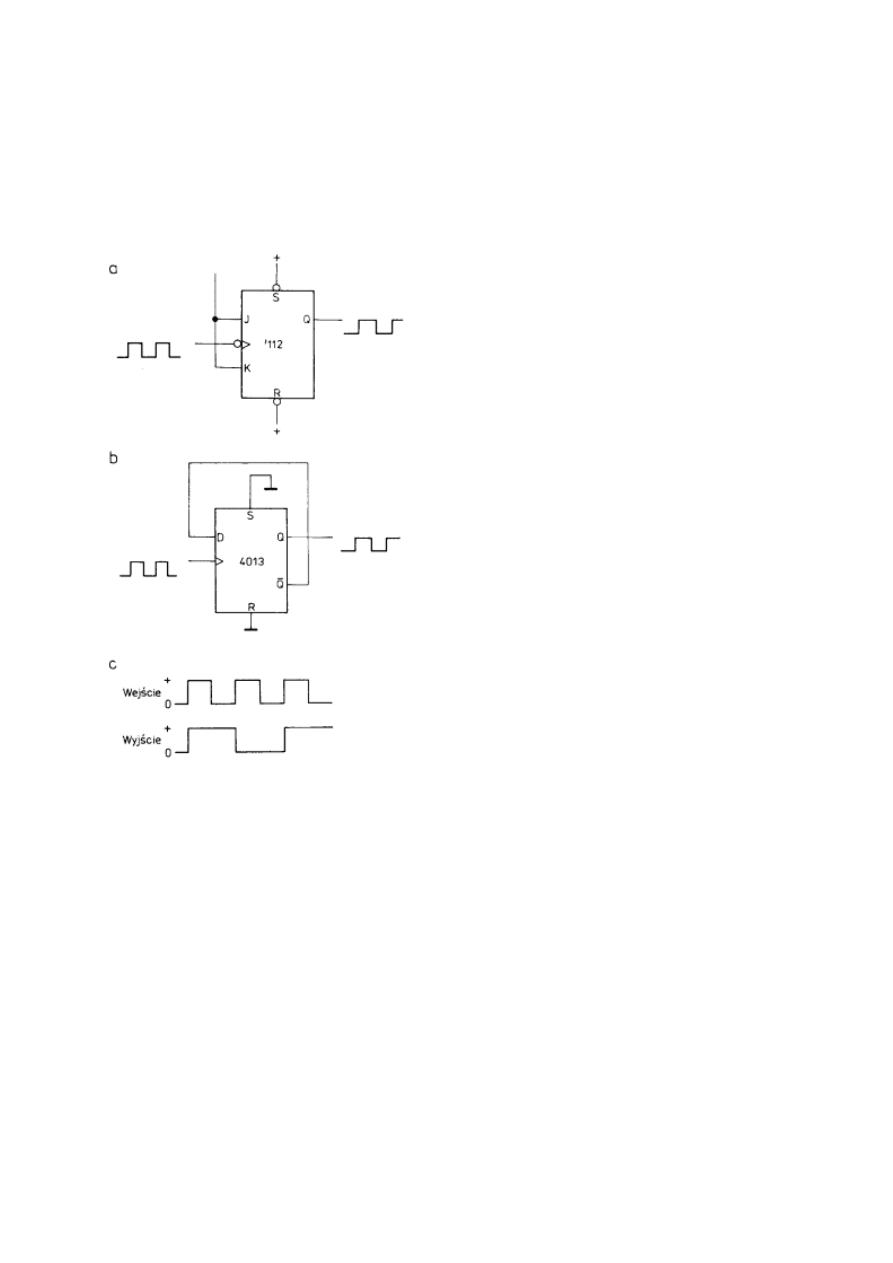

4. Dzielniki częstotliwości

4.1. Dzielniki częstotliwości przez 2

Wykorzystując właściwość przerzutnika, polegającą na zmianie stanu po każdym impulsie

zegara, można łatwo wykonać układ dzielenia częstotliwości przez 2. Dwa przykłady takiego

układu pokazano na rys. 5.

Rys. 5. - Przerzutniki w układach dzielników częstotliwości przez 2

Przerzutnik JK zmienia stan na przeciwny po każdym impulsie zegara, gdy jego oba

wejścia utrzymywane są w stanie wysokim. Tę samą funkcję spełnia również drugi układ,

ponieważ do wejścia D przerzutnika jest doprowadzany sygnał z jego własnego wyjścia

Q'. Wobec tego w momencie nadejścia impulsu zegara przerzutnik D widzi na wejściu

negację swojego własnego stanu. W każdym przypadku częstotliwość przebiegu

wyjściowego jest dwukrotnie mniejsza od częstotliwości przebiegu wejściowego.

4.2. Dzielniki częstotliwości przez 2

n

Łącząc kaskadowo kilka dzielników przez 2 (tzn. łącząc wyjście Q każdego przerzutnika z

wejściem zegarowym następnego przerzutnika) uzyskuje się układ dzielnika przez 2

n

,

czyli licznika binarnego. Na rysunku 6 pokazaliśmy 4-stopniowy licznik asynchroniczny z

przeniesieniem szeregowym (ang. ripple counter) oraz jego przebiegi czasowe.

11

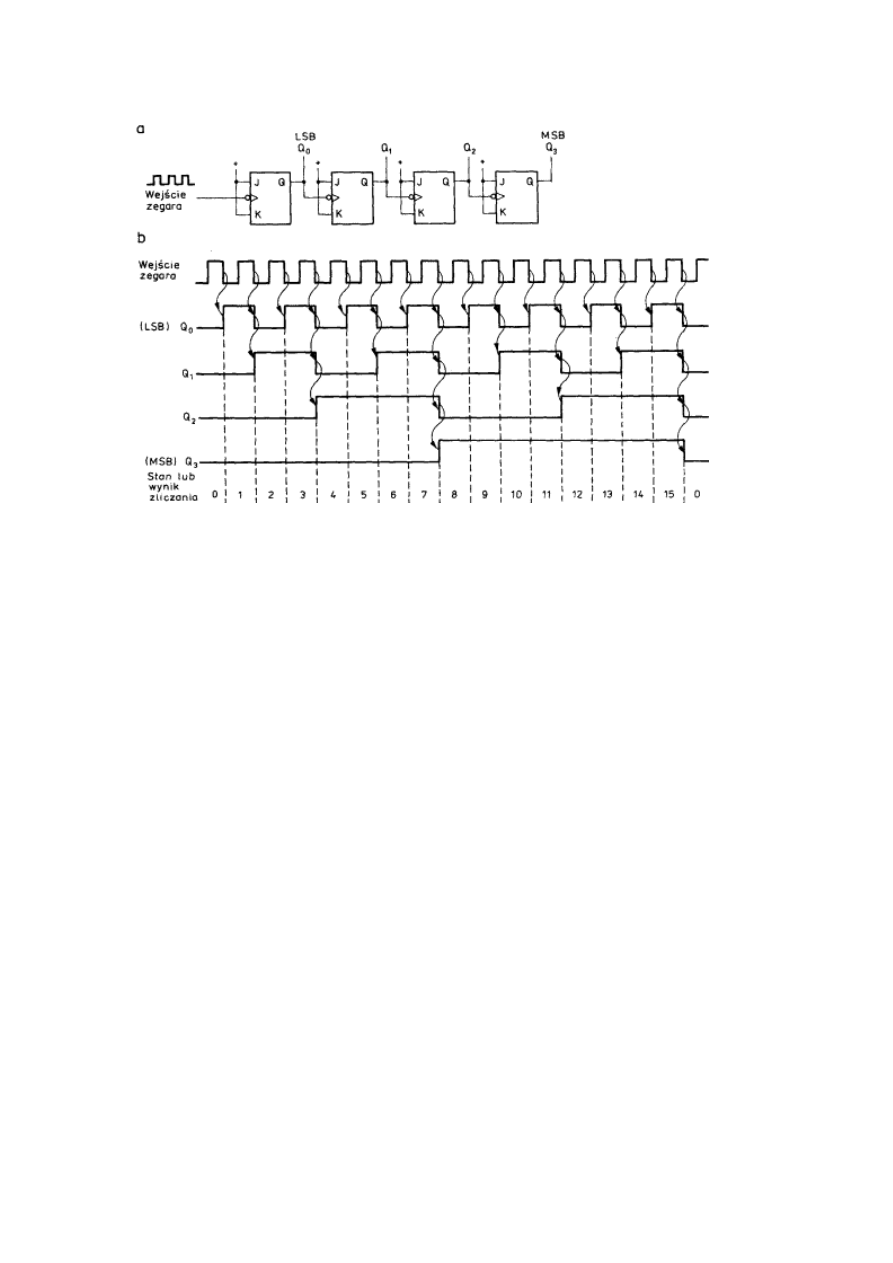

Rys. 6. - Licznik 4-bitowy: a) schemat, b) przebiegi czasowe

Jeżeli wejścia zegarowe są sterowane sygnałami z wyjść Q, trzeba użyć przerzutników

wyzwalanych zboczem opadającym (wskazują na to symbole negacji). Pokazany układ jest

licznikiem zliczającym do 16, albo inaczej - dzielnikiem częstotliwości sygnału zegarowego

przez 16. Sygnał wyjściowy ostatniego przerzutnika jest falą prostokątną o częstotliwości

równej 1/16 częstotliwości wejściowego sygnału taktującego. Układ taki nazywa się

licznikiem, ponieważ informacja obecna na czterech wyjściach Q, odczytywana jako 4-bitowa

liczba binarna, przyjmuje w kolejnych taktach zegara kolejne wartości binarne od 0 do 15,

ulegając za każdym razem zwiększeniu o jeden. Ilustrują ten fakt pokazane na rysunku 6

przebiegi czasowe. W ich opisie skrótami MSB i LSB oznaczono odpowiednio najbardziej i

najmniej znaczący bit licznika. Wygięte strzałki wskazują uzależnienia między sygnałami, co

ułatwia zrozumienie zasady działania układu. Licznik jest tak pożytecznym układem

funkcjonalnym, tak że doczekał się wykonania w postaci scalonej w wielu wersjach, w tym

jako licznik 4-bitowy, BCD i wielocyfrowy. Łącząc kaskadowo wiele takich liczników i

wyświetlając wynik zliczania na wyświetlaczu cyfrowym (np. wykorzystującym diody

ś

wiecące) można stosunkowo łatwo zbudować licznik zdarzeń.

Jeżeli ciąg impulsów będzie doprowadzany do wejścia takiego licznika dokładnie przez 1

sekundę, uzyskamy częstościomierz, który wyświetla częstotliwość (liczbę okresów na

sekundę), zliczając naprawdę liczbę okresów w ciągu jednej sekundy. W rzeczywistości

istnieją już scalone jednoukładowe częstościomierze, zawierające generator wzorcowy,

licznik, układy sterowania i wyświetlania.. W praktyce prosta metoda kaskadowego łączenia

liczników, polegająca na łączeniu wyjść Q każdego przerzutnika z wejściem zegarowym

następnego przerzutnika, prowadzi do pojawienia się kilku interesujących problemów

związanych z kumulującymi się opóźnieniami, które powstają w czasie "przenoszenia się"

sygnału przez łańcuch przerzutników. Liczniki "synchroniczne”, (w których wszystkie

wejścia zegarowe widzą ten sam sygnał taktujący) są zwykle lepsze. Wobec tego zajmijmy

się teraz systemami taktowanymi synchronicznie.

12

Układy badane.

Przerzutnik typu JK – MS z wejściem zerującym i ustawiającym.

Symbol przerzutnika i tablica przejść.

Ustaliliśmy, że przerzutnik reaguje na opadające zbocze impulsu zegarowego, na co

wskazuje symbol.

0 0 1 1 Q

0 1 1 1 0

1 0 1 1 1

1 1 1 1 Q

Q

+

J K R S

0 0 0 1 0

0 1 0 1 0

1 0 0 1 0

1 1 0 1 0

Q

+

J K R S

0 0 1 0 1

0 1 1 0 1

1 0 1 0 1

1 1 1 0 1

Q

+

J K R S

J

K

C

Q

Q

R

S

0 0 0 0

0 1 0 0

1 0 0 0

1 1 0 0

Q

+

J K R S

Q

=

Q

Wyszukiwarka

Podobne podstrony:

ip lpec bramki AND,OR,NAND,NOR,NOT

Adresy IP

w8 VLAN oraz IP w sieciach LAN

ADRESACJA W SIECIACJ IP

PA2 8 przerzutniki synchron

SNMP (IP)

PA2 5 przerzutniki asynchr

Adresy IP

ip 11 04

Microsoft PowerPoint IP tryb zgodnosci

M Newton Przerznaczenie dusz

CGEIB IP

ZAPROSZENIE, Documents, IP Zielona gora, mat inf

Podsumowanie pracy Zespołu Informacji Publicznej i Współpracy z innymi za rok 2015, Documents, ip, s

Nauka przerzutu bokiem, Gimnastyka1

więcej podobnych podstron