Lista rozkazów

1

L

ISTA ROZKAZÓW MIKROKONTROLER

ÓW '51

Lista

rozkazów

mikrokontroler

ów '51 zawiera 111 rozkazów,

w ród których jest 49 jednobajtowych, 45 dwubajtowych i 17 trzybajtowych. Wyko-

nywane s one w ci gu jednego lub dwóch cykli maszynowych. Wyj tkiem s rozkazy

mno enia i dzielenia, które wykonywane s w ci gu czterech cykli maszynowych.

W opisie rozkazów przyj to nast puj ce oznaczenia:

A

− akumulator,

B

− rejestr B,

Rr

− rejestr roboczy (R0...R7),

Ri

− rejestr roboczy - wska nik danych: i=0,1. (R0 i R1),

DPTR

− wska nik danych,

PC − licznik rozkazów,

SP

− wska nik stosu,

C (CY) − wska nik przeniesienia,

AC − znacznik (flaga) przeniesienia pomocniczego,

OV − znacznik (flaga) przepe

łnienia,

ad

− 8−bitowy adres bezpo redni,

n

− 8−bitowy argument bezpo redni,

nn

− 16−bitowy argument bezpo redni,

bit

− 8−bitowy adres bitu w pami ci RAM lub SFR,

adr11 − adres 11−bitowy,

adr16 − adres 16−bitowy,

d

− 8−bitowe przesuni cie o warto ci z przedzia

łu <−128, 127>

(w praktyce d oznacza etykiet lub adres),

@

− w mnemoniku rozkazu poprzedza adres po redni,

#

− w mnemoniku rozkazu poprzedza argument bezpo redni,

x

− w zapisie operacji oznacza zawarto

ć rejestru x,

(x)

− w zapisie operacji oznacza zawarto

ć pami ci o adresie x,

<r> − miejsce pobrania argumentu i zapisania wyniku operacji,

<s> − miejsce pobrania drugiego argumentu operacji,

<br> − rejestr bazowy,

<dp> − wska nik danych,

Lista rozkazów

2

L

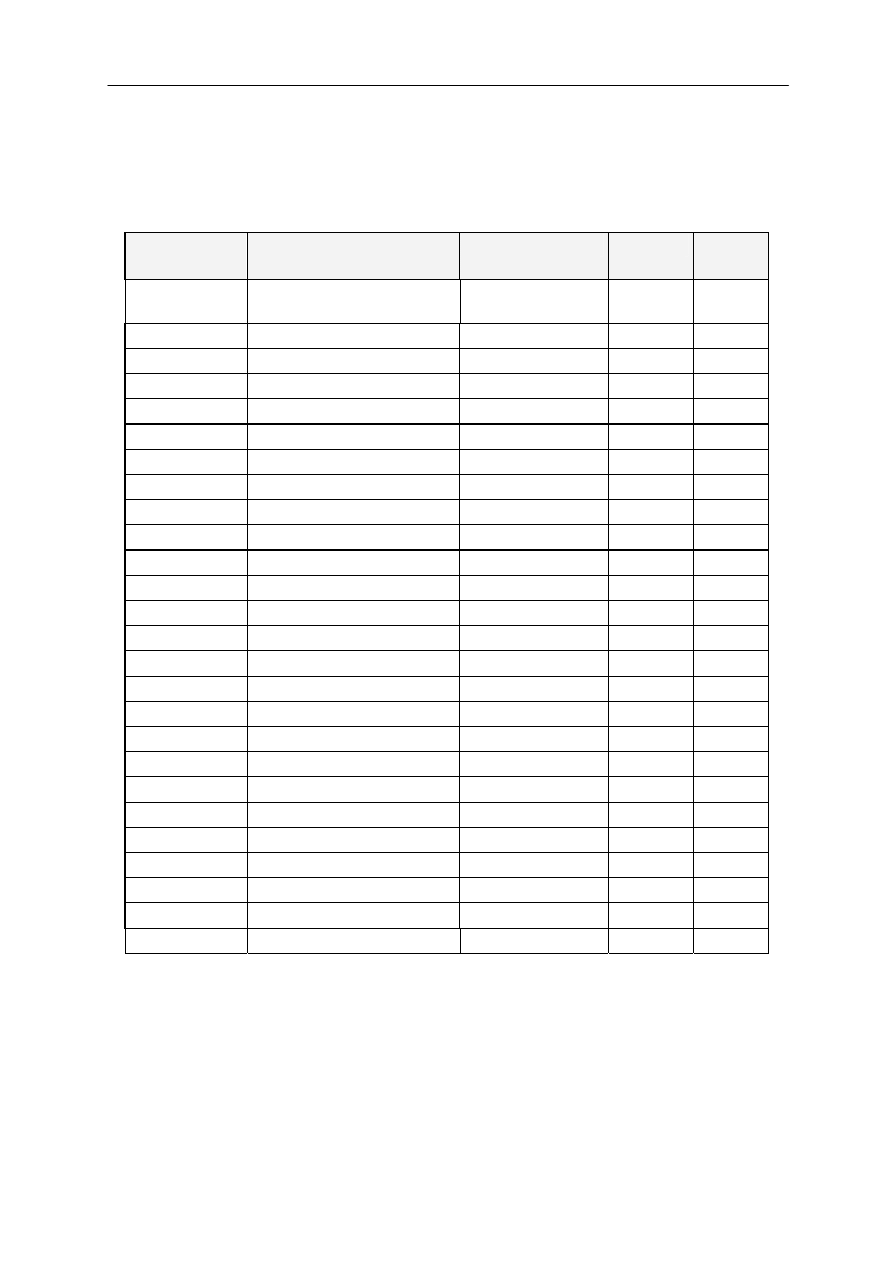

ISTA ROZKAZÓW POGRUPOWANYCH FUNKCJONALNIE

Rozkazy przesy

łania danych

Kod rozkazu

(hex)

Mnemonik

Operacja

Bajty

Cykle

E8-EF MOV

A,Rr

A ← Rr

1 1

E5 MOV

A,ad

A ← (ad)

2 1

E6-E7 MOV

A,@Ri

A ← (Ri)

1 1

74 MOV

A,#n

A ← n

2 1

F8-FF MOV

Rr,A

Rr ← A

1 1

A8-AF MOV

Rr,ad

Rr ← (ad)

2 2

78-7F MOV

Rr,#n

Rr ← n

2 1

F5 MOV

ad,A

(ad) ← A

2 1

88-8F MOV

ad,Rr

(ad) ← Rr

2 2

85 MOV

ad1,ad2

(ad1) ← (ad2)

3 2

86-87 MOV

ad,@Ri

(ad) ← (Ri)

2 2

75 MOV

ad,#n

(ad) ← n

3 2

F6-F7 MOV

@Ri,A

(Ri) ← A

1 1

A6-A7 MOV

@Ri,ad

(Ri) ← (ad)

2 2

76-77 MOV

@Ri,#n

(Ri) ← n

2 1

90 MOV

DPTR,#nn

DPTR ← nn

3 2

93

MOVC A,@A + DPTR

A ← (A+DPTR)

1 2

83

MOVC A,@A + PC

A ← (A+PC)

1 2

E2-E3 MOVX

A,@Ri

A ← (Ri)

1 2

F2-F3 MOVX

@Ri,A

(Ri) ← A

1 2

E0 MOVX

A,@DPTR A ← (DPTR)

1 2

F0 MOVX

@DPTR,A (DPTR) ← A

1 2

C8-CF XCH

A,Rr

A ↔ Rr

1 1

C5 XCH

A,ad

A ↔ (ad)

2 1

C6-C7 XCH

A,@Ri

A ↔ (Ri)

1 1

D6-D7 XCHD

A,@Ri

A

3..0

↔ (Ri)

3..0

1 1

Lista rozkazów

3

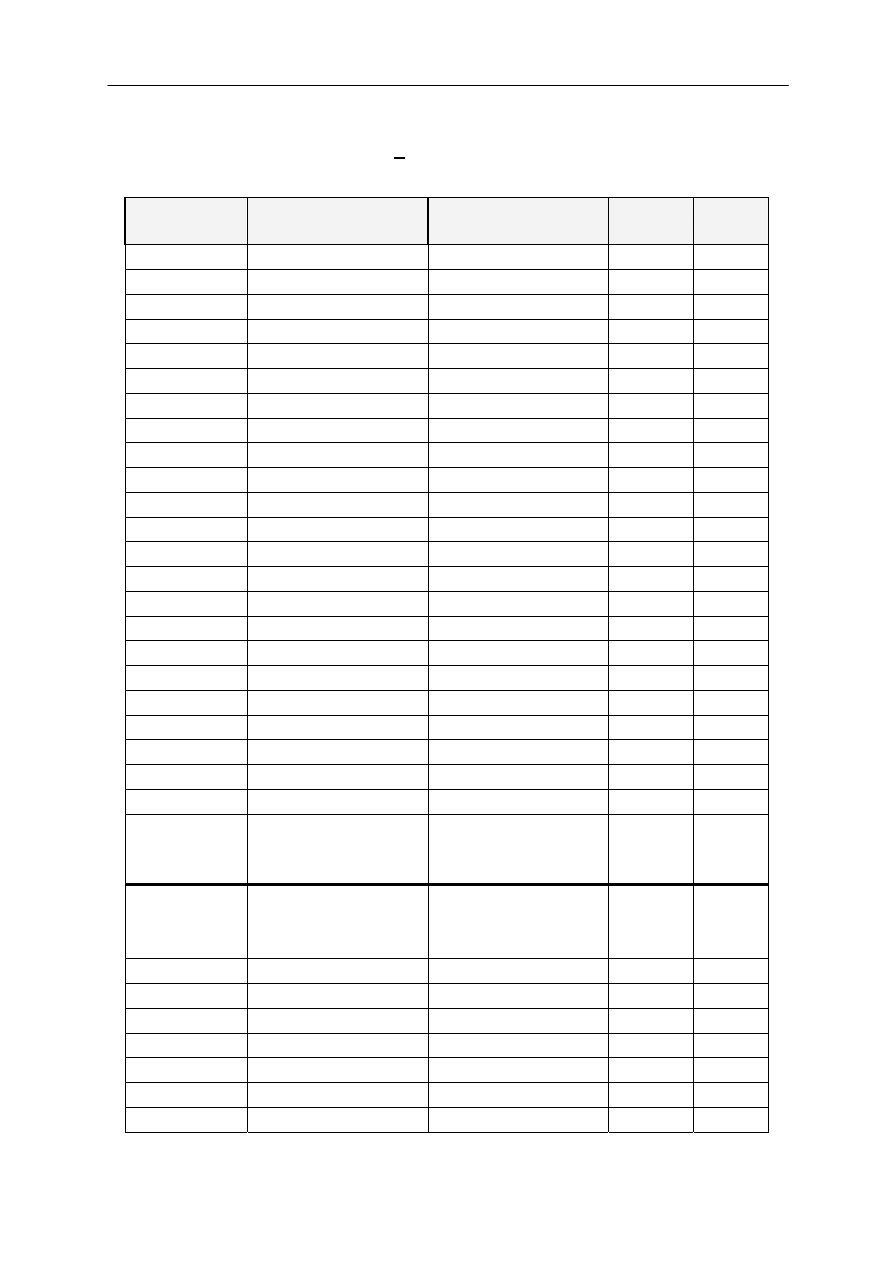

Rozkazy operacji arytmetyczno logicznych

Kod rozkazu

(hex)

Mnemonik

Operacja

Bajty

Cykle

28-2F ADD

A,Rr

A ← A + Rr

1 1

25 ADD

A,ad

A ← A + (ad)

2 1

26-27 ADD

A,@Ri

A ← A + (Ri)

1 1

24 ADD

A,#n

A ← A + n

2 1

38-3F ADDC

A,Rr

A ← A + Rr + C

1 1

35 ADDC

A,ad

A ← A + (ad) + C

2 1

36-37 ADDC

A,@Ri

A ← A + (Ri) + C

1 1

34 ADDC

A,#n

A ← A + n + C

2 1

98-9F SUBB

A,Rr

A ← A – Rr – C

1 1

95 SUBB

A,ad

A ← A – (ad) – C

2 1

96-97 SUBB

A,@Ri

A ← A – (Ri) – C

1 1

94 SUBB

A,#n

A ← A – n – C

2 1

04 INC

A

A ← A + 1

1 1

08-0F INC

Rr

Rr ← Rr + 1

1 1

05 INC

ad

(ad) ← (ad) + 1

2 1

06-07 INC

@Ri

(Ri) ← (Ri) + 1

1 1

A3 INC

DPTR

DPTR ← DPTR + 1

1 2

14 DEC

A

A ← A – 1

1 1

18-1F DEC

Rr

Rr ← Rr – 1

1 1

15 DEC

ad

(ad) ← (ad) – 1

2 1

16-17 DEC

@Ri

(Ri) ← (Ri) – 1

1 1

A4 MUL

AB

B.A ← A x B

1 4

84 DIV

AB

A ← A div B

1 4

D4 DA

A

Korekcja

dziesi tna

A (nie dotyczy odej-

mowania)

1 1

58-5F ANL

A,Rr

A ← A ∧ Rr

1 1

55 ANL

A,ad

A ← A ∧ (ad)

2 1

56-57 ANL

A,@Ri

A ← A ∧ (Ri)

1 1

54 ANL

A,#n

A ← A ∧ n

2 1

52 ANL

ad,A

(ad) ← (ad) ∧ A

2 1

53 ANL

ad,#n

(ad) ← (ad) ∧ n

3 2

48-4F ORL

A,Rr

A ← A ∨ Rr

1 1

45 ORL

A,ad

A ←A ∨ (ad)

2 1

46-47 ORL

A,@Ri

A ← A ∨ (Ri)

1 1

44 ORL

A,#n

A ← A ∨ n

2 1

Lista rozkazów

4

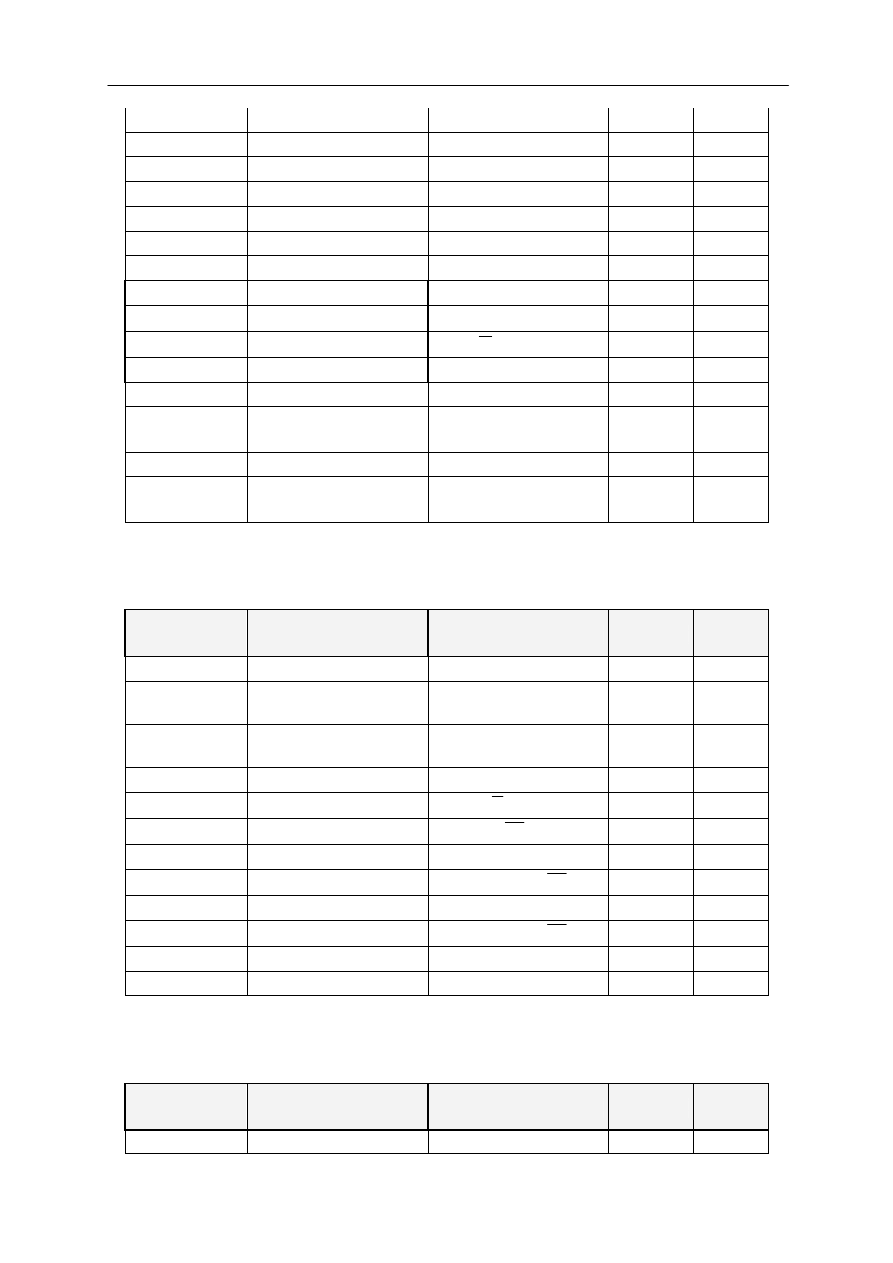

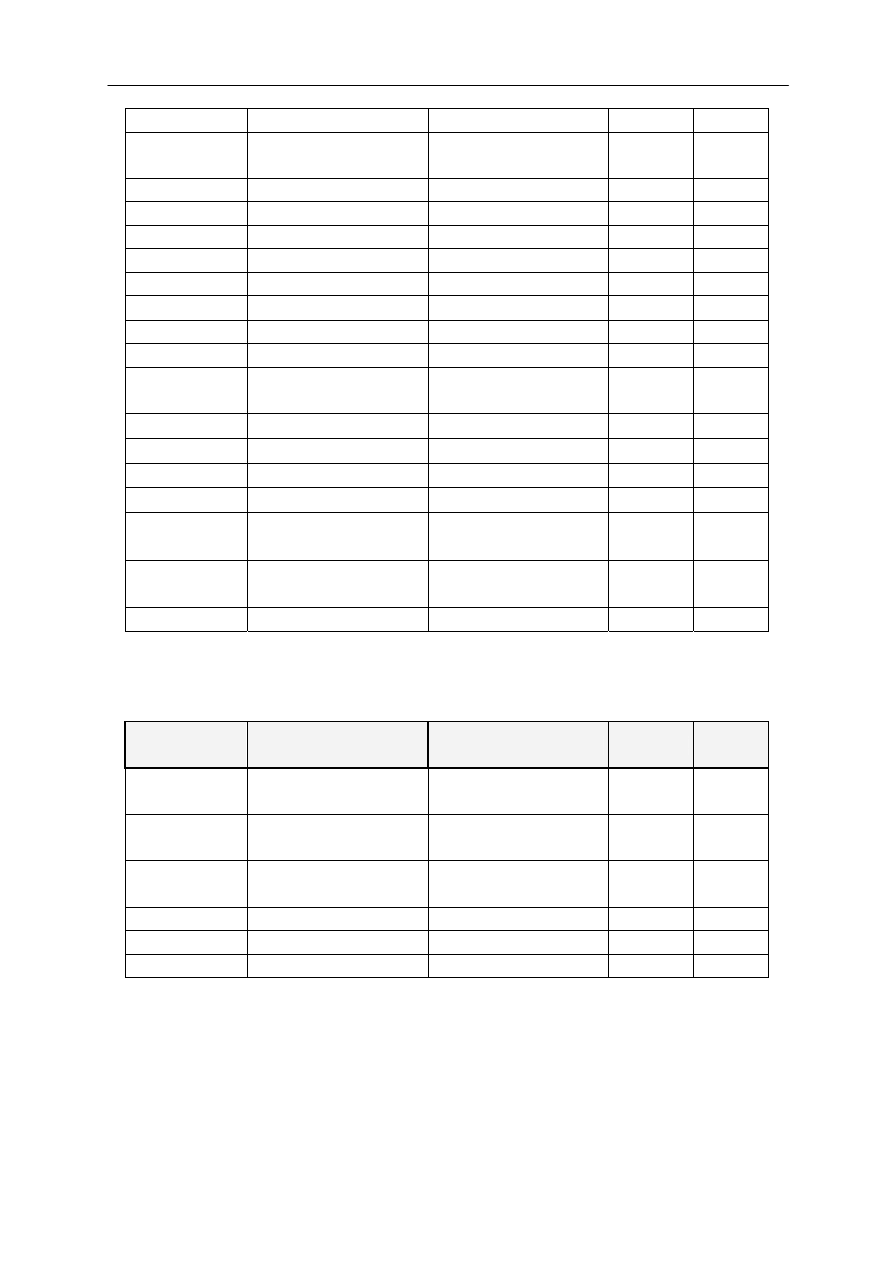

42 ORL

ad,A

(ad) ← (ad) ∧ A

2 1

43 ORL

ad,#n

(ad) ← (ad) ∨ n

3 2

68-6F XRL

A,Rr

A ← A ⊕ Rr

1 1

65 XRL

A,ad

A ← A ⊕ (ad)

2 1

66-67 XRL

A,@Ri

A ← A ⊕ (Ri)

1 1

64 XRL

A,#n

A ← A ⊕ n

2 1

62 XRL

ad,A

(ad) ← (ad) ⊕ A

2 1

63 XRL

ad,#n

(ad) ← (ad) ⊕ n

3 2

E4 CLR

A

A ← 0

1 1

F4 CPL

A

A ←

A

1 1

C4 SWAP

A

A

3...0

↔ A

7...4

1 1

23 RL

A

Przesu w lewo

1

1

33 RLC

A

Przesu w lewo z

przeniesieniem

1 1

03 RR

A

Przesu w prawo

1

1

13 RRC

A

Przesu w prawo z

przeniesieniem

1 1

Rozkazy operacji na bitach

Kod rozkazu

(hex)

Mnemonik

Operacja

Bajty

Cykle

C3 CLR

C

CY ← 0

1 1

C2 CLR

bit

(bit) ← 0

2 1

D3 SETB

C

CY ← 1

1 1

D2 SETB

bit

(bit) ← 1

2 1

B3 CPL

C

CY ←

C

1 1

B2 CPL

bit

(bit) ← (

bit

)

2 1

82 ANL

C,bit

CY ← CY ∧ (bit)

2 2

B0 ANL

C,/bit

CY ← CY ∧ (

bit

)

2 2

72 ORL

C,bit

CY ← CY ∨ (bit)

2 2

A0 ORL

C,/bit

CY ← CY ∨ (

bit

)

2 2

A2 MOV

C,bit

CY ← (bit)

2 1

92 MOV

bit,C

(bit) ← CY

2 2

Rozkazy skoków i rozkazy steruj ce

Kod rozkazu

(hex)

Mnemonik

Operacja

Bajty

Cykle

01,21,41,61,8 AJMP adr11

Skocz bezwarunko-

2

2

Lista rozkazów

5

1,A1,C1,E1

wo na stronie

02 LJMP

adr16

Skocz

bezwarunko-

wo

3 2

80

SJMP d

Skocz wzgl dem PC

2

2

73

JMP @A + DPTR

Skocz po rednio 1

2

40

JC d

Skocz, je li CY=1

2

2

50

JNC d

Skocz, je li CY=0

2

2

60

JZ d

Skocz, je li A=0

2

2

70 JNZ

d

Skocz, je li A≠0

2 2

20

JB bit,d

Skocz, je li bit=1

3

2

30

JNB bit,d

Skocz, je li bit=0

3

2

10 JBC

bit,d

Je li bit=1, to zeruj

go i skocz

3 2

B5 CJNE

A,ad,d

Skocz, je li A≠(ad)

3 2

B4 CJNE

A,#n,d

Skocz, je li A≠n

3 2

B8-BF CJNE

Rr,#n,d

Skocz, je li Rr≠n

3 2

B6-B7 CJNE

@Ri,#n,d Skocz, je li (Ri)≠n

3 2

D8-DF

DJNZ Rr,d

Zmniejsz o 1 i skocz,

je li Rr≠0

2 2

D5

DJNZ ad,d

Zmniejsz o 1 i skocz,

je li (ad)≠0

3 2

00

NOP

Nie rób nic

1

1

Rozkazy obs

ługi podprogramów, przerwa i operacji na stosie

Kod rozkazu

(hex)

Mnemonik

Operacja

Bajty

Cykle

11,31,51,71,9

1,B1,D1,F1

ACALL adr11

Skocz do podprogra-

mu na stronie

2 2

12 LCALL

adr16 Skocz

do

podprogra-

mu

3 2

22 RET

Powró

ć z podprogra-

mu

1 2

32 RETI

Powró

ć z przerwania

1

2

C0

PUSH ad

Zdejmij ze stosu

2

2

D0 POP

ad

Wy lij na stos

2

2

Lista rozkazów

6

D

OK

ŁADNY OPIS ROZKAZÓW

Rozkazy przesy

łania danych

MOV bit,C

Prze lij flag CY do bitu

Zawarto

ć znacznika przeniesienia przesyłana jest do

bitu o podanym adresie bezpo rednim.

(bit) ← CY

MOV C,bit

Prze lij warto

ć bitu do flagi

przeniesienia

Zawarto

ć bitu o podanym adresie bezpo rednim prze-

sy

łana jest do znacznika przeniesienia.

Cy ← (bit)

MOV DPTR,#nn

Wpisz 16-bitow warto

ć do

wska nika danych

Do 16−bitowego rejestru DPTR wpisywany jest argu-

ment bezpo redni, podany jako drugi i trzeci bajt roz-

kazu. Pierwszy bajt argumentu wpisywany jest do reje-

stru DPH, a drugi do rejestru DPL.

DPTR ← nn

MOV <r>,<s>

Prze lij dane

O miobitowy argument <s> jest przesy

łany do miejsca

wskazanego przez argument <r>. Mo liwe jest pi tna-

cie kombinacji adresowania argumentów:

MOV

A,Rr

A

←

Rr

MOV A,@Ri

A ← (Ri)

MOV

A,ad

A

←

(ad)

MOV

A,#n

A

←

n

MOV

Rr,A

Rr

←

A

MOV

Rr,ad

Rr

←

(ad)

MOV

Rr,#n

Rr

←

n

MOV @Ri,A

(Ri) ← A

MOV @Ri,ad

(Ri) ← (ad)

MOV @Ri,#n

(Ri) ← n

MOV

ad,A

(ad)

←

A

MOV

ad,Rr

(ad)

←

Rr

MOV ad,@Ri

(ad) ← (Ri)

MOV ad1,ad2

(ad1) ← (ad2)

MOV

ad,#n

(ad)

←

n

MOVC A, @A +<br>

Prze lij bajt z pami ci pro-

gramu do akumulatora

Do akumulatora przesy

łana jest zawarto ć komórki

pami ci programu o adresie b d cym sum zawarto ci

akumulatora i 16-bitowego rejestru bazowego <br>.

Lista rozkazów

7

Jako rejestry bazowe mog by

ć u yte wska nik danych

DPTR i licznik rozkazów PC. Je eli rejestrem bazo-

wym jest PC, to adresem bazowym jest adres pierw-

szego bajtu rozkazu nast pnego po MOVC.

MOVC A,@A + DPTR

A ← (A + DPTR)

MOVC A,@A + PC

A ← (A + PC)

MOVX A,@<dp>

Prze lij bajt z zewn trznej

pami ci danych do akumula-

tora

Do akumulatora wpisywane s dane z komórki ze-

wn trznej pami ci danych o adresie po rednim zawar-

tym we wska niku danych <dp>. Wska nikiem danych

mo e by

ć rejestr roboczy R0 lub R1 albo rejestr DPTR.

Je eli wska nikiem danych jest rejestr R0 lub R1, to

adres 8-bitowy wys

łany jest tylko przez port P0, nato-

miast je eli wska nikiem danych jest DPTR, to 16-

bitowy adres wysy

łany jest przez porty P0 i P2 .

MOVX A,@DPTR

A ← (DPTR)

MOVX A,@Ri

A ← (Ri)

MOVX @<dp>,A

Prze lij bajt z akumulatora

do zewn trznej pami ci da-

nych

Do komórki zewn trznej pami ci danych o adresie po-

rednim zawartym we wska niku danych <dp> wpisy-

wane s dane z akumulatora. Wska nikiem danych

mo e by

ć rejestr roboczy R0 lub R1 albo rejestr DPTR.

Je eli wska nikiem danych jest rejestr R0 lub R1, to

adres 8−bitowy wys

łany jest tylko przez port P0, na-

tomiast je eli wska nikiem danych jest DPTR, to

16−bitowy adres wysy

łany jest przez porty P0 i P2.

MOVX @DPTR,A

(DPTR) ← A

MOVX @Ri,A

(Ri) ← A

XCH A,<s>

Wymie akumulator z

za-

warto ci komórki pami ci

Zawarto

ć akumulatora wymieniana jest z zawarto ci

wskazanego argumentu. Mo liwe s trzy tryby adre-

sowania argumentu:

XCH A,Rr

A ↔ Rr

XCH A,@Ri

A ↔ (Ri)

XCH A,ad

A ↔ (ad)

Lista rozkazów

8

XCHD A,@Ri

Wymie pó

łbajty z akumu-

latora i pami ci

Zawarto

ć mniej znacz cych bitów akumulatora (bity

3...0) zostaje wymieniona z zawarto ci mniej znacz -

cych bitów komórki wewn trznej pami ci danych o

adresie zawartym w rejestrze Ri (R1 lub R0). Bardziej

znacz ce bity akumulatora (bity 7...4) i komórki pa-

mi ci pozostaj bez zmian.

A

3...0

↔ (Ri)

3...0

Rozkazy operacji arytmetyczno logicznych

ADD A,<s>

Dodaj do akumulatora

Wskazany argument dodawany jest do akumulatora, do

którego wpisywany jest wynik. Znaczniki CY, AC

i OV ustawiane s zgodnie z wynikiem operacji. Mo -

liwe s cztery tryby adresowania argumentu <s>:

ADD A,Rr

A ← A + Rr

ADD A,@Ri

A ← A + (Ri)

ADD A,ad

A ← A + (ad)

ADD A,#n

A ← A + n

ADDC A,<s>

Dodaj do akumulatora z

przeniesieniem

Do akumulatora dodawany jest wskazany argument

i zawarto

ć znacznika przeniesienia, przy czym wynik

wpisywany jest do akumulatora. Znaczniki CY, AC

i OV ustawiane s zgodnie z wynikiem operacji. Mo -

liwe s cztery tryby adresowania argumentu <s>:

ADDC A,Rr

A ← A + Rr + CY

ADDC A,@Ri

A← A + (Ri) + CY

ADDC A,ad

A← A + (ad) + CY

ADDC A,#n

A← A + n + CY

SUBB A,<s>

Odejmij od akumulatora z

po yczk

Zawarto

ć wskazanego argumentu oraz zawarto ć

znacznika przeniesienia CY odejmowana jest od aku-

mulatora, przy czym wynik operacji wpisywany jest do

akumulatora i ustawiane s znaczniki CY, AC i OV.

Mo liwe s cztery tryby adresowania argumentu:

SUBB A,Rr

A ← A − Rr − CY

SUBB A,@Ri

A ← A − (Ri) − CY

Lista rozkazów

9

SUBB A,ad

A ← A − (ad) − CY

SUBB A,#n

A ← A − n − CY

INC <r>

Zwi ksz o 1

Do wskazanego argumentu dodawana jest jedynka,

przy czym stan znaczników nie ulega zmianie. Je eli

rozkaz u yty jest do zmiany stanu wyj cia, to jest od-

czytywana i modyfikowana zawarto

ć rejestru wyj-

ciowego portu, a nie stan logiczny ko cówek uk

ładu.

Mo liwe s cztery tryby adresowania argumentu:

INC A

A ← A + 1

INC Rr

Rr ← Rr + 1

INC @Ri

(Ri) ← (Ri) + 1

INC ad

(ad)← (ad) + 1

INC DPTR

Zwi ksz o 1 wska nik da-

nych

Do 16-bitowego rejestru DPTR dodawana jest 1, przy

czym stan znaczników nie ulega zmianie.

DPTR ← DPTR + 1

DEC <r>

Zmniejsz o 1

Od wskazanego argumentu odejmowana jest jedynka,

przy czym stan znaczników nie ulega zmianie. Je eli

rozkaz u yty jest do zmiany stanu wyj cia, to jest od-

czytywana i modyfikowana zawarto

ć rejestru wyj-

ciowego portu, a nie stan logiczny ko cówek uk

ładu.

Mo liwe s cztery tryby adresowania argumentu:

DEC A

A ← A − 1

DEC Rr

Rr ← Rr − 1

DEC @Ri

(Ri) ← (Ri) − 1

DEC ad

(ad) ← (ad) − 1

MUL AB

Pomnó

O miobitowa liczba dwójkowa bez znaku z akumulato-

ra mno ona jest przez 8−bitow liczb bez znaku

z

rejestru B. Osiem bardziej znacz cych bitów

16−bitowego wyniku wpisywanych jest do rejestru B,

natomiast 8 mniej znacz cych do akumulatora. Je li

wynik mno enia jest wi kszy od 255, to jest ustawiany

znacznik OV, w przeciwnym razie znacznik ten jest

zerowany. Znacznik CY jest zerowany.

Lista rozkazów

10

B.A ← [A x B]

DIV AB

Podziel

Operacja dokonuje dzielenia o miobitowej liczby bez

znaku zawartej w akumulatorze przez o miobitow

liczb bez znaku zawart w rejestrze B. Cz

ć całkowi-

ta wyniku dzielenia wpisywana jest do akumulatora,

reszta za do rejestru B. Znaczniki CY i OV s zero-

wane. Je li w rejestrze B jest 0, to po wykonaniu roz-

kazu zawarto

ć akumulatora i rejestru B jest nieokre-

lona, a znacznik OV = 1.

A ← [A/B]

B ← reszta (A/B)

DA A

Korekcja dziesi tna

Wykonywana jest korekcja dziesi tna wyniku dodawa-

nia (nie jest dokonywana korekcja wyniku odejmowa-

nia!). Je eli argumenty podane s w formacie BCD, to

wynik przedstawiany jest w postaci dwóch cyfr dzie-

si tnych w tym kodzie. Je li liczba dziesi tna jest

wi ksza od 99, ustawiany jest znacznik przeniesienia

CY. Nie zmienia si stan znaczników AC i OV.

ANL <r>,<s>

Wymnó logicznie

Wykonywane jest mno enie logiczne wskazanych ar-

gumentów, przy czym wynik operacji wpisywany jest

do miejsca, z którego zosta

ł pobrany argument <r>.

Nale y pami ta

ć, e je eli rozkaz jest u yty do zmiany

stanu wyj cia, to jest odczytywana i zapisywana zawar-

to

ć rejestru wyj ciowego portu, a nie stan logiczny

z ko cówek uk

ładu. Mo liwych jest sze ć ró nych try-

bów adresowania argumentów:

ANL A,Rr

A ← A ∧ Rr

ANL A,@Ri

A ← A ∧ (Ri)

ANL A,ad

A ← A ∧ (ad)

ANL A,#n

A ← A ∧ n

ANL ad,A

ad ← (ad) ∧ A

ANL ad,#n

ad ← (ad) ∧ n

ANL C,bit

Znacznik przeniesienia C jest zerowany, je eli warto

ć

Lista rozkazów

11

Wymnó logicznie przez

bit

logiczna bitu o podanym adresie jest równa 0, w prze-

ciwnym wypadku nie zmienia si .

CY ← CY ∧ (bit)

ANL C,/bit

Wymnó logicznie przez

negacj zawarto ci bitu

Znacznik przeniesienia C jest zerowany, je eli warto

ć

logiczna bitu o podanym adresie jest równa 1, w prze-

ciwnym wypadku nie zmienia si .

CY ← CY∧ ( bit )

ORL <r>,<s>

Sumuj logicznie

Wykonywana jest suma logiczna wskazanych argu-

mentów, przy czym wynik wpisywany jest do miejsca,

z którego pobrany zosta

ł argument <r>. Je eli operacja

zosta

ła u yta do zmiany stanu wyj cia, to zmianie ule-

ga zawarto

ć rejestru wyj ciowego portu a nie stan lo-

giczny ko cówek uk

ładu. Mo liwych jest sze ć kom-

binacji adresowania argumentów:

ORL A,Rr

A ← A ∨ Rr

ORL A,@Ri

A ← A ∨ Ri

ORL A,ad

A ← A ∨ (ad)

ORL A,#n

A ← A ∨ n

ORL ad,A

(ad) ← (ad) ∨ A

ORL ad,#n

(ad) ← (ad) ∨ n

ORL CY,bit

Sumuj logicznie CY z bi-

tem

Wykonana zostaje operacja sumowania logicznego fla-

gi przeniesienia CY z zawarto ci bitu o podanym ad-

resie bezpo rednim: je li warto

ć logiczna bitu równa

jest 1, to flaga CY przyjmuje warto

ć 1. W przeciw-

nym razie zawarto

ć CY nie zmienia si .

CY ← CY ∨ (bit)

ORL C,/bit

Sumuj logicznie CY z ne-

gacj bitu

Wykonana zostaje operacja sumowania logicznego fla-

gi przeniesienia CY z negacj zawarto ci bitu

o podanym adresie bezpo rednim: je li warto

ć logicz-

na bitu równa jest 0, to flaga CY przyjmuje warto

ć 1.

W przeciwnym razie zawarto

ć CY nie zmienia si .

CY ← CY ∨ (

bit )

XRL

<r>,<s>

Wykonywana jest suma mod 2 wskazanych argumen-

Lista rozkazów

12

Sumuj mod 2

tów, przy czym wynik wpisywany jest do miejsca,

z którego pobrany zosta

ł argument <r>. Mo liwych

jest sze

ć kombinacji trybów adresowania argumen-

tów:

XRL A,Rr

A ← A ⊕ Rr

XRL A,@Ri

A ← A ⊕ (Ri)

XRL A,ad

A ← A ⊕ (ad)

XRL A,#n

A ← A ⊕ n

XRL ad,A

(ad) ← (ad) ⊕ A

XRL ad,#n

(ad) ← (ad) ⊕ n

CLR

A

Wyzeruj akumulator

Zawarto

ć akumulatora zostaje wyzerowana.

A ← 0

CPL

A

Negacja akumulatora

Zawarto

ć akumulatora jest negowana bit po bicie.

A ← A

SWAP

A

Wymie pó

łbajty w akumu-

latorze

Zawarto

ć bardziej znacz cych bajtów (MSB) wymie-

niona zostaje z zawarto ci mniej znacz cych bajtów,

co jest równowa ne z czterokrotnym cyklicznym prze-

suni ciem akumulatora.

A

7...4

↔ A

3...0

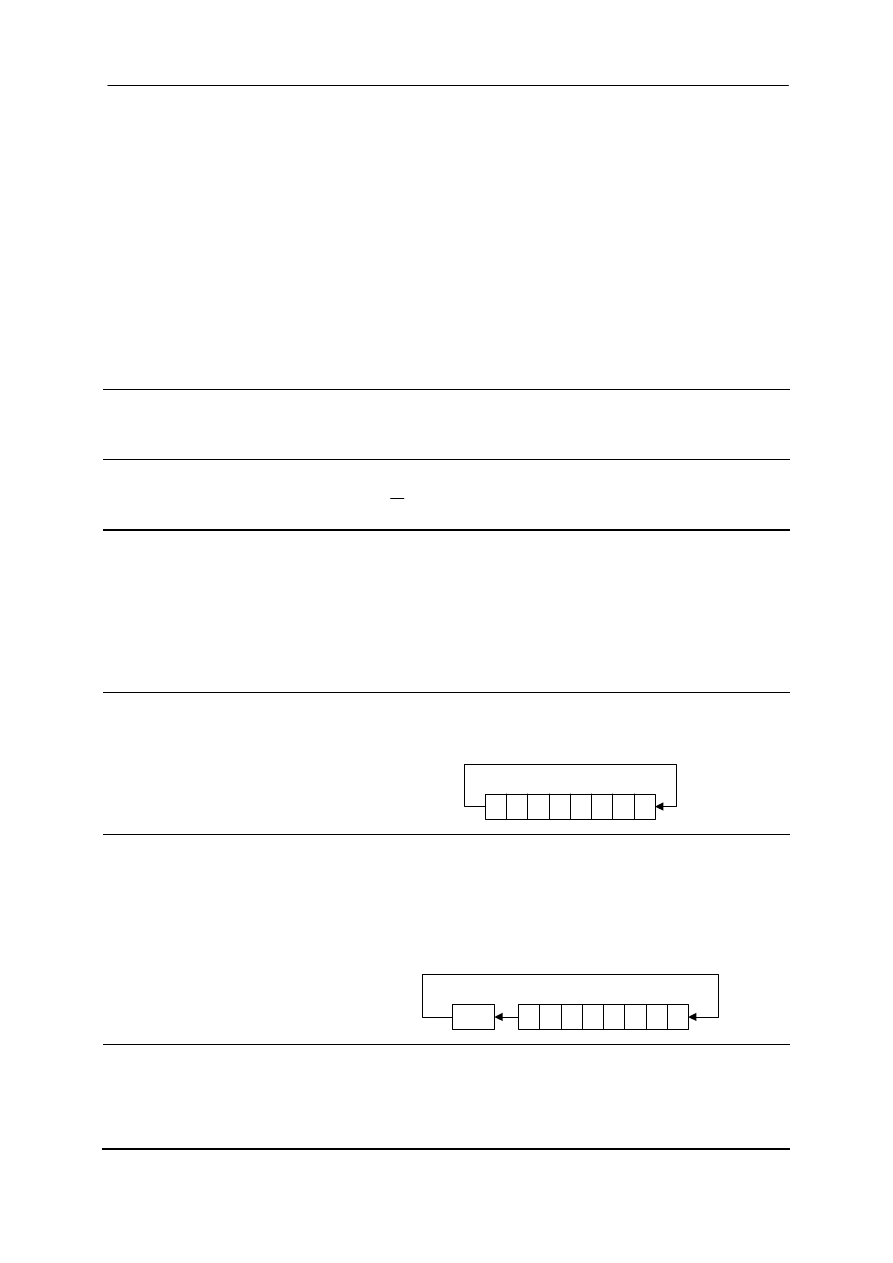

RL

A

Przesu akumulator cy-

klicznie w lewo

Zawarto

ć akumulatora przesuwana jest cyklicznie

w lewo.

7 6 5 4 3 2 1 0

A

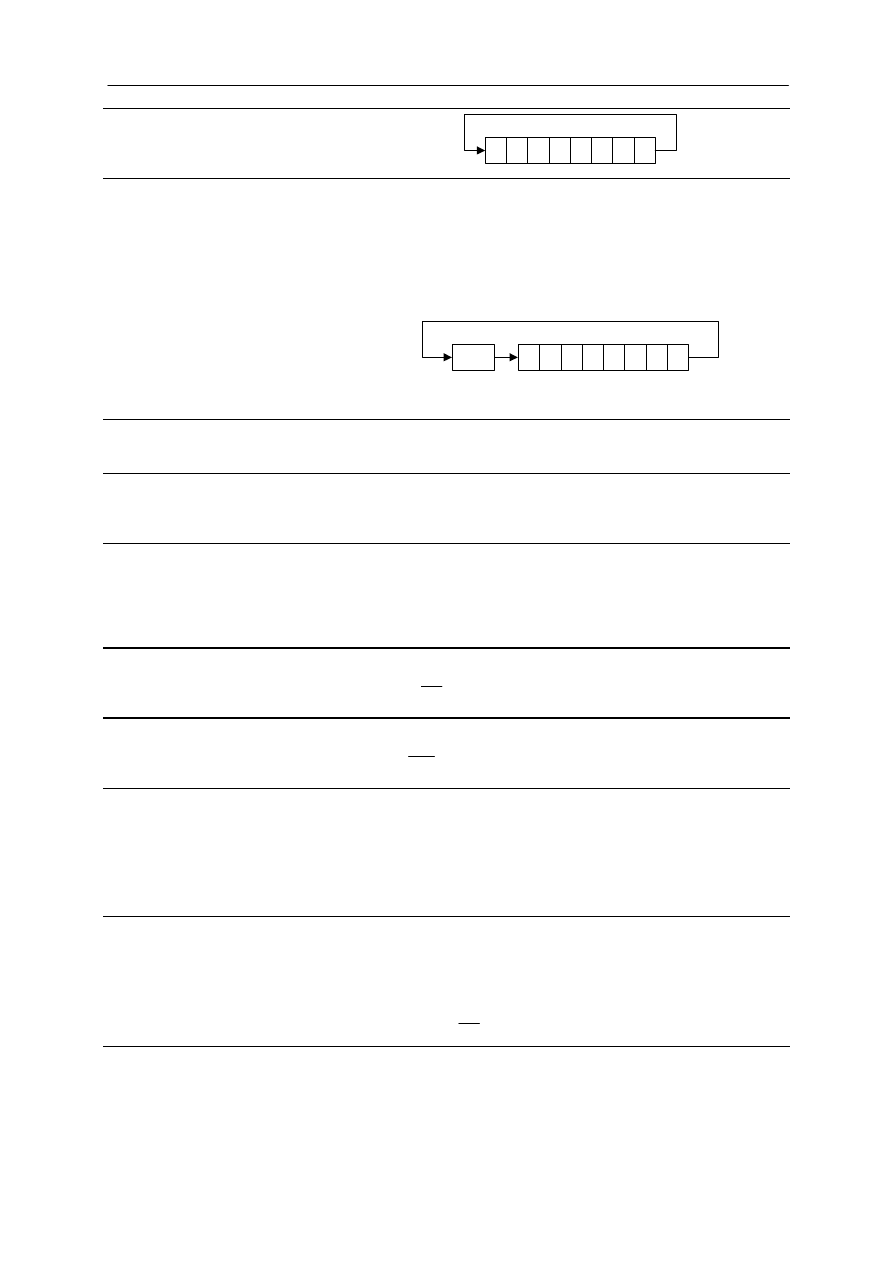

RLC

A

Przesu akumulator cy-

klicznie w lewo z CY

Zawarto

ć akumulatora przesuwana jest cyklicznie

w lewo z uwzgl dnieniem flagi CY. Wykonanie tego

rozkazu przy zerowej warto ci flagi CY odpowiada

pomno eniu przez 2 liczby zawartej w akumulatorze.

7 6 5 4 3 2 1 0

A

CY

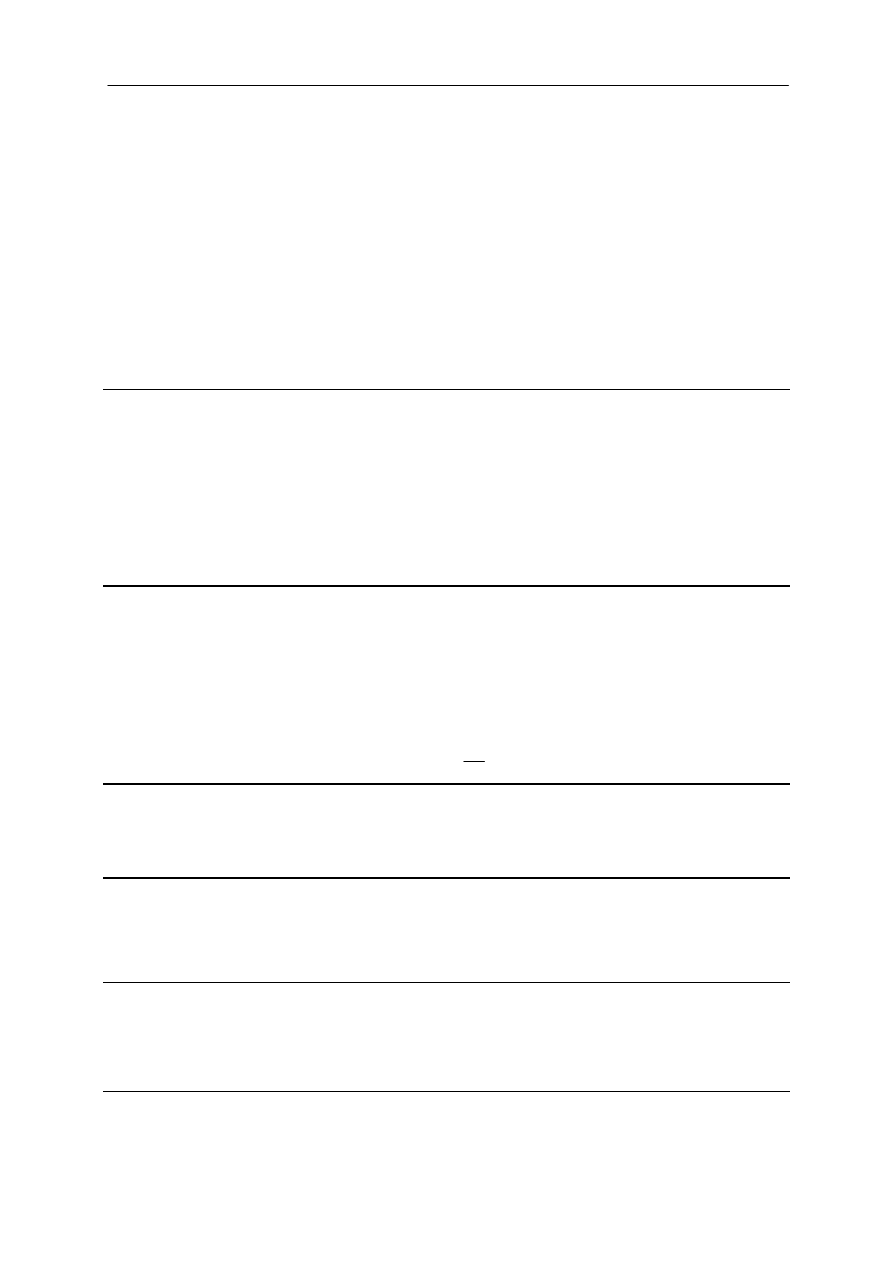

RR

A

Przesu akumulator cy-

klicznie w prawo

Zawarto

ć akumulatora przesuwana jest cyklicznie

w prawo.

Lista rozkazów

13

7 6 5 4 3 2 1 0

A

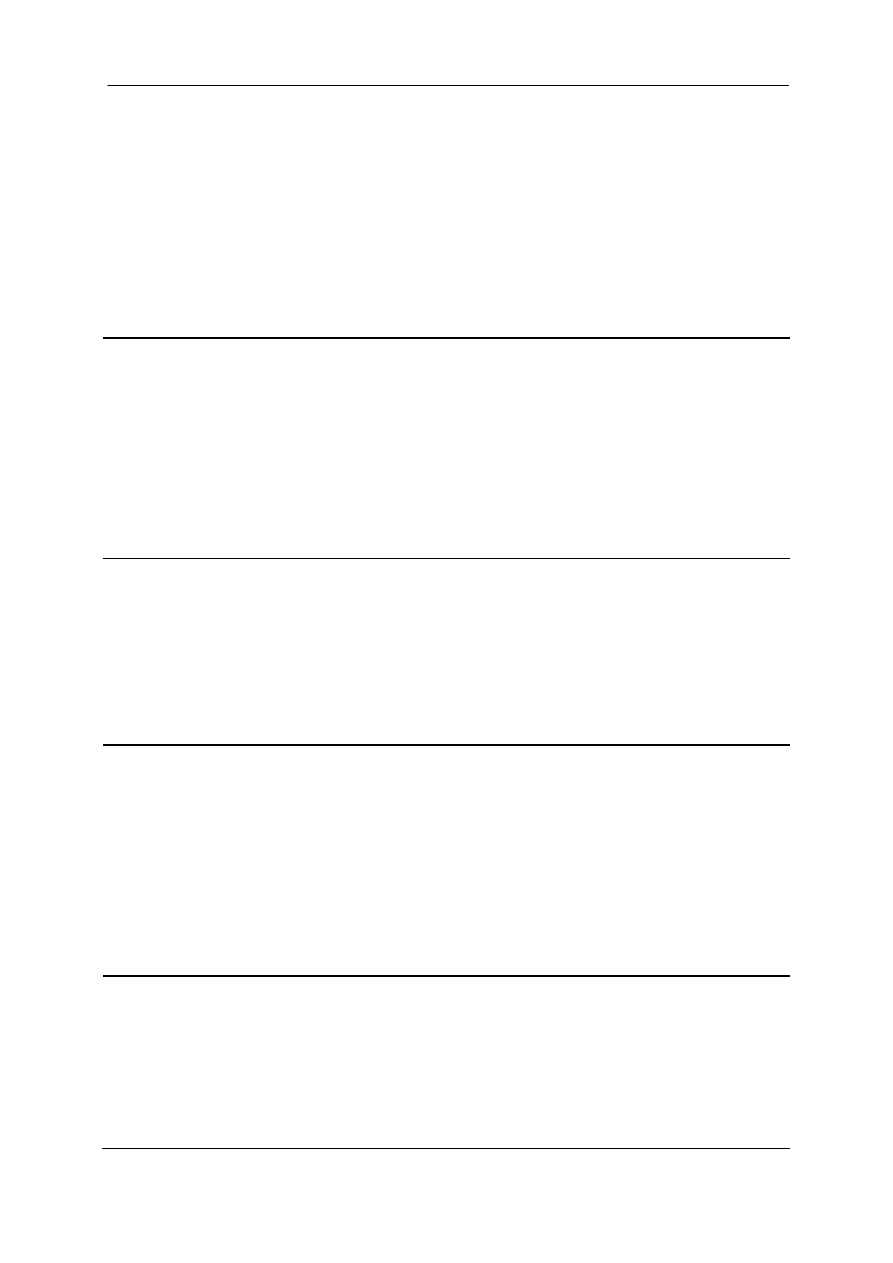

RRC

A

Przesu akumulator cy-

klicznie w prawo z CY

Zawarto

ć akumulatora przesuwana jest cyklicznie

w prawo z uwzgl dnieniem flagi CY. Wykonanie tego

rozkazu przy zerowej warto ci flagi CY odpowiada

podzieleniu przez 2 liczby zawartej w akumulatorze.

7 6 5 4 3 2 1 0

A

CY

Rozkazy operacji na bitach

CLR

bit

Wyzeruj bit

Zerowany jest bit o podanym adresie bezpo rednim.

(bit) ← 0

CLR

C

Wyzeruj znacznik (flag )

przeniesienia

Zerowany jest znacznik (flaga) przeniesienia.

C ← 0

CPL

bit

Negacja bitu

Negowany jest bit o podanym adresie bezpo rednim.

(bit) ← ( bit )

CPL

C

Negacja CY

Negowany jest znacznik (flaga) przeniesienia.

CY ← CY

ANL

C,bit

Pomnó logicznie przez bit.

Znacznik przeniesienia C jest zerowany, je eli warto

ć

logiczna bitu o podanym adresie jest równa 0, w prze-

ciwnym wypadku nie zmienia si .

CY ← CY ∧ (bit)

ANL

C,/bit

Pomnó logicznie przez

negacj zawarto ci bitu

Znacznik przeniesienia C jest zerowany, je eli warto

ć

logiczna bitu o podanym adresie jest równa 1, w prze-

ciwnym wypadku nie zmienia si .

CY ← CY∧ ( bit )

ORL

<r>,<s>

Sumuj logicznie

Wykonywana jest suma logiczna wskazanych argu-

mentów, przy czym wynik wpisywany jest do miejsca,

z którego pobrany zosta

ł argument <r>. Je eli operacja

Lista rozkazów

14

zosta

ła u yta do zmiany stanu wyj cia, to zmianie ule-

ga zawarto

ć rejestru wyj ciowego portu, a nie stan lo-

giczny ko cówek uk

ładu. Mo liwych jest sze ć kom-

binacji adresowania argumentów:

ORL A,Rr

A ← A ∨ Rr

ORL A,@Ri

A ← A ∨ Ri

ORL A,ad

A ← A ∨ (ad)

ORL A,#n

A ← A ∨ n

ORL ad,A

(ad) ← (ad) ∨ A

ORL ad,#n

(ad) ← (ad) ∨ n

ORL

CY,bit

Sumuj logicznie CY z bi-

tem

Wykonana zostaje operacja sumowania logicznego fla-

gi przeniesienia CY z zawarto ci bitu o podanym ad-

resie bezpo rednim: je li warto

ć logiczna bitu równa

jest 1, to flaga CY przyjmuje warto

ć 1.

W przeciwnym razie zawarto

ć CY nie zmienia si .

CY ← CY ∨ (bit)

ORL

C,/bit

Sumuj logicznie CY

z negacj bitu

Wykonana zostaje operacja sumowania logicznego fla-

gi przeniesienia CY z negacj zawarto ci bitu o poda-

nym adresie bezpo rednim: je li warto

ć logiczna bitu

równa jest 0, to flaga CY przyjmuje warto

ć 1.

W przeciwnym razie zawarto

ć CY nie zmienia si .

CY ← CY ∨ ( bit )

MOV

bit,C

Prze lij flag CY do bitu

Zawarto

ć flagi przeniesienia przesyłana jest do bitu o

podanym adresie bezpo rednim.

(bit) ← CY

MOV

C,bit

Prze lij warto

ć bitu do fla-

gi przeniesienia

Zawarto

ć bitu o podanym adresie bezpo rednim prze-

sy

łana jest do flagi przeniesienia.

Cy ← (bit)

Rozkazy skoków i rozkazy steruj ce

AJMP

adr11

Zawarto

ć licznika rozkazów zwi ksza si o 2. Do bi-

Lista rozkazów

15

Skocz bezwarunkowo na

stron

tów 0...10 licznika rozkazów jest wpisywany

11−bitowy adres bezpo redni, przy czym pi

ć bardziej

znacz cych bitów licznika rozkazów nie zmienia si .

Skok wykonywany jest pod adres na stronie, na której

jest umieszczony pierwszy bajt rozkazu nast pnego po

AJMP.

PC

10...0

← adr11

CJNE

<r>,<s>,d

Porównaj argumenty

i skocz, je li nie s równe

Wskazane argumenty <r> i <s> s porównywane. Je li

nie s równe, to nast puje skok wzgl dem adresu

pierwszego bajtu rozkazu nast pnego po CJNE. Je eli

warto

ć <r> jest mniejsza ni <s>, to znacznik C

przyjmuje warto

ć 1, w przeciwnym razie C jest zero-

wany. Mo liwe s cztery tryby adresowania argumen-

tów:

CJNE A,ad,d

PC ← PC + 3, je li A = (ad)

PC ← PC + d, je li A ≠ (ad)

CJNE A,#n,d

PC ← PC + 3, je li A = n

PC ← PC + d, je li A ≠ n

CJNE Rr,#n,d

PC ← PC + 3, je li Rr = n

PC ← PC + d, je li Rr ≠ n

CJNE @Ri,#n,d PC ← PC + 3, je li (Ri) = n

PC ← PC + d, je li (Ri) ≠ n

DJNZ

<r>,d

Zmniejsz o 1 i skocz, je li

nie zero

Od wskazanego argumentu odejmowana jest jedynka.

Je li po tej operacji argument nie jest równy zero, to

wykonywany jest skok wzgl dem adresu pierwszego

bajtu rozkazu nast pnego po DJNZ, przy czym stan

znaczników nie ulega zmianie. Mo liwe s dwa rodzaje

trybów adresowania:

DJNZ Rr,d

Rr ← Rr − 1,

je li Rr ≠ 0, to PC ← PC + d

je li Rr = 0, to PC ← PC + 2

DJNZ ad,d

(ad) ← (ad) − 1,

je li (ad) ≠ 0, to PC ← PC + d

je li (ad) = 0, to PC ← PC + 2

Lista rozkazów

16

JB

bit,d

Skocz, je li bit=1

Je eli warto

ć bitu o podanym adresie wynosi 1, to na-

st puje skok wzgl dem adresu pierwszego bajtu rozka-

zu nast pnego po JB (do wska nika licznika rozkazów

dodaje si przesuni cie d). Testowany bit nie ulega

zmianie.

PC ← PC + d,

je li (bit) = 1

PC ← PC + 3,

je li (bit) = 0

JBC

bit,d

Zeruj bit je li jest ustawio-

ny i skocz

Je li warto

ć bitu o wskazanym adresie bezpo rednim

wynosi 1, to jest on zerowany i wykonywany jest skok

wzgl dem pierwszego bajtu rozkazu nast pnego po

JBC (do zawarto ci licznika rozkazów dodawane jest

przesuni cie d).

PC ← PC + 3,

je li (bit) = 0

PC ← PC + d,

je li (bit) = 1

JC

d

Skocz, je li wyst pi

ło prze-

niesienie (je li CY= 1)

Je eli warto

ć flagi przeniesienia CY wynosi 1, to wy-

konywany jest skok wzgl dem pierwszego bajtu rozka-

zu nast pnego po JC, czyli do licznika rozkazów do-

dawane jest przesuni cie d.

PC ← PC + 2,

je li CY = 0

PC ← PC + d,

je li CY = 1

JMP

@A + DPTR

Skocz po rednio

Wykonywany jest skok pod adres b d cy sum warto-

ci DPTR i warto ci akumulatora, przy czym zawarto

ć

akumulatora traktowana jest jako liczba dwójkowa bez

znaku (z zakresu 0...255). Do licznika rozkazów wpi-

sywana jest suma zawarto ci rejestru DPTR

i akumulatora.

PC ← A + DPTR

JNB

bit,d

Skocz, je li bit o podanym

adresie jest zerowy

Je eli warto

ć bitu o podanym adresie bezpo rednim

jest zerowa, to wykonywany jest skok wzgl dem adre-

su pierwszego bajtu rozkazu nast pnego po JNB (do

zawarto ci licznika rozkazów dodawane jest przesuni -

cie d), przy czym warto

ć testowanego bitu nie ulega

Lista rozkazów

17

zmianie.

PC ← PC +3,

je li (bit) = 1

PC ← PC + d,

je li (bit) = 0

JNC

d

Skocz, je li nie wyst pi

ło

przeniesienie (je li CY=0)

Je eli warto

ć flagi przeniesienia CY wynosi 0, to wy-

konywany jest skok wzgl dem adresu pierwszego bajtu

rozkazu nast pnego po JNC, czyli do zawarto ci licz-

nika rozkazów dodawane jest przesuni cie d.

PC ← PC + 2,

je li CY = 1

PC ← PC + d,

je li CY = 0

JNZ

d

Skocz, je li akumulator nie

jest zerowy

Je eli zawarto

ć akumulatora nie jest równa zeru, to

nast puje skok wzgl dem adresu pierwszego bajtu roz-

kazu nast pnego po JNZ, czyli do licznika rozkazów

dodawane jest przesuni cie d.

PC ← PC + 2,

je li A = 0

PC ← PC + d,

je li A ≠ 0

JZ

d

Skocz, je li akumulator jest

zerowy

Je eli zawarto

ć akumulatora jest równa 0, to nast puje

skok wzgl dem adresu pierwszego bajtu rozkazu na-

st pnego po JZ, czyli do licznika rozkazów dodawane

jest przesuni cie d.

PC ← PC + 2,

je li A ≠ 0

PC ← PC + d,

je li A = 0

LJMP

adr16

Skocz bezwarunkowo

Do licznika rozkazów wpisywany jest 16−bitowy adres

bezpo redni, pozwalaj c na skok pod dowolny adres

w ca

łej przestrzeni pami ci programu

PC ← adr16

NOP

Rozkaz pusty (nie rób nic)

adna operacja nie jest wykonywana.

SJMP

d

skocz bezwarunkowo

Do zawarto ci licznika rozkazów dodawane jest prze-

suni cie d. Skok jest wykonywany wzgl dem adresu

pierwszego bajtu nast pnego rozkazu.

PC ← PC + 2

PC ← PC + d

SETB

bit

Do bitu o podanym adresie bezpo rednim wpisywana

Lista rozkazów

18

Ustaw bit

jest 1.

(bit) ← 1

SETB

C

Ustaw flag przeniesienia

Do flagi przeniesienia wpisywana jest 1.

CY ← 1

Rozkazy obs

ługi podprogramów, przerwa i operacji na stosie

ACALL

adr11

Skocz do podprogramu na

stronie

Zawarto

ć licznika rozkazów PC zwi kszana jest o 2,

a nast pnie odk

ładana na stos. Wska nik stosu jest

zwi kszany o 2, do bitów 0−10 licznika rozkazów jest

wpisywany 11−bitowy adres bezpo redni, przy czym

pi

ć bardziej znacz cych bitów licznika rozkazów nie

zmienia si . Skok do podprogramu wykonuje si na tej

stronie, na której jest umieszczony pierwszy bajt roz-

kazu nast pnego po ACALL.

PC ← PC + 2

SP ← SP + 1

(SP) ← PC

7...0

SP ← SP + 1

(SP) ← PC

15...8

PC

10...0

← adr11

LCALL

adr16

Wywo

łaj podprogram

Podczas pobrania rozkazu zawarto

ć licznika rozkazów

jest powi kszana o 3 i

ładowana na stos. Zawarto ć

wska nika stosu jest zwi kszana o 2, a do licznika roz-

kazów jest wpisywany 16-bitowy adres bezpo redni,

pozwalaj c na skok do podprogramu pod dowolny ad-

res w pami ci programu.

PC ← PC + 3

SP ← SP + 1

(SP) ← PC

7...10

SP ← SP + 1

(SP) ← PC

15...8

PC ← adr16

POP

ad

Do komórki wewn trznej pami ci danych o podanym

Lista rozkazów

19

Zdejmij ze stosu

adresie bezpo rednim wpisywane s dane z wierzcho

ł-

ka stosu, tzn komórki wewn trznej pami ci danych

o adresie zawartym we wska niku stosu SP. Warto

ć

SP zmniejszana jest o 1.

(ad) ← SP

SP ← SP − 1

PUSH

ad

Ładuj na stos

Zawarto

ć wska nika stosu zwi kszana jest o 1, a na-

st pnie na wierzcho

łek stosu jest wpisywana zawarto ć

komórki wewn trznej pami ci danych lub rejestru spe-

cjalnego SFR o podanym adresie bezpo rednim.

SP ← SP + 1

(SP) ← (ad)

RET

Wró

ć z podprogramu

Rozkaz powrotu z podprogramu. Adres powrotu jest

wpisywany ze stosu do licznika rozkazów, po czym

zawarto

ć wska nika stosu zmniejszana jest o dwa.

PC

15...8

← (SP)

SP ← SP − 1

PC

7...0

← (SP)

SP ← SP − 1

RETI

Wró

ć z przerwania

Rozkaz powrotu z podprogramu obs

ługi przerwania.

Adres powrotu jest wpisywany ze stosu do licznika

rozkazów, po czym zawarto

ć wska nika stosu zmniej-

szana jest o dwa. Wykonanie tego rozkazu jest dla sys-

temu przerwa sygna

łem zako czenia obsługi prze-

rwania, czyli adne zg

łoszenie przerwania o takim sa-

mym lub ni szym priorytecie nie b dzie wcze niej

przyj te.

PC

15...8

← (SP)

SP ← SP – 1

PC

7...0

← (SP)

SP ← SP – 1

Wyszukiwarka

Podobne podstrony:

Lista rozkazów?51

Lista rozkazow 8051

@ Lista rozkazowa

lista rozkazow 8051

8086 Lista rozkazów, Akademia Morska, III semestr, technika cyfrowa, Technika Cyfrowa, TC - lab Dąbr

Lista rozkazow 8051, architektura komputerow, architektura komputerow

8051 lista rozkazow, ELEKTRONIKA I PROGRAMOWANIE, Mikroprocesory, programowanie Bascom, AVR,

Lista rozkazów i opis 8051

lista rozkazowh000

8080 lista rozkazów i kodów, Akademia Morska, III semestr, technika cyfrowa, Technika Cyfrowa, TC -

lista rozkazów 8051

8051 lista rozkazow

mazurkiewicz,Technika Cyfrowa, lista rozkazów procesora

8051 lista rozkazow

lista rozkazów 8051

więcej podobnych podstron