1

V. Tranzystory polowe/unipolowe

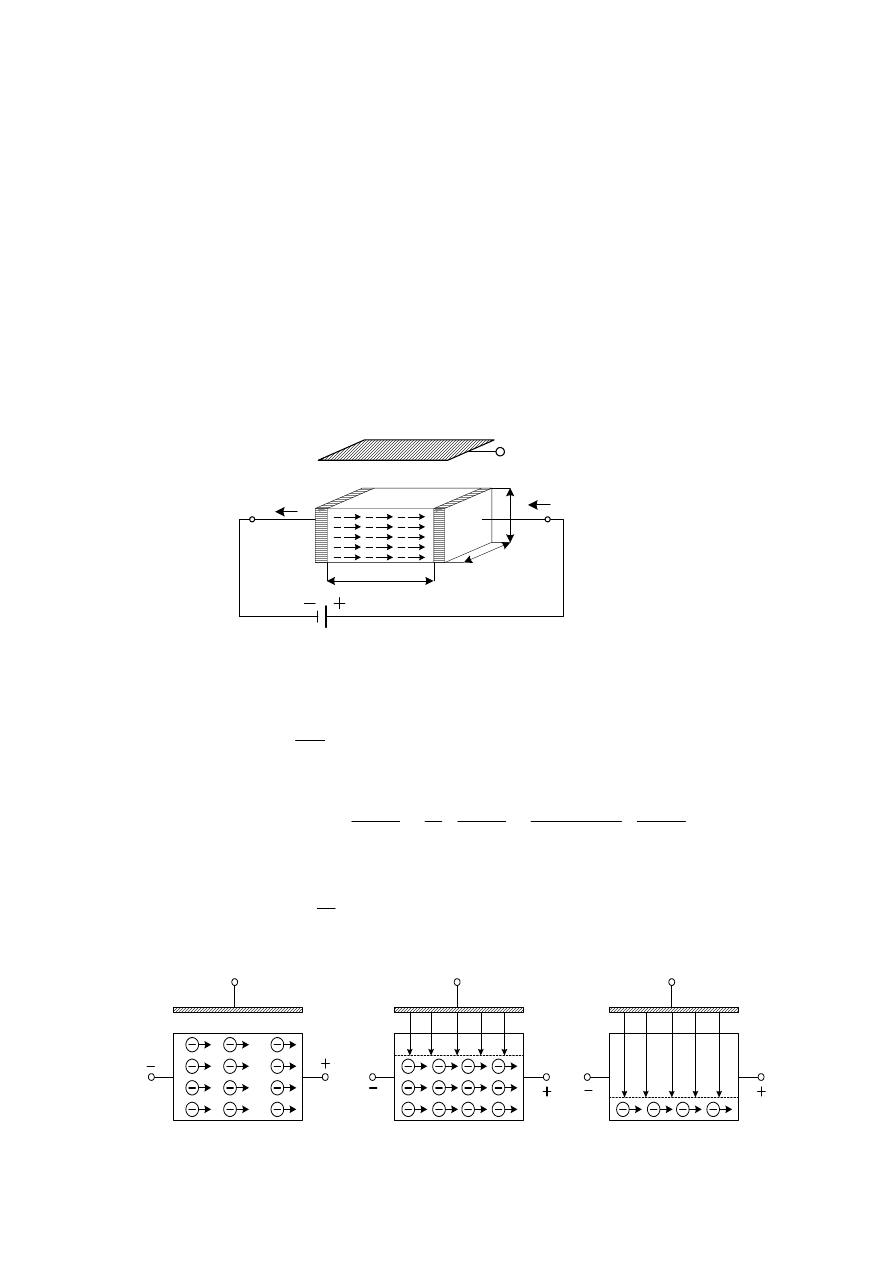

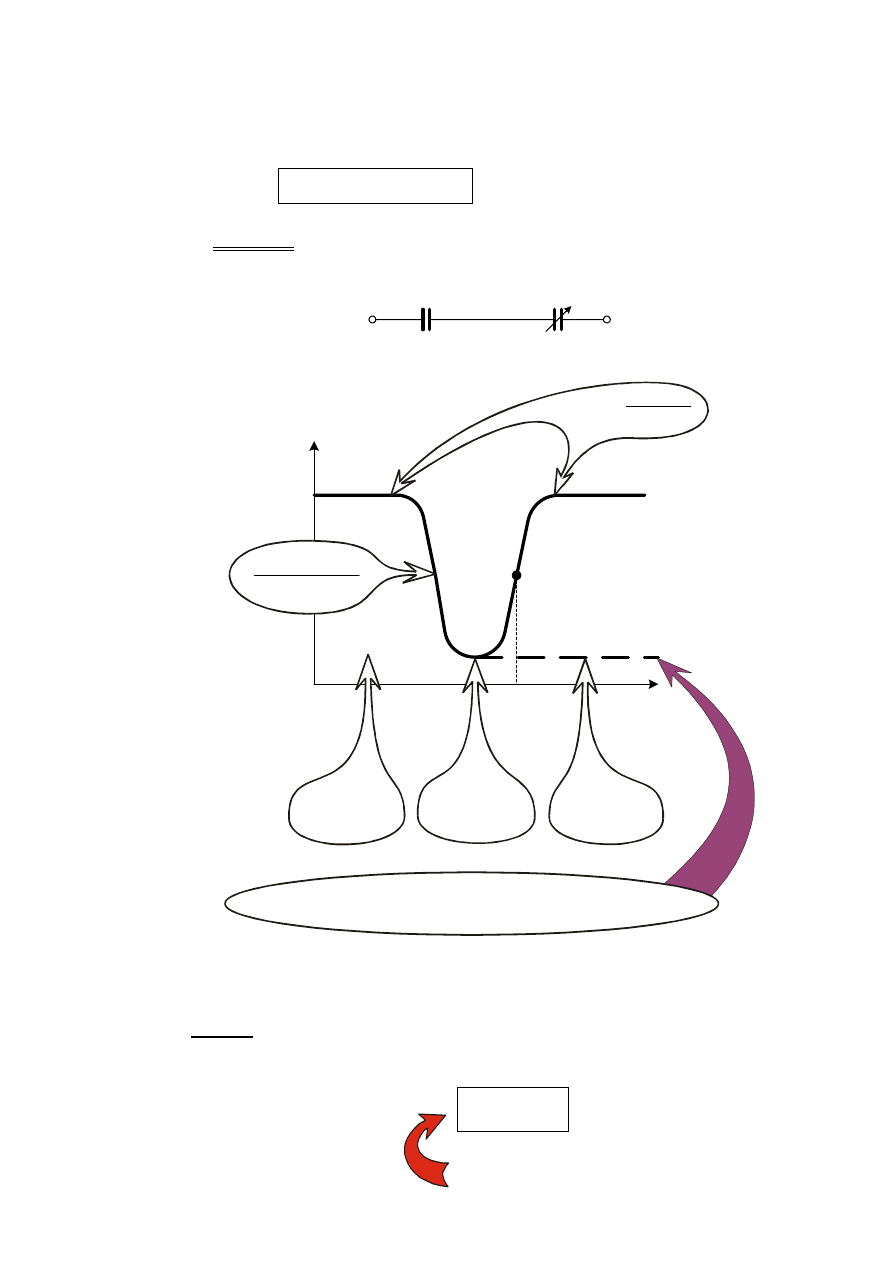

FET – zasada działania

l

S

i

E = U

DS

h

w

kanał typu n

D

i

V

G

„–”

n

n

p

n

>>

n

n

p

n

≈

gate

Rys. 5.1

•

Prąd w obwodzie

o

R

E

i

=

(5.1)

w

h

l

N

q

1

w

h

l

1

w

h

l

R

n

o

⋅

⋅

⋅

µ

⋅

=

⋅

⋅

σ

=

⋅

⋅

ρ

=

(5.2)

stąd

w

1

~

R

o

(5.3)

•

S

D

S

D

S

D

V

1

V

G

−

=

0

V

G

=

V

3

V

G

−

=

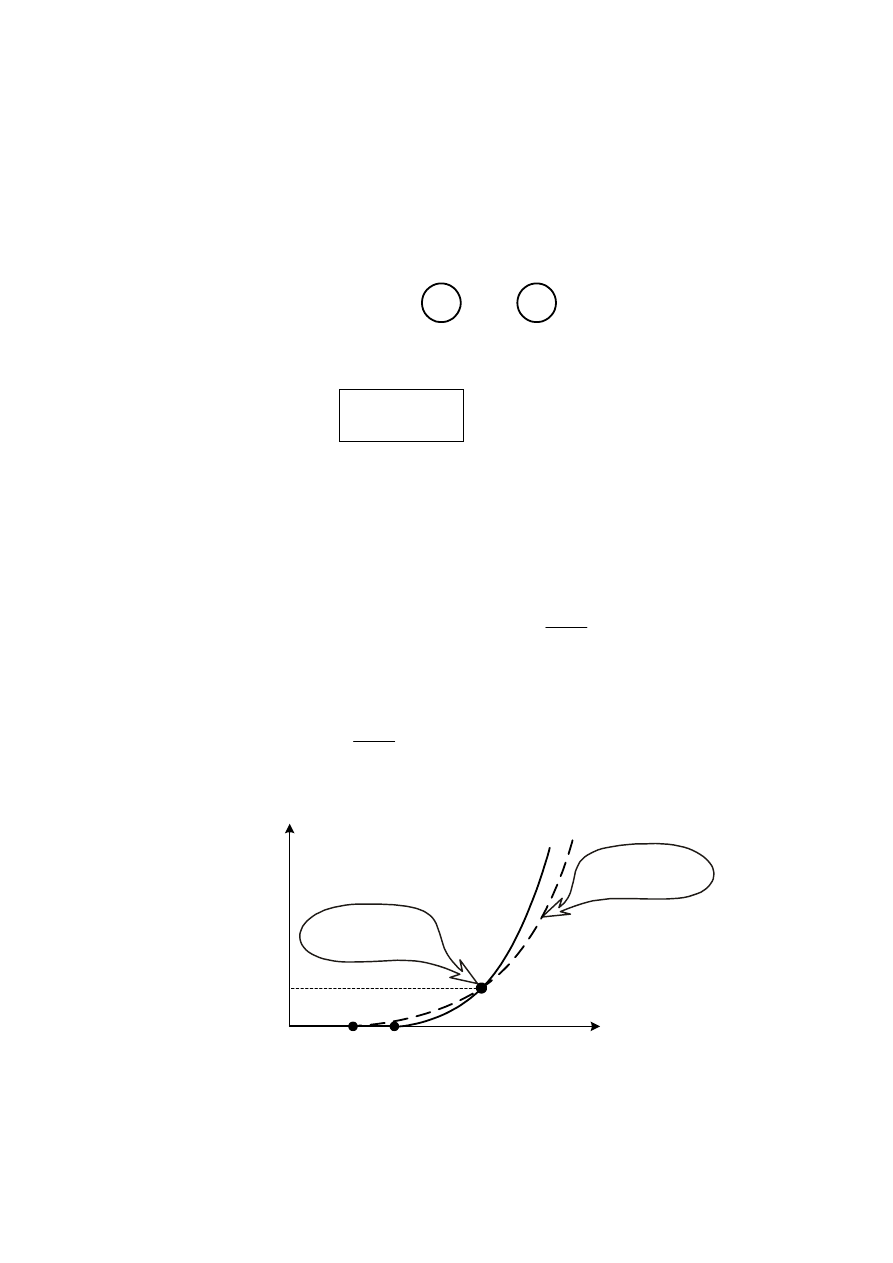

Rys 5.2

2

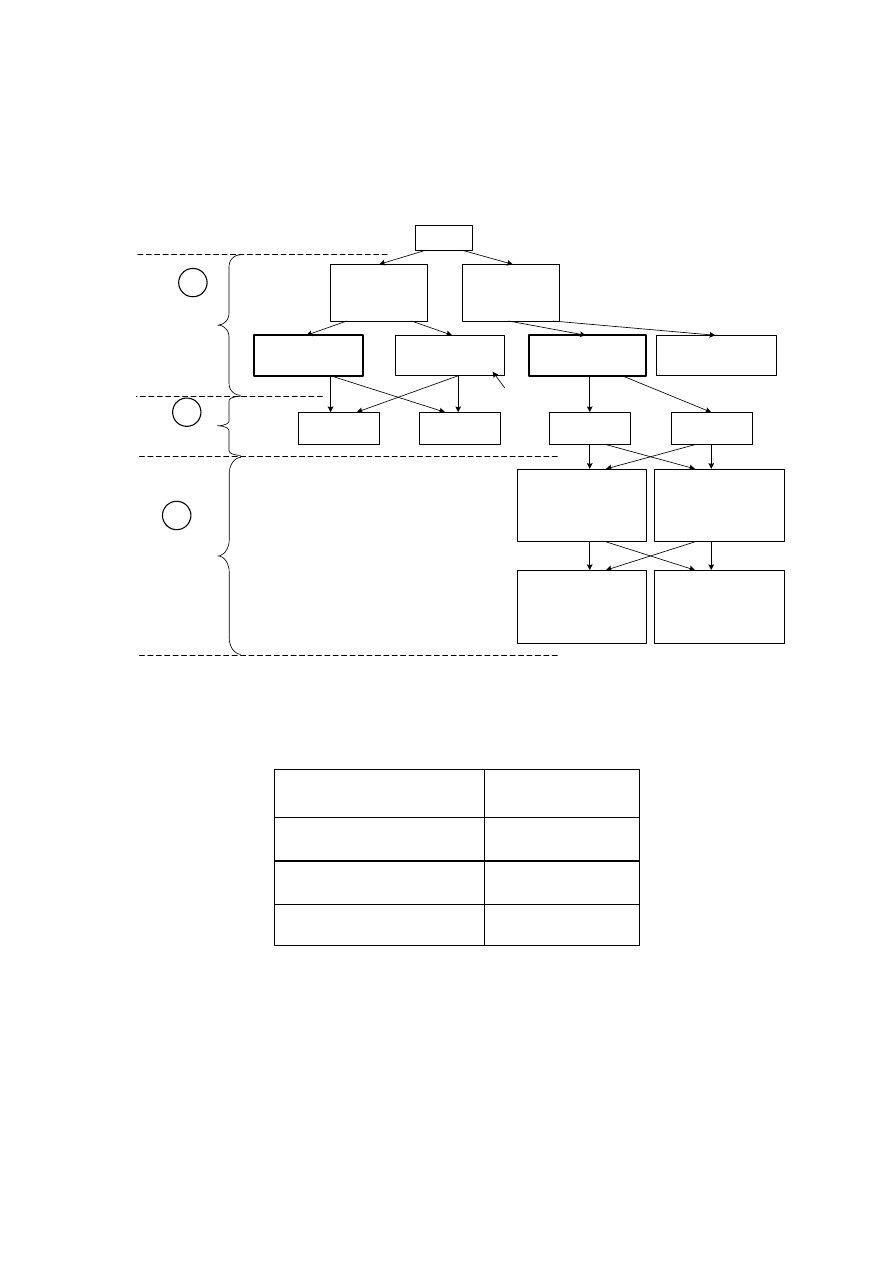

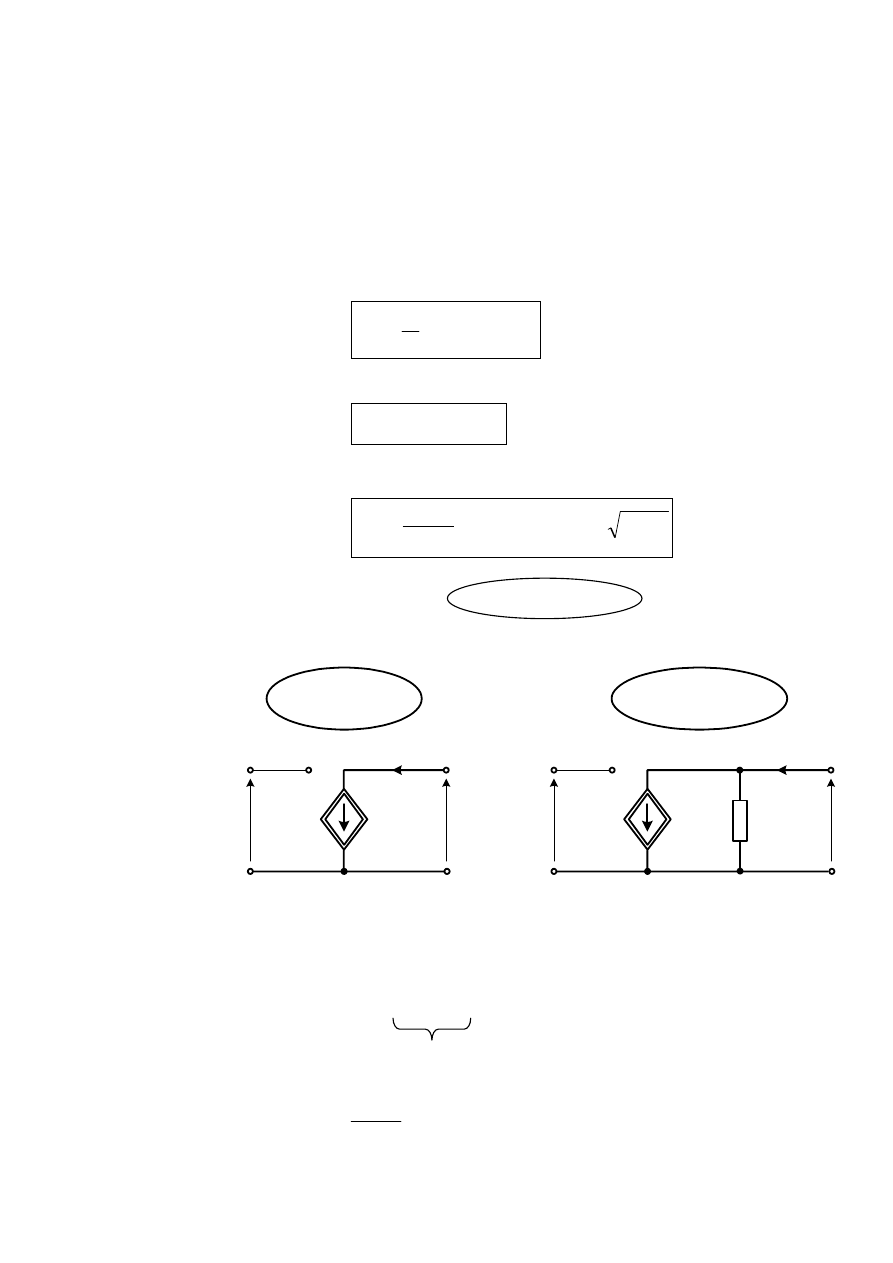

Klasyfikacja

•

Klasyfikacja 3- warstwowa

FET

złącze

JFET

z izolowaną

bramką

IGFET

ze złączem p-n

PNFET

ze złączem m-s

MESFET

MIS, MISFET

MOS, MOSFET

ciekowarstwowy

TFT

GaAs

kanał „n”

kanał „p”

I

II

III

sposób

izolacji

rodzaj

kanału

technologia

kanału

kanał n

kanał p

kanał

zaindukowany

(SCMOS)

kanał

wbudowany

(BCMOS)

praca z kanałem

wzbogacanym

(EMOS)

praca z kanałem

zubożanym

(DMOS)

Rys. 5.3

•

Typ tranzystora a rodzaj izolacji

typ tranzystora

izolacja

MOS, MIS

dielektryk

JFET

złącze p-n

złącze m-s

MESFET

3

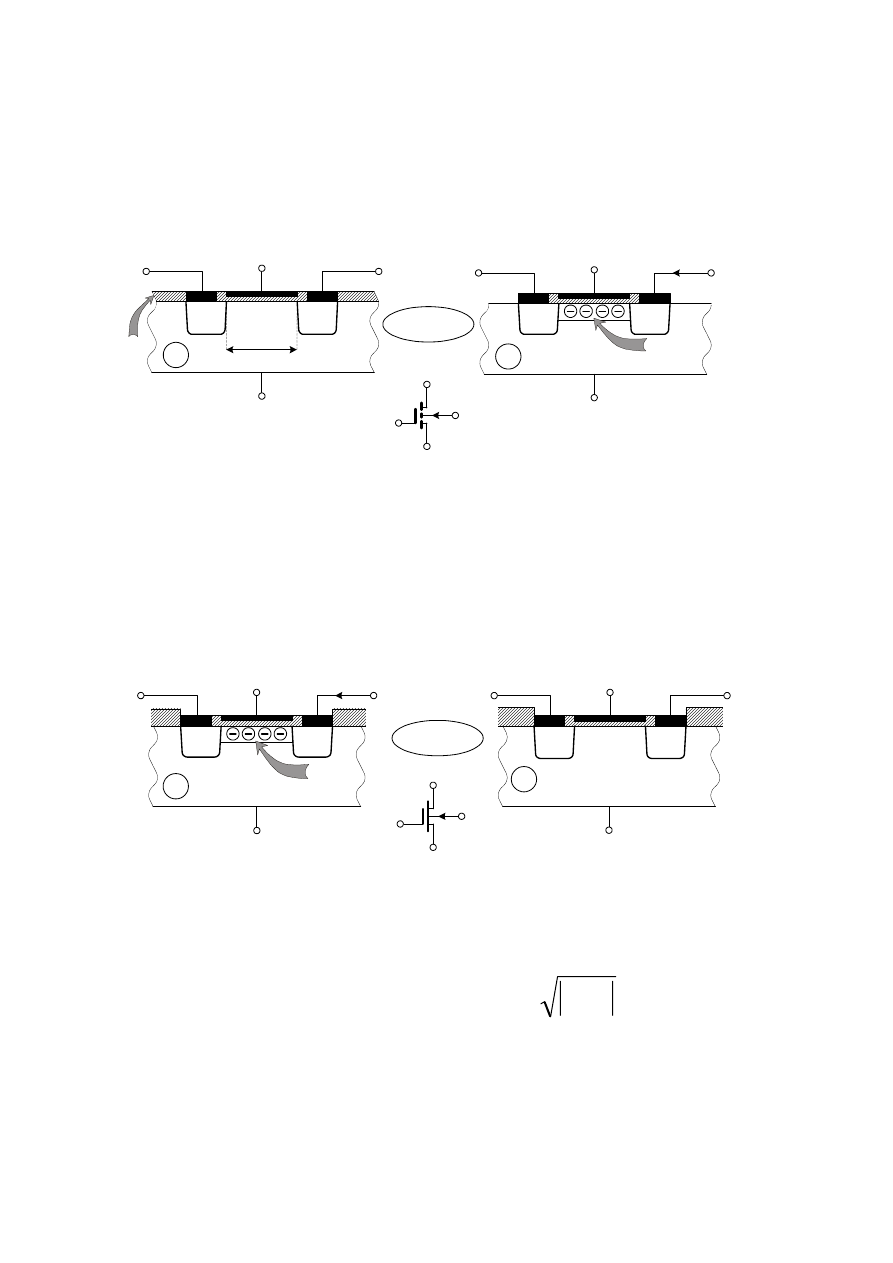

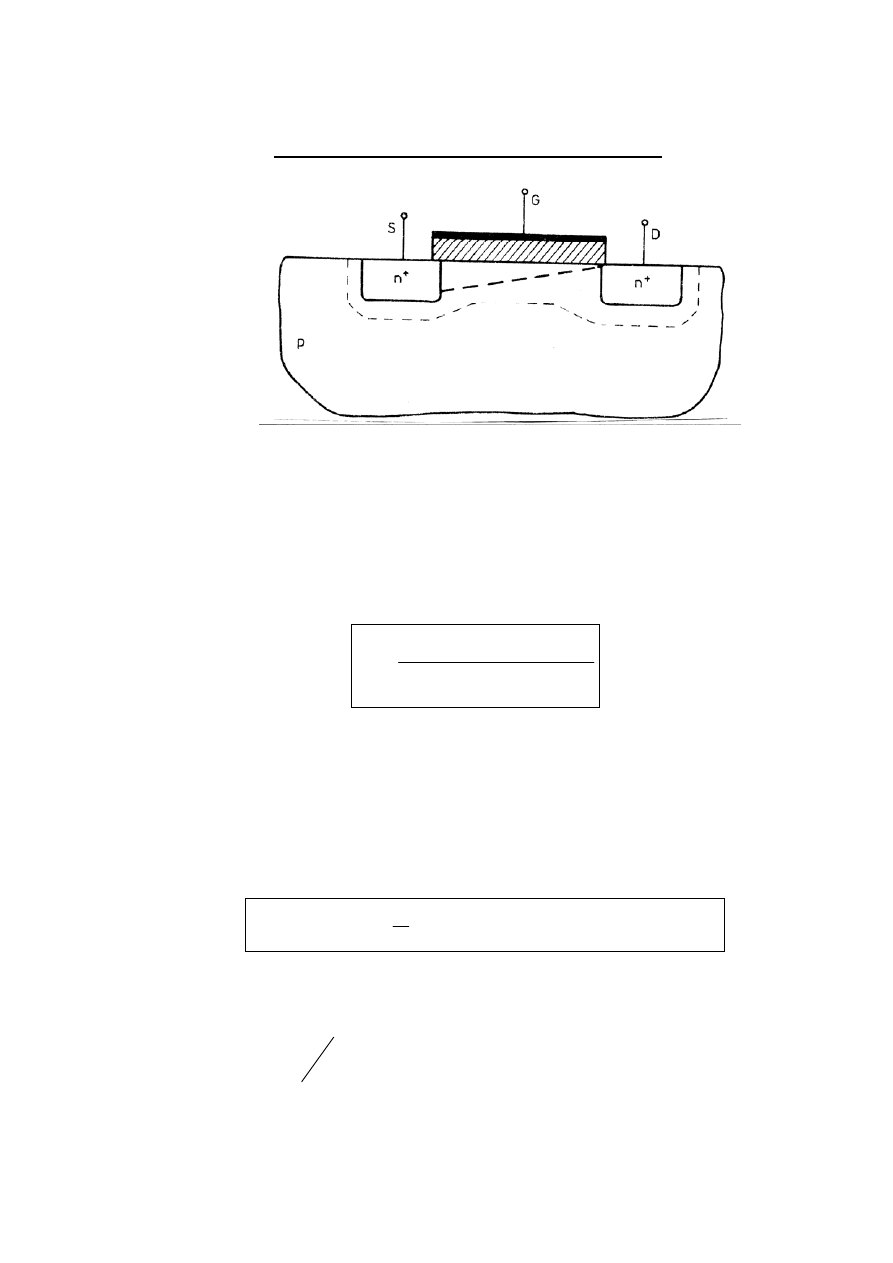

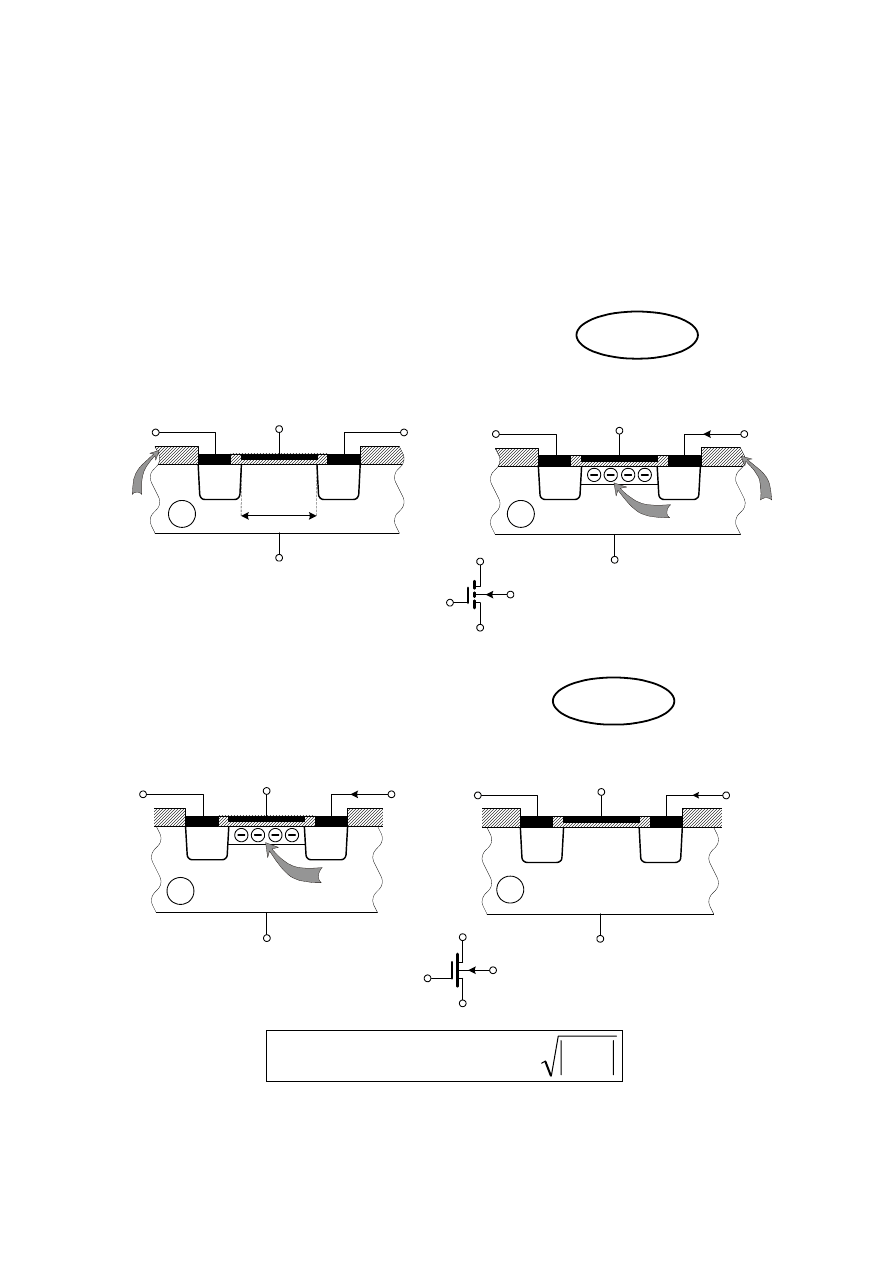

MOS

-

kanał indukowany

-

normalnie wyłączony

-

pracujący ze wzbogaceniem

D

S

G V

G

= 0

m

1

L

µ

<

+

n

+

n

p

B

D

S

V

G

> 0

+

n

+

n

p

B

D

i

kanał

(stan inwersji)

EMOS

S

G

D

B

2

0

Si

(substrate)

Rys. 5.4

MOS

-

kanał wbudowany

-

normalnie załączony

-

pracujący ze zubożaniem

D

S

G

+

n

+

n

p

B

D

i

kanał

D

S

V

G

< 0

+

n

+

n

p

B

S

B

G

DMOS

D

Rys. 5.5

„Elektryczna” regulacja wartości napięcia

progowego

(

)

( )

BS

p

BS

p

u

A

0

U

u

U

⋅

+

=

(5.4)

6

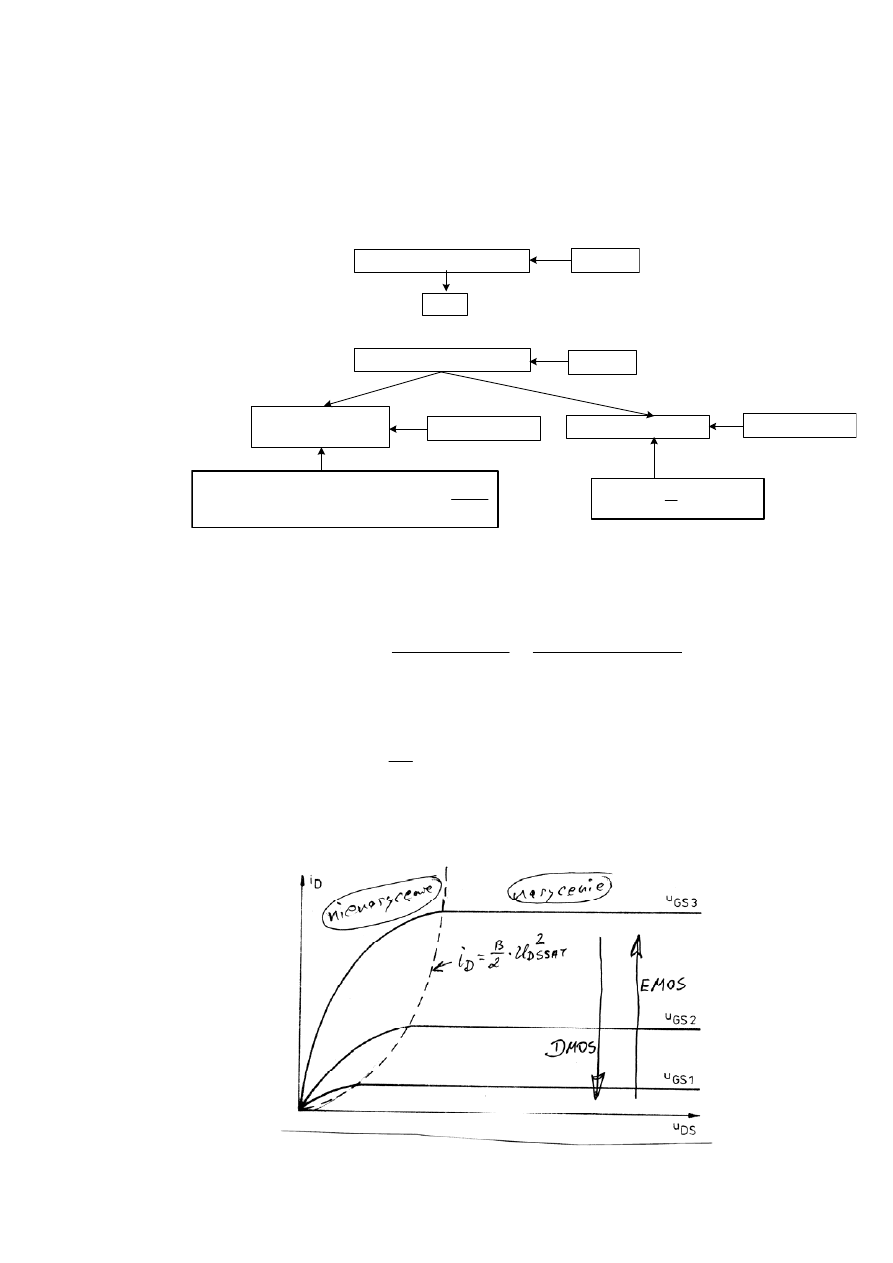

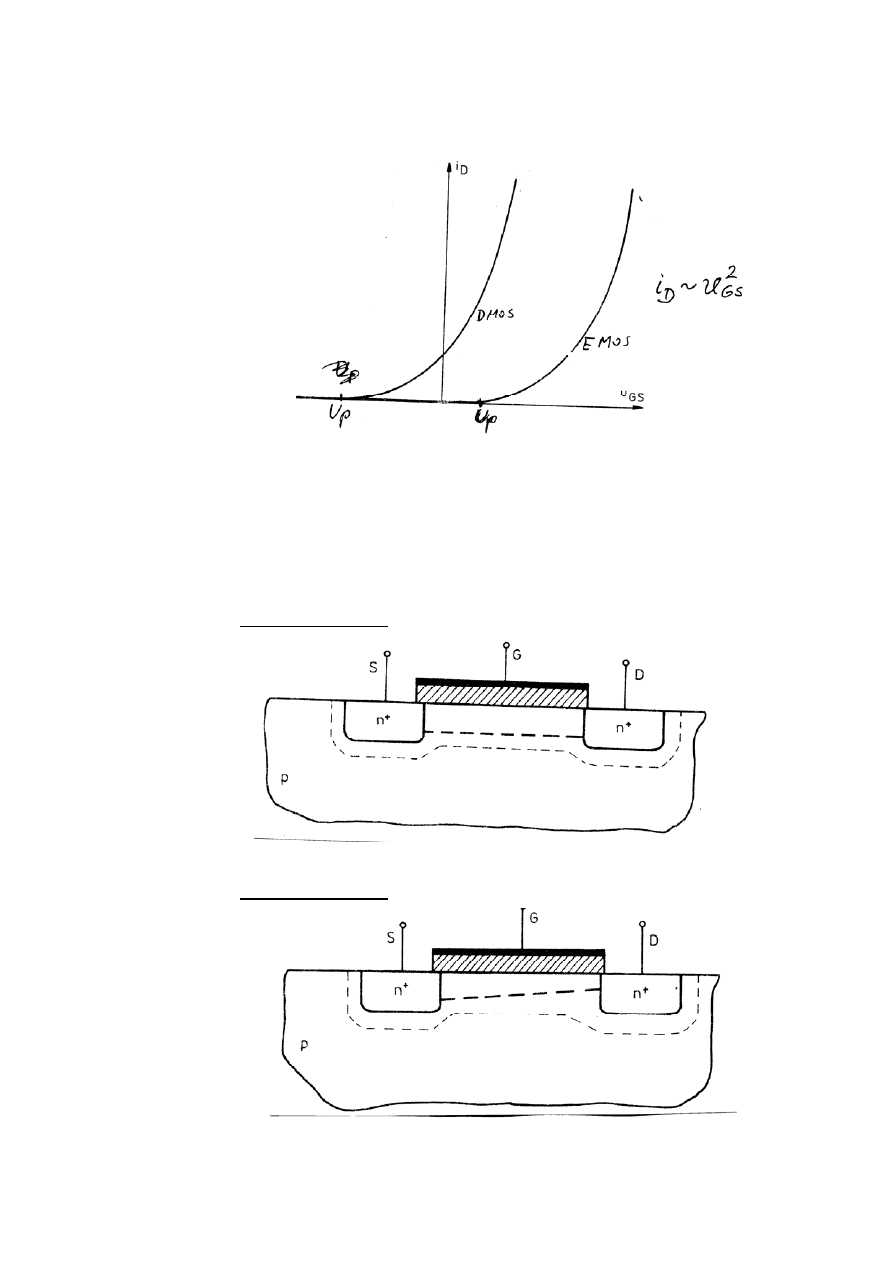

Charakterystyki statyczne idealnego MOS

•

Zakresy pracy i zależności

analityczne

0

i

D

=

zakres odcięcia

p

GS

U

u

<

(5.5)

zakres przewodzenia

p

GS

U

u

≥

zakres pentodowy

zakres triodowy

(nienasycenia)

p

GS

GS

U

u

u

−

<

p

GS

GS

U

u

u

−

≥

(

) (

)

−

−

=

2

u

u

U

u

B

u

,

u

i

2

DS

DS

p

GS

DS

GS

D

(5.6)

(

)

(

)

2

p

GS

GS

D

U

u

2

B

u

i

−

=

(5.7)

•

Parametr materiałowy B

ox

ox

o

o

ox

o

t

L

W

L

C

W

B

⋅

ε

⋅

ε

⋅

⋅

µ

=

⋅

⋅

µ

=

(5.8)

tzn.

L

W

~

B

o

~

B

µ

•

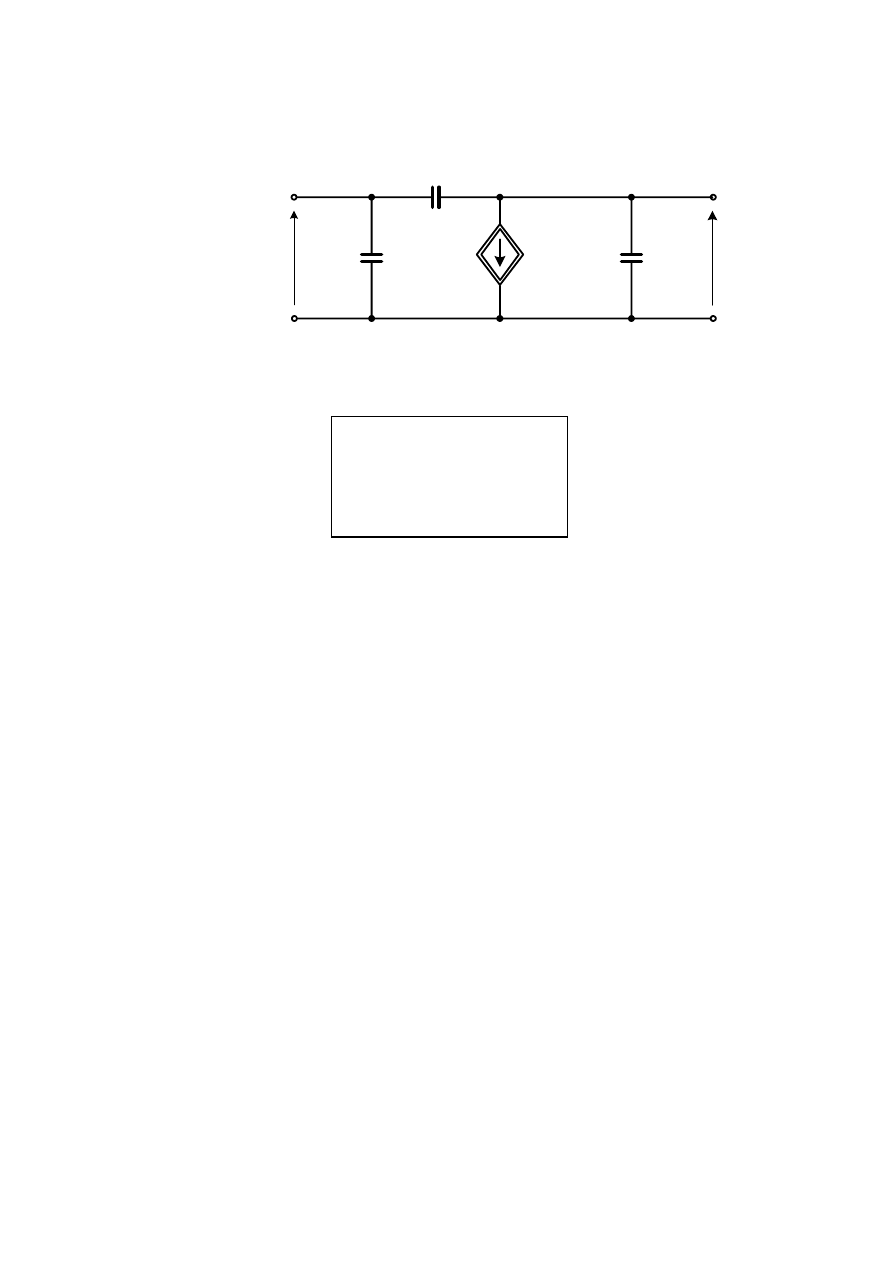

Postać graficzna modelu

Charakterystyki wyjściowe i

D

(u

DS

)

7

Rys. 5.6

Charakterystyki przejściowe

Rys. 5.7

•

Kształt kanału dla różnych zakresów pracy

Zał:

const

u

GS

=

var

u

DS

=

•

Zakres triodowy: małe wartości u

DS

Rys. 5.8a

•

Zakres triodowy: większe wartości u

DS.

Rys. 5.8b

8

•

Granica zakresu triodowego i pentodowego

Rys. 5.8c

Charakterystyki statyczne rzeczywistego

MOS

•

Modulacja ruchliwości nośników

(

)

p

GS

o

U

u

1

−

⋅

Θ

+

µ

=

µ

(5.9)

gdzie:

Θ

- parametr modelu

Stąd modyfikacja parametrem B w którym

0

µ

należy

zastąpić przez

µ

•

Modulacja długości kanału (zakres pentodowy)

(

) (

)

(

)

[

]

DSSAT

DS

2

p

GS

DS

GS

D

u

u

1

U

u

2

B

u

,

u

i

−

γ

+

⋅

−

=

(5.10)

gdzie:

γ

- parametr modelu

γ

1

- sens analogiczny jak napięcie Early’ego w

BJT

9

•

Praca w zakresie podprogowym (odcięcia)

g

D

i

i

=

D

G

S

B

+

n

p

GS

U

u

<

p

GS

U

u

≈

dla

DS

D

u

exp

~

i

składowa dyfuzyjna

!

+

n

•

Przebicie bramka – podłoże (warstwy izolatora Si0

2

)

max

GS

U

– typowo kilkadziesiąt voltów

•

Przebicie lawinowe złącza dren-podłoże

typowo mierzy się

DSO

U

tzn. przy

0

u

GS

=

Rys. 5.9

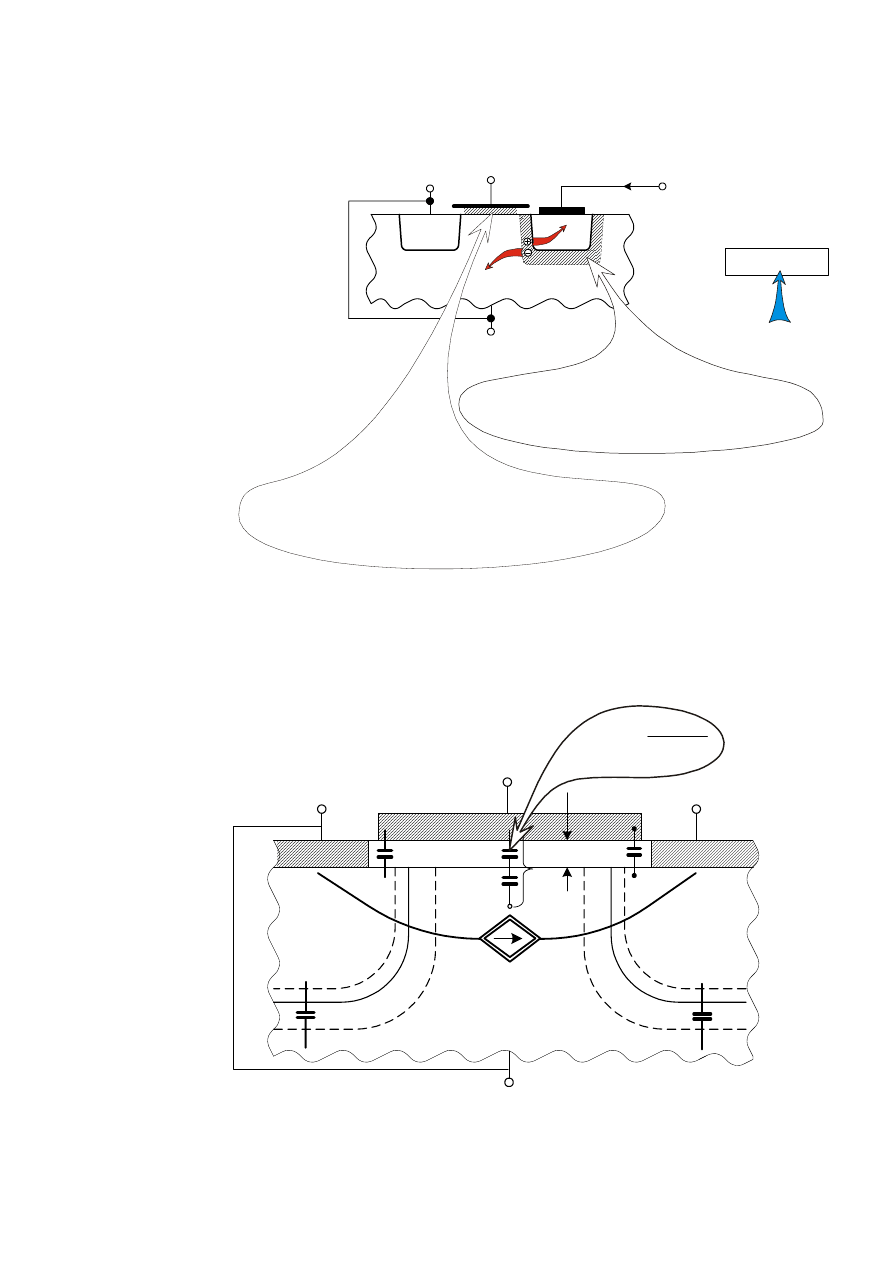

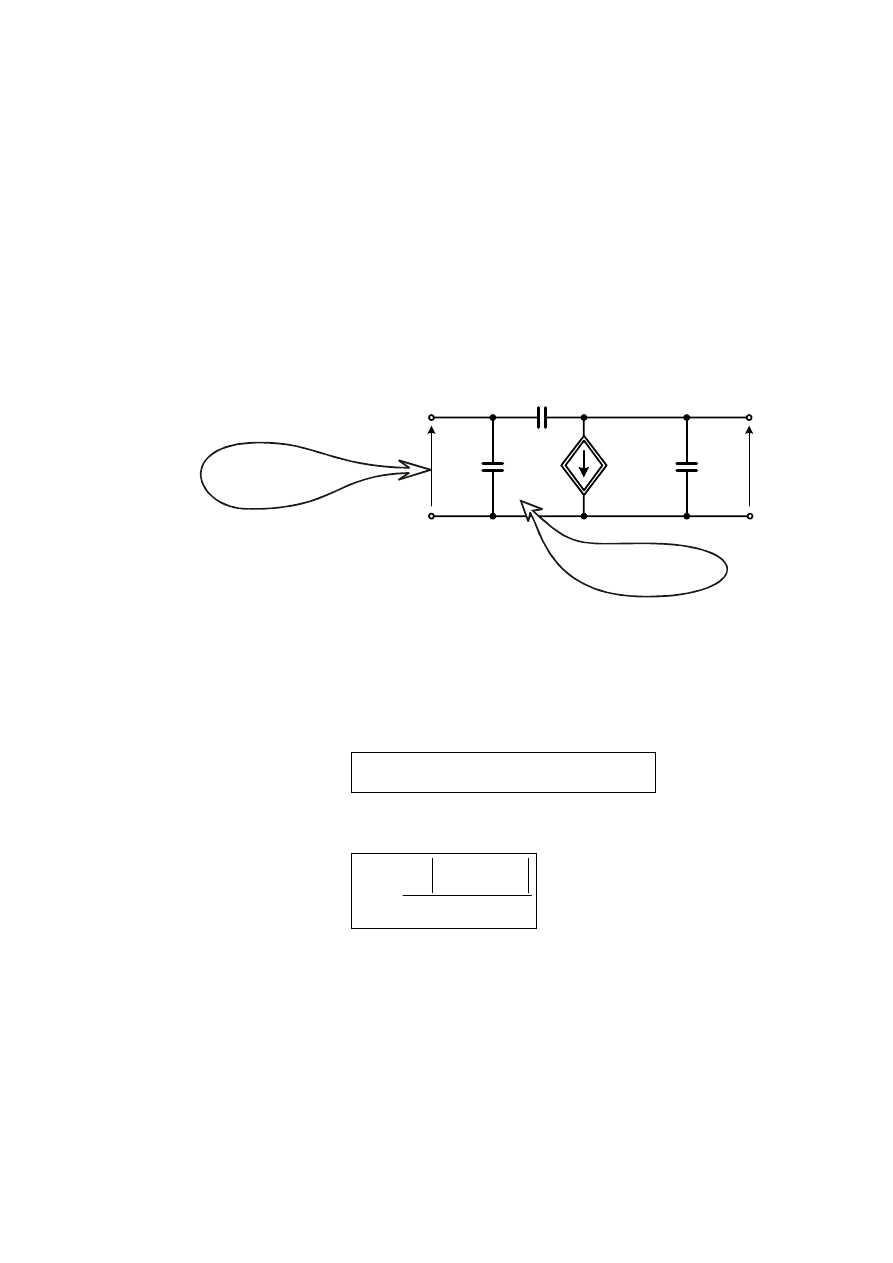

Wielkosygnałowy dynamiczny model MOS

•

Należy uzupełnić model stałoprądowy o pojemności (rys

5.10)

GDE

C

GSE

C

ox

C

( )

u

C

j

G

C

S

D

G

(

)

DS

GS

D

u

,

u

i

ox

t

B

„-”

„+”

SB

C

DB

C

ox

ox

o

ox

t

C

ε

ε

=

Rys. 5.10

8

Trzy grupy pojemności

•

Nieliniowe pojemności złączowe (pasożytnicze)

SB

SB

u

~

C

DB

DB

u

~

C

typowo kilka pF

Typowo „

S

” zwarte z „

B

”

⇒

0

C

SB

→

→

DB

C

pojemność wyjściowa

•

Liniowe pojemności nakładki metalowej elektrody bramki na

obszary źródła i drenu (pasożytnicze)

x

GDE

GSE

t

1

~

C

,

C

szczególnie szkodliwa, jest powodem sprzężenia zwrotnego

między wyjściem (dren) a wejściem (bramka)

!

9

•

Nieliniowa pojemność bramki (rys. 5.10)

(

)

sygn

GB

G

f

,

u

f

C

=

założenie

Rozważamy

nEMOS

(kanał

n

, normalnie OFF)

g

C

ox

C

.

cz

.

m

.

cz

.

w

p

U

G

u

x

ox

o

ox

t

C

ε

⋅

ε

=

stan

akumulacji

stan

zubożenia

stan

inwersji

ox

C

( )

u

C

j

( )

( )

u

C

C

u

C

C

j

ox

j

ox

+

⋅

Dyspersja częstotliwościowa pojemności bramki

Rys. 5.11

Uwaga

Pojemność

ox

C

jest pojemnością użyteczną, gdyż

ox

C

~

B

!

10

ma mieć dużą wartość

11

•

Postać modelu

GS

u

GSE

G

GS

C

C

C

+

=

(

)

DS

GS

D

u

,

u

i

GDE

C

D

S

DB

C

G

DS

u

Rys. 5.12

Typowe

wartości pojemności

pF

30

5

C

G

÷

=

pF

1

C

,

C

GSE

GDE

<

pF

5

2

,

0

C

DB

÷

=

12

Model małosygnałowy MOS (m-cz)

•

Zasada tworzenia – podana wcześniej (rozdz. I)

•

Określa się dla zakresu nasycenia, głównie konfiguracja WS

•

Z modelu stałoprądowego (nasycenie)

(

)

2

p

GS

D

U

u

2

B

i

−

=

Można napisać dla małych amplitud

gs

m

d

U

g

I

⋅

=

(5.11)

•

Transkonduktancja

m

g

(

)

D

p

GS

GS

D

m

Bi

2

U

u

B

du

di

g

=

−

=

=

(5.12)

typowo

mS

1

3

.

0

g

m

÷

=

•

Schematy zastępcze

gs

U

gs

m

U

g

⋅

ds

U

G

D

d

I

S

MOS idealny

gs

U

gs

m

U

g

⋅

ds

U

G

D

d

I

S

MOS rzeczywisty

ds

r

Rys. 5.13

Dla rzeczywistego MOS

ds

ds

gs

m

d

U

g

U

g

I

⋅

+

⋅

=

(5.13)

MOS idealny

gdzie

D

DS

D

ds

i

du

di

g

⋅

γ

=

=

(5.14)

Nachylenie ch-ki

wyjściowej (wzór 5.10)

13

Model małosygnałowy MOS (m.cz.)

•

Małosygnałowy model m.cz. należy uzupełnić o

pojemności:

Æ

pojemność bramki –

g

C

Æ

pojemność warstwy opróżnionej dren-podłoże –

db

C

Æ

pojemności pasożytnicze wynikające z nakładki

powierzchni bramki nad źródło i dren –

gde

,

gse

C

C

•

Schemat zastępczy

gs

U

gs

m

U

g

⋅

ds

U

gde

C

db

C

gs

C

widać tylko

pojemność

!

g

gse

gs

C

C

C

+

=

•

Właściwości częstotliwościowe

Częstotliwość charakterystyczna

=

m

f

częstotliwość przy

której moduł amplitudy prądu wejściowego o charakterze

pojemnościowym jest równy modułowi amplitudy prądu źródła

sterowanego w obwodzie wyjściowym, tj.

gs

m

gs

gs

m

U

g

U

C

f

2

⋅

=

⋅

⋅

⋅

π

(5.15)

Po podstawieniu odpowiednich zależności i przekształceniach,

dla dowolnego typu przewodnictwa w kanale otrzymujemy

2

p

GS

m

L

2

U

u

f

⋅

π

−

⋅

µ

=

(5.16)

gdzie:

L

– długość kanału

•

Wniosek:

C

zęstotliwość charakterystyczna jest większa dla

nMOS-ów

w porównaniu z

pMOS-ami

, ze względu

na około trzykrotnie większą wartość ruchliwości

elektronów w porównaniu z dziurami. Także istotny

def

.

Rys. 5.14

14

jest wpływ długości kanału – im krótszy kanał, tym

większa

m

f

.

MOS – wpływ temperatury

•

Temperatura wpływa na parametry

B

p

U

oraz

•

Zależność B(T) wynika z zależności

( )

T

µ

, stąd

κ

−

T

~

B

(5.17)

tutaj

1

≈

κ

(wpływ międzypowierzchni na mechanizm

rozpraszania nośników)

•

Napięcie progowe zależy liniowo od temperatury

( )

( )

∆

⋅

+

⋅

=

T

dT

dU

1

T

U

T

U

p

0

p

p

(5.18)

gdzie

wartość współczynnika termicznego

K

/

mV

kilka

dT

dU

p

−

=

•

Wpływ temperatury na statyczną charakterystykę

(

)

GS

D

u

i

1

T

2

T

>

.

komp

I

D

1

T

2

T

2

p

U

1

p

U

D

i

GS

u

korzystne

!

TÊ to i

D

Ì

punkt

autokompens.

Rys. 5.15

15

Uwaga

!

punkt

autokompensacji

!

JFET

Budowa

•

Elektroda bramki

JFET’a

jest oddzielona od kanału za pomocą

zaporowo spolaryzowanego złącza

p-n

.

•

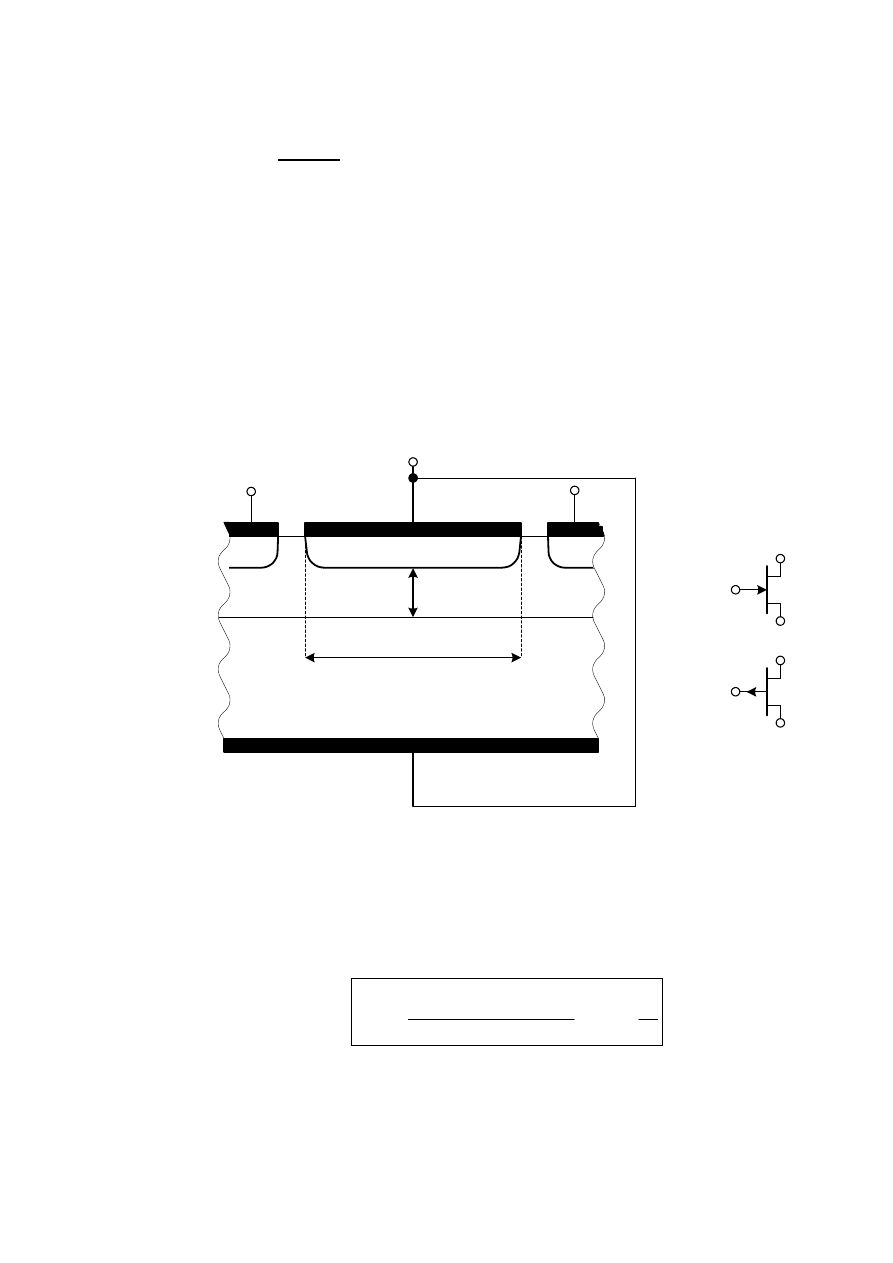

Szkic przekroju

JFET

z kanałem

n

oraz symbole

Rys. 5.16

•

Przy braku polaryzacji kanał jest przewodzący

•

Konduktywność kanału otwartego

(

)

0

u

GS

=

L

w

~

L

W

N

q

a

2

G

n

D

n

0

⋅

µ

µ

=

(5.19)

gdzie:

D

N

- koncentracja domieszki donorowej w kanale

n

µ

- ruchliwość elektronów

w

- szerokość kanału

+

n

+

n

+

p

L

a

2

n

+

p

S

G

D

S

G

D

„n”

S

G

D

„p”

(dolna bramka)

16

Stąd dla małej wartości

0

u

DS

→

DS

0

D

u

G

i

⋅

=

(5.20)

Charakterystyki statyczne

•

Podział na zakresy pracy i wzory opisujące podstawowe

charakterystyki

JFET

są w przybliżeniu takie jak dla

MOS

•

Charakterystyki przejściowe w zakresie nasycenia

(

)

(

)

2

p

GS

2

p

GS

DSS

GS

D

U

u

2

B

U

u

1

I

u

i

−

=

−

=

(5.21)

DSS

I

- nowy parametr (o innym wymiarze

!

)

=

DSS

I

prąd drenu płynący przy

0

u

GS

=

p

0

DSS

U

B

G

2

1

I

⋅

⋅

⋅

−

=

gdzie:

0

G

- konduktancja otwartego kanału

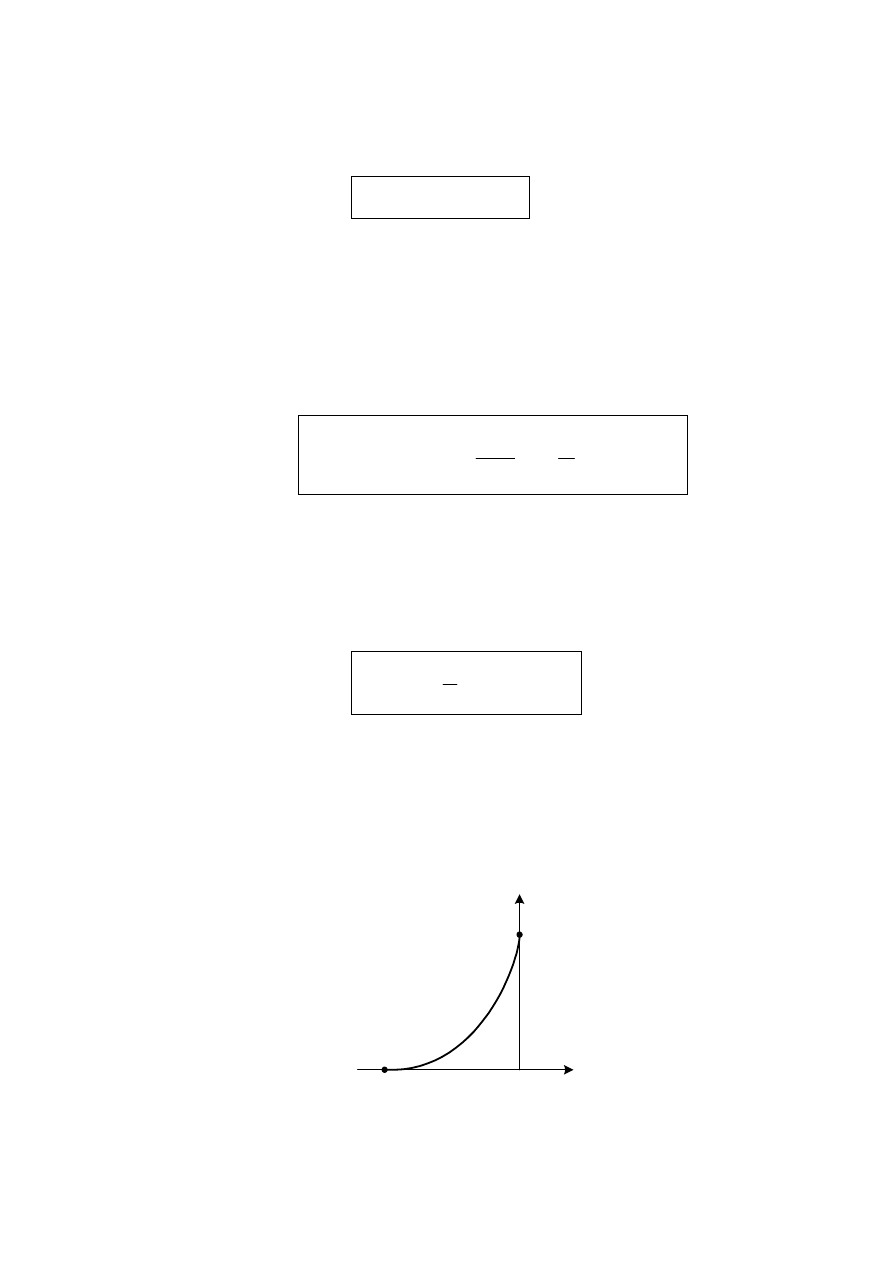

•

Typowa zależność

(

)

GS

D

u

i

pokazano na rys. 5.17

D

i

GS

u

p

U

−

DSS

I

Rys. 5.17

def.

17

•

Napięcie progowe

0

D

2

p

2

N

a

q

U

ε

⋅

ε

⋅

⋅

−

=

(5.21)

gdzie

a oznacza połowę szerokości kanału (mierzoną w głąb

struktury).

•

Charakterystyki wejściowe

Są inne niż dla tranzystorów

MOS. Charakterystyki

(

)

GS

G

u

i

JFET są analogiczne jak dla złącza p-n spolaryzowanego

zaporowo (prąd generacyjny) stąd

przebicie bramki JFET’a

⇒

przebicie lawinowe złącza p-n

typowo

→

G

i

rzędu nA

Inne uwagi

•

w

JFET’ach występuje efekt modulacji długości kanału

•

w

JFET’ach nie występuje efekt modulacji ruchliwości

nośników

•

model małosygnałowy ma postać identyczną jak dla tranzystora

MOS

!

18

Porównanie właściwości tranzystorów

bipolarnych i polowych

•

W tranzystorach polowych prąd związany jest z ruchem nośników

większościowych, natomiast w tranzystorach bipolarnych główną rolę w

przepływie prądu odgrywają nośniki mniejszościowe wprowadzone z

emitera do bazy i transportowane przez bazę do złącza kolektorowego.

•

Dla tej samej wartości prądu polaryzującego transkonduktancja (bo do niej

jest proporcjonalnie wzmocnienie napięciowe stopnia wzmacniającego na

pojedynczym tranzystorze) tranzystora bipolarnego jest do kilkuset razy

większa niż tranzystora polowego.

•

Rezystancja wejściowa tranzystorów polowych jest pięć do sześciu

rzędów większe niż dla tranzystorów bipolarnych.

•

Przeciętnie tranzystory bipolarne mają częstotliwości graniczne większe

niż przeciętne tranzystory polowe.

•

Istotne znaczenie ma zakres napięć, w których tranzystor jest elementem

aktywnym. Minimalnie napięcie na wyjściu tranzystora bipolarnego, przy

którym przechodzi on w obszar nasycenia wynosi od 100 do 200 mV. Dla

tranzystorów polowych przejście w obszar triodowy zachodzi dla napięć

rzędu kilku voltów.

Maksymalne napięcie wyjściowe związane jest ze zjawiskami przebicia i jest większe w tranzystorach bipolarnych.

Reasumując: w tranzystorach bipolarnych użyteczny zakres napięć

odpowiadający pracy w obszarze aktywnym jest zdecydowanie większy.

•

Tranzystory polowe wnoszą mniejsze zniekształcenia sygnałów

harmonicznych. Dotyczy to głównie zniekształcenia trzeciego rzędu, gdyż

charakterystyki tranzystorów polowych są bardzo zbliżone do zależności

kwadratowej.

•

Przełącznik typu

CMOS zapewnia znacznie mniejszy pobór mocy w

stanach ustalonych aniżeli przełącznik na tranzystorze bipolarnym.

Natomiast szybkość działania przełącznika bipolarnego jest nieco większa

niż przełącznika polowego.

19

MOSFET

Rozważa się tranzystory z kanałem n (n-MOS)

tzn. podłoże jest typu p

MOS -

kanał indukowany

-

normalnie wyłączony

-

pracujący ze wzbogacaniem

D

S

G V

G

= 0

m

1

L

µ

<

+

n

+

n

p

B

D

S

V

G

> 0

+

n

+

n

p

B

D

i

kanał

(stan inwersji)

2

0

Si

(substrate)

2

0

Si

S

G

D

B

symbol

MOS -

kanał wbudowany

-

normalnie załączony

-

pracujący ze zubożaniem

D

S

G

+

n

+

n

p

B

D

i

kanał

D

S

V

G

< 0

+

n

+

n

p

B

S

B

G

D

symbol

D

i

(

)

( )

BS

p

BS

p

u

A

0

U

u

U

⋅

+

=

(5.4)

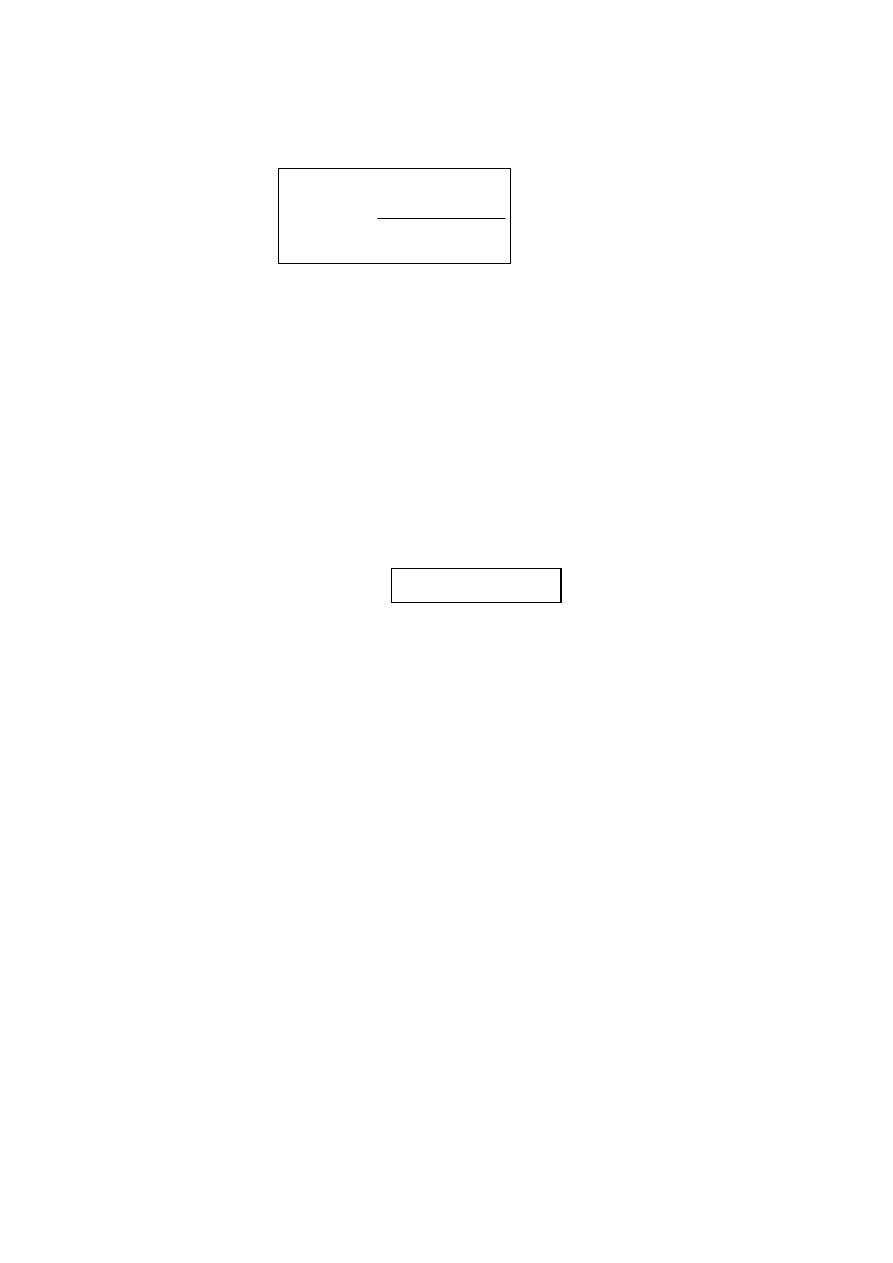

Taka sytuacja ma miejsce w układach scalonych

EMOS

DMOS

Rys. 5.4

Rys. 5.5

!

20

Wyszukiwarka

Podobne podstrony:

odejmowanie do 10 5

BIAŁKA DO 10, Studia, 1-stopień, inżynierka, Ochrona Środowiska, Od Agaty

Akumulator do JCB?strac?strac

dodawanie do 10 4

dodawanie do 10 4 id 138940 Nieznany

5 Tranzystory polowe

Liczby od 1 do 10 kolorowanka (eng)

odejmowanie do 10 14

ROK V pytania do lektury ST

RACHUNKOWO BANKOWA 10 ST, Inne

ELEKTORNIKA TRANZYSTORY POLOWE

TRANZYSTORY POLOWE

dodawanie do 10 3 id 138939 Nieznany

dodawanie do 10 11

więcej podobnych podstron