PODSTAWY ARCHITEKTURY KOMPUTERA

PODSTAWY ARCHITEKTURY KOMPUTERA

dr inż. Jacek FLOREK

dr inż. Jacek FLOREK

Instytut Informatyki

Instytut Informatyki

Specjalizowany układ cyfrowy a maszyna

Specjalizowany układ cyfrowy a maszyna

cyfrowa

cyfrowa

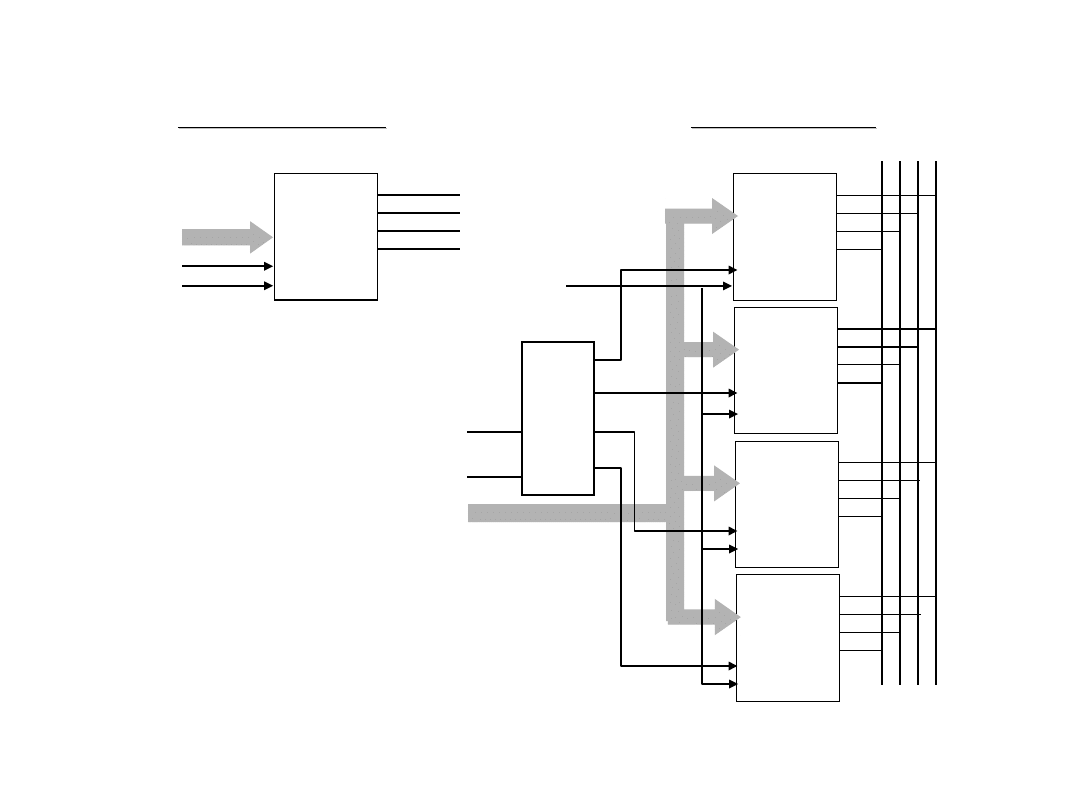

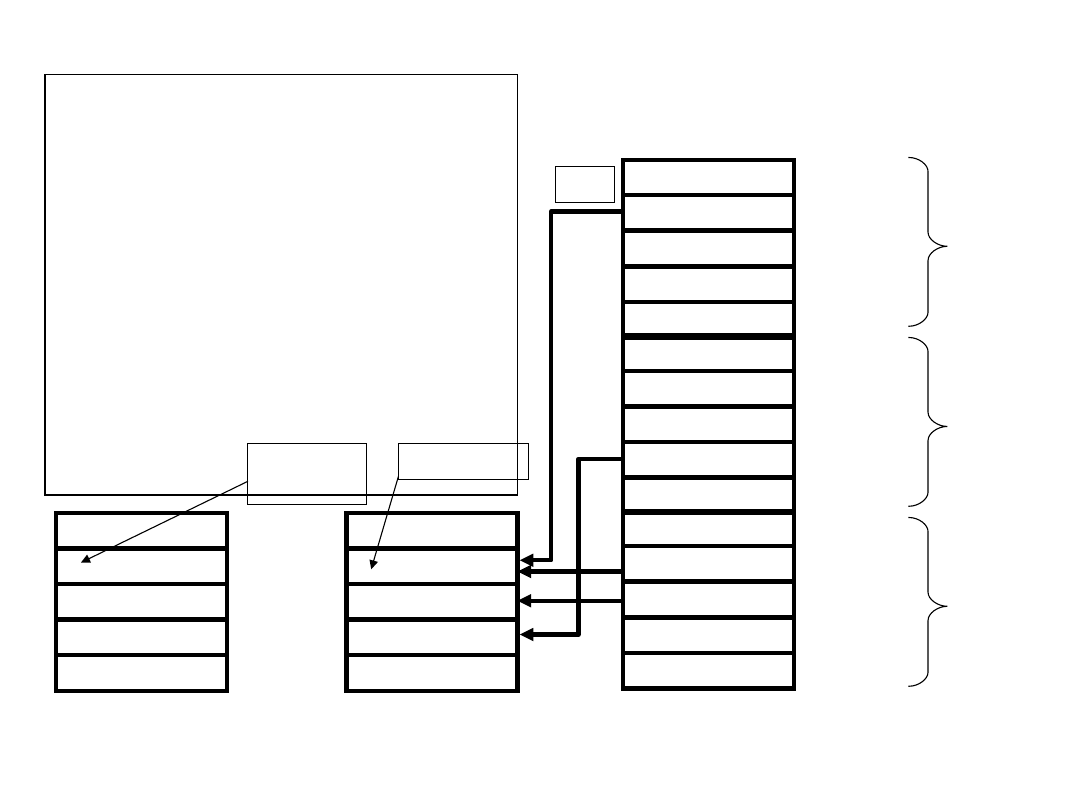

Struktura systemu mikroprocesorowego

Struktura systemu mikroprocesorowego

Bloki funkcjonalne - organizacja i

Bloki funkcjonalne - organizacja i

architektura

architektura

7

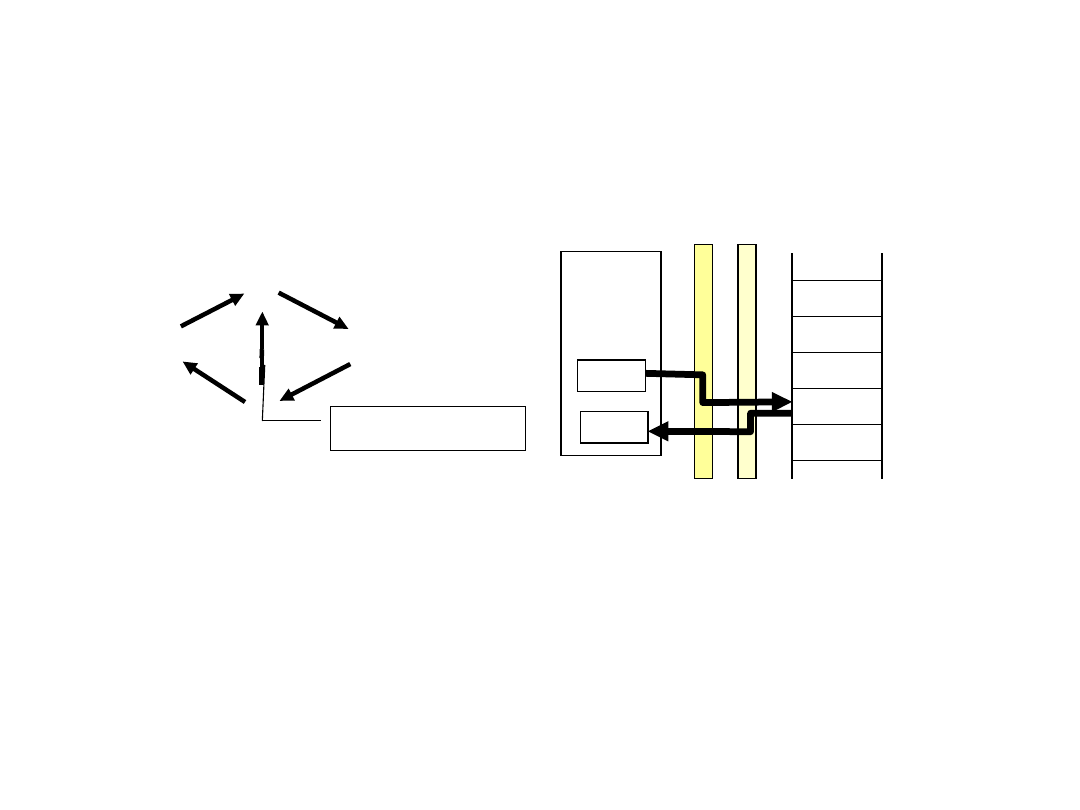

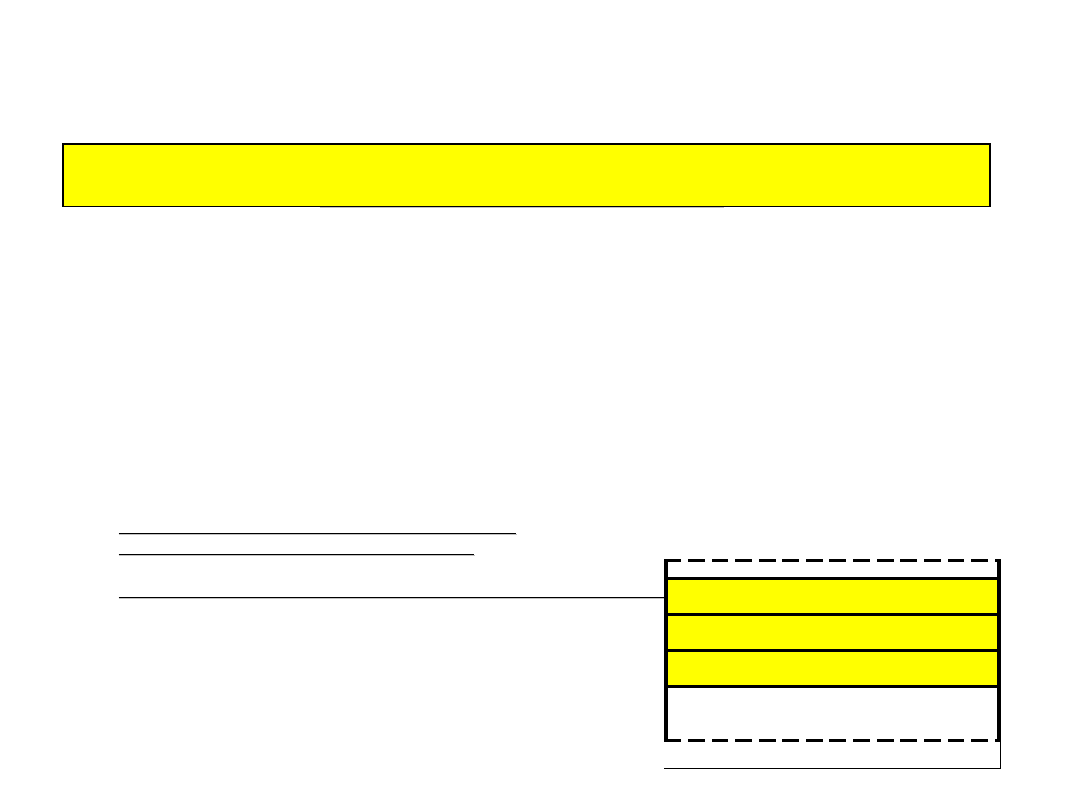

PRZETWARZANIE

PRZETWARZANIE

INFORMACJI

INFORMACJI

Wszelkie procesy zamierzonego przetwarzania informacji

Wszelkie procesy zamierzonego przetwarzania informacji

przebiegają według ustalonego algorytmu

przebiegają według ustalonego algorytmu

DANE

DANE

POCZĄTKOW

POCZĄTKOW

E

E

WYNIKI

WYNIKI

KOŃCOWE

KOŃCOWE

PROCES

PROCES

PRZETWARZANI

PRZETWARZANI

A

A

ALGORYTM

ALGORYTM

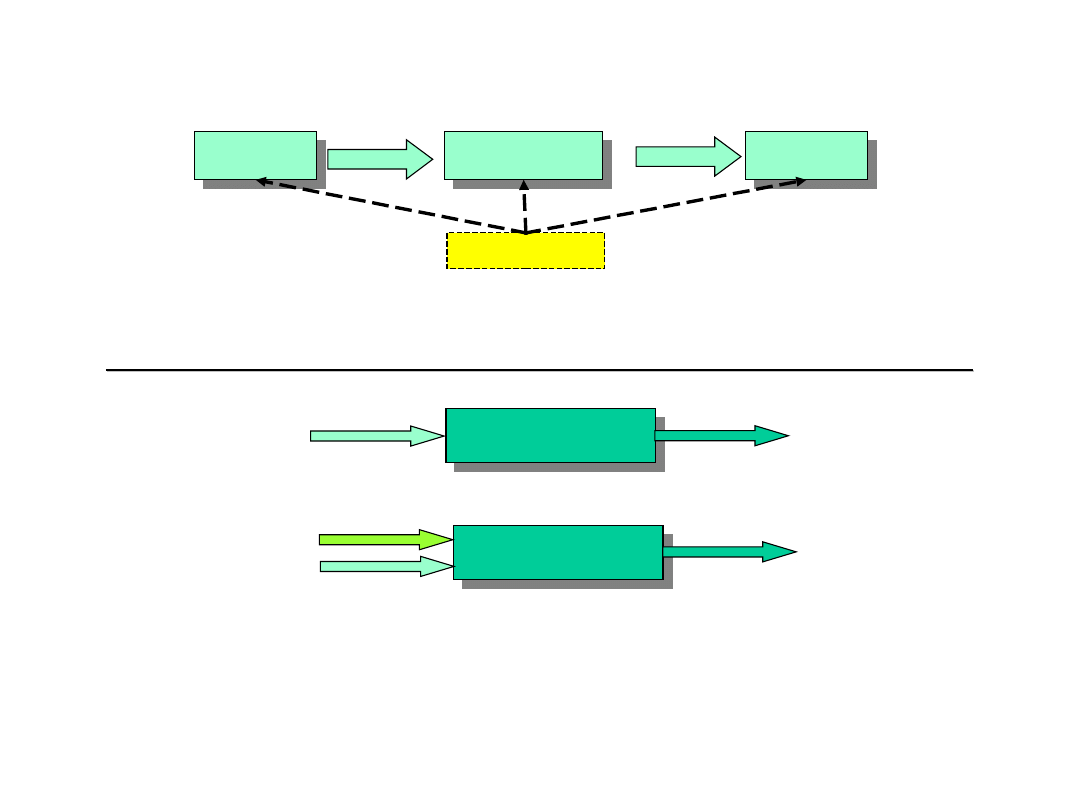

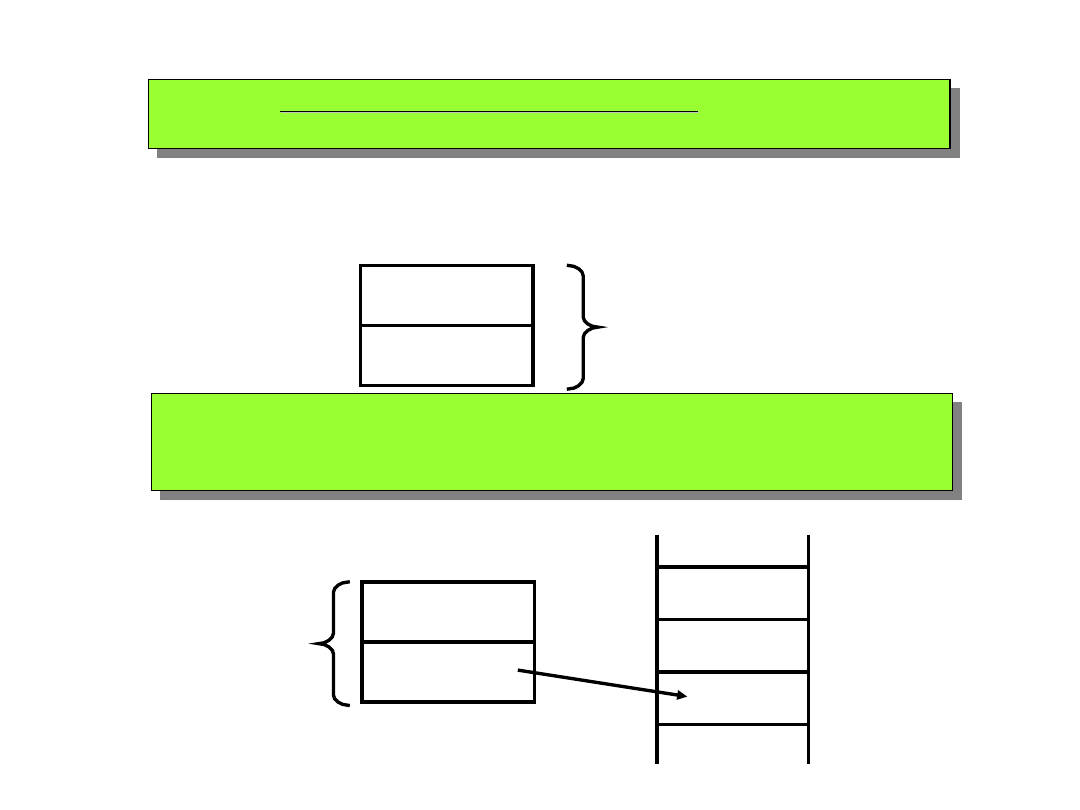

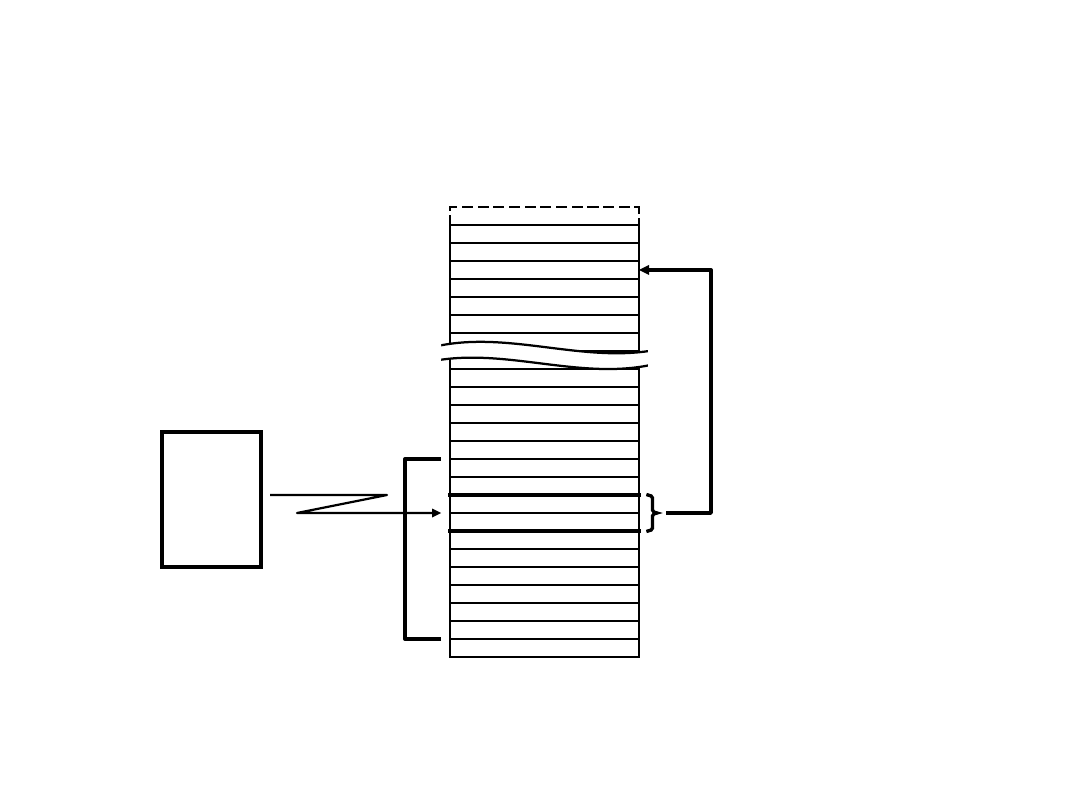

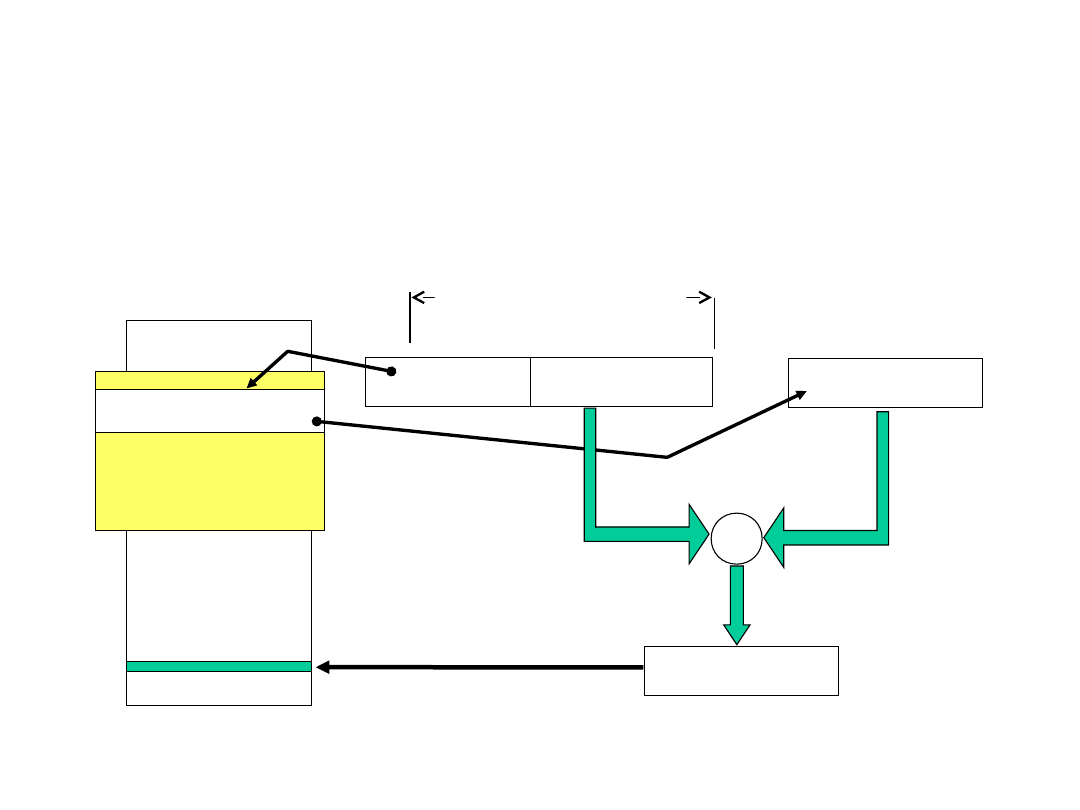

Przetwarzanie informacji można zrealizować dwoma sposobami:

Przetwarzanie informacji można zrealizować dwoma sposobami:

•

Specjalizowany układ cyfrowy:

Specjalizowany układ cyfrowy:

•

System mikroprocesorowy (maszyna cyfrowa):

System mikroprocesorowy (maszyna cyfrowa):

SPECJALIZOWANY

SPECJALIZOWANY

UKŁAD CYFROWY

UKŁAD CYFROWY

MASZYNA

MASZYNA

CYFROWA

CYFROWA

WYNIKI

WYNIKI

PROGRAM

PROGRAM

DANE

DANE

DANE

DANE

WYNIKI

WYNIKI

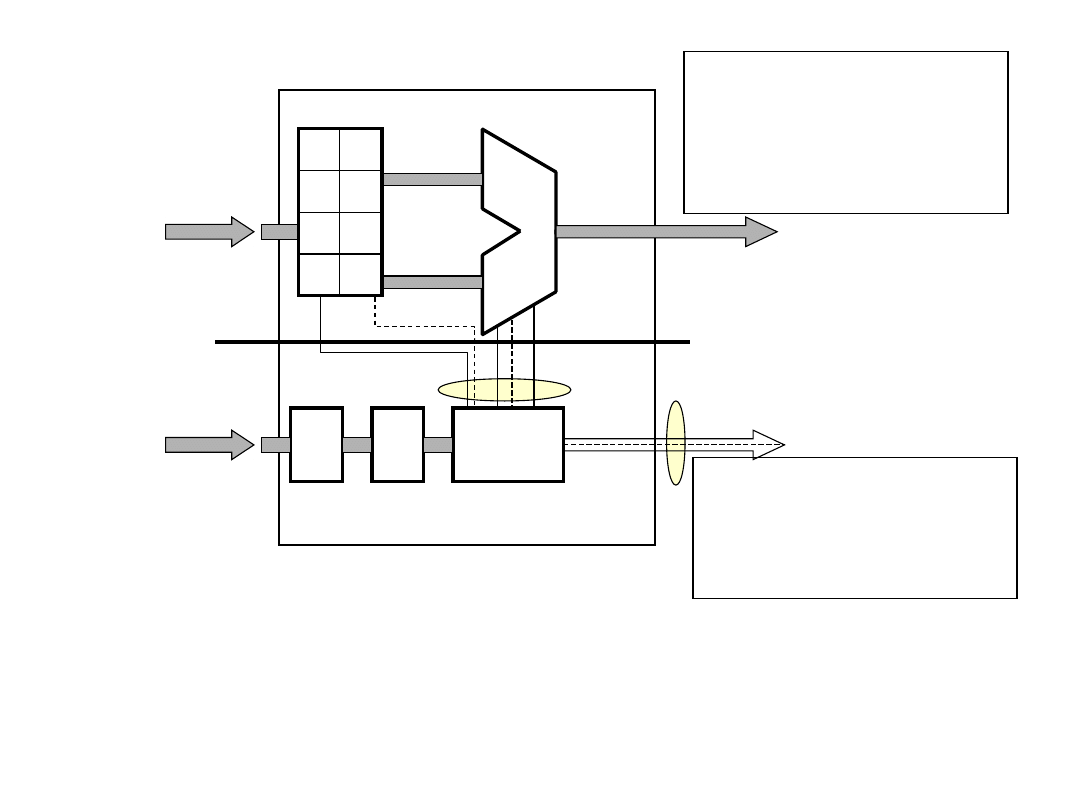

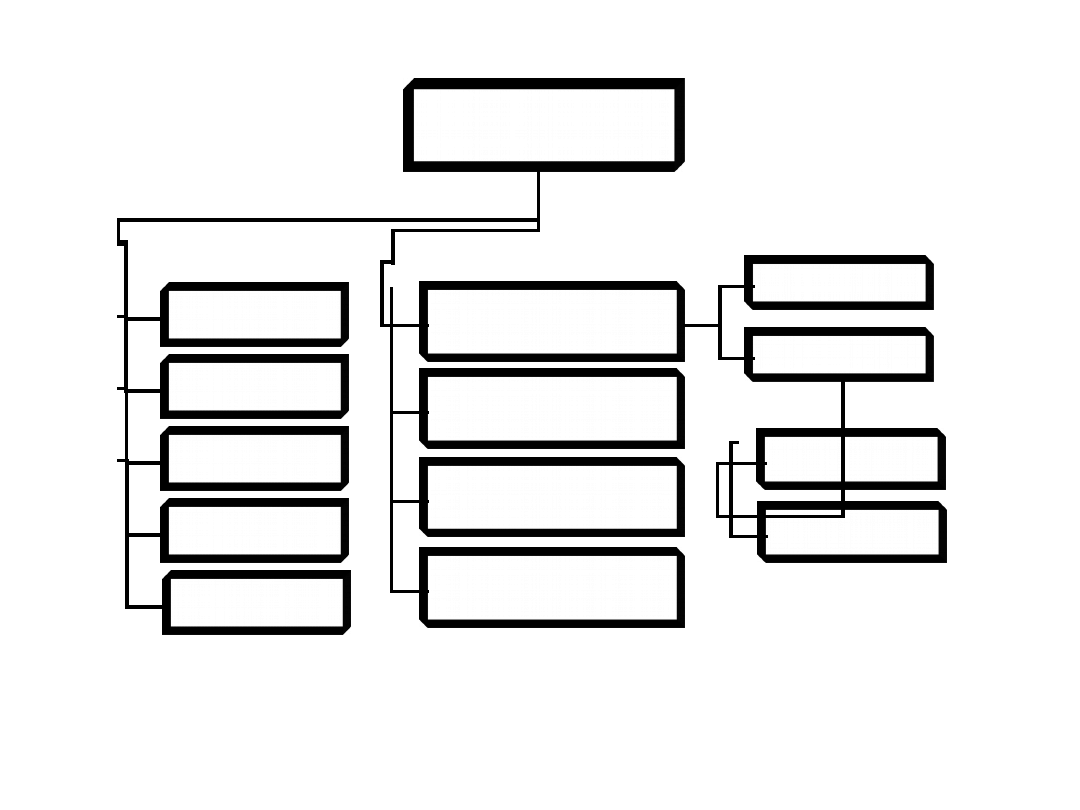

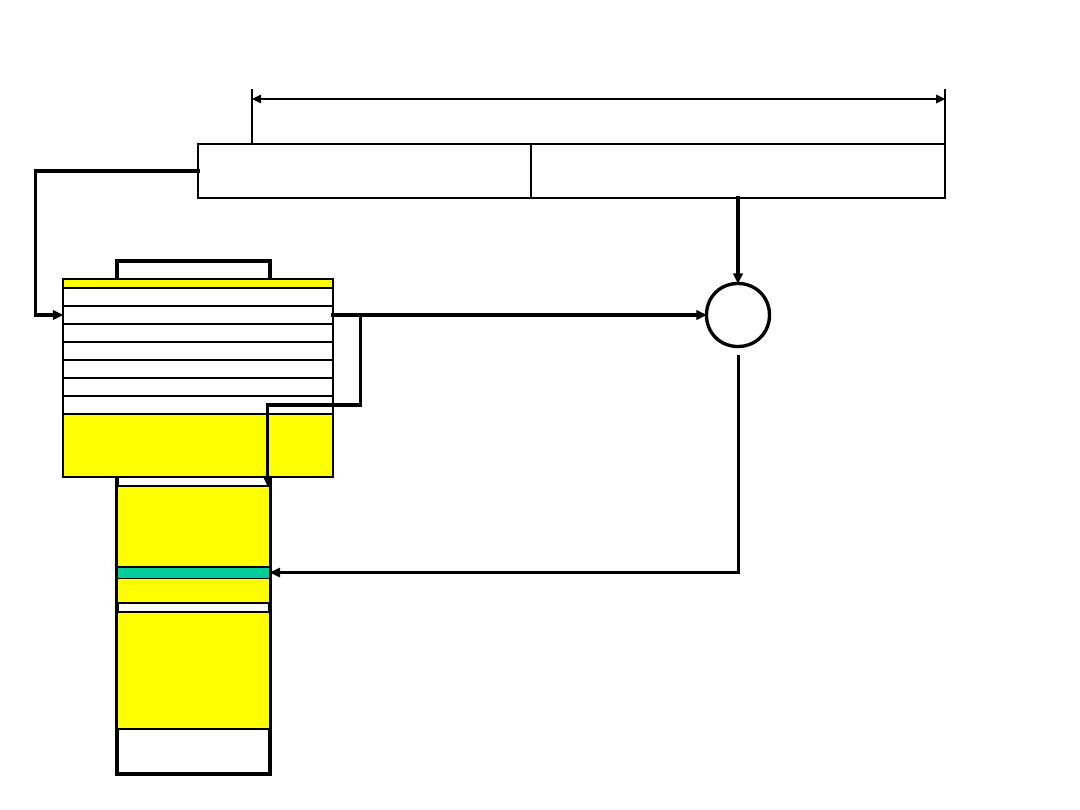

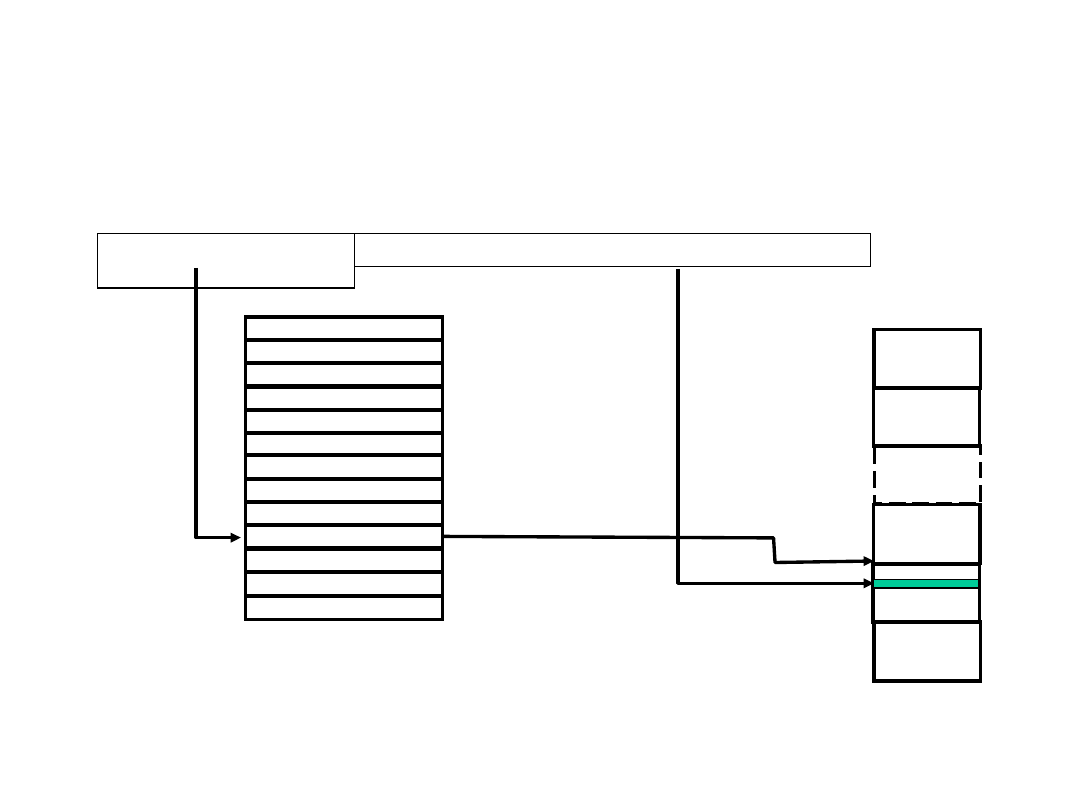

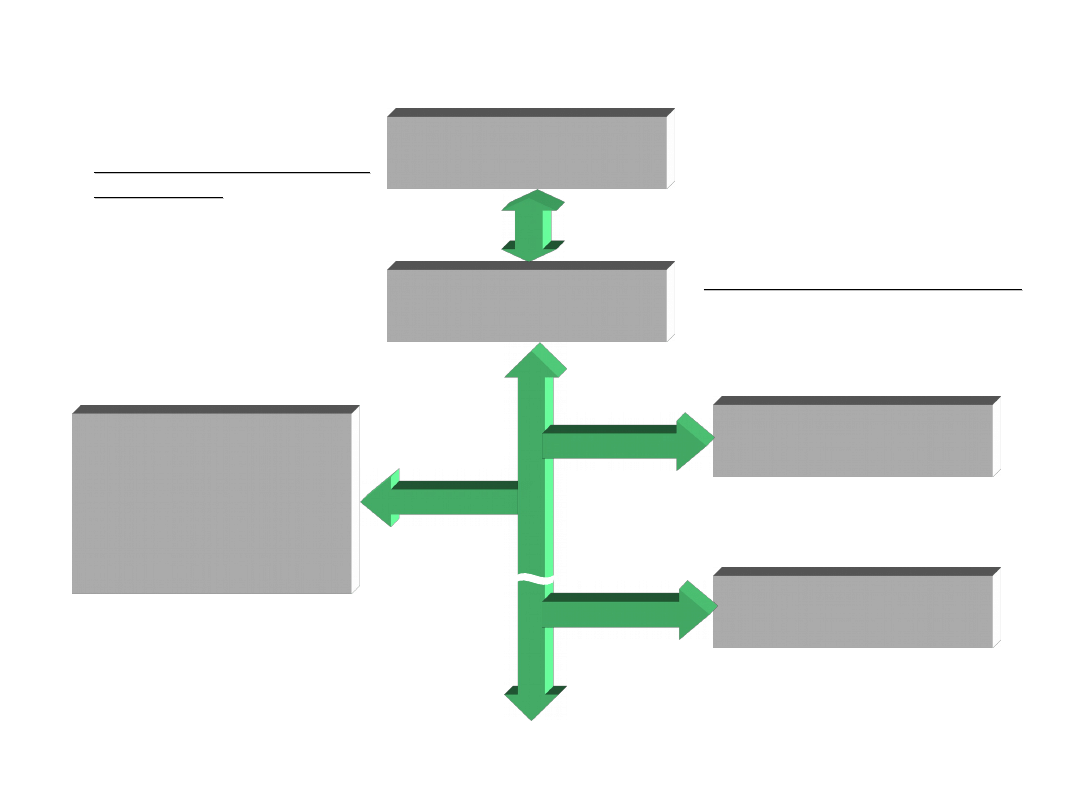

ARCHITEKTURA MASZYNY CYFROWEJ

ARCHITEKTURA MASZYNY CYFROWEJ

PAMIĘĆ

PAMIĘĆ

ZEWNĘTRZNA

ZEWNĘTRZNA

UKŁADY WY

UKŁADY WY

URZĄDZENIA

URZĄDZENIA

ZEWNĘTRZNE

ZEWNĘTRZNE

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

BLOK

BLOK

PRZETWA-

PRZETWA-

RZANIA

RZANIA

STEROWANIE

STEROWANIE

UKŁADY WE

UKŁADY WE

URZĄDZENIA

URZĄDZENIA

ZEWNĘTRZNE

ZEWNĘTRZNE

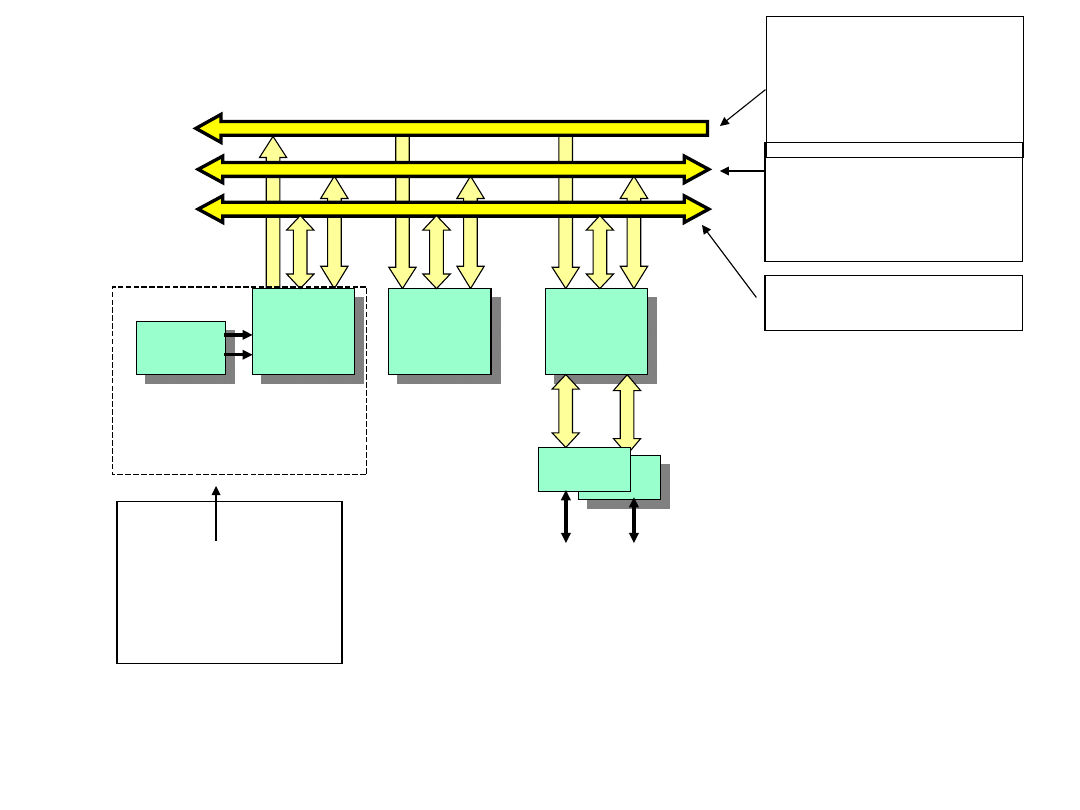

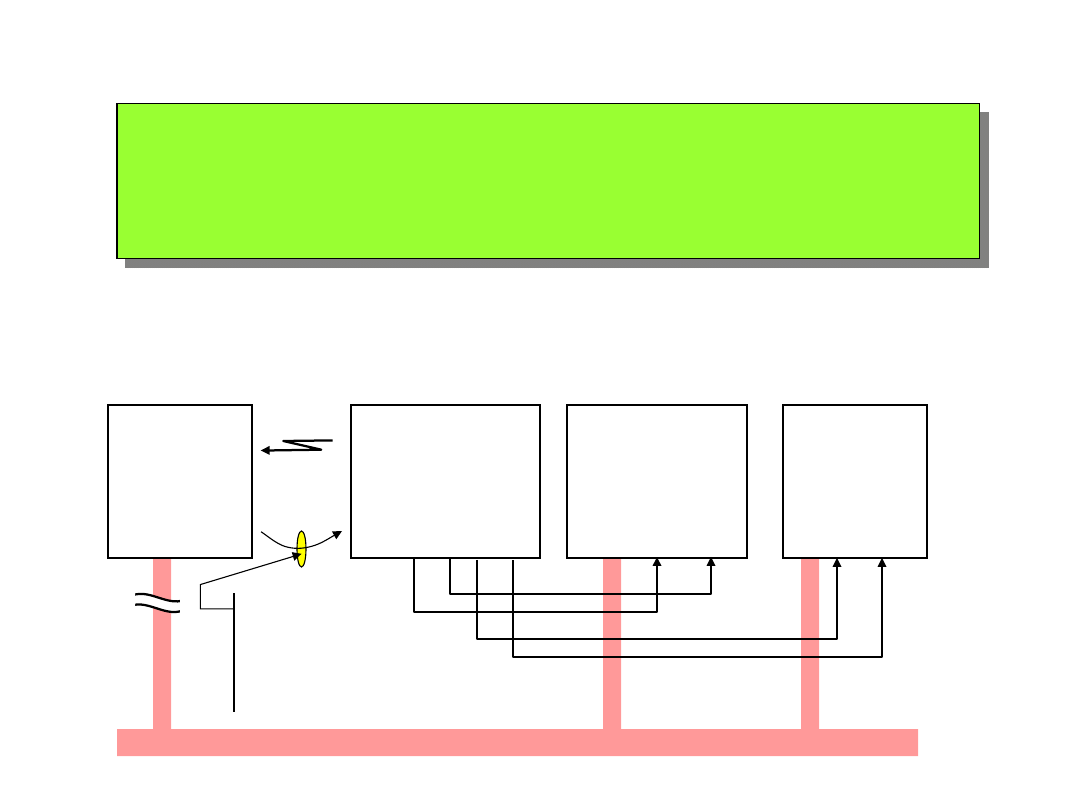

MASZYNA CYFROWA

MASZYNA CYFROWA

PROCESOR

PROCESOR

JEDNOSTKA CENTRALNA

JEDNOSTKA CENTRALNA

W

Y

N

IK

I

W

Y

N

IK

I

P

R

O

G

R

A

M

P

R

O

G

R

A

M

D

A

N

E

D

A

N

E

...

...

URZ.

URZ.

ZEWN.

ZEWN.

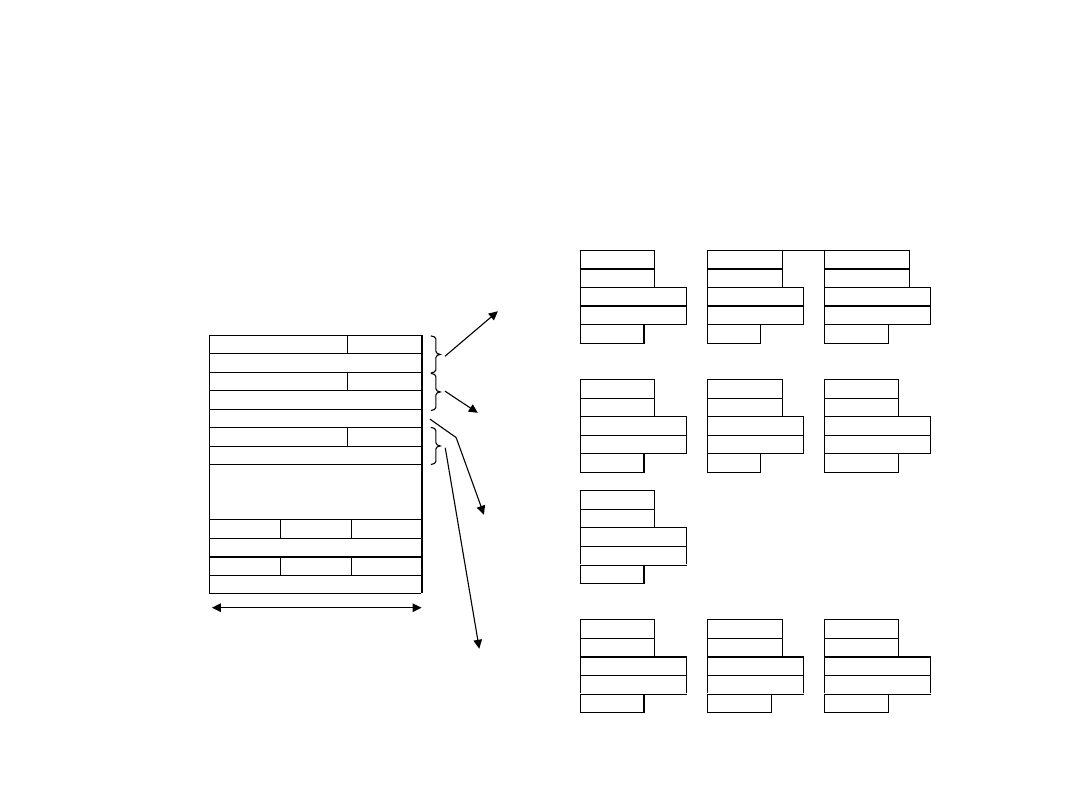

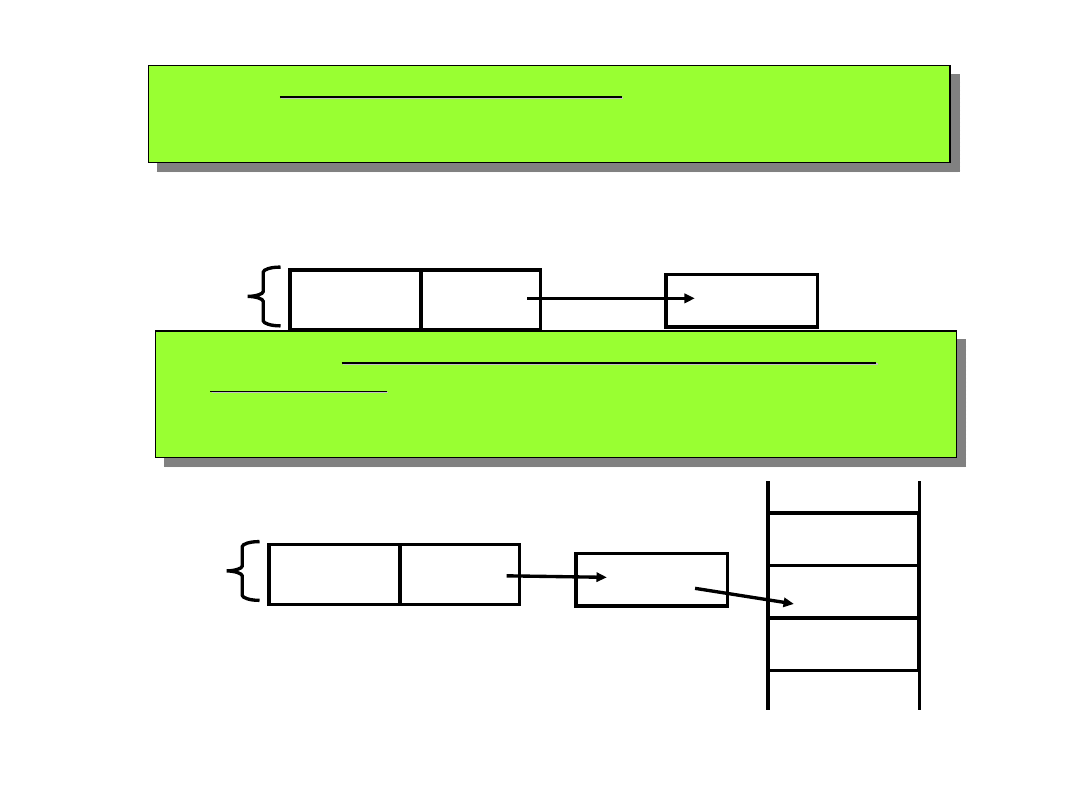

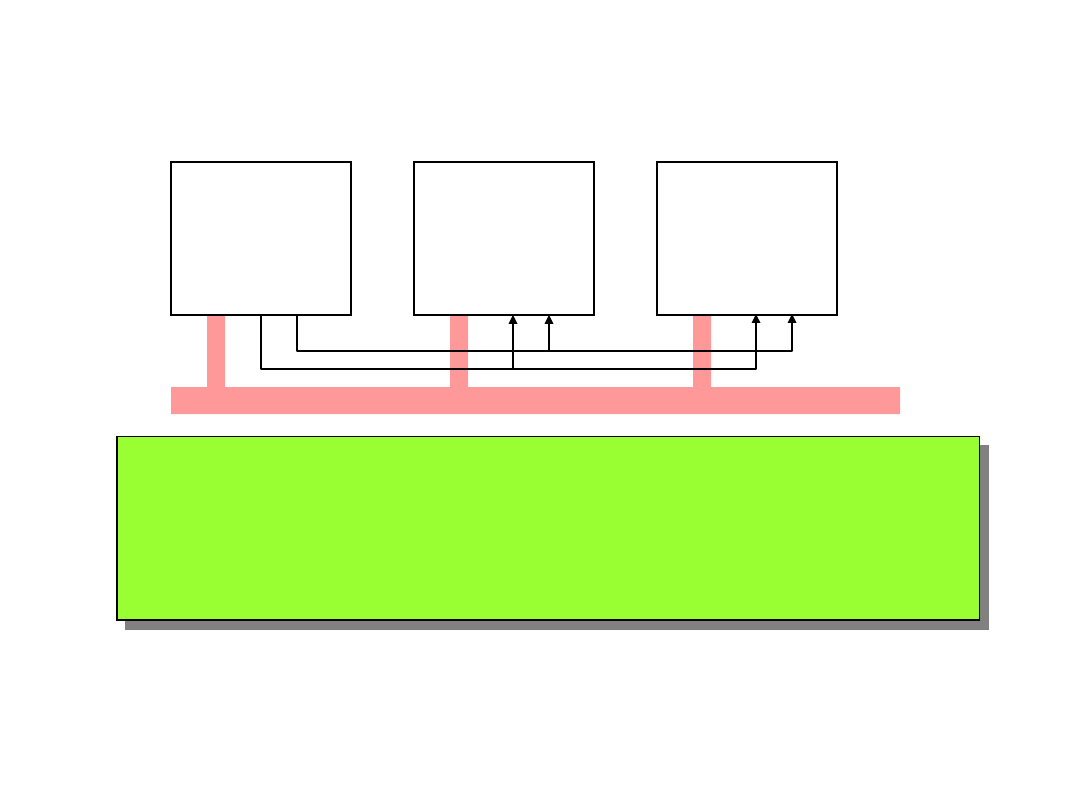

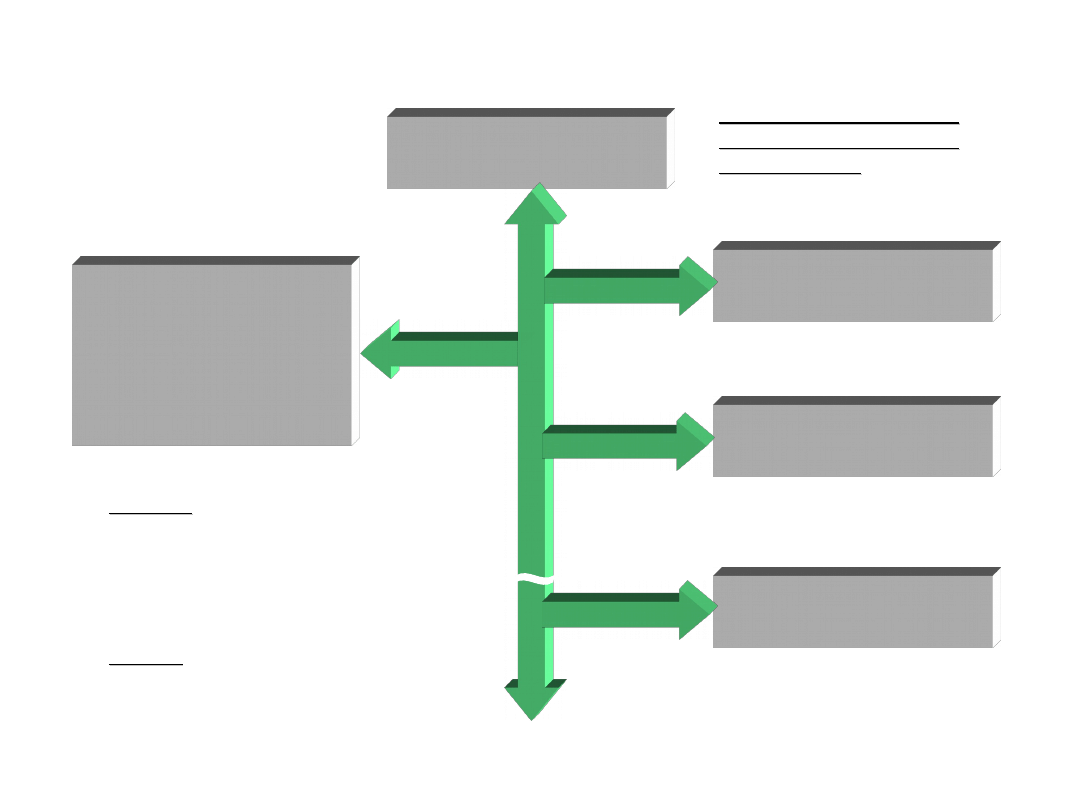

PROCESOR

PROCESOR

PAMIĘC

PAMIĘC

UKŁADY

UKŁADY

WE/WY

WE/WY

ZEGAR

ZEGAR

SZYNA DANYCH

SZYNA DANYCH

SZYNA ADRESOWA

SZYNA ADRESOWA

SZYNA STEROWANIA

SZYNA STEROWANIA

UŻYTKOWNIK

UŻYTKOWNIK

DANE

DANE

PROGRAMY

PROGRAMY

WYNIKI

WYNIKI

MONITORY, DRUKARKI,

MONITORY, DRUKARKI,

CZYTNIKI,...

CZYTNIKI,...

SYSTEM MIKROPROCESOROWY

SYSTEM MIKROPROCESOROWY

Centralna jednostka

Centralna jednostka

przetwarzająca (CPU)

przetwarzająca (CPU)

Liczba linii wyznacza

Liczba linii wyznacza

możliwości

możliwości

adresowania np. liczba

adresowania np. liczba

linii 20 to można

linii 20 to można

zaadresować 2

zaadresować 2

20

20

komórek

komórek

Liczba linii określa

Liczba linii określa

długość słowa

długość słowa

procesora (8, 16,

procesora (8, 16,

32, .... (+biyt detekcji i

32, .... (+biyt detekcji i

korekcji błędów

korekcji błędów

)

)

Kilkanaście

Kilkanaście

(kilkadziesiąt) linii

(kilkadziesiąt) linii

Uniwersalny układ

Uniwersalny układ

przetwarzający

przetwarzający

informację i

informację i

sterujący pracą

sterujący pracą

pozostałych

pozostałych

elementów

elementów

systemu

systemu

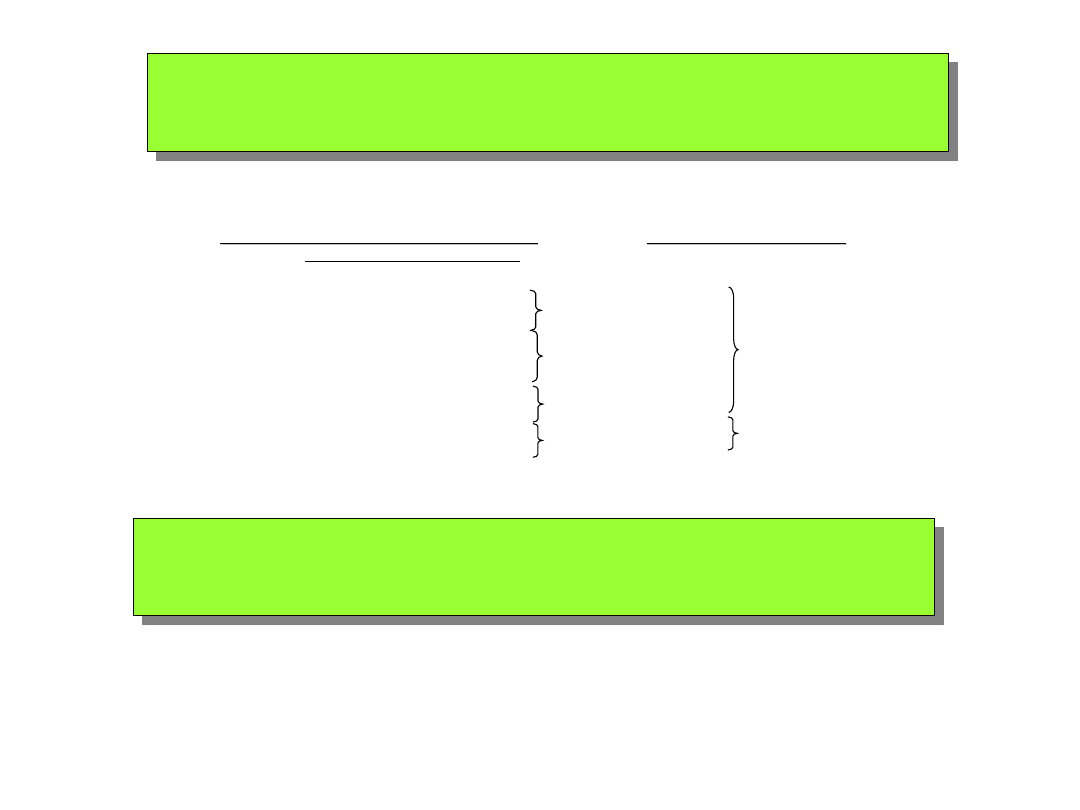

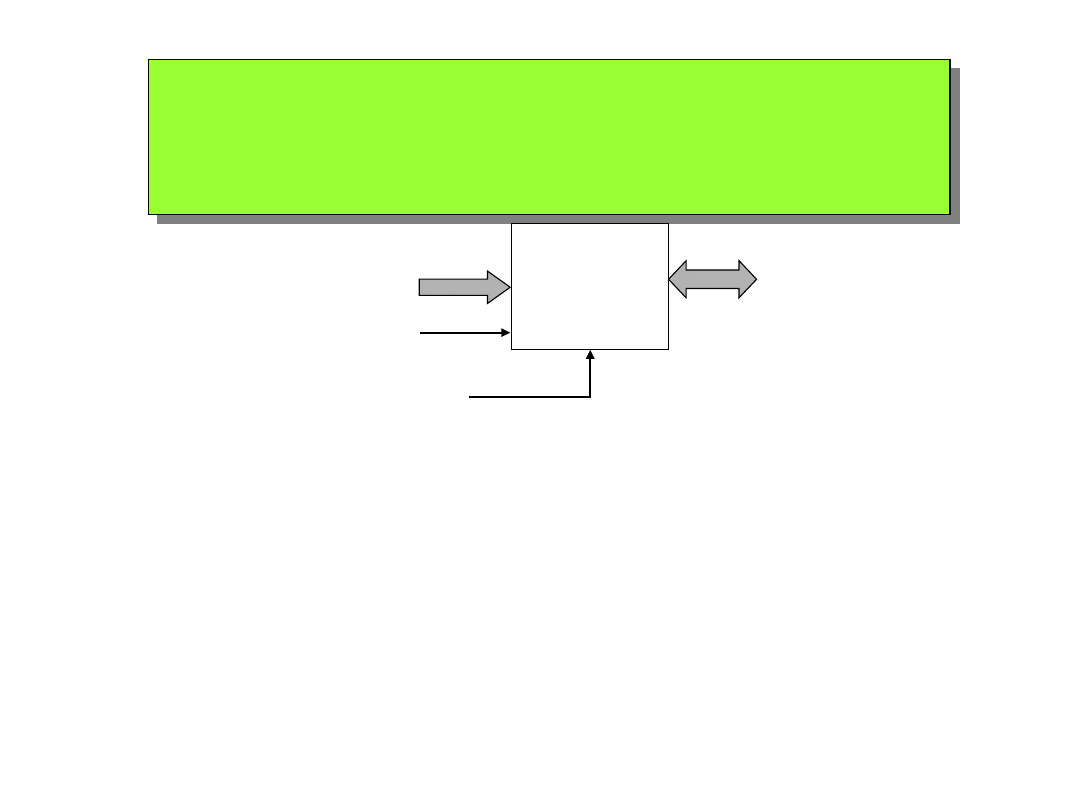

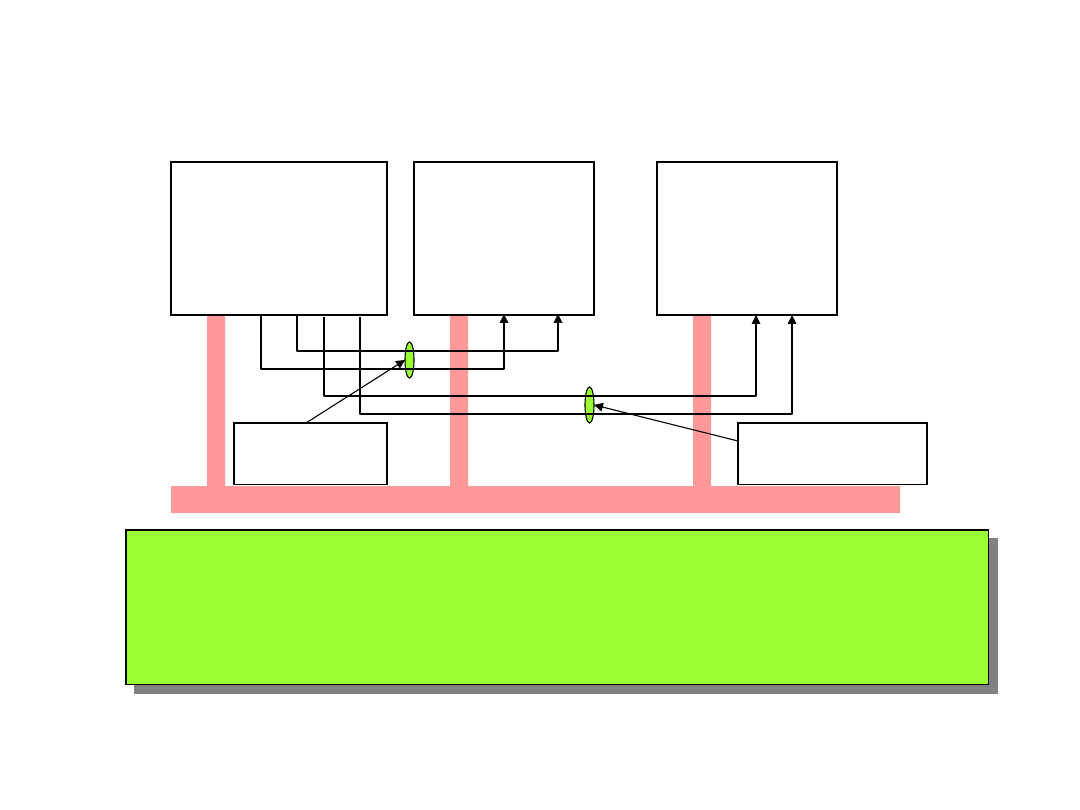

ORGANIZACJA SYSTEMU

ORGANIZACJA SYSTEMU

»

Architektura klasycznego komputera (wg von Neumana)

Architektura klasycznego komputera (wg von Neumana)

opiera się na założeniach:

opiera się na założeniach:

–

program wykonywany przez procesor wraz z danymi

program wykonywany przez procesor wraz z danymi

jest umieszczony w pamięci;

jest umieszczony w pamięci;

–

kolejność wykonywanych rozkazów zależy od ich

kolejność wykonywanych rozkazów zależy od ich

umieszczenia w programie (w kolejnych komórkach

umieszczenia w programie (w kolejnych komórkach

pamięci), a zmiana tej zasady może być wykonana

pamięci), a zmiana tej zasady może być wykonana

tylko:

tylko:

•

przez program (rozkaz skoku);

przez program (rozkaz skoku);

•

przez system operacyjny np. wykrycie błędu;

przez system operacyjny np. wykrycie błędu;

•

przez operatora np.

przez operatora np.

reset

reset

–

procesor odczytuje kolejne rozkazy z pamięci

procesor odczytuje kolejne rozkazy z pamięci

wysyłając odpowiednie adresy

wysyłając odpowiednie adresy

»

Każde działanie wykonywane przez system jest wynikiem

Każde działanie wykonywane przez system jest wynikiem

realizacji określonego programu bądź jego fragmentu

realizacji określonego programu bądź jego fragmentu

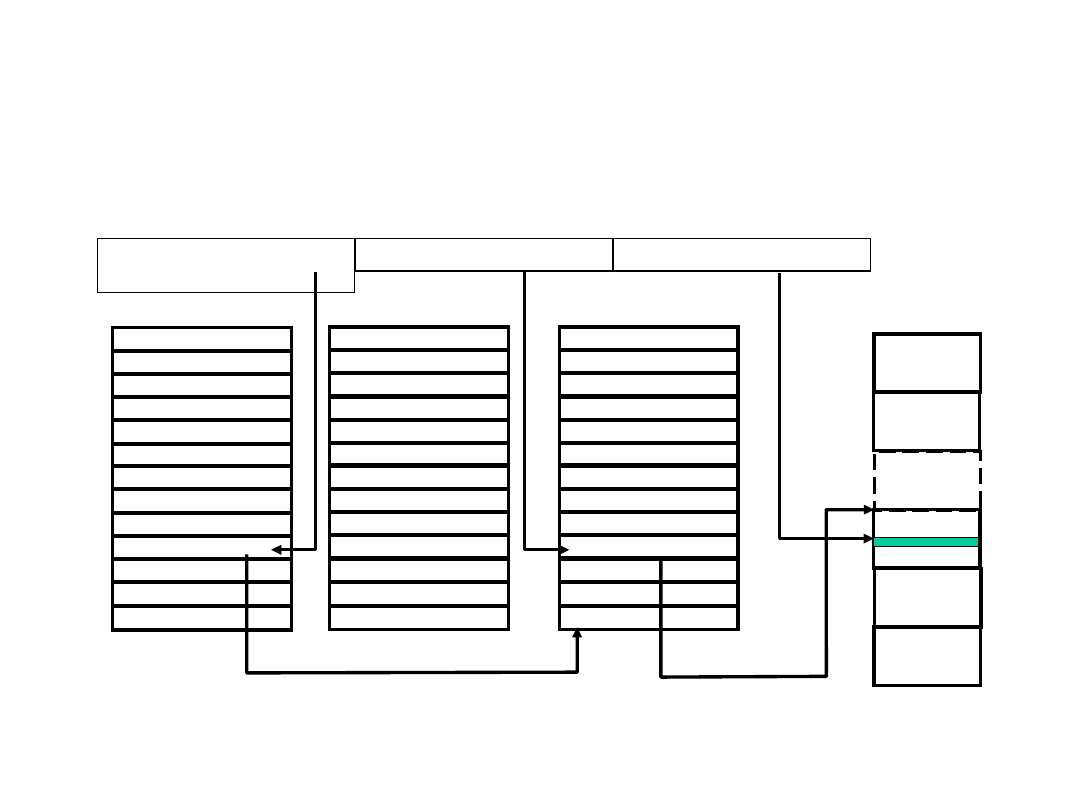

PROCESOR

PROCESOR

PAMIĘĆ

PAMIĘĆ

Adres

Adres

Dane

Dane

Zapis

Zapis

1

1

2

2

3

3

3

3

4

4

PROCESOR

PROCESOR

PAMIĘĆ

PAMIĘĆ

Adres

Adres

Dane

Dane

Odczyt

Odczyt

1

1

2

2

3

3

4

4

PROCESOR

PROCESOR

UKŁAD

UKŁAD

WY-WE

WY-WE

Adres

Adres

Dane

Dane

Zapis

Zapis

1

1

2

2

3

3

4

4

PROCESOR

PROCESOR

UKŁAD

UKŁAD

WY-WE

WY-WE

Adres

Adres

Dane

Dane

Odczyt

Odczyt

1

1

2

2

3

3

4

4

Z

P

R

O

C

E

S

O

R

A

D

O

P

A

M

IĘ

C

I

Z

P

R

O

C

E

S

O

R

A

D

O

P

A

M

IĘ

C

I

Z

P

A

M

IĘ

C

I

D

O

P

R

O

C

E

S

O

R

A

Z

P

A

M

IĘ

C

I

D

O

P

R

O

C

E

S

O

R

A

Z

P

R

O

C

E

S

O

R

A

N

A

W

Y

JŚ

C

IE

Z

P

R

O

C

E

S

O

R

A

N

A

W

Y

JŚ

C

IE

Z

W

E

JŚ

C

IA

D

O

P

R

O

C

E

S

O

R

A

Z

W

E

JŚ

C

IA

D

O

P

R

O

C

E

S

O

R

A

PRZEPŁYW DANYCH W SYSTEMIE

PRZEPŁYW DANYCH W SYSTEMIE

MIKROPROCESOROWYM

MIKROPROCESOROWYM

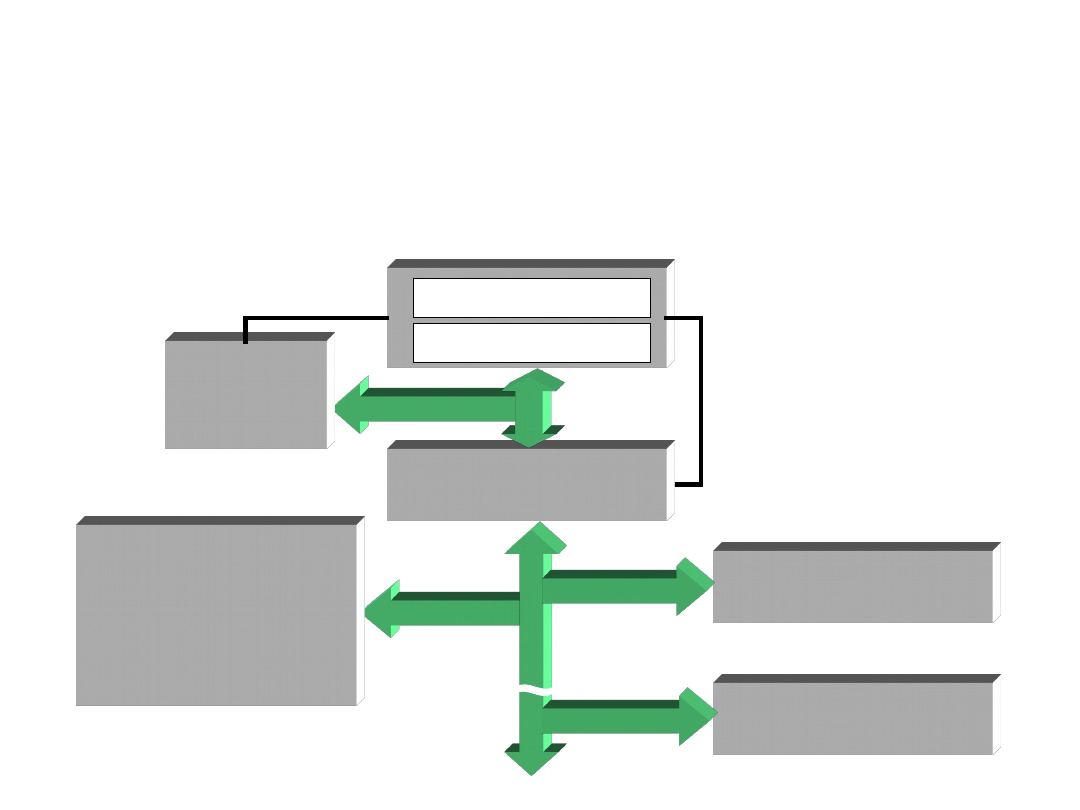

ARCHITEKTURA PROCESORA

ARCHITEKTURA PROCESORA

dr inż. Jacek FLOREK

dr inż. Jacek FLOREK

Instytut Informatyki

Instytut Informatyki

Schemat blokowy procesora

Schemat blokowy procesora

Rejestry

Rejestry

Blok arytmetyczno-logiczny (ALU)

Blok arytmetyczno-logiczny (ALU)

Układ sterowania

Układ sterowania

8

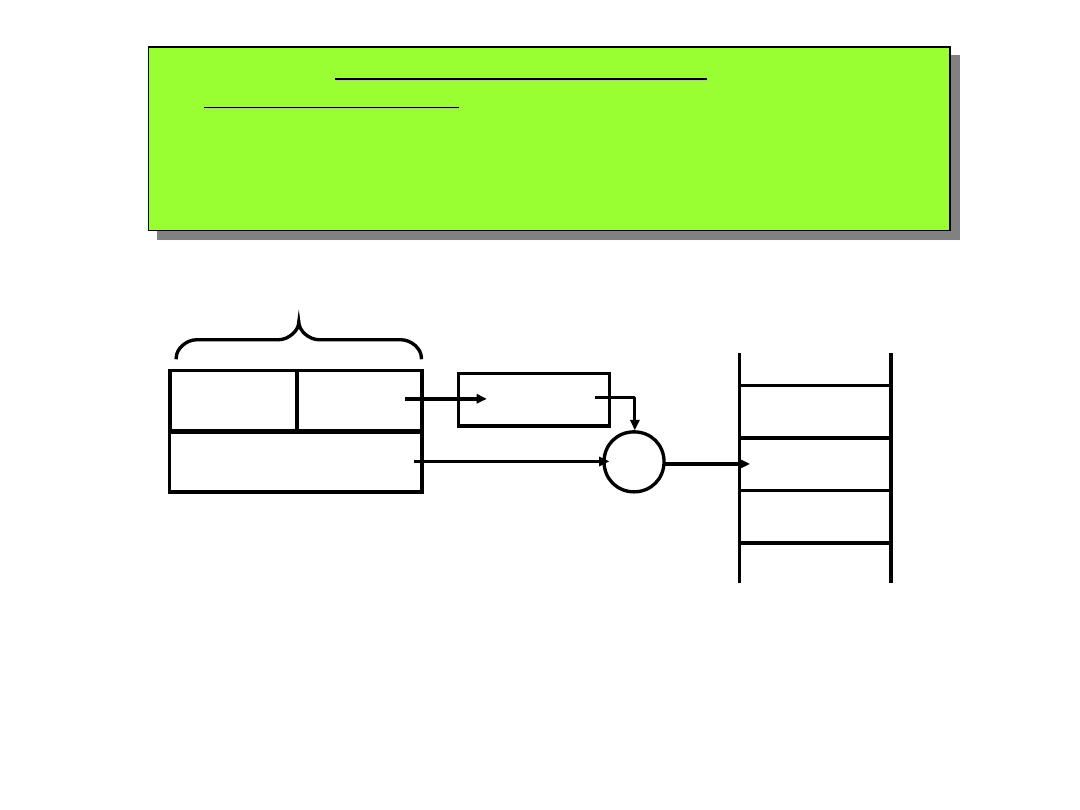

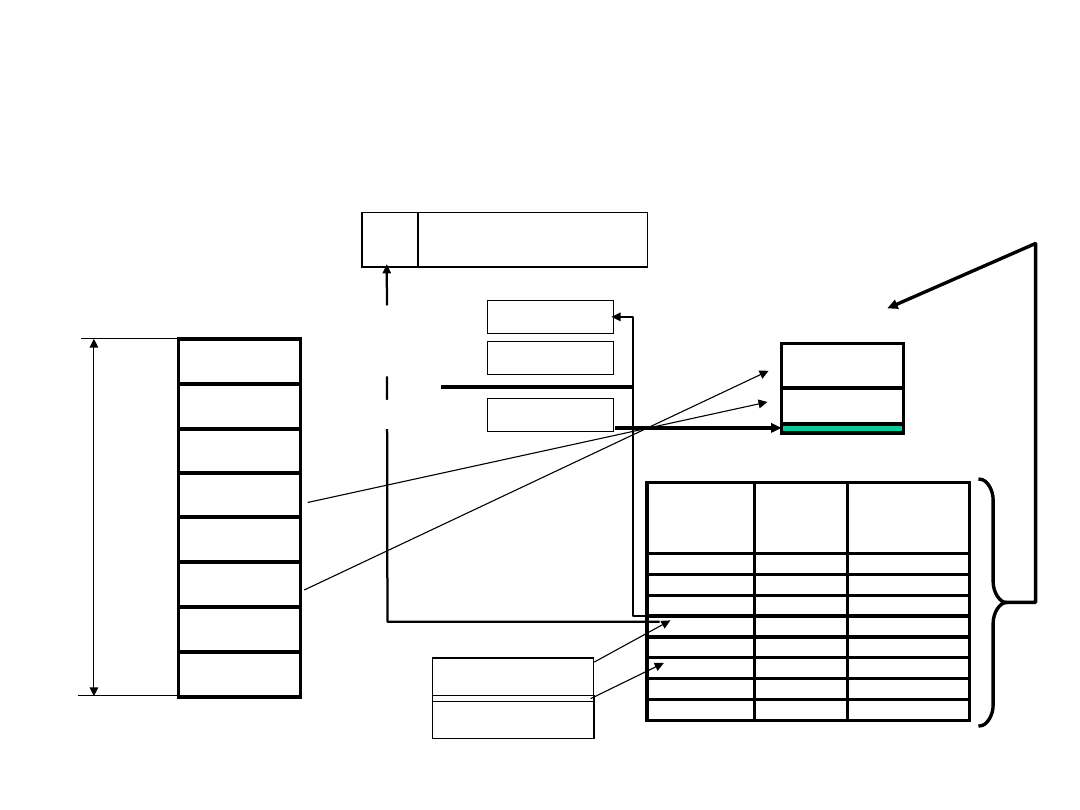

SCHEMAT BLOKOWY PROCESORA

SCHEMAT BLOKOWY PROCESORA

ALU

ALU

JEDNOSTKA

JEDNOSTKA

WYKONAWCZA

WYKONAWCZA

układ

układ

sterowania

sterowania

d

e

k

o

d

e

r

d

e

k

o

d

e

r

ro

zk

a

zó

w

ro

zk

a

zó

w

re

je

s

tr

re

je

s

tr

ro

zk

a

zó

w

ro

zk

a

zó

w

rejestry części

rejestry części

wykonawczej

wykonawczej

DANE

DANE

PROGRAM

PROGRAM

WYNIKI

WYNIKI

wewnętrzne

wewnętrzne

sygnały

sygnały

sterujące

sterujące

zewnętrzne

zewnętrzne

sygnały

sygnały

sterujące

sterujące

JEDNOSTKA

JEDNOSTKA

STERUJĄCA

STERUJĄCA

Zadaniem jednostki

Zadaniem jednostki

wykonawczej jest

wykonawczej jest

wykonywanie operacji

wykonywanie operacji

arytmetycznych i logicznych

arytmetycznych i logicznych

w zależności od

w zależności od

wewnętrznych sygnałów

wewnętrznych sygnałów

sterujących

sterujących

Jednostka sterująca z

Jednostka sterująca z

programu dekoduje rozkaz i

programu dekoduje rozkaz i

na jego podstawie

na jego podstawie

generowane są wewnętrzne i

generowane są wewnętrzne i

zewnętrzne sygnały sterujące

zewnętrzne sygnały sterujące

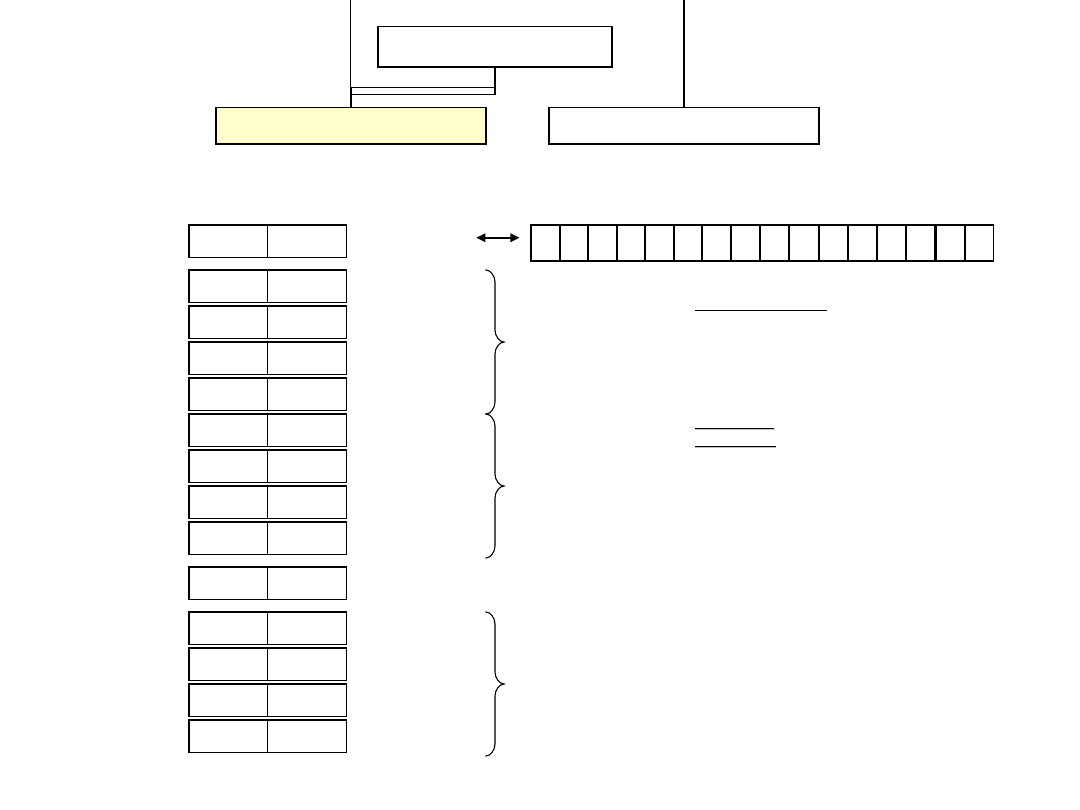

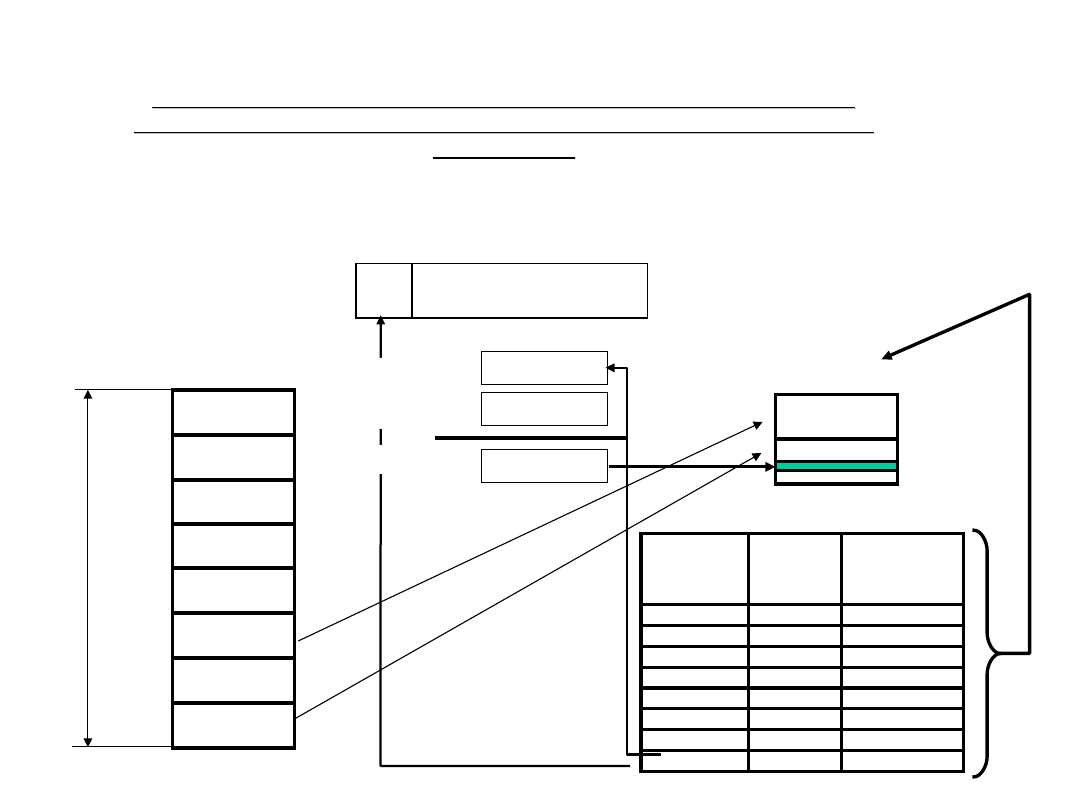

REJESTRY

REJESTRY

dostępne

dostępne

programowo

programowo

niedostępne

niedostępne

programowo

programowo

(na przykładzie 8 bitowego procesora 8086/8088)

(na przykładzie 8 bitowego procesora 8086/8088)

FLAGS

FLAGS

AX

AX

AX

AX

BX

BX

CX

CX

DX

DX

SI

SI

DI

DI

BP

BP

SP

SP

IP

IP

CS

CS

DS

DS

ES

ES

SS

SS

15

15

0

0

7

7

15

15

0

0

Rejestr

Rejestr

znacznikó

znacznikó

w

w

(flagowy

(flagowy

Rejestry

Rejestry

powszechne

powszechne

go

go

stosowania

stosowania

Rejestry

Rejestry

wskaźniko

wskaźniko

we i

we i

indeksowe

indeksowe

Rejestry

Rejestry

segmento

segmento

we

we

Wskaźnik

Wskaźnik

rozkazów

rozkazów

OF

OF

DF

DF

IF

IF

TF

TF

SF

SF

ZF

ZF

AF

AF

PF

PF

CF

CF

OF - flaga nadmiaru

OF - flaga nadmiaru

(przepełnienia)

(przepełnienia)

DF - flaga kierunku

DF - flaga kierunku

IF - flaga zezwolenia na

IF - flaga zezwolenia na

przerwanie

przerwanie

TF - flaga pracy krokowej

TF - flaga pracy krokowej

SF - flaga znaku

SF - flaga znaku

ZF - flaga zera

ZF - flaga zera

AF - flaga przeniesienia

AF - flaga przeniesienia

pomocniczego

pomocniczego

PF - flaga parzystości

PF - flaga parzystości

CF - flaga

CF - flaga

przeniesienia

przeniesienia

AH

AH

AL

AL

BH

BH

BL

BL

CH

CH

CL

CL

DH

DH

DL

DL

Wskaźnik stosu

Wskaźnik stosu

Wskaźnik bazy

Wskaźnik bazy

Rejestr

Rejestr

indeksowy

indeksowy

przeznaczenia

przeznaczenia

Rejestr

Rejestr

indeksowy

indeksowy

źródła

źródła

Rejestr danych

Rejestr danych

Rejestr

Rejestr

zliczający

zliczający

Rejestr bazowy

Rejestr bazowy

Akumulator

Akumulator

Rejestr

Rejestr

programu

programu

Rejestr danych

Rejestr danych

Rejestr

Rejestr

dodatkowy

dodatkowy

Rejestr stosu

Rejestr stosu

Znaczniki

Znaczniki

kontrolne

kontrolne

Znaczniki stanu

Znaczniki stanu

REJESTRY

REJESTRY

Rejestr znaczników (flagowy)

Rejestr znaczników (flagowy)

- rejestr przeznaczony do przechowywania

- rejestr przeznaczony do przechowywania

dodatkowych cech wyniku operacji (np. znak, przekroczenie zakresu, znak

dodatkowych cech wyniku operacji (np. znak, przekroczenie zakresu, znak

parzystości, ...) w postaci tzw. flagi (znacznika). Każdy znacznik jest bitem w

parzystości, ...) w postaci tzw. flagi (znacznika). Każdy znacznik jest bitem w

rejestrze, który wskazuje czy określony stan wystąpił. Znaczniki mogą być

rejestrze, który wskazuje czy określony stan wystąpił. Znaczniki mogą być

wykorzystywane przez procesor lub programistę na dwa sposoby:

wykorzystywane przez procesor lub programistę na dwa sposoby:

•

ustawienie znacznika dla zapamiętania określonego stanu po wykonaniu

ustawienie znacznika dla zapamiętania określonego stanu po wykonaniu

rozkazu

rozkazu

•

testowanie znacznika celem umożliwienia decyzji o sposobie dalszego

testowanie znacznika celem umożliwienia decyzji o sposobie dalszego

postępowania (przetwarzania danych)

postępowania (przetwarzania danych)

Znaczniki stanu:

Znaczniki stanu:

–

CF - flaga przeniesienia lub pożyczki, ustawiana przy przekroczeniu zakresu

CF - flaga przeniesienia lub pożyczki, ustawiana przy przekroczeniu zakresu

długości słowa, w którym zapisywany jest wynik (1 wystąpiło przeniesienie)

długości słowa, w którym zapisywany jest wynik (1 wystąpiło przeniesienie)

–

PF - flaga parzystości (1) wskazuje na parzystą lub nieparzystą liczbę bitów o

PF - flaga parzystości (1) wskazuje na parzystą lub nieparzystą liczbę bitów o

wartości jedynki

wartości jedynki

–

ZF - flaga zera - sygnalizująca, że wynikiem ostatnio wykonywanej operacji

ZF - flaga zera - sygnalizująca, że wynikiem ostatnio wykonywanej operacji

jest zero

jest zero

–

PF - flaga przeniesienia pomocniczego jest wykorzystywana przy działaniach

PF - flaga przeniesienia pomocniczego jest wykorzystywana przy działaniach

na liczbach w kodzie BCD. Ustawiana jest gdy następuje przeniesienie lub

na liczbach w kodzie BCD. Ustawiana jest gdy następuje przeniesienie lub

pożyczka z najstarszego bitu pierwszej tetrady wyniku

pożyczka z najstarszego bitu pierwszej tetrady wyniku

–

SF - flaga znaku, ustawiana gdy najstarszy bit wyniku jest równy 1 (operacje

SF - flaga znaku, ustawiana gdy najstarszy bit wyniku jest równy 1 (operacje

liczb ze znakiem - kod U2)

liczb ze znakiem - kod U2)

–

OF - flaga przepełnienia, sygnalizująca przekroczenie zakresu dla operacji

OF - flaga przepełnienia, sygnalizująca przekroczenie zakresu dla operacji

arytmetycznych (operacje liczb ze znakiem - kod U2)

arytmetycznych (operacje liczb ze znakiem - kod U2)

Znaczniki kontrolne:

Znaczniki kontrolne:

–

TF- znacznik pracy krokowej - ustawienie 1 pozwala na wykonanie przez

TF- znacznik pracy krokowej - ustawienie 1 pozwala na wykonanie przez

procesor po wykonaniu każdego rozkazu przerwania i przejście do

procesor po wykonaniu każdego rozkazu przerwania i przejście do

specjalnych procedur obsługi

specjalnych procedur obsługi

–

IF- znacznik zezwolenia na przerwanie - ustawienie 1 powoduje odblokowanie

IF- znacznik zezwolenia na przerwanie - ustawienie 1 powoduje odblokowanie

systemu przerwań w procesorze (0 - procesor ignoruje przerwania)

systemu przerwań w procesorze (0 - procesor ignoruje przerwania)

–

DF - znacznik kierunku - umożliwia realizację przetwarzania łańcuchów (ciągu

DF - znacznik kierunku - umożliwia realizację przetwarzania łańcuchów (ciągu

słów) przy rosnących adresach (1) lub malejących adresach (0)

słów) przy rosnących adresach (1) lub malejących adresach (0)

REJESTRY

REJESTRY

Rejestry ogólnego przeznaczenia

Rejestry ogólnego przeznaczenia

- rejestry przeznaczone do przechowywania

- rejestry przeznaczone do przechowywania

dowolnych danych i wykonywania operacji (arytmetycznych i logicznych), ale

dowolnych danych i wykonywania operacji (arytmetycznych i logicznych), ale

jednocześnie spełniające pewne funkcje specjalne. Szczególną funkcję pełni

jednocześnie spełniające pewne funkcje specjalne. Szczególną funkcję pełni

akumulator

akumulator

Akumulator

Akumulator

- rejestr przeznaczony do przechowywania jednego z operandów

- rejestr przeznaczony do przechowywania jednego z operandów

(argumentów) wykonywanej operacji oraz wyniku wykonywanej operacji

(argumentów) wykonywanej operacji oraz wyniku wykonywanej operacji

(czasami wynik może być umieszczany w innym rejestrze)

(czasami wynik może być umieszczany w innym rejestrze)

Rejestry segmentowe

Rejestry segmentowe

- są rejestrami wykorzystywanymi do adresowania

- są rejestrami wykorzystywanymi do adresowania

pamięci operacyjnej. Rejestry te zawierają adresy początkowe segmentów

pamięci operacyjnej. Rejestry te zawierają adresy początkowe segmentów

–

CS rejestr segmentowy programu wskazuje segment programu, z

CS rejestr segmentowy programu wskazuje segment programu, z

którego aktualnie są pobierane kolejne rozkazy do wykonania,

którego aktualnie są pobierane kolejne rozkazy do wykonania,

–

DS rejestr segmentowy stosu wskazuje segment, w którym zapamiętane

DS rejestr segmentowy stosu wskazuje segment, w którym zapamiętane

są zmienne używane w programie,

są zmienne używane w programie,

–

ES rejestr segmentowy dodatkowy wskazuje dodatkowy segment

ES rejestr segmentowy dodatkowy wskazuje dodatkowy segment

danych,

danych,

–

SS rejestr segmentowy stosu wskazuje segment pamięci, w którym

SS rejestr segmentowy stosu wskazuje segment pamięci, w którym

zdefiniowany jest stos.

zdefiniowany jest stos.

Wskaźnik rozkazów

Wskaźnik rozkazów

(wskaźnik instrukcji) - łącznie z rejestrem segmentowym

(wskaźnik instrukcji) - łącznie z rejestrem segmentowym

CS adresuje kolejne rozkazy przeznaczone do wykonania. Wskazuje adres

CS adresuje kolejne rozkazy przeznaczone do wykonania. Wskazuje adres

względem początku segmentu programu

względem początku segmentu programu

Rejestry wskaźnikowe i indeksowe

Rejestry wskaźnikowe i indeksowe

- posiadają dwa rejestry wskaźnikowe i

- posiadają dwa rejestry wskaźnikowe i

dwa rejestry indeksowe.

dwa rejestry indeksowe.

Rejestry wskaźnikowe (SP, BP) są stosowane do adresowania danych w

Rejestry wskaźnikowe (SP, BP) są stosowane do adresowania danych w

obrębie wydzielonego obszaru pamięci (stosu).

obrębie wydzielonego obszaru pamięci (stosu).

Rejestry indeksowe (SI, DI) służą do adresowania danych w obszarze pamięci

Rejestry indeksowe (SI, DI) służą do adresowania danych w obszarze pamięci

zwanym segmentem danych.

zwanym segmentem danych.

Wszystkie rejestry mogą być wykorzystywane jako argumenty większości

Wszystkie rejestry mogą być wykorzystywane jako argumenty większości

rozkazów arytmetycznych i logicznych.

rozkazów arytmetycznych i logicznych.

REJESTRY

REJESTRY

Wskaźnik stosu(SP) - rejestr zawierający adres ostatniej zapełnionej komórki

Wskaźnik stosu(SP) - rejestr zawierający adres ostatniej zapełnionej komórki

stosu (wierzchołka stosu)

stosu (wierzchołka stosu)

Stosem nazywamy wyróżniony obszar w pamięci używany wg reguł:

Stosem nazywamy wyróżniony obszar w pamięci używany wg reguł:

–

informacje zapisane są na stos do kolejnych komórek (pod kolejnymi

informacje zapisane są na stos do kolejnych komórek (pod kolejnymi

adresami), przy czym żadnego adresu nie wolno pominąć

adresami), przy czym żadnego adresu nie wolno pominąć

–

odczytujemy informacje w kolejności odwrotnej do ich zapisu

odczytujemy informacje w kolejności odwrotnej do ich zapisu

–

informacje odczytujemy z ostatnio zapełnionej komórki, natomiast

informacje odczytujemy z ostatnio zapełnionej komórki, natomiast

zapisujemy do pierwszej wolnej

zapisujemy do pierwszej wolnej

Czyli obowiązuje reguła LIFO - ostatni wchodzi pierwszy wychodzi

Czyli obowiązuje reguła LIFO - ostatni wchodzi pierwszy wychodzi

lub

lub

Adres

Program główny

101

Instrukcja

102

Instrukcja

103

Call

Wywołanie podprogramu I

(adres 104 na stos)

1002

Instrukcja

1003

Instrukcja

1004

Call

Wywołanie podprogramu II

(adres 1005 na stos)

2001

Instrukcja

2002

Instrukcja

2003

Return

1005

Instrukcja

1006

Instrukcja

1007

Return

Powrót z podprogramu II

(do adresu 1005

odczytanego ze stosu)

104

Instrukcja

105

Instrukcja

106

Instrukcja

Powrót z podprogramu I

(do adresu 104

odczytanego ze stosu)

107

Instrukcja

stos

stos

stos

stos

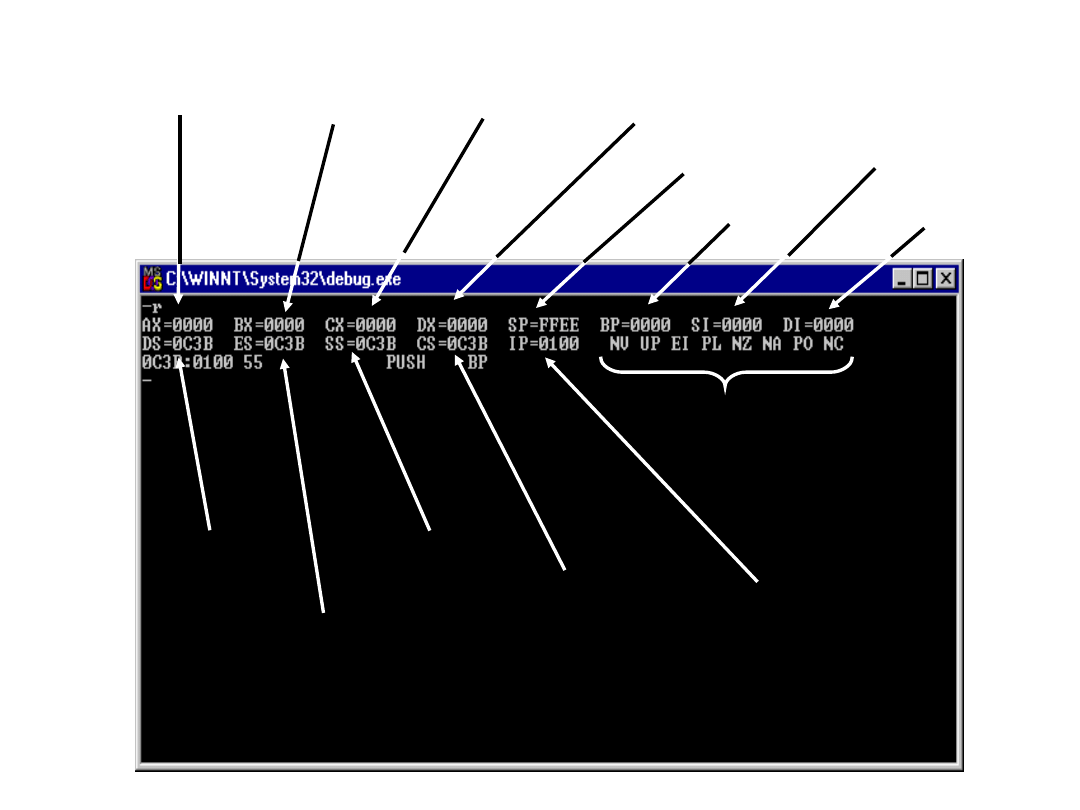

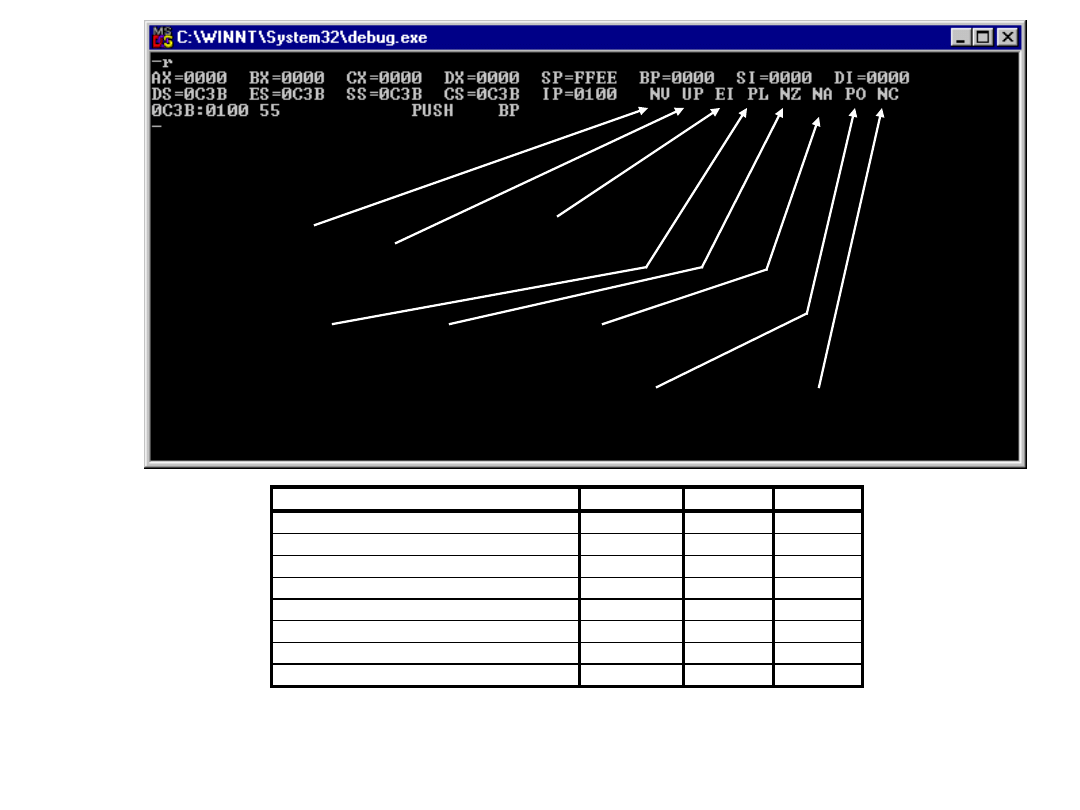

akumulator rejestr bazowy

rejestr

zliczający

rejestr danych

wskaźnik stosu

wskaźnik bazy

rejestr indeksowy

źródła

rejestr indeksowy

przeznaczenia

rejestr danych

rejestr dodatkowy

rejestr stosu

rejestr programu wskaźnik rozkazów

rejestr flagowy

(znaczników)

flaga parzystości

flaga przeniesienia

pomocniczego

flaga zera

flaga zezwolenia

na przerwanie

flaga nadmiaru

flaga kierunku

flaga znaku

flaga przeniesienia

Flaga (znacznik)

symbol

=1

=0

Flaga nadmiaru

OF

OV

NV

Flaga kierunku

DF

DN

UP

Flaga zezwolenia na przerwanie

IF

EI

DI

Flaga znaku

SF

NG

PL

Flaga zera

ZF

ZR

NZ

Flaga przeniesienia pomocniczego

AF

AC

NA

Flaga parzystości

PF

PE

PO

Flaga przeniesienia

CF

CY

NC

BLOK ARYTMETYCZNO-LOGICZNY

BLOK ARYTMETYCZNO-LOGICZNY

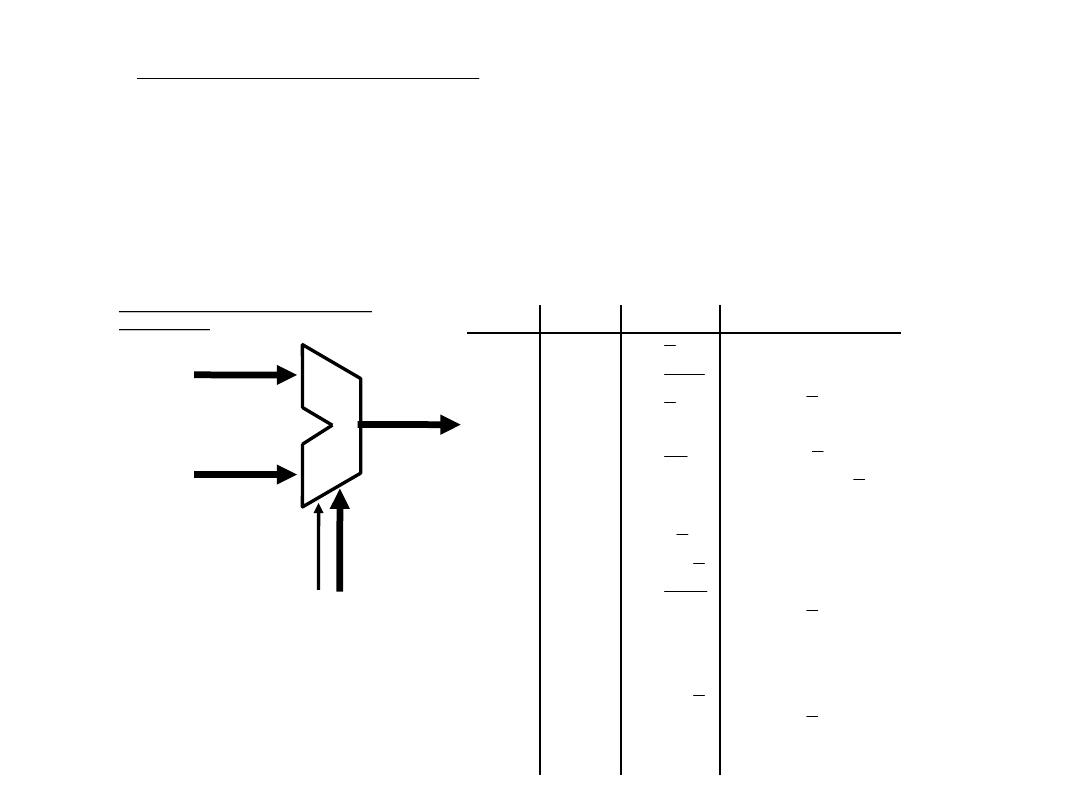

Blok arytmetyczno-logiczny (ALU)

Blok arytmetyczno-logiczny (ALU)

- jest uniwersalnym układem

- jest uniwersalnym układem

kombinacyjnym, który realizuje operacje matematyczne i logiczne w

kombinacyjnym, który realizuje operacje matematyczne i logiczne w

zależności od zaprogramowanej operacji tj. rozkazu umieszczonego w

zależności od zaprogramowanej operacji tj. rozkazu umieszczonego w

programie.

programie.

Rozkazy mogą dotyczyć

Rozkazy mogą dotyczyć

•

operacji dwuargumentowych:

operacji dwuargumentowych:

–

operacji arytmetycznych (dodawanie i odejmowanie)

operacji arytmetycznych (dodawanie i odejmowanie)

–

operacji logicznych (sumowanie mnożenie, sumowanie mod 2, itp.)

operacji logicznych (sumowanie mnożenie, sumowanie mod 2, itp.)

•

operacji jednoargumentowych (np. negowanie bitów lub przesuwanie

operacji jednoargumentowych (np. negowanie bitów lub przesuwanie

zawartości rejestrów)

zawartości rejestrów)

Argumentami rozkazów są najczęściej dwa słowa binarne, od długości

Argumentami rozkazów są najczęściej dwa słowa binarne, od długości

których mówi się o liczbie bitów ALU.

których mówi się o liczbie bitów ALU.

A

A

0

0

- A

- A

3

3

B

B

0

0

- B

- B

3

3

S

S

0

0

- S

- S

3

3

M

M

F

F

0

0

- F

- F

3

3

A

F

B

A

F

B

A

F

F

AB

F

B

F

B

A

F

B

A

F

B

A

F

B

A

F

B

F

AB

F

F

B

A

F

B

A

F

A

F

1

0

)

1

(

)

(

)

(

2

)

1

(

)

(

)

1

(

)

1

(

)

(

1

)

(

)

(

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

C

A

F

C

A

B

A

F

C

A

AB

F

C

A

F

C

AB

F

C

AB

B

A

F

C

B

A

F

C

AB

A

F

C

A

F

C

B

A

F

C

B

A

B

A

F

C

B

A

A

F

C

F

C

B

A

F

C

B

A

F

C

A

F

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

1111

0111

1011

0011

1101

0101

1001

0001

1110

0110

1010

0010

1100

0100

1000

0000

Lp. S

Lp. S

0

0

- S

- S

3

3

M=0 M=1

M=0 M=1

Sygnały sterujące

Sygnały sterujące

do wyboru

do wyboru

mikrooperacji

mikrooperacji

logicznej (M=0) lub

logicznej (M=0) lub

arytmetycznej

arytmetycznej

(M=1)

(M=1)

Przykład 4 bitowego ALU

Przykład 4 bitowego ALU

SN74181

SN74181

UKŁAD STEROWANIA

UKŁAD STEROWANIA

Często (a może najczęściej) procesor wykonuje rozkazy nie w

Często (a może najczęściej) procesor wykonuje rozkazy nie w

jednym kroku (jak np. dodawanie) ale w wielu krokach (np.

jednym kroku (jak np. dodawanie) ale w wielu krokach (np.

mnożenie lub dzielenie jako ciąg dodawań i przesunięć).

mnożenie lub dzielenie jako ciąg dodawań i przesunięć).

W tym celu potrzebny jest złożony automat sekwencyjny,

W tym celu potrzebny jest złożony automat sekwencyjny,

generujący odpowiednie ciągi słów podawanych na wejścia

generujący odpowiednie ciągi słów podawanych na wejścia

sterujące układu ALU - układ sterowania.

sterujące układu ALU - układ sterowania.

Cechy takiego automatu to:

Cechy takiego automatu to:

•

konieczność posiadania bardzo dużej liczby stanów

konieczność posiadania bardzo dużej liczby stanów

dostosowanych do wymaganej liczby wykonywanych

dostosowanych do wymaganej liczby wykonywanych

rozkazów;

rozkazów;

•

konieczność zapewnienia synchronizacji pracy układu

konieczność zapewnienia synchronizacji pracy układu

sterowania i wykonawczego (uwzględnienie czasów

sterowania i wykonawczego (uwzględnienie czasów

wykonywania poszczególnych operacji).

wykonywania poszczególnych operacji).

W praktyce realizowane są jako:

W praktyce realizowane są jako:

•

generatory sekwencyjne

generatory sekwencyjne

•

układy mikroprogramowalne

układy mikroprogramowalne

ROZKAZY I TRYB ADRESOWANIA

ROZKAZY I TRYB ADRESOWANIA

dr inż. Jacek FLOREK

dr inż. Jacek FLOREK

Instytut Informatyki

Instytut Informatyki

Cykl rozkazowy

Cykl rozkazowy

Lista i format rozkazu

Lista i format rozkazu

Tryb adresowania

Tryb adresowania

Sposób prezentowania rozkazu

Sposób prezentowania rozkazu

9

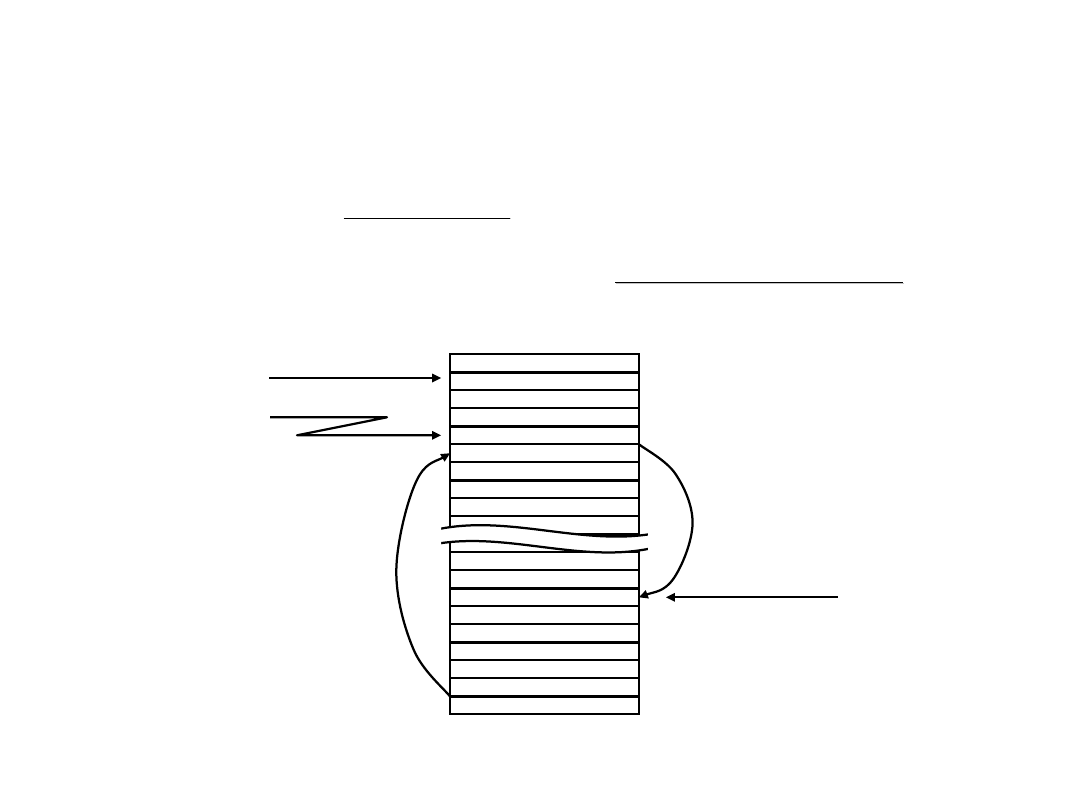

CYKL ROZKAZOWY PROCESORA

CYKL ROZKAZOWY PROCESORA

Realizując program, system mikroprocesorowy wykonuje pewne

Realizując program, system mikroprocesorowy wykonuje pewne

powtarzające się czynności, polegające na cyklicznym pobieraniu

powtarzające się czynności, polegające na cyklicznym pobieraniu

kodów rozkazów z pamięci i wczytywaniu ich do układu sterowania,

kodów rozkazów z pamięci i wczytywaniu ich do układu sterowania,

a następnie realizacji rozkazu

a następnie realizacji rozkazu

Def.1. Czas potrzebny na odczytanie kodu rozkazu z

Def.1. Czas potrzebny na odczytanie kodu rozkazu z

pamięci, na pobranie argumentów, na wykonanie

pamięci, na pobranie argumentów, na wykonanie

rozkazu i przesłanie wyniku operacji nazywa się

rozkazu i przesłanie wyniku operacji nazywa się

cyklem rozkazowym (instrukcyjnym)

cyklem rozkazowym (instrukcyjnym)

Def.1. Czas potrzebny na odczytanie kodu rozkazu z

Def.1. Czas potrzebny na odczytanie kodu rozkazu z

pamięci, na pobranie argumentów, na wykonanie

pamięci, na pobranie argumentów, na wykonanie

rozkazu i przesłanie wyniku operacji nazywa się

rozkazu i przesłanie wyniku operacji nazywa się

cyklem rozkazowym (instrukcyjnym)

cyklem rozkazowym (instrukcyjnym)

Cykl rozkazowy składa się zwykle z faz pobierania (kodu rozkazu,

Cykl rozkazowy składa się zwykle z faz pobierania (kodu rozkazu,

pobierania argumentu) i wykonania rozkazu.

pobierania argumentu) i wykonania rozkazu.

P

a

m

ię

ć

P

a

m

ię

ć

C

P

U

C

P

U

POBRANIE

POBRANIE

ROZKAZU

ROZKAZU

WYSŁANIE

WYSŁANIE

ADRESU

ADRESU

ROZKAZU

ROZKAZU

DEKODOW

DEKODOW

ANIE

ANIE

ROZKAZU

ROZKAZU

OBLICZANIE

OBLICZANIE

ADRESU

ADRESU

ARGUMENTU

ARGUMENTU

I

I

OBLICZANIE

OBLICZANIE

ADRESU

ADRESU

ARGUMENTU

ARGUMENTU

II

II

WYKONANIE

WYKONANIE

ROZKAZU

ROZKAZU

OBLICZENIE

OBLICZENIE

ADRESU

ADRESU

PRZEZNACZE

PRZEZNACZE

-

-

NIA

NIA

ZAPIS

ZAPIS

WYNIKU

WYNIKU

POBRANIE

POBRANIE

ARGUMENTU

ARGUMENTU

II

II

POBRANIE

POBRANIE

ARGUMENTU

ARGUMENTU

I

I

cykl pobrania

cykl pobrania

rozkazu

rozkazu

cykl

cykl

pobrani

pobrani

a

a

argume

argume

ntu I

ntu I

cykl

cykl

pobrani

pobrani

a

a

argume

argume

ntu II

ntu II

cykl zapisu wyniku

cykl zapisu wyniku

CYKL ROZKAZOWY PROCESORA

CYKL ROZKAZOWY PROCESORA

Czas trwania fazy pobierania rozkazu (pobierania argumentu)

Czas trwania fazy pobierania rozkazu (pobierania argumentu)

zależy od rodzaju procesora i rodzaju rozkazu (argumentu).

zależy od rodzaju procesora i rodzaju rozkazu (argumentu).

Np.

Np.

Jeżeli procesor jest 8-bitowy, kod rozkazu 8-bitowy, adres

Jeżeli procesor jest 8-bitowy, kod rozkazu 8-bitowy, adres

argumentu 16-bitowy to faza pobrania rozkazu składa się z trzech

argumentu 16-bitowy to faza pobrania rozkazu składa się z trzech

cykli odczytu pamięci:

cykli odczytu pamięci:

•

odczyt kodu - pobranie rozkazu

odczyt kodu - pobranie rozkazu

•

odczyt jednego bajtu adresu

odczyt jednego bajtu adresu

•

odczyt drugiego bajtu adresu

odczyt drugiego bajtu adresu

Jeżeli procesor i rozkaz są 32-bitowe to wystąpi jedna faza

Jeżeli procesor i rozkaz są 32-bitowe to wystąpi jedna faza

pobrania rozkazu

pobrania rozkazu

Rozpatrzmy przykład wykonania programu dodawania dwóch liczb

Rozpatrzmy przykład wykonania programu dodawania dwóch liczb

16-bitowych stałopozycyjnych w komputerze 16-bitowym. Pamięć

16-bitowych stałopozycyjnych w komputerze 16-bitowym. Pamięć

jest 16-bitowa, kod rozkazu 12-bitowy a adres 20-bitowy (kod

jest 16-bitowa, kod rozkazu 12-bitowy a adres 20-bitowy (kod

rozkazu i adres można zatem umieścić w 2 komórkach pamięci)

rozkazu i adres można zatem umieścić w 2 komórkach pamięci)

Faza pobrania:

Faza pobrania:

1. adresowanie: podanie zawartości licznika rozkazów PC

1. adresowanie: podanie zawartości licznika rozkazów PC

(rejestru adresującego pamięć AD) na magistralę adresową

(rejestru adresującego pamięć AD) na magistralę adresową

2. odczyt zaadresowanej komórki pamięci do rejestru rozkazów

2. odczyt zaadresowanej komórki pamięci do rejestru rozkazów

(RR)

(RR)

3. zwiększenie zawartości licznika rozkazów

3. zwiększenie zawartości licznika rozkazów

Faza wykonania:

Faza wykonania:

4. zdekodowanie kodu rozkazu i wytworzenie sygnałów

4. zdekodowanie kodu rozkazu i wytworzenie sygnałów

sterujących realizujących dany rozkaz

sterujących realizujących dany rozkaz

1

1

2

2

3

3

4

4

Cykl von

Cykl von

Neumana

Neumana

w przypadku rozkazów

wielobajtowych

PC(AD)

PC(AD)

RR

RR

kod

kod

rozkazu

rozkazu

kod

kod

rozkazu

rozkazu

kod

kod

rozkazu

rozkazu

kod

kod

rozkazu

rozkazu

kod

kod

rozkazu

rozkazu

procesor

procesor

pamięć

pamięć

s

zy

n

a

a

d

re

so

w

a

s

zy

n

a

a

d

re

so

w

a

s

zy

n

a

d

a

n

y

c

h

s

zy

n

a

d

a

n

y

c

h

MAPA PAMIĘCI

300

ładuj A

adres 841

301

adres 841

302

ładuj B

adres 915

303

adres 915

304

dodaj A+B

305

zapisz pamięć

adres 915

306

adres 915

841

4

915

5

ZAWARTOŚĆ REJ ESTRÓW PROCESORA

Pobranie kodu rozkazu

i 4 bitów adresu

Pobranie 16

bitów adresu

Odczyt

argumentu

A

4

B

ładuj A

PC

300

301

302

AD

300

301

841

RR

ładuj A

ładuj A

ładuj A

Pobranie kodu rozkazu

i 4 bitów adresu

Pobranie 16

bitów adresu

Odczyt

argumentu

A

4

4

4

B

5

ładuj B

PC

302

303

304

AD

302

303

915

RR

ładuj B

ładuj B

ładuj B

Pobranie kodu rozkazu

A

B

5

dodaj

PC

304

AD

304

RR

dodaj

Pobranie kodu rozkazu

i 4 bitów adresu

Pobranie 16

bitów adresu

Odczyt

argumentu

A

9

9

9

B

5

5

5

zapisz

PC

305

306

307

pamięć

AD

305

306

915

RR

zapisz

zapisz

zapisz

A

Rejestr A

B

Rejestr B

PC

Licznik rozkazów

AD

Rejestr adresujący pamięć

RR

Rejestr rozkazów

1

6

Program składa się z 4 rozkazów (adres pierwszego rozkazu wynosi

Program składa się z 4 rozkazów (adres pierwszego rozkazu wynosi

300):

300):

•

odczyt pierwszego argumentu z komórki o adresie 841 i zapisanie go

odczyt pierwszego argumentu z komórki o adresie 841 i zapisanie go

do rejestru A

do rejestru A

•

odczyt drugiego argumentu z komórki o adresie 915 i zapisanie go do

odczyt drugiego argumentu z komórki o adresie 915 i zapisanie go do

rejestru B

rejestru B

•

dodanie obu argumentów

dodanie obu argumentów

•

przesłanie wyniku do komórki pamięci o adresie 915

przesłanie wyniku do komórki pamięci o adresie 915

LISTA ROZKAZÓW

LISTA ROZKAZÓW

Def.1. Rozkazem (instrukcją maszynową) nazywamy

Def.1. Rozkazem (instrukcją maszynową) nazywamy

najprostszą operację, której wykonania programista

najprostszą operację, której wykonania programista

może zażądać od procesora

może zażądać od procesora

Def.1. Rozkazem (instrukcją maszynową) nazywamy

Def.1. Rozkazem (instrukcją maszynową) nazywamy

najprostszą operację, której wykonania programista

najprostszą operację, której wykonania programista

może zażądać od procesora

może zażądać od procesora

Def.2. Listą rozkazów nazywamy zestaw wszystkich

Def.2. Listą rozkazów nazywamy zestaw wszystkich

instrukcji maszynowych (rozkazów), jakie potrafi

instrukcji maszynowych (rozkazów), jakie potrafi

wykonać dany procesor

wykonać dany procesor

Def.2. Listą rozkazów nazywamy zestaw wszystkich

Def.2. Listą rozkazów nazywamy zestaw wszystkich

instrukcji maszynowych (rozkazów), jakie potrafi

instrukcji maszynowych (rozkazów), jakie potrafi

wykonać dany procesor

wykonać dany procesor

•

rozkazy przesłań

rozkazy przesłań

•

rozkazy arytmetyczne i logiczne

rozkazy arytmetyczne i logiczne

•

rozkazy sterujące (skoki, wywołania podprogramów, pętle, itp.)

rozkazy sterujące (skoki, wywołania podprogramów, pętle, itp.)

•

inne (np. sterowanie pracą koprocesora, rozkazy testujące, operacje w

inne (np. sterowanie pracą koprocesora, rozkazy testujące, operacje w

trybie chronionym)

trybie chronionym)

Rozkazy (jak inne informacje) są przechowywane w systemie

Rozkazy (jak inne informacje) są przechowywane w systemie

mikroprocesorowym w postaci kodów binarnych

mikroprocesorowym w postaci kodów binarnych

Adres

komórki

Zawartość

komórki

0000

0000

1011

0001

0000

0001

0001

0101

0000

0010

1010

0000

0000

0011

0000

0000

0000

0100

0000

1111

0000

0101

0000

0000

0000

0110

1100

1000

0000

0111

1100

0110

0000

1000

1010

1010

-

-

0000

1111

0000

0010

MOV CL,5

MOV A, [B2,B3]

ADD CL,A

A=A+5

OUT [B2]

rozkazy w postaci kodów binarnych

rozkazy w postaci kodów binarnych

instrukcje maszynowe

instrukcje maszynowe

instrukcje w FORTRANie

instrukcje w FORTRANie

FORMAT ROZKAZÓW I TRYB

FORMAT ROZKAZÓW I TRYB

ADRESOWANIA

ADRESOWANIA

Def.1. Formatem rozkazu nazywamy sposób

Def.1. Formatem rozkazu nazywamy sposób

rozmieszczenia informacji w kodzie rozkazu

rozmieszczenia informacji w kodzie rozkazu

Def.1. Formatem rozkazu nazywamy sposób

Def.1. Formatem rozkazu nazywamy sposób

rozmieszczenia informacji w kodzie rozkazu

rozmieszczenia informacji w kodzie rozkazu

Kod rozkazu:

Kod rozkazu:

•

musi zawierać określenie rodzaju wykonywanej operacji (kod operacji)

musi zawierać określenie rodzaju wykonywanej operacji (kod operacji)

- w pierwszym bajcie (bajtach) kodu rozkazu

- w pierwszym bajcie (bajtach) kodu rozkazu

•

może zawierać operandy i/lub adresy operandów wykonywanych

może zawierać operandy i/lub adresy operandów wykonywanych

operacji

operacji

Def.2. Trybem adresowania nazywamy

Def.2. Trybem adresowania nazywamy

sposób

sposób

określenia

określenia

miejsca przechowywania argumentów rozkazu

miejsca przechowywania argumentów rozkazu

Def.2. Trybem adresowania nazywamy

Def.2. Trybem adresowania nazywamy

sposób

sposób

określenia

określenia

miejsca przechowywania argumentów rozkazu

miejsca przechowywania argumentów rozkazu

Argumenty rozkazu (dotyczy zarówno danych jak i wyników) mogą być

Argumenty rozkazu (dotyczy zarówno danych jak i wyników) mogą być

przechowywane w:

przechowywane w:

•

rejestrach

rejestrach

•

pamięci

pamięci

•

kodzie rozkazu

kodzie rozkazu

Rozróżniamy następujące tryby

Rozróżniamy następujące tryby

adresowania

adresowania

•

adresowanie natychmiastowe

adresowanie natychmiastowe

•

adresowanie bezpośrednie

adresowanie bezpośrednie

•

adresowanie rejestrowe

adresowanie rejestrowe

•

adresowanie pośrednie

adresowanie pośrednie

•

adresowanie indeksowe z

adresowanie indeksowe z

przemieszczeniem

przemieszczeniem

TRYB ADRESOWANIA

TRYB ADRESOWANIA

Def.Przy

Def.Przy

adresowaniu natychmiastowym

adresowaniu natychmiastowym

argument

argument

rozkazu zawarty jest w kodzie rozkazu

rozkazu zawarty jest w kodzie rozkazu

Def.Przy

Def.Przy

adresowaniu natychmiastowym

adresowaniu natychmiastowym

argument

argument

rozkazu zawarty jest w kodzie rozkazu

rozkazu zawarty jest w kodzie rozkazu

Oznacza to, że w zasadzie nie jest to adresowanie w

Oznacza to, że w zasadzie nie jest to adresowanie w

zwykłym sensie. Argument jest umieszczany w kodzie

zwykłym sensie. Argument jest umieszczany w kodzie

rozkazu, więc musi być on znany w momencie pisania

rozkazu, więc musi być on znany w momencie pisania

programu.

programu.

Kod rozkazu

Kod rozkazu

Kod operacji

Kod operacji

Argument

Argument

Def.Przy adresowaniu bezpośrednim kod rozkazu zawiera

Def.Przy adresowaniu bezpośrednim kod rozkazu zawiera

adres komórki pamięci, w której przechowywany jest

adres komórki pamięci, w której przechowywany jest

argument rozkazu

argument rozkazu

Def.Przy adresowaniu bezpośrednim kod rozkazu zawiera

Def.Przy adresowaniu bezpośrednim kod rozkazu zawiera

adres komórki pamięci, w której przechowywany jest

adres komórki pamięci, w której przechowywany jest

argument rozkazu

argument rozkazu

W momencie pisania programu musimy zarezerwować adres

W momencie pisania programu musimy zarezerwować adres

przechowywania argumentu.

przechowywania argumentu.

Kod

Kod

rozkazu

rozkazu

Kod operacji

Kod operacji

Adres

Adres

Argument

Argument

P

A

M

IĘ

Ć

P

A

M

IĘ

Ć

TRYB ADRESOWANIA

TRYB ADRESOWANIA

Def.Przy

Def.Przy

adresowaniu rejestrowym

adresowaniu rejestrowym

w kodzie rozkazu

w kodzie rozkazu

zawarty jest rejestr, w którym przechowywany jest

zawarty jest rejestr, w którym przechowywany jest

argument

argument

Def.Przy

Def.Przy

adresowaniu rejestrowym

adresowaniu rejestrowym

w kodzie rozkazu

w kodzie rozkazu

zawarty jest rejestr, w którym przechowywany jest

zawarty jest rejestr, w którym przechowywany jest

argument

argument

Zaletą tego trybu jest krótki kod i szybkie wykonanie

Zaletą tego trybu jest krótki kod i szybkie wykonanie

Kod

Kod

rozkazu

rozkazu

Kod

Kod

operacji

operacji

Określeni

Określeni

e

e

rejestru

rejestru

Argument

Argument

REJESTR

REJESTR

Def.W trybie

Def.W trybie

adresowania pośredniego (rejestrowego

adresowania pośredniego (rejestrowego

pośredniego)

pośredniego)

kod rozkazu zawiera określenie rejestru

kod rozkazu zawiera określenie rejestru

bądź rejestrów, w których znajduje się adres komórki

bądź rejestrów, w których znajduje się adres komórki

pamięci zawierającej argument

pamięci zawierającej argument

Def.W trybie

Def.W trybie

adresowania pośredniego (rejestrowego

adresowania pośredniego (rejestrowego

pośredniego)

pośredniego)

kod rozkazu zawiera określenie rejestru

kod rozkazu zawiera określenie rejestru

bądź rejestrów, w których znajduje się adres komórki

bądź rejestrów, w których znajduje się adres komórki

pamięci zawierającej argument

pamięci zawierającej argument

Adres

Adres

REJESTR

REJESTR

Argument

Argument

P

A

M

IĘ

Ć

P

A

M

IĘ

Ć

Kod

Kod

operacji

operacji

Określeni

Określeni

e

e

rejestru

rejestru

Kod

Kod

rozkazu

rozkazu

TRYB ADRESOWANIA

TRYB ADRESOWANIA

Def.W trybie

Def.W trybie

adresowania indeksowego z

adresowania indeksowego z

przemieszczeniem

przemieszczeniem

adres argumentu

adres argumentu

przechowywanego w pamięci obliczany jest jako suma

przechowywanego w pamięci obliczany jest jako suma

zawartości rejestru określonego w kodzie rozkazu i

zawartości rejestru określonego w kodzie rozkazu i

wartości umieszczonej w kodzie rozkazu, zwanej

wartości umieszczonej w kodzie rozkazu, zwanej

przemieszczeniem

przemieszczeniem

Def.W trybie

Def.W trybie

adresowania indeksowego z

adresowania indeksowego z

przemieszczeniem

przemieszczeniem

adres argumentu

adres argumentu

przechowywanego w pamięci obliczany jest jako suma

przechowywanego w pamięci obliczany jest jako suma

zawartości rejestru określonego w kodzie rozkazu i

zawartości rejestru określonego w kodzie rozkazu i

wartości umieszczonej w kodzie rozkazu, zwanej

wartości umieszczonej w kodzie rozkazu, zwanej

przemieszczeniem

przemieszczeniem

Kod

Kod

rozkazu

rozkazu

Kod

Kod

operacji

operacji

Określeni

Określeni

e

e

rejestru

rejestru

wartość

wartość

REJESTR

REJESTR

Przemieszczen

Przemieszczen

ie

ie

Argument

Argument

P

A

M

IĘ

Ć

P

A

M

IĘ

Ć

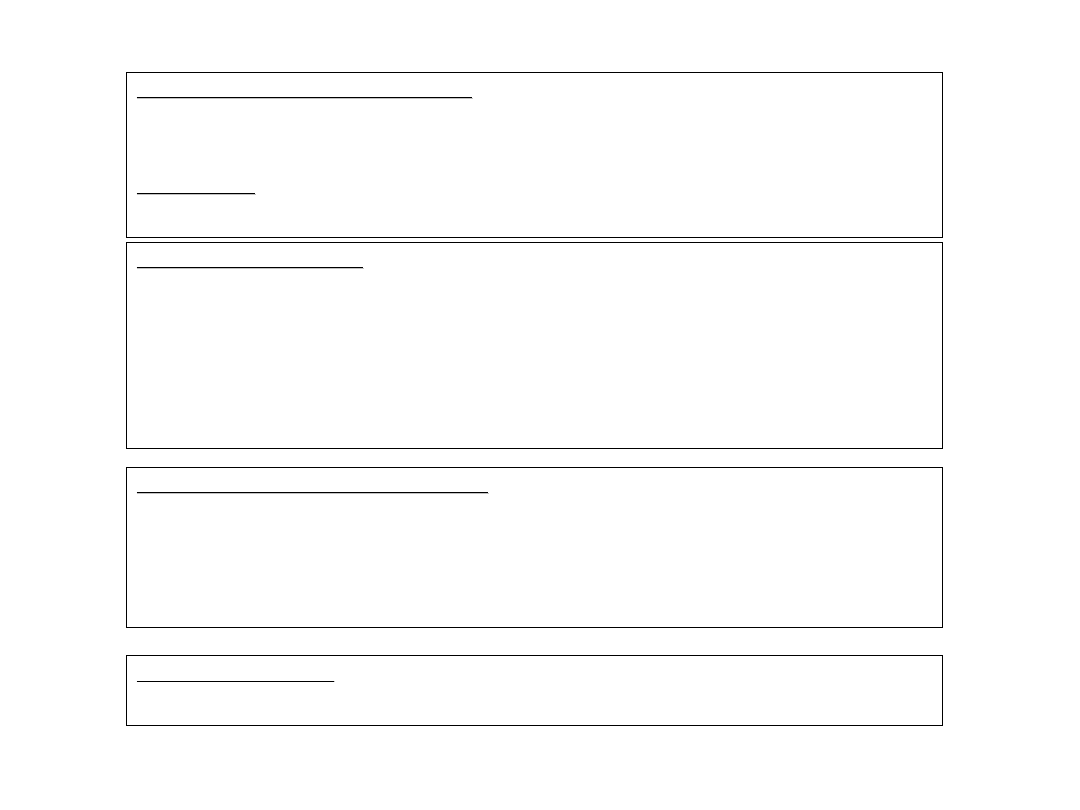

SPOSÓB PREZENTOWANIA ROZKAZU

SPOSÓB PREZENTOWANIA ROZKAZU

1.

1.

Oznaczenie symboliczne rozkazu

Oznaczenie symboliczne rozkazu

Jest stosowane dla prezentacji programu człowiekowi lub przy

Jest stosowane dla prezentacji programu człowiekowi lub przy

pisaniu programów w asemblerze

pisaniu programów w asemblerze

Składa się ono z mnemonika (skrótu, który powinien sugerować

Składa się ono z mnemonika (skrótu, który powinien sugerować

rodzaj operacji) i pola argumentów

rodzaj operacji) i pola argumentów

JMP SHORT

JMP SHORT

NEXT

NEXT

mnemonik

mnemonik

argument

argument

PAMIĘĆ

ADRESY

11101011

000

00000011

001

010

011

NEXT

Kolejny rozkaz

100

101

110

EB 03h

EB 03h

argumen

argumen

t

t

kod operacji

kod operacji

Kod rozkazu w

Kod rozkazu w

kodzie

kodzie

heksadecymalnym

heksadecymalnym

Kod rozkazu

Kod rozkazu

binarnie (w

binarnie (w

pamięci)

pamięci)

................................

................................

SPOSÓB PREZENTOWANIA ROZKAZU

SPOSÓB PREZENTOWANIA ROZKAZU

2.

2.

Opis działania rozkazu

Opis działania rozkazu

Jest możliwy w formie słownej lub symbolicznej

Jest możliwy w formie słownej lub symbolicznej

Opis słowny:

Opis słowny:

„

„

Wykonaj skok i pobierz kod rozkazu z

Wykonaj skok i pobierz kod rozkazu z

komórki pamięci o adresie równym

komórki pamięci o adresie równym

etykieta”

etykieta”

(u nas NEXT=100)

Argumentem jest jednak nie adres komórki lecz długość

Argumentem jest jednak nie adres komórki lecz długość

skoku (interpretowana w kodzie U2). SHORT oznacza w tym

skoku (interpretowana w kodzie U2). SHORT oznacza w tym

przypadku skok bliski (w zakresie od 127 bajtów w górę do

przypadku skok bliski (w zakresie od 127 bajtów w górę do

128 bajtów w dół)

128 bajtów w dół)

Opis symboliczny:

Opis symboliczny:

(PC)

(PC)

(PC) + przesunięcie

(PC) + przesunięcie

czyli zwiększ licznik rozkazów o przesunięcie (o liczbę

czyli zwiększ licznik rozkazów o przesunięcie (o liczbę

komórek)

komórek)

SPOSÓB PREZENTOWANIA ROZKAZU

SPOSÓB PREZENTOWANIA ROZKAZU

3.

3.

Format rozkazu

Format rozkazu

Jest to sposób rozmieszczenia informacji w kodzie rozkazu. Jest

Jest to sposób rozmieszczenia informacji w kodzie rozkazu. Jest

on następujący:

on następujący:

Kod

Kod

rozkazu

rozkazu

111010

111010

11

11

przemieszcze

przemieszcze

nie

nie

kod

kod

operacji

operacji

argument

argument

4.

4.

Ustawienie flagi

Ustawienie flagi

Istotną informacją jest określenie czy są ustawiane flagi (i

Istotną informacją jest określenie czy są ustawiane flagi (i

które) przy wykonaniu rozkazu. W tym przykładzie flagi nie są

które) przy wykonaniu rozkazu. W tym przykładzie flagi nie są

ustawiane.

ustawiane.

5.

5.

Szybkość wykonywania rozkazu

Szybkość wykonywania rozkazu

Szybkość podawana jest jako ilość taktów zegara procesora

Szybkość podawana jest jako ilość taktów zegara procesora

potrzebnych do wykonania rozkazu. W tym przykładzie

potrzebnych do wykonania rozkazu. W tym przykładzie

procesor 80386 wykonuje rozkaz w 7 taktach.

procesor 80386 wykonuje rozkaz w 7 taktach.

PRZYKŁADOWE ROZKAZY

PRZYKŁADOWE ROZKAZY

Rozkazy przesłań:

Rozkazy przesłań:

MOV -

MOV -

move

move

- przesłanie słowa między dwoma rejestrami

- przesłanie słowa między dwoma rejestrami

STR -

STR -

store

store

- przesłanie słowa ze wskazanego w rozkazie rejestru do

- przesłanie słowa ze wskazanego w rozkazie rejestru do

komórki pamięci

komórki pamięci

LD -

LD -

load

load

- przesłanie słowa z pamięci do wskazanego rejestru

- przesłanie słowa z pamięci do wskazanego rejestru

XCH -

XCH -

exchange

exchange

- wymiana zawartości rejestrów

- wymiana zawartości rejestrów

Rozkazy arytmetyczno-logiczne:

Rozkazy arytmetyczno-logiczne:

ADD -

ADD -

addition

addition

- dodawanie

- dodawanie

SUB -

SUB -

subtraction

subtraction

- odejmowanie

- odejmowanie

MUL -

MUL -

multiplication

multiplication

- mnożenie

- mnożenie

DIV -

DIV -

division

division

- dzielenie

- dzielenie

NEG -

NEG -

negate

negate

- negacja

- negacja

DEC -

DEC -

decrement

decrement

- zmniejszanie wartości o

- zmniejszanie wartości o

jeden

jeden

INC -

INC -

increment

increment

- awiększanie wartości o

- awiększanie wartości o

jeden

jeden

Rozkazy sterujące pracą programu:

Rozkazy sterujące pracą programu:

JMP -

JMP -

jump

jump

- skok bezwarunkowy do wyspecyfikowanego miejsca w

- skok bezwarunkowy do wyspecyfikowanego miejsca w

pamięci

pamięci

CALL -

CALL -

jump to subroutine

jump to subroutine

- wywołanie podprogramu

- wywołanie podprogramu

RET -

RET -

return

return

- skok powrotny z podprogramu

- skok powrotny z podprogramu

SKIP -

SKIP -

skip

skip

- przeskok przez jeden rozkaz

- przeskok przez jeden rozkaz

Rozkazy sterujące pracą procesora :

Rozkazy sterujące pracą procesora :

HALT -

HALT -

stop

stop

- zatrzymanie wykonania programu

- zatrzymanie wykonania programu

NOP -

NOP -

no operation

no operation

- rozkaz pusty

- rozkaz pusty

AND -

AND -

conjuction

conjuction

- iloczyn

- iloczyn

OR -

OR -

disjunction

disjunction

- suma

- suma

EXOR -

EXOR -

exclusive-OR

exclusive-OR

-suma mod 2

-suma mod 2

NOT -

NOT -

complement

complement

- negacja

- negacja

PAMIĘCI

PAMIĘCI

dr inż. Jacek FLOREK

dr inż. Jacek FLOREK

Instytut Informatyki

Instytut Informatyki

Podstawowe cechy i klasyfikacja

Podstawowe cechy i klasyfikacja

Pamięci RAM

Pamięci RAM

Pamięci dynamiczne RAM

Pamięci dynamiczne RAM

Pamięci ROM

Pamięci ROM

10

PARAMETRY PAMIĘCI

PARAMETRY PAMIĘCI

Pamięć jako układ przeznaczony do przechowywania informacji

Pamięć jako układ przeznaczony do przechowywania informacji

binarnej można scharakteryzować następującymi

binarnej można scharakteryzować następującymi

parametrami:

parametrami:

•

pojemność

pojemność

•

szybkość

szybkość

•

koszt

koszt

•

pobór mocy

pobór mocy

Pojemność pamięci

Pojemność pamięci

określa ilość informacji jaką można w niej

określa ilość informacji jaką można w niej

przechować wyrażoną w bitach, bajtach lub słowach.

przechować wyrażoną w bitach, bajtach lub słowach.

Pamięć dzielona jest na fragmenty (w zależności od typu

Pamięć dzielona jest na fragmenty (w zależności od typu

pamięci) umożliwiające adresowanie.

pamięci) umożliwiające adresowanie.

W pamięci operacyjnej są to fragmenty określane długością

W pamięci operacyjnej są to fragmenty określane długością

słowa (8, 16, 32, 64 bity). Pojemność określa się podając liczbę

słowa (8, 16, 32, 64 bity). Pojemność określa się podając liczbę

słów i długość słowa, np. 512Kx64 - 2

słów i długość słowa, np. 512Kx64 - 2

19

19

słów 64-bitowych

słów 64-bitowych

W pamięciach masowych fragmentami są sektory (setki lub

W pamięciach masowych fragmentami są sektory (setki lub

tysiące słów).

tysiące słów).

PARAMETRY PAMIĘCI

PARAMETRY PAMIĘCI

Szybkość pamięci

Szybkość pamięci

określa jak często procesor (lub inne

określa jak często procesor (lub inne

urządzenie) może z niej korzystać.

urządzenie) może z niej korzystać.

•

czas dostępu - czas od momentu żądania informacji z

czas dostępu - czas od momentu żądania informacji z

pamięci do momentu, w którym ta informacja ukaże się na

pamięci do momentu, w którym ta informacja ukaże się na

wyjściu pamięci

wyjściu pamięci

•

czas cyklu - najkrótszy czas jaki musi upłynąć pomiędzy

czas cyklu - najkrótszy czas jaki musi upłynąć pomiędzy

dwoma żądaniami dostępu do pamięci

dwoma żądaniami dostępu do pamięci

•

szybkość transmisji - określa ile bajtów (bitów) można

szybkość transmisji - określa ile bajtów (bitów) można

przesłać pomiędzy pamięcią a innym urządzeniem w

przesłać pomiędzy pamięcią a innym urządzeniem w

jednostce czasu.

jednostce czasu.

Koszt pamięci

Koszt pamięci

określa cenę jaką należy ponieść za uzyskanie

określa cenę jaką należy ponieść za uzyskanie

wysokich parametrów pamięci

wysokich parametrów pamięci

szybciej - drożej !!!

szybciej - drożej !!!

wolniej - taniej !!!

wolniej - taniej !!!

Pobór mocy

Pobór mocy

określa jakie jest

określa jakie jest

zapotrzebowanie energetyczne na realizację

zapotrzebowanie energetyczne na realizację

funkcji pamięci zwłaszcza przy dążeniu do

funkcji pamięci zwłaszcza przy dążeniu do

wzrostu jej pojemności

wzrostu jej pojemności

!

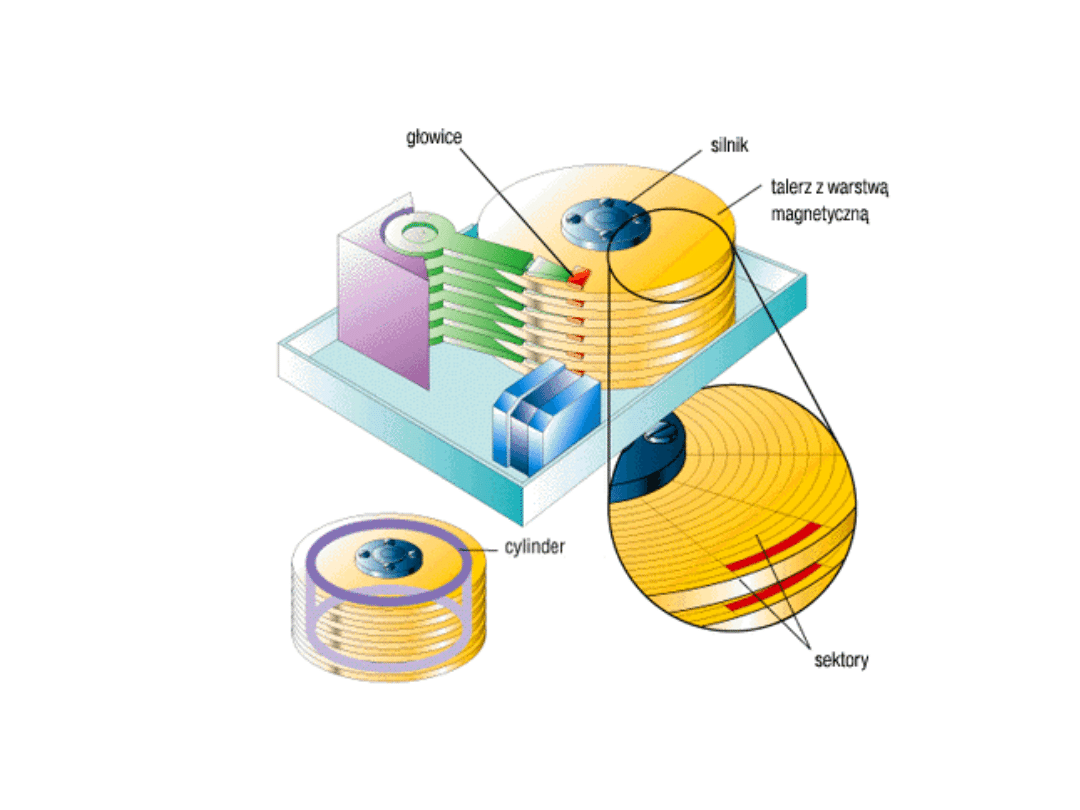

PAMIĘCI

PAMIĘCI

Rejestrowa

Rejestrowa

Kieszeniowa

Kieszeniowa

Operacyjna

Operacyjna

Masowa

Masowa

Zewnętrzna

Zewnętrzna

Z dostępem swobodnym

Z dostępem swobodnym

(bezpośrednim)

(bezpośrednim)

Z dostępem cyklicznym

Z dostępem cyklicznym

Z dostępem

Z dostępem

sekwencyjnym

sekwencyjnym

Z dostępem

Z dostępem

asocjacyjnym

asocjacyjnym

ROM

ROM

RAM

RAM

DRAM

DRAM

(dynamiczne)

(dynamiczne)

SRAM

SRAM

(statyczne)

(statyczne)

H

ie

ra

rc

h

ia

p

a

m

ię

c

i

H

ie

ra

rc

h

ia

p

a

m

ię

c

i

D

o

s

tę

p

d

o

i

n

fo

rm

a

c

ji

D

o

s

tę

p

d

o

i

n

fo

rm

a

c

ji

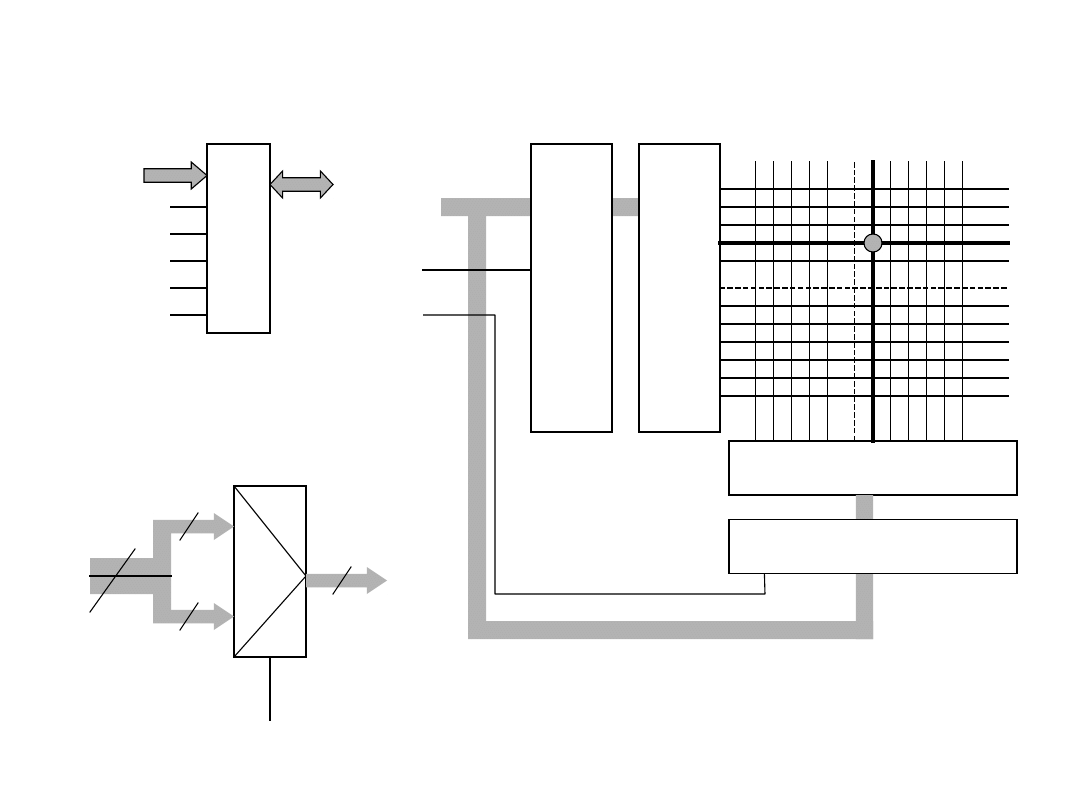

PAMIĘCI RAM

PAMIĘCI RAM

Def. Pamięcią RAM (

Def. Pamięcią RAM (

Random Access Memory

Random Access Memory

) nazywamy

) nazywamy

pamięć półprzewodnikową o dostępie swobodnym

pamięć półprzewodnikową o dostępie swobodnym

przeznaczoną do zapisu i odczytu. RAM jest pamięcią

przeznaczoną do zapisu i odczytu. RAM jest pamięcią

ulotną, co oznacza, że po wyłączeniu zasilania dane są

ulotną, co oznacza, że po wyłączeniu zasilania dane są

tracone.

tracone.

Def. Pamięcią RAM (

Def. Pamięcią RAM (

Random Access Memory

Random Access Memory

) nazywamy

) nazywamy

pamięć półprzewodnikową o dostępie swobodnym

pamięć półprzewodnikową o dostępie swobodnym

przeznaczoną do zapisu i odczytu. RAM jest pamięcią

przeznaczoną do zapisu i odczytu. RAM jest pamięcią

ulotną, co oznacza, że po wyłączeniu zasilania dane są

ulotną, co oznacza, że po wyłączeniu zasilania dane są

tracone.

tracone.

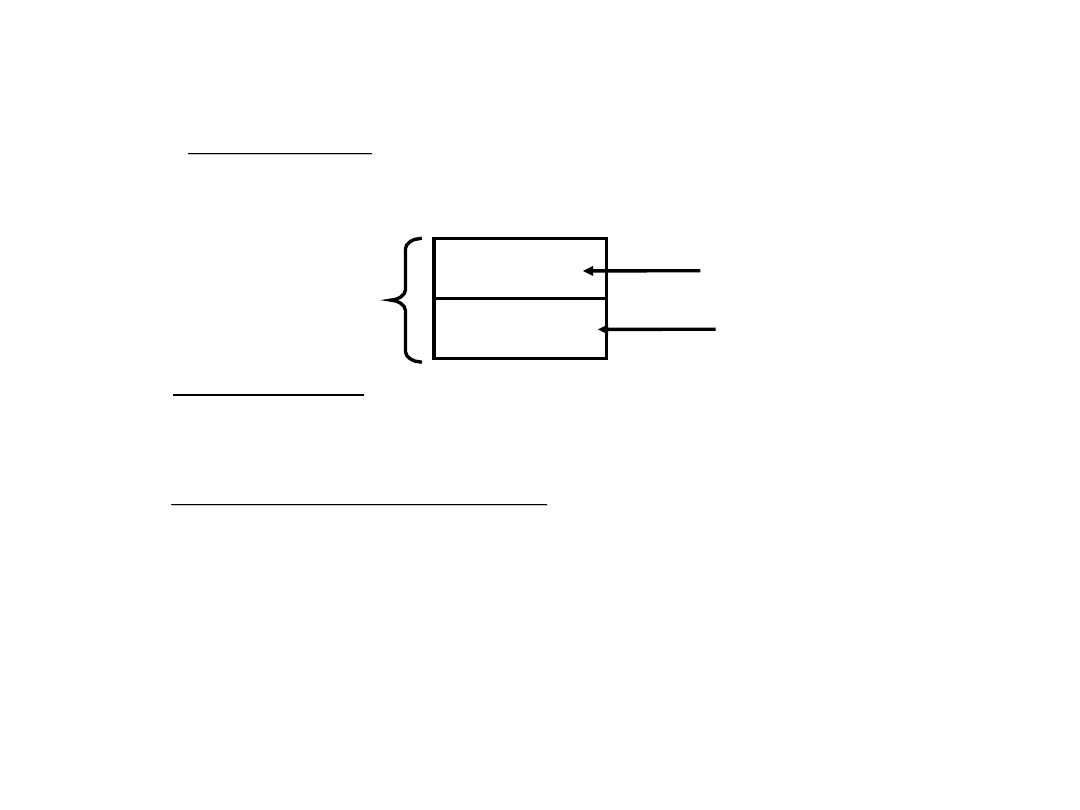

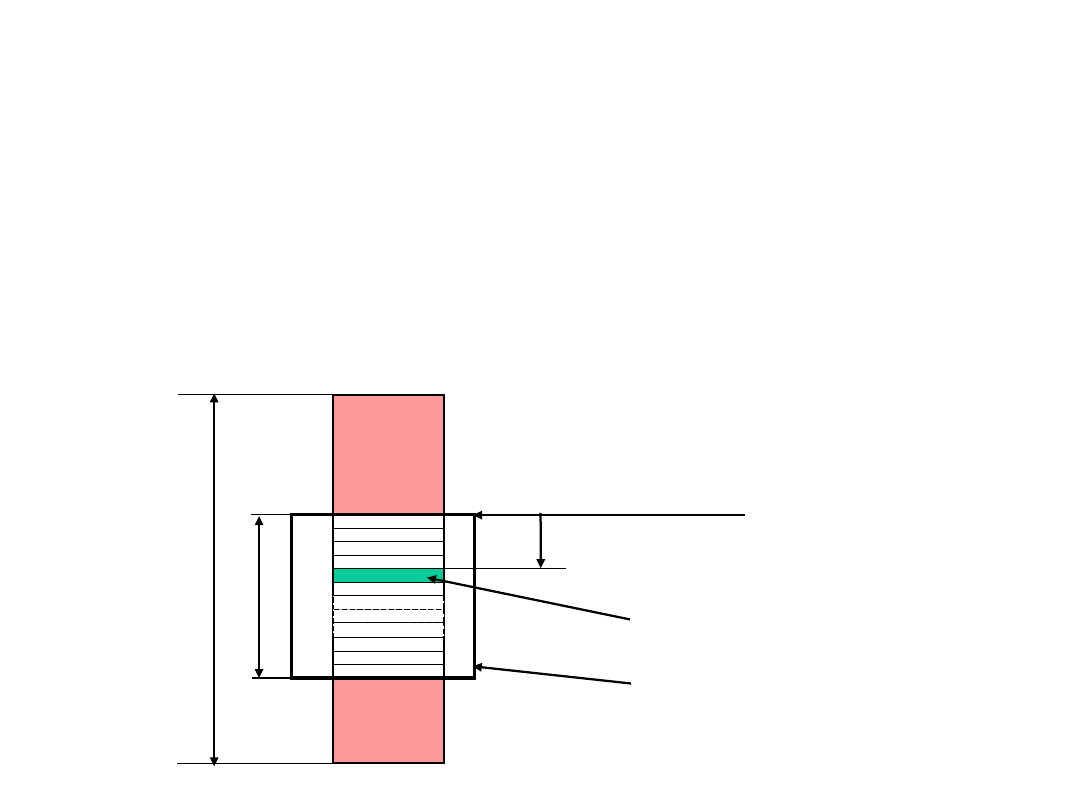

Pamięć

Pamięć

2

2

n

n

x m

x m

adres

adres

E

E

zapis/odcz

zapis/odcz

yt

yt

n

n

m

m

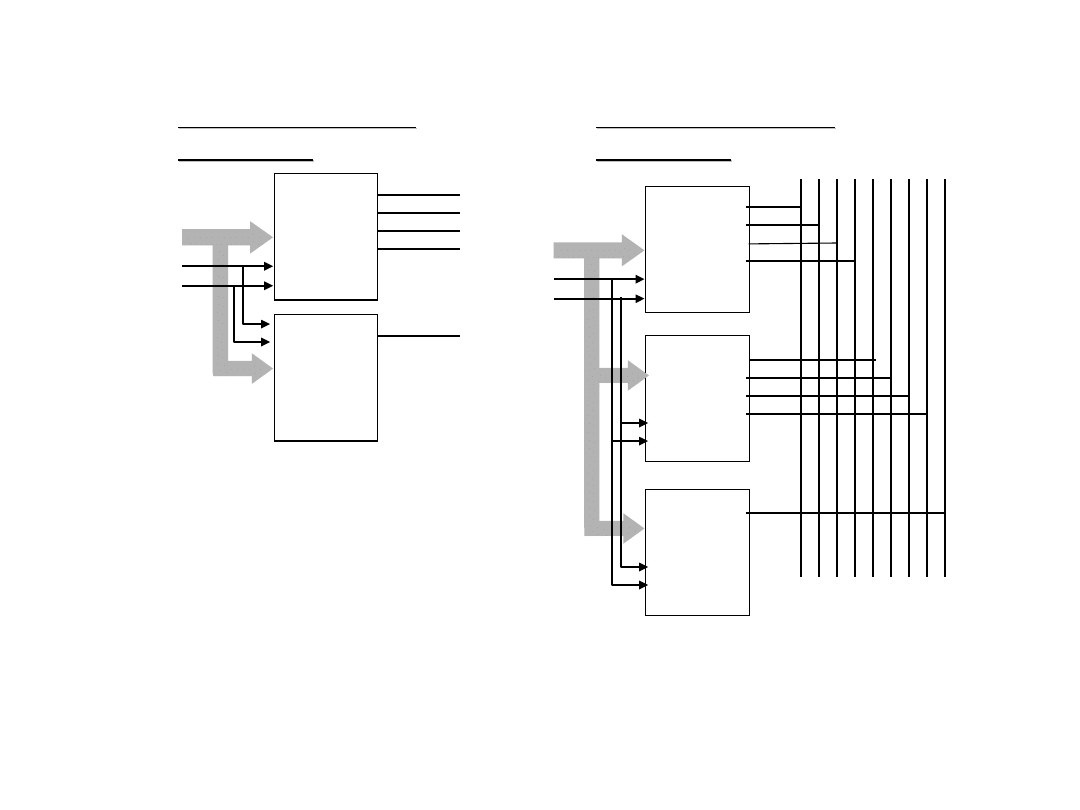

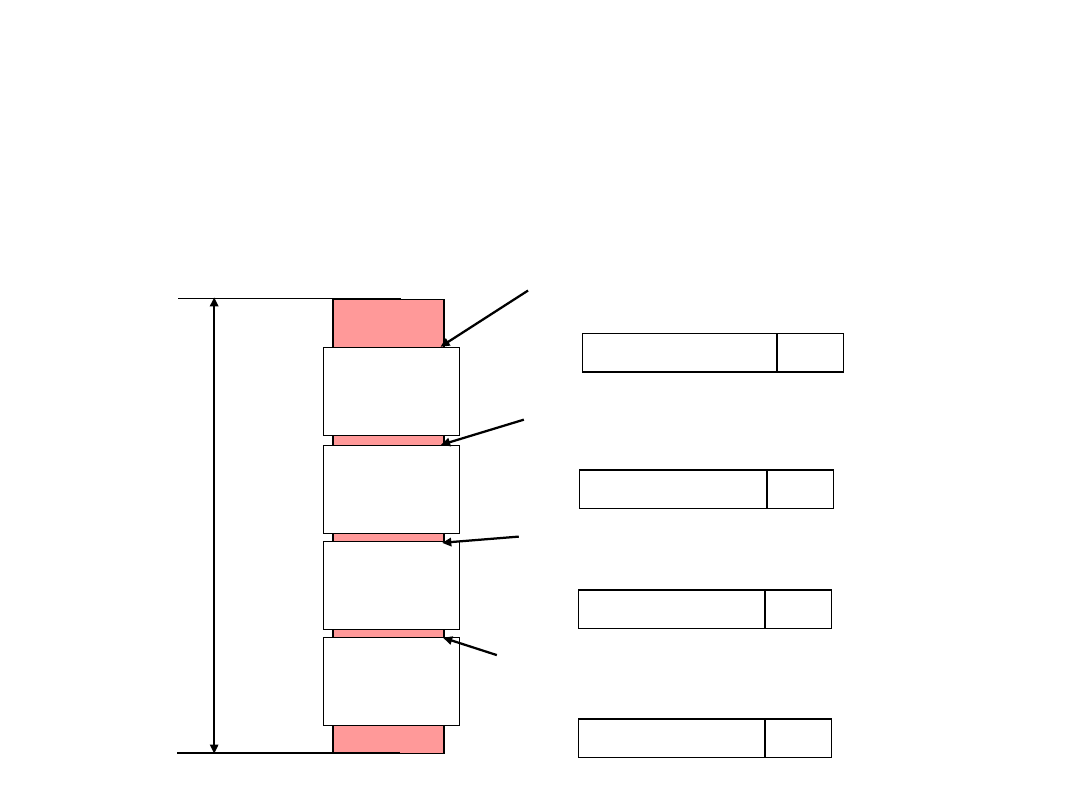

Łączenie układów pamięci dla zwiększenia

Łączenie układów pamięci dla zwiększenia

pojemności:

pojemności:

•

zwiększanie długości słowa

zwiększanie długości słowa

•

zwiększanie ilości słów

zwiększanie ilości słów

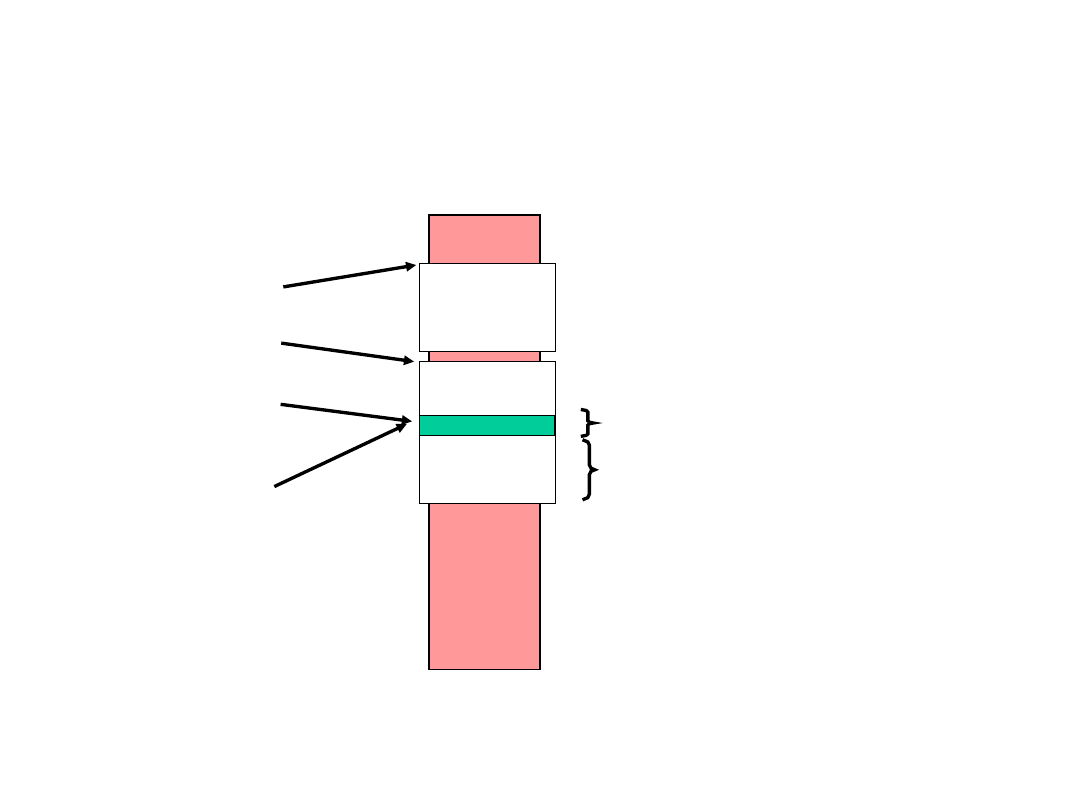

PAMIĘCI RAM

PAMIĘCI RAM

zwiększanie długości słowa (rozbudowa szyny danych)

zwiększanie długości słowa (rozbudowa szyny danych)

Pamięć

Pamięć

1M x 4b

1M x 4b

adres

adres

E

E

z/o

z/o

20

20

D0

D0

D1

D1

D2

D2

D3

D3

Pamięć

Pamięć

1M x 1b

1M x 1b

D0

D0

Pamięć 4Mb z bitem

Pamięć 4Mb z bitem

parzystości

parzystości

Pamięć 8Mb z bitem

Pamięć 8Mb z bitem

parzystości

parzystości

Pamięć

Pamięć

1M x 4b

1M x 4b

adres

adres

E

E

z/o

z/o

20

20

D0

D0

D1

D1

D2

D2

D3

D3

Pamięć

Pamięć

1M x 1b

1M x 1b

D0

D0

Pamięć

Pamięć

1M x 4b

1M x 4b

D0

D0

D1

D1

D2

D2

D3

D3

D0 D1 D2

D0 D1 D2

D3

D3

Sposób stosowany w budowie modułów SIMM (

Sposób stosowany w budowie modułów SIMM (

Single In Line

Single In Line

Module

Module

)

)

D4 D5 D6 D7 D8

D4 D5 D6 D7 D8

PAMIĘCI RAM

PAMIĘCI RAM

zwiększanie liczby słów (rozbudowa szyny adresowej)

zwiększanie liczby słów (rozbudowa szyny adresowej)

Pamięć

Pamięć

256k x 4b

256k x 4b

adres

adres

E

E

z/o

z/o

18

18

D0

D0

D1

D1

D2

D2

D3

D3

Pamięć 256k x 4b

Pamięć 256k x 4b

Pamięć

Pamięć

256k x 4b

256k x 4b

D

E

K

O

D

E

R

D

E

K

O

D

E

R

E

E

z/o

z/o

A

0

-

A

0

-

A

1

7

A

1

7

D0

D0

D1

D1

D2

D2

D3

D3

Pamięć 1M x 4b

Pamięć 1M x 4b

Pamięć

Pamięć

256k x 4b

256k x 4b

D0

D0

D1

D1

D2

D2

D3

D3

Pamięć

Pamięć

256k x 4b

256k x 4b

D0

D0

D1

D1

D2

D2

D3

D3

Pamięć

Pamięć

256k x 4b

256k x 4b

D0

D0

D1

D1

D2

D2

D3

D3

D3 D2 D1

D3 D2 D1

D0

D0

E

E

E

E

E

E

18

18

A

1

8

A

1

9

A

1

8

A

1

9

PAMIĘCI RAM

PAMIĘCI RAM

dynamiczne i statyczne

dynamiczne i statyczne

CECHY PAMIĘCI

CECHY PAMIĘCI

DRAM

DRAM

SRAM

SRAM

szybkość

szybkość

mała

mała

duża

duża

koszt

koszt

niski

niski

wysoki

wysoki

pojemność

pojemność

duża

duża

mała

mała

pobór mocy

pobór mocy

mały

mały

duży

duży

łatwość scalania

łatwość scalania

duża

duża

mała

mała

konieczność odświeżania

konieczność odświeżania

tak

tak

nie

nie

główne zastosowanie

główne zastosowanie

główna pamięć

główna pamięć

pamięć

pamięć

operacyjna

operacyjna

kieszeniowa

kieszeniowa

(

(

cache

cache

)

)

PAMIĘĆ DYNAMICZNA RAM (DRAM)

PAMIĘĆ DYNAMICZNA RAM (DRAM)

adres

adres

dane

dane

RAS#

RAS#

CAS#

CAS#

WE#

WE#

OE#

OE#

CE#

CE#

OE# - zezwolenie na odczyt

OE# - zezwolenie na odczyt

WE# - zezwolenie na zapis

WE# - zezwolenie na zapis

CE# - uaktywnianie (strob)

CE# - uaktywnianie (strob)

RAS# - syg.wprowadzania adresu do

RAS# - syg.wprowadzania adresu do

pamięci

pamięci

CAS# - -‘’-

CAS# - -‘’-

-‘’- -‘’- -‘’-

-‘’- -‘’- -‘’-

adres

adres

RAS#

RAS#

CAS#

CAS#

DEKODER

DEKODER

KOLUMN

KOLUMN

R

E

JE

S

T

R

A

D

R

E

S

U

R

E

JE

S

T

R

A

D

R

E

S

U

W

IE

R

S

Z

A

W

IE

R

S

Z

A

D

E

K

O

D

E

R

D

E

K

O

D

E

R

W

IE

R

S

Z

Y

W

IE

R

S

Z

Y

REJESTR ADRESU

REJESTR ADRESU

KOLUMNY

KOLUMNY

0 dla aktywnego sygnału

0 dla aktywnego sygnału

RAS#

RAS#

1 dla aktywnego sygnału

1 dla aktywnego sygnału

CAS#

CAS#

adres

adres

kolumny

kolumny

d

o

w

e

jś

c

ia

d

o

w

e

jś

c

ia

a

d

re

s

o

w

e

g

a

d

re

s

o

w

e

g

o

D

R

A

M

o

D

R

A

M

adres

adres

wiersz

wiersz

n

n

2

2

n

n

n

n

n

n

S

S

WE1

WE1

WE0

WE0

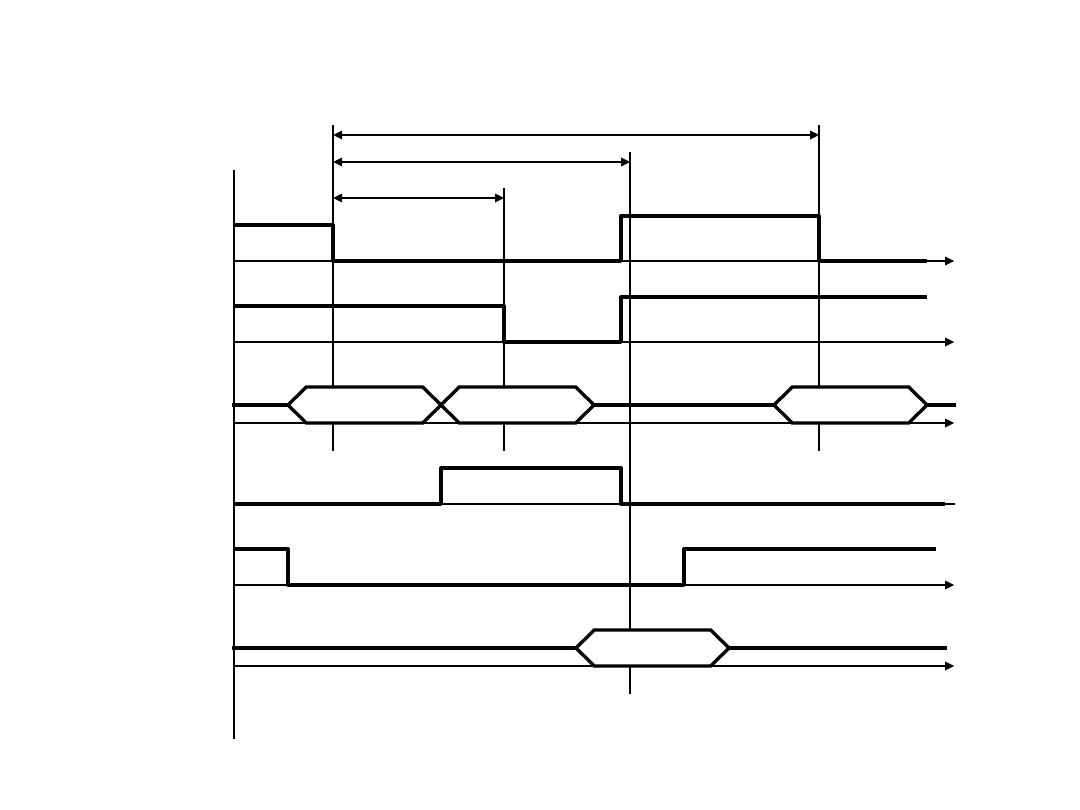

PAMIĘĆ DYNAMICZNA RAM (DRAM)

PAMIĘĆ DYNAMICZNA RAM (DRAM)

operacje odczytu

operacje odczytu

t

t

c

c

-

-

minimalny czas pomiędzy dwoma

minimalny czas pomiędzy dwoma

cyklami

cyklami

RAS#

RAS#

t

t

a

a

-

-

czas

czas

dostępu

dostępu

t

t

D RAS-CAS

D RAS-CAS

-

-

opóźnienie sygnału CAS# względem

opóźnienie sygnału CAS# względem

RAS#

RAS#

Wyjście

Wyjście

danych

danych

Adres

Adres

wiersza

wiersza

Ważne

Ważne

dane

dane

Adres

Adres

kolumny

kolumny

Adres

Adres

wiersza

wiersza

CAS#

CAS#

Wejścia

Wejścia

adresow

adresow

e

e

pamięci

pamięci

S

S

OE#

OE#

PAMIĘĆ DYNAMICZNA RAM (DRAM)

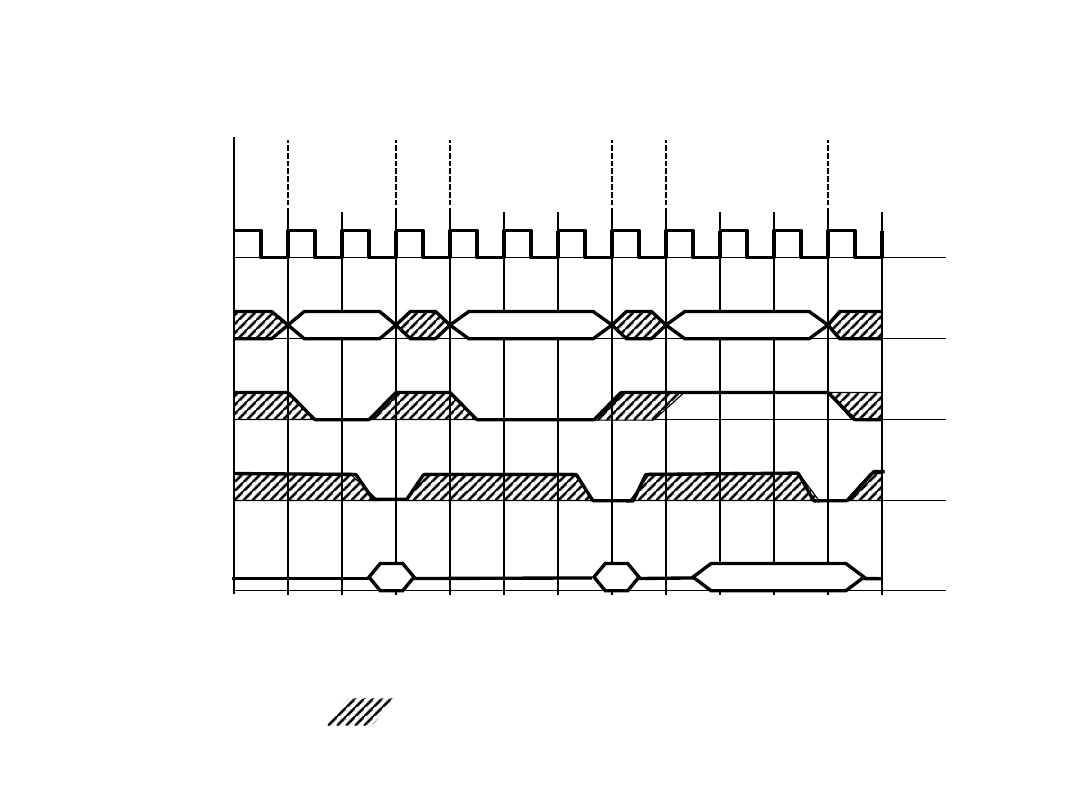

PAMIĘĆ DYNAMICZNA RAM (DRAM)

stany oczekiwania

stany oczekiwania

BCLK

BCLK

A23 - A0

A23 - A0

W/R#

W/R#

READY

READY

D15 - D0

D15 - D0

T

T

i

i

T

T

i

i

T

T

i

i

T

T

i

i

T

T

1

1

T

T

2

2

T

T

1

1

T

T

2

2

T

T

2

2

T

T

1

1

T

T

2

2

T

T

2

2

VA

VA

VA

VA

VA

VA

odczyt

odczyt

(0

(0

oczekiwania

oczekiwania

)

)

uśpienie

uśpienie

uśpienie

uśpienie

uśpienie

uśpienie

uśpienie

uśpienie

odczyt

odczyt

(1

(1

oczekiwania

oczekiwania

)

)

zapis

zapis

(1

(1

oczekiwania

oczekiwania

)

)

DO dane zapisywane

DO dane zapisywane

DI dane odczytywane

DI dane odczytywane

VA ważny adres

VA ważny adres

stan nieistotny

stan nieistotny

DI

DI

DI

DI

DO

DO

PAMIĘĆ DYNAMICZNA RAM (DRAM)

PAMIĘĆ DYNAMICZNA RAM (DRAM)

odświeżanie

odświeżanie

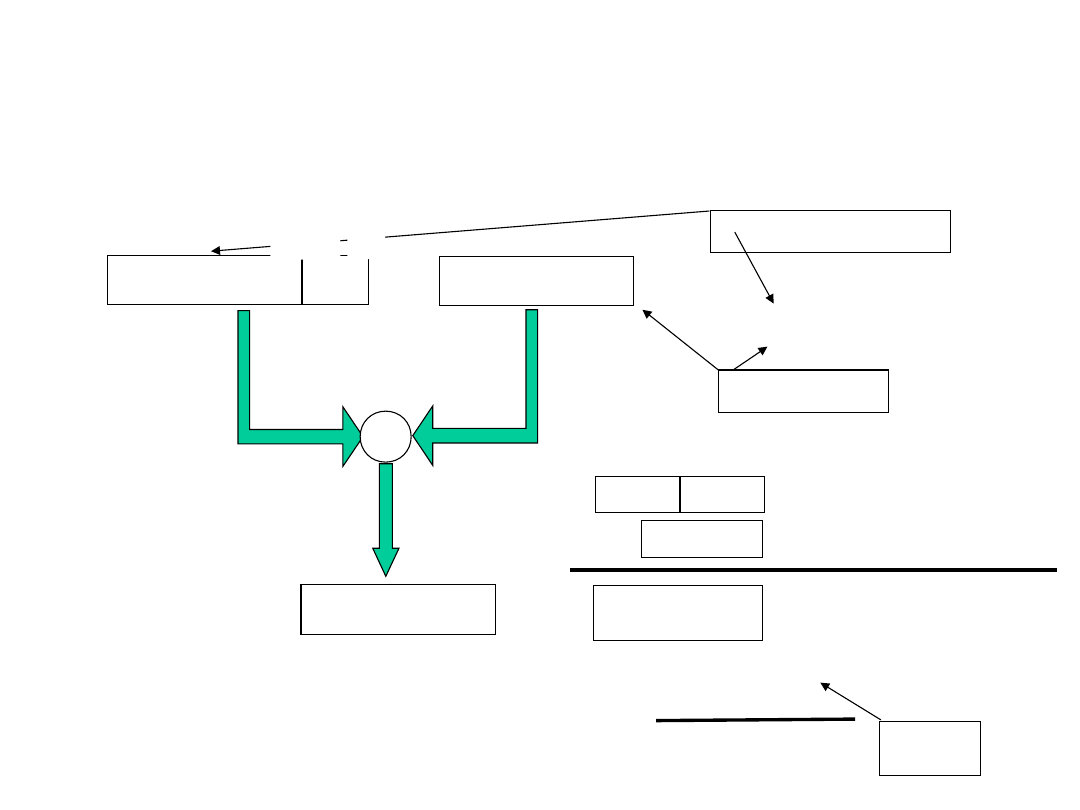

Odświeżanie komórek pamięci dynamicznych polega na cyklicznym

Odświeżanie komórek pamięci dynamicznych polega na cyklicznym

doładowaniu pojemności pamiętających przechowujących wartość

doładowaniu pojemności pamiętających przechowujących wartość

logiczną „1”.

logiczną „1”.

Operacja odświeżania realizowana jest przez specjalistyczne układy

Operacja odświeżania realizowana jest przez specjalistyczne układy

logiczne, będące elementem płyty głównej komputera.

logiczne, będące elementem płyty głównej komputera.

Istnieją cztery podstawowe sposoby odświeżania pamięci

Istnieją cztery podstawowe sposoby odświeżania pamięci

dynamicznych RAM:

dynamicznych RAM:

•

sygnałem RAS (tryb wierszowy)

sygnałem RAS (tryb wierszowy)

•

sygnałem CAS przed RAS (tryb statyczny)

sygnałem CAS przed RAS (tryb statyczny)

•

odświeżanie ukryte

odświeżanie ukryte

•

autoodświeżanie

autoodświeżanie

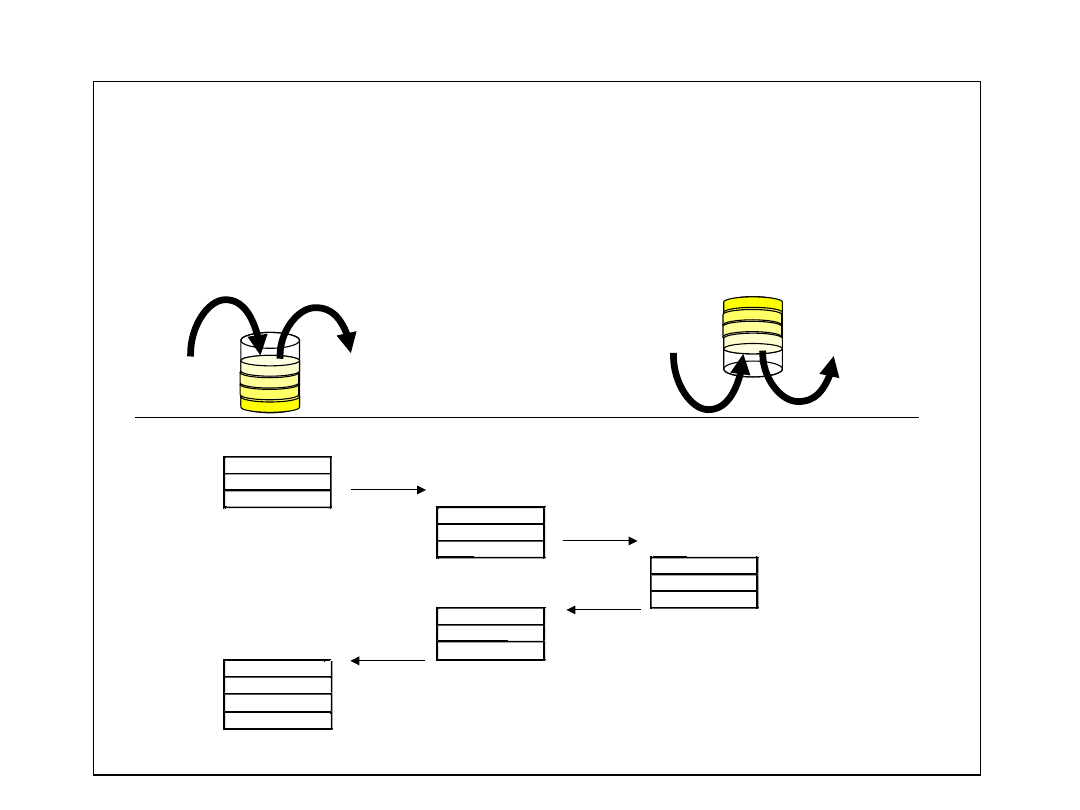

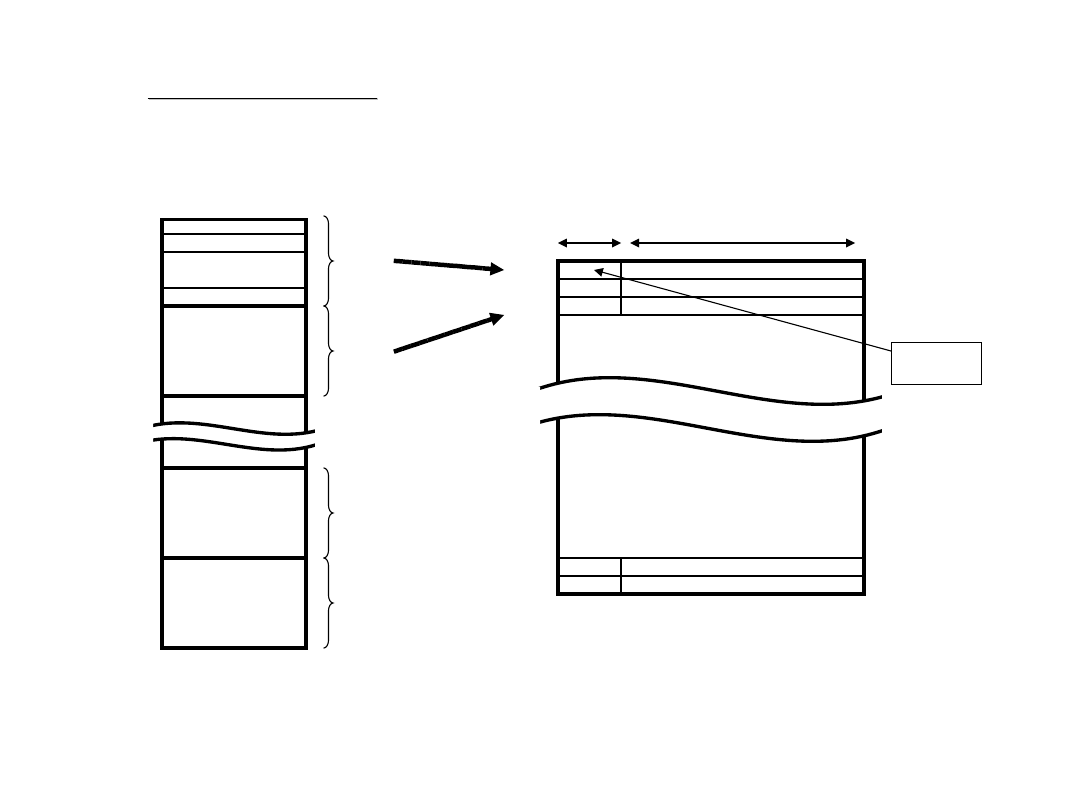

PAMIĘĆ KIESZENIOWA (STATYCZNA)

PAMIĘĆ KIESZENIOWA (STATYCZNA)

RAM

RAM

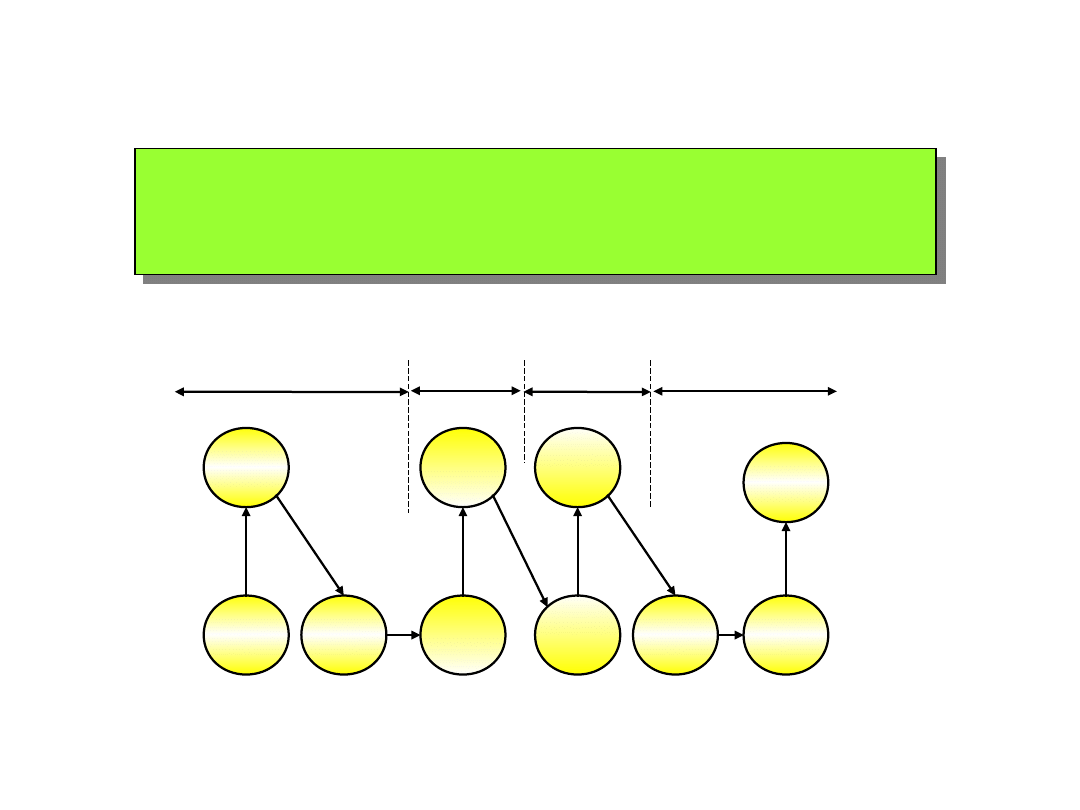

Zjawisko lokalności

Zjawisko lokalności

- procesor odwołuje się najczęściej do pamięci

- procesor odwołuje się najczęściej do pamięci

(

(

trafienie

trafienie

) w pewnym niewielkim obszarze (w okolicach danego

) w pewnym niewielkim obszarze (w okolicach danego

programu) - bardzo rzadko do obszarów odległych. Stąd stosowanie

programu) - bardzo rzadko do obszarów odległych. Stąd stosowanie

szybkich pamięci kieszeniowych (cache) zawierających właśnie taki

szybkich pamięci kieszeniowych (cache) zawierających właśnie taki

lokalny obszar pamięci.

lokalny obszar pamięci.

0

0

1

1

q-1

q-1

1 blok

1 blok

2 blok

2 blok

k-1 blok

k-1 blok

k-2 blok

k-2 blok

...

...

0

0

1

1

m-1

m-1

2

2

m-2

m-2

q słów

q słów

log

log

2

2

k

k

pamięć operacyjna

pamięć operacyjna

pamięć kieszeniowa

pamięć kieszeniowa

zawiera tylko

zawiera tylko

m

m

spośród

spośród

k

k

bloków

bloków

(k>>m)

(k>>m)

Gdy procesor zażąda dostępu do bloku, którego nie ma w pamięci cache

Gdy procesor zażąda dostępu do bloku, którego nie ma w pamięci cache

(

(

chybienie

chybienie

) to następuje wymiana zawartości jednej komórki pamięci

) to następuje wymiana zawartości jednej komórki pamięci

kieszeniowej.

kieszeniowej.

Nr

Nr

bloku

bloku

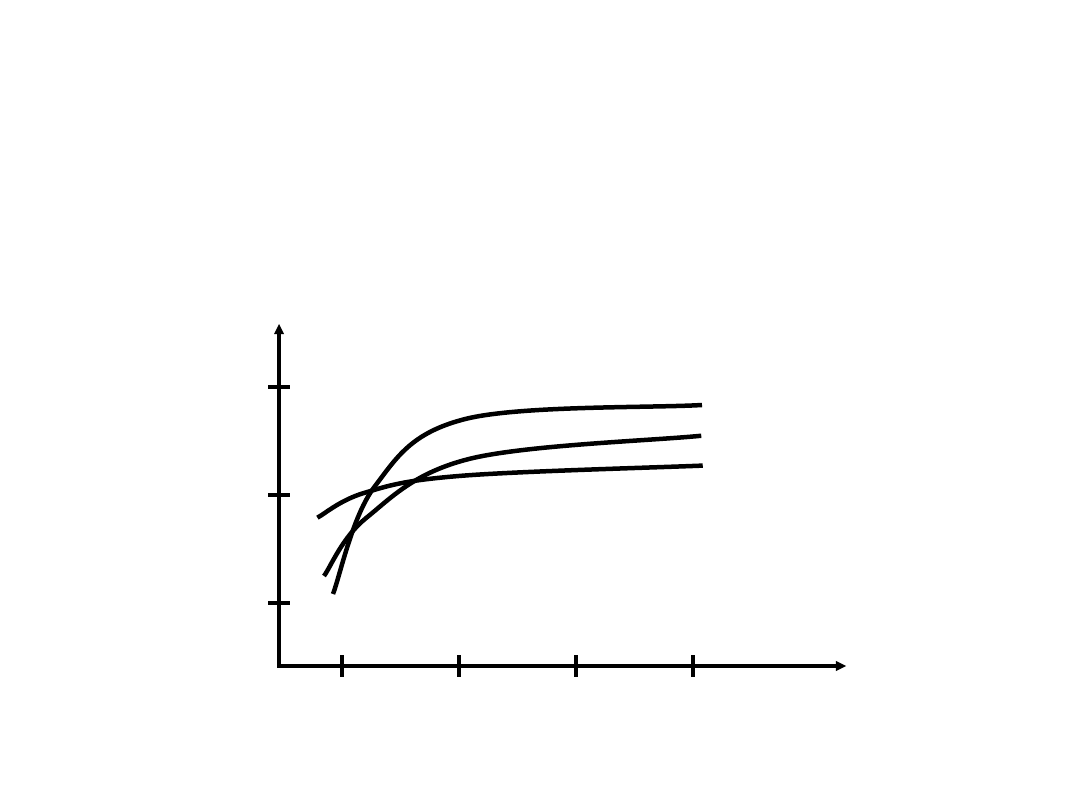

PAMIĘĆ KIESZENIOWA (STATYCZNA)

PAMIĘĆ KIESZENIOWA (STATYCZNA)

RAM

RAM

H - współczynnik

H - współczynnik

trafienia

trafienia

Jeżeli założymy pojemność pamięci operacyjnej: 8192 bloki (k) po 8 bajtów (q)

Jeżeli założymy pojemność pamięci operacyjnej: 8192 bloki (k) po 8 bajtów (q)

tj. 8192*8 = 65536B = 64KB

tj. 8192*8 = 65536B = 64KB

oraz pojemność pamięci kieszeniowej m=128 linii

oraz pojemność pamięci kieszeniowej m=128 linii

to długość linii pamięci kieszeniowej wyniesie

to długość linii pamięci kieszeniowej wyniesie

s=8*q + log

s=8*q + log

2

2

k = 8*8 + log

k = 8*8 + log

2

2

8193 = 64+13=77bitów

8193 = 64+13=77bitów

q = 8

q = 8

q =

q =

64

64

q =

q =

16

16

0,3

0,3

0,6

0,6

0,9

0,9

5 kB

5 kB

10 kB

10 kB

15 kB

15 kB

20 kB

20 kB

pojemność pamięci

pojemność pamięci

kieszeniowej

kieszeniowej

PAMIĘCI ROM

PAMIĘCI ROM

Def. Pamięcią ROM (

Def. Pamięcią ROM (

Read Only Memory

Read Only Memory

) nazywamy pamięć

) nazywamy pamięć

półprzewodnikową o dostępie swobodnym przeznaczoną

półprzewodnikową o dostępie swobodnym przeznaczoną

tylko do odczytu uprzednio zapisanych danych. Oznacza

tylko do odczytu uprzednio zapisanych danych. Oznacza

to, że nie można do niej zapisywać danych w trakcie

to, że nie można do niej zapisywać danych w trakcie

normalnej pracy w systemie. ROM jest pamięcią

normalnej pracy w systemie. ROM jest pamięcią

nieulotną, co oznacza, że po wyłączeniu zasilania dane

nieulotną, co oznacza, że po wyłączeniu zasilania dane

nie są tracone.

nie są tracone.

Def. Pamięcią ROM (

Def. Pamięcią ROM (

Read Only Memory

Read Only Memory

) nazywamy pamięć

) nazywamy pamięć

półprzewodnikową o dostępie swobodnym przeznaczoną

półprzewodnikową o dostępie swobodnym przeznaczoną

tylko do odczytu uprzednio zapisanych danych. Oznacza

tylko do odczytu uprzednio zapisanych danych. Oznacza

to, że nie można do niej zapisywać danych w trakcie

to, że nie można do niej zapisywać danych w trakcie

normalnej pracy w systemie. ROM jest pamięcią

normalnej pracy w systemie. ROM jest pamięcią

nieulotną, co oznacza, że po wyłączeniu zasilania dane

nieulotną, co oznacza, że po wyłączeniu zasilania dane

nie są tracone.

nie są tracone.

•

MROM (

MROM (

mascable ROM

mascable ROM

) zawartość pamięci ustalana jest w

) zawartość pamięci ustalana jest w

procesie produkcji (za pomocą odpowiednich masek) - BIOS do

procesie produkcji (za pomocą odpowiednich masek) - BIOS do

obsługi klawiatury

obsługi klawiatury

•

PROM (

PROM (

programmable ROM

programmable ROM

) pamięć jednokrotnie programowalna

) pamięć jednokrotnie programowalna

przez użytkownika - obecnie nieużywana

przez użytkownika - obecnie nieużywana

•

EPROM pamięć wielokrotnie programowalna w ultrafioletowych

EPROM pamięć wielokrotnie programowalna w ultrafioletowych

programatorach - obecnie wychodzi z użycia

programatorach - obecnie wychodzi z użycia

•

EEPROM pamięć kasowana i programowana na drodze

EEPROM pamięć kasowana i programowana na drodze

elektrycznej (podobnie jak RAM ale czas zapisu jest

elektrycznej (podobnie jak RAM ale czas zapisu jest

nieporównywalnie długi) - flash-BIOS (uaktualniany BIOS)

nieporównywalnie długi) - flash-BIOS (uaktualniany BIOS)

UKŁADY I OPERACJE WEJŚCIA/WYJŚCIA

UKŁADY I OPERACJE WEJŚCIA/WYJŚCIA

dr inż. Jacek FLOREK

dr inż. Jacek FLOREK

Instytut Informatyki

Instytut Informatyki

Układy wejścia/wyjścia

Układy wejścia/wyjścia

Operacje wejścia/wyjścia

Operacje wejścia/wyjścia

11

UKŁDY WEJŚCIA/WYJŚCIA

UKŁDY WEJŚCIA/WYJŚCIA

Def. Układem we/wy nazywamy układ elektroniczny

Def. Układem we/wy nazywamy układ elektroniczny

pośredniczący w wymianie informacji pomiędzy

pośredniczący w wymianie informacji pomiędzy

mikroprocesorem i pamięcią systemu z jednej strony a

mikroprocesorem i pamięcią systemu z jednej strony a

urządzeniem peryferyjnym (zewnętrznym urządzeniem

urządzeniem peryferyjnym (zewnętrznym urządzeniem

współpracującym) z drugiej.

współpracującym) z drugiej.

Dla systemu mikroprocesorowego układ we/wy widoczny

Dla systemu mikroprocesorowego układ we/wy widoczny

jest jako rejestr lub zespół rejestrów o określonych

jest jako rejestr lub zespół rejestrów o określonych

adresach oraz pewien zestaw sygnałów sterujących.

adresach oraz pewien zestaw sygnałów sterujących.

Def. Układem we/wy nazywamy układ elektroniczny

Def. Układem we/wy nazywamy układ elektroniczny

pośredniczący w wymianie informacji pomiędzy

pośredniczący w wymianie informacji pomiędzy

mikroprocesorem i pamięcią systemu z jednej strony a

mikroprocesorem i pamięcią systemu z jednej strony a

urządzeniem peryferyjnym (zewnętrznym urządzeniem

urządzeniem peryferyjnym (zewnętrznym urządzeniem

współpracującym) z drugiej.

współpracującym) z drugiej.

Dla systemu mikroprocesorowego układ we/wy widoczny

Dla systemu mikroprocesorowego układ we/wy widoczny

jest jako rejestr lub zespół rejestrów o określonych

jest jako rejestr lub zespół rejestrów o określonych

adresach oraz pewien zestaw sygnałów sterujących.