1

I

T

P

W

ZPT

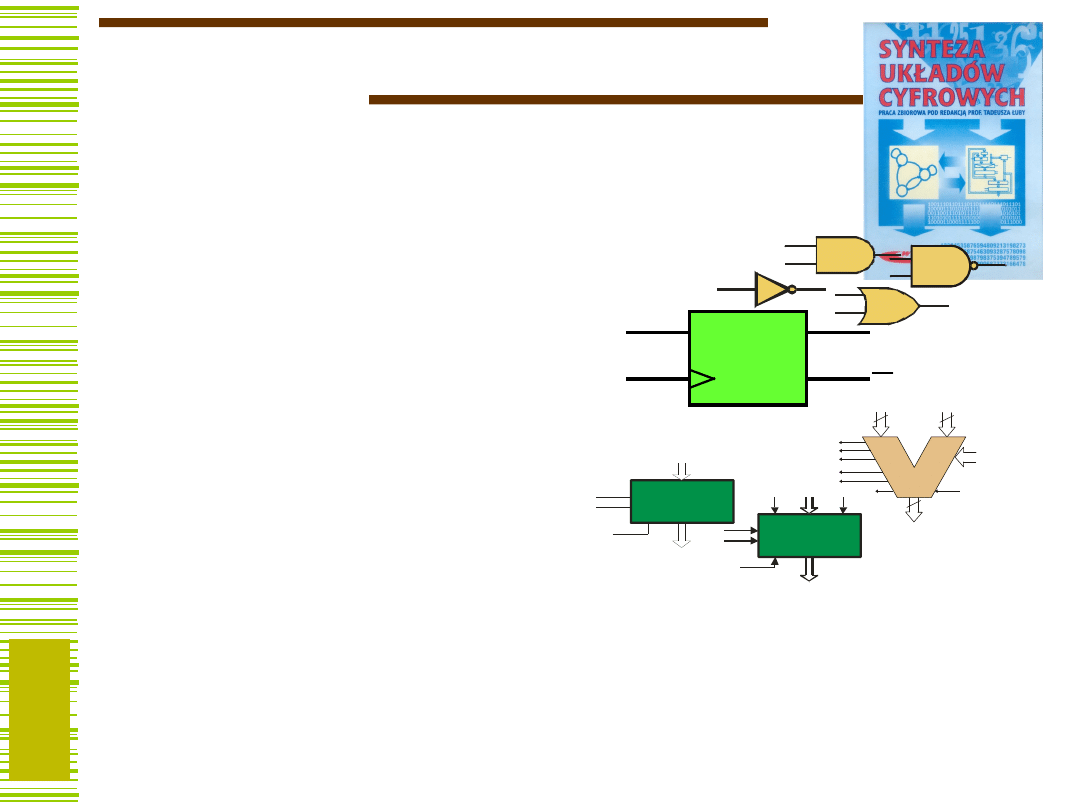

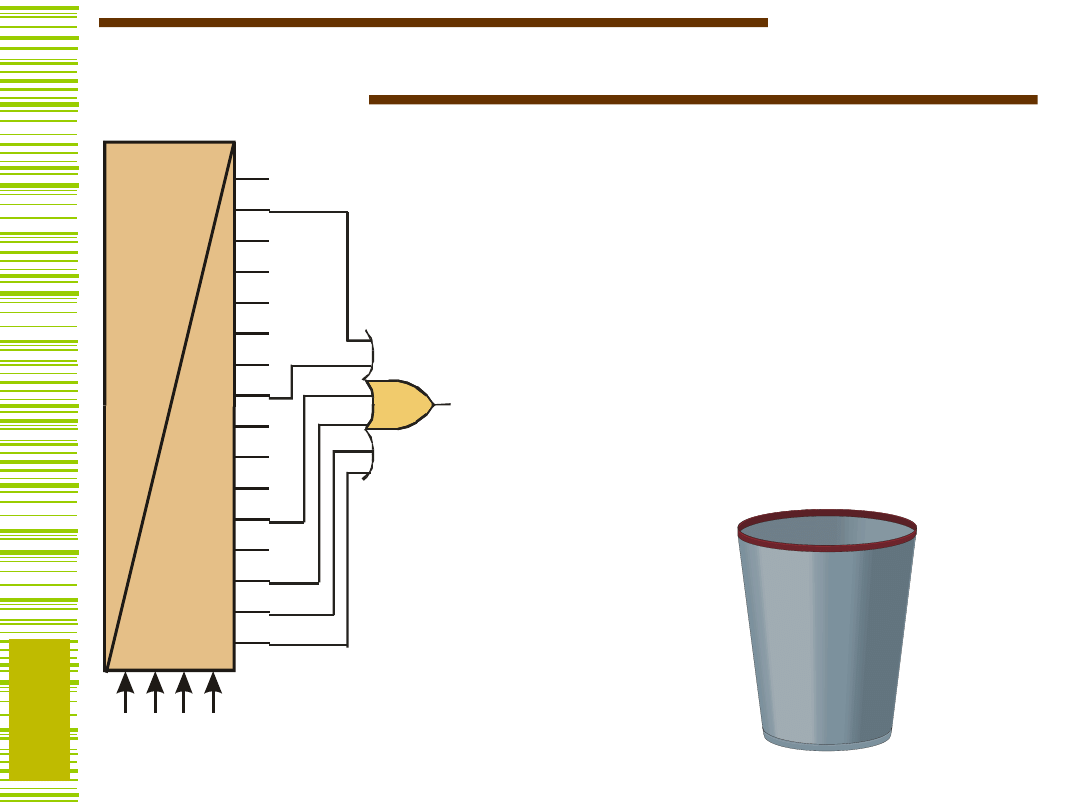

Układy cyfrowe

Układy logiczne (cyfrowe)

konstruowane są w różnych

technologiach i na różnych poziomach

opisu.

Poziomy opisu:

1) Bramki i elementarne

układy pamięciowe

(przerzutniki)

2) Bloki funkcjonalne: układy

arytmetyczne (sumatory),

liczniki, rejestry.

Tworzą one nowe elementy konstrukcyjne, z których

buduje się złożone układy cyfrowe o różnorodnych

zastosowaniach: układy przetwarzania sygnałów,

układy sterowania, specjalizowane procesory, układy

kryptograficzne

Przerzutn

ik

typu D

D

D

Clk

Clk

Q

Q

Y

B

A

n

n

n

Y

n - 1

Z

O V R

P

G

c

n

c

0

S

A L U

R

(Q)

s

1

s

2

clock

X

Y

x

l

x

p

L

(Q)

s

1

s

2

clock

X

Y

2

I

T

P

W

ZPT

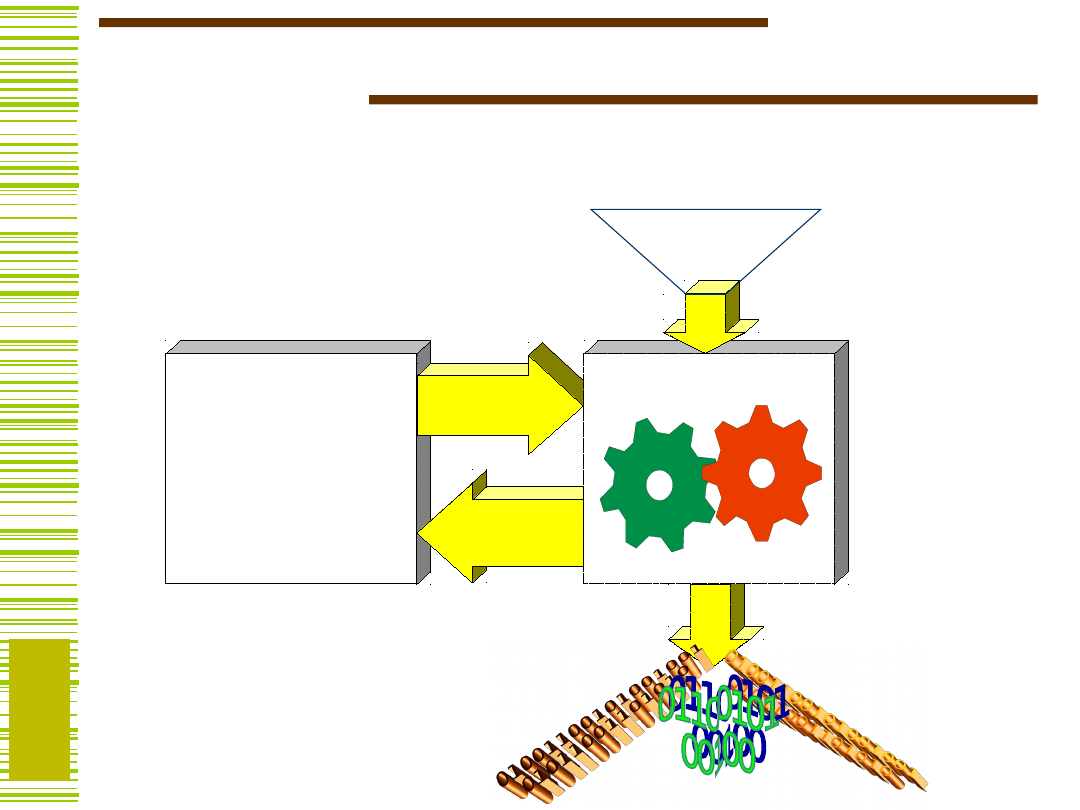

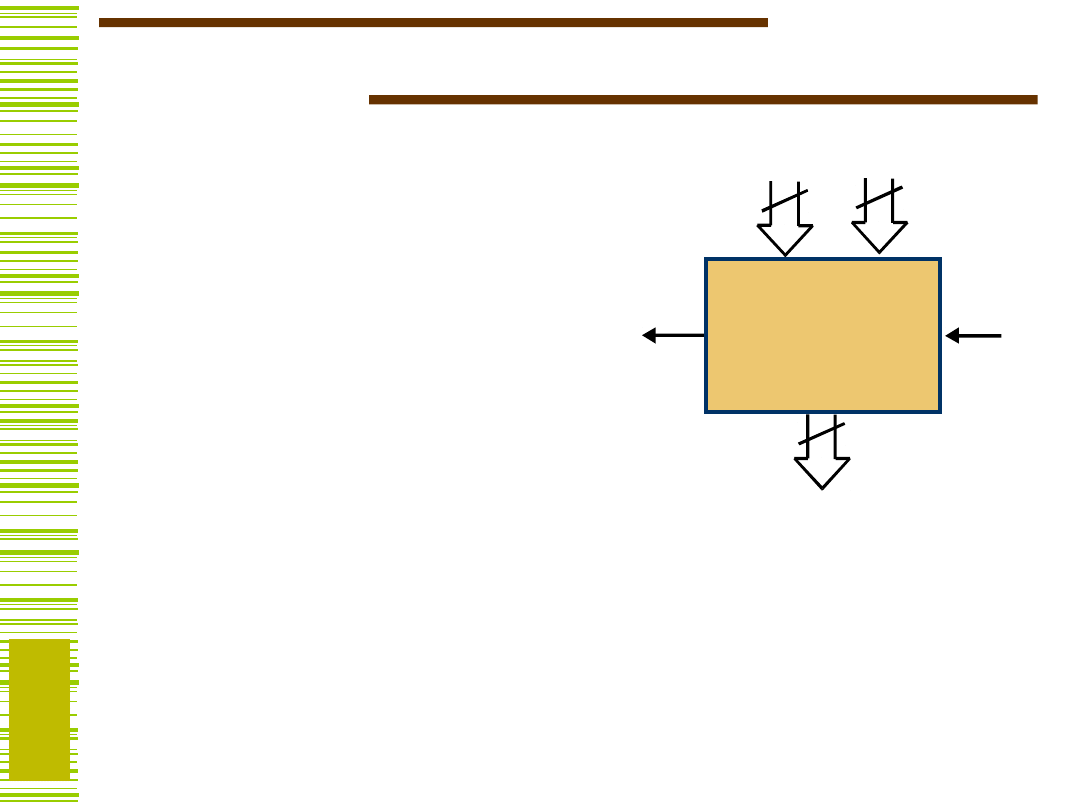

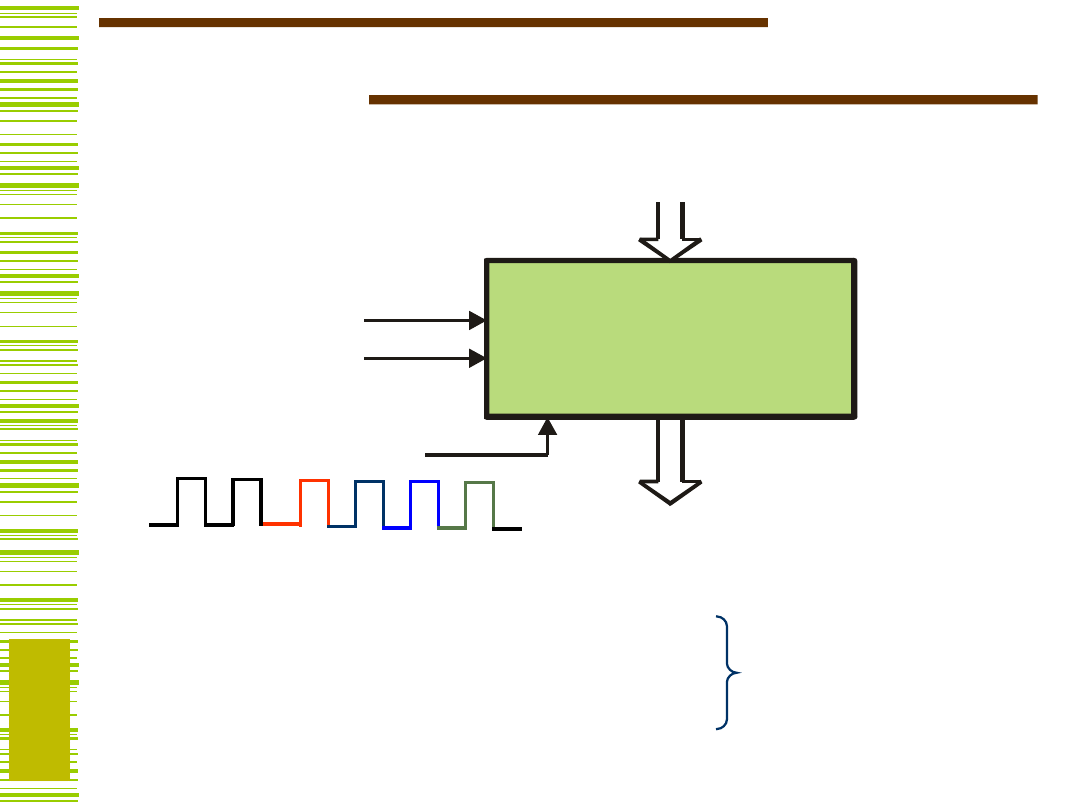

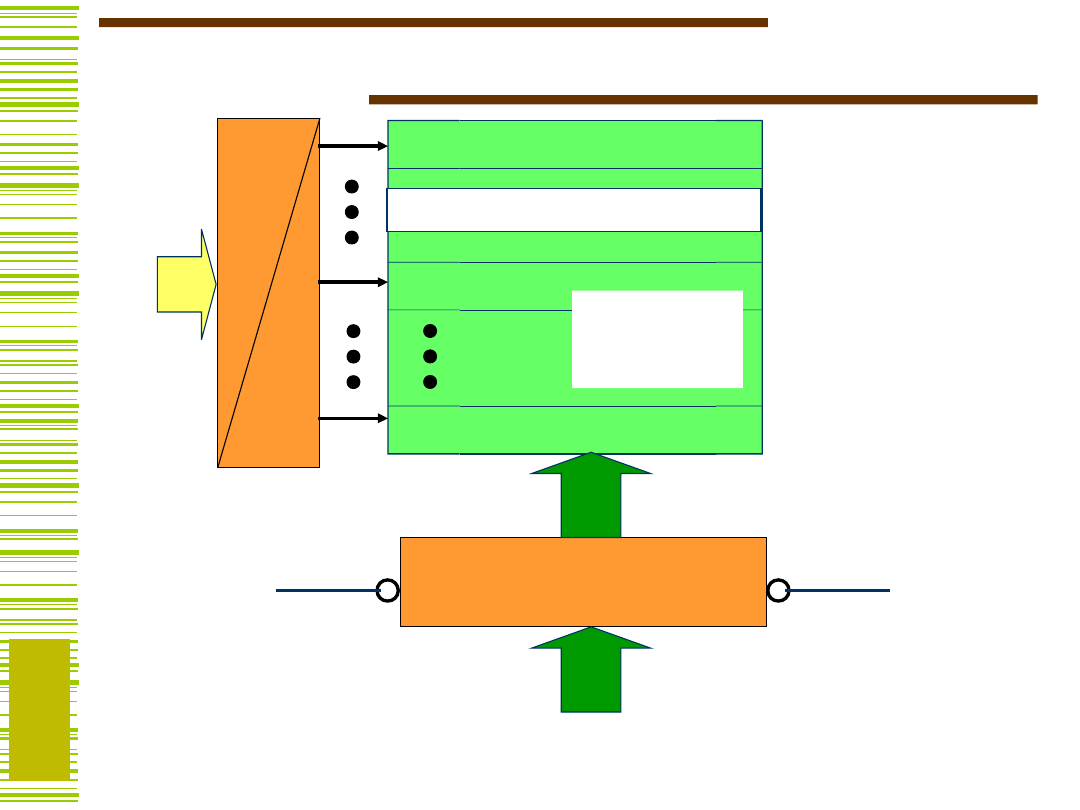

Układ

sterujący

(kontroler

)

Dane wyjściowe

Dane

wejściowe

Sygnały

sterujące

Stan części

operacyjnej

Układ operacyjny

(Datapath)

System cyfrowy

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Mikrooperacje

wywoływane przez

sygnały sterujące

3

I

T

P

W

ZPT

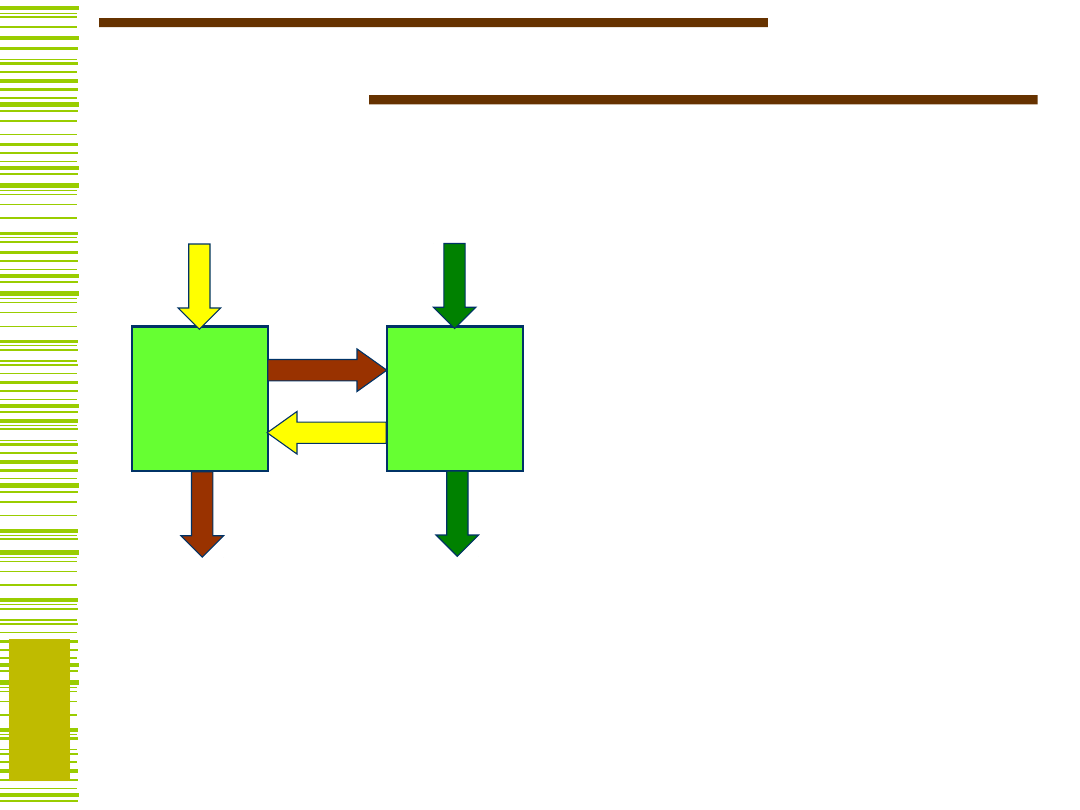

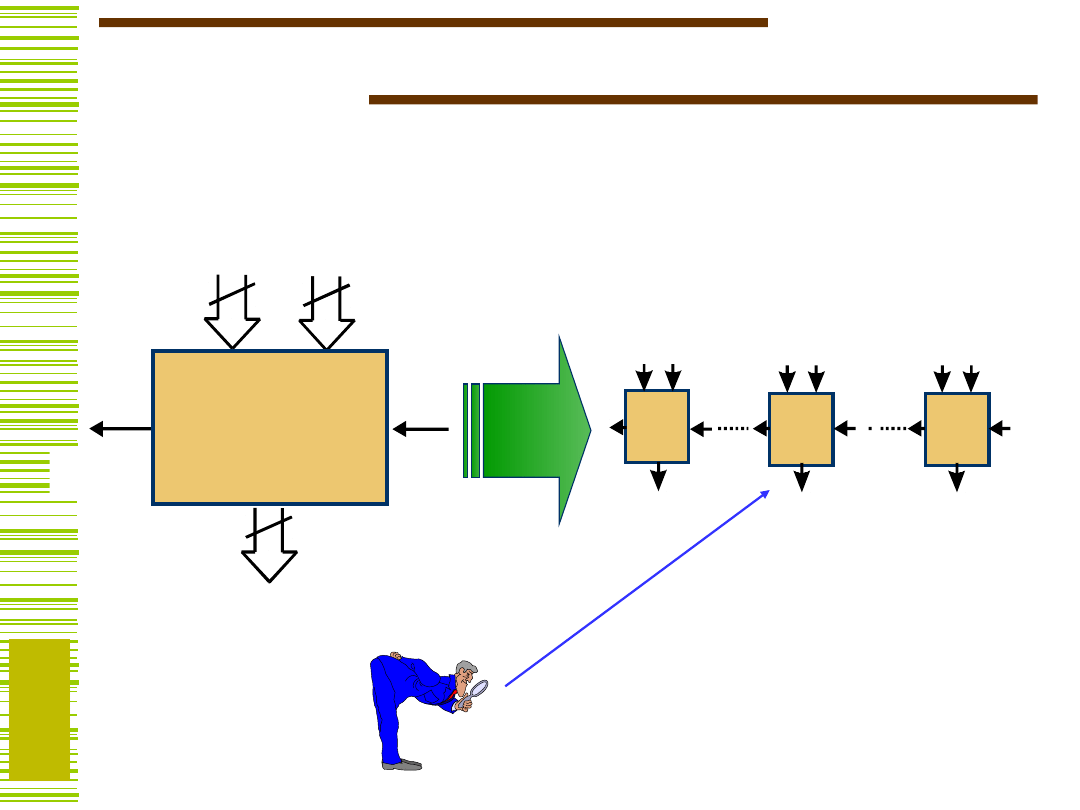

System cyfrowy…

D, F - przetwarzana

informacja (wektory

binarne),

UO - układ operacyjny

US - układ sterujący

X

Z

X

P

Z

Y

Z

D

F

X - sygnały warunków,

Z - sygnały sterujące

(mikrorozkazy)

US

UO

4

I

T

P

W

ZPT

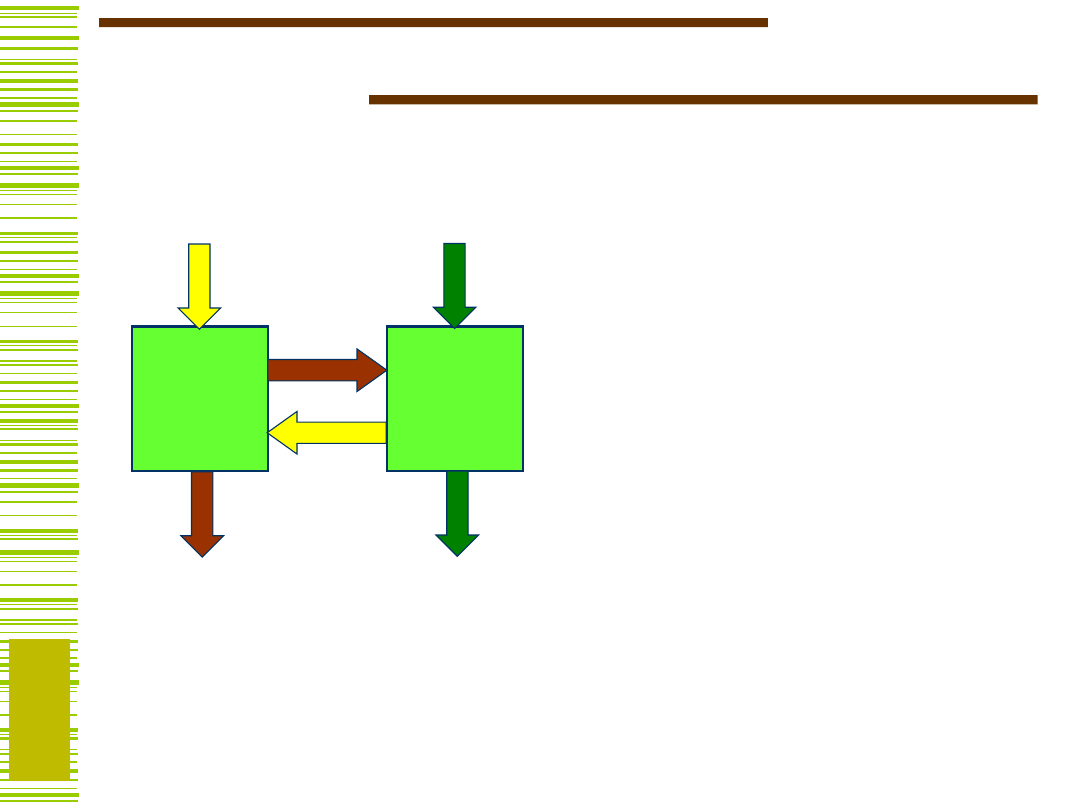

System cyfrowy - realizacja

UO – z bloków funkcjonalnych

US – automat

lub układ mikroprogramowany

X

Z

X

P

Z

Y

Z

D

F

US

UO

5

I

T

P

W

ZPT

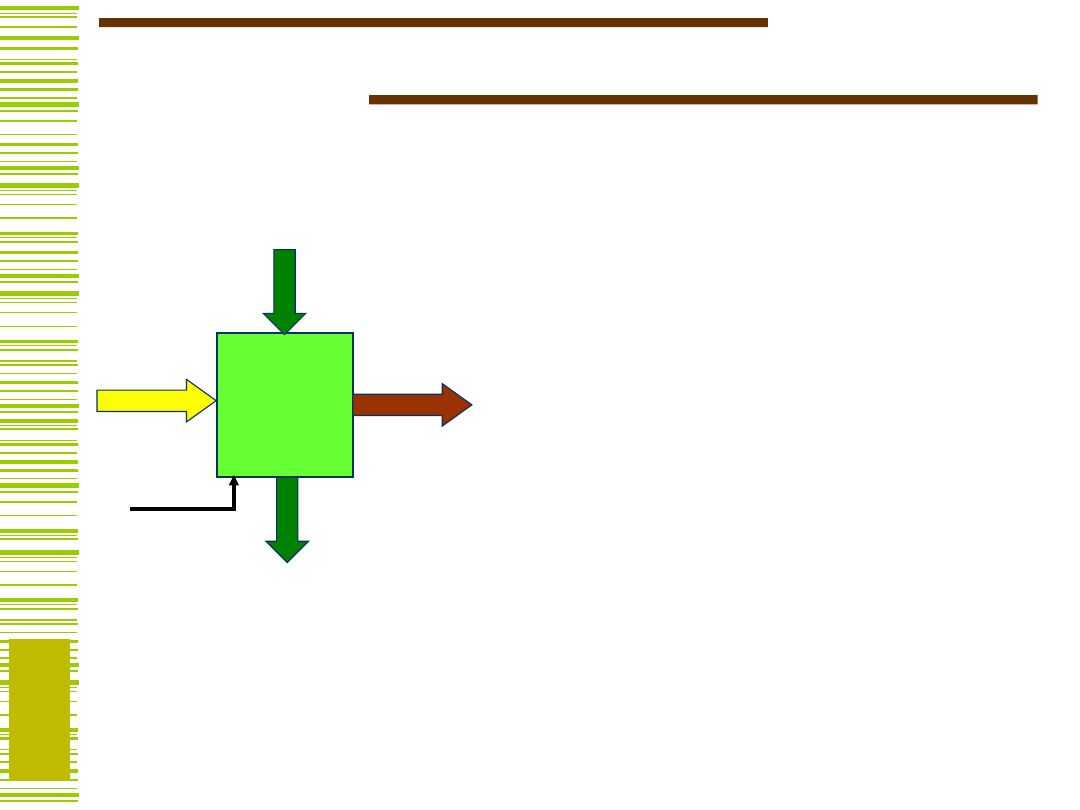

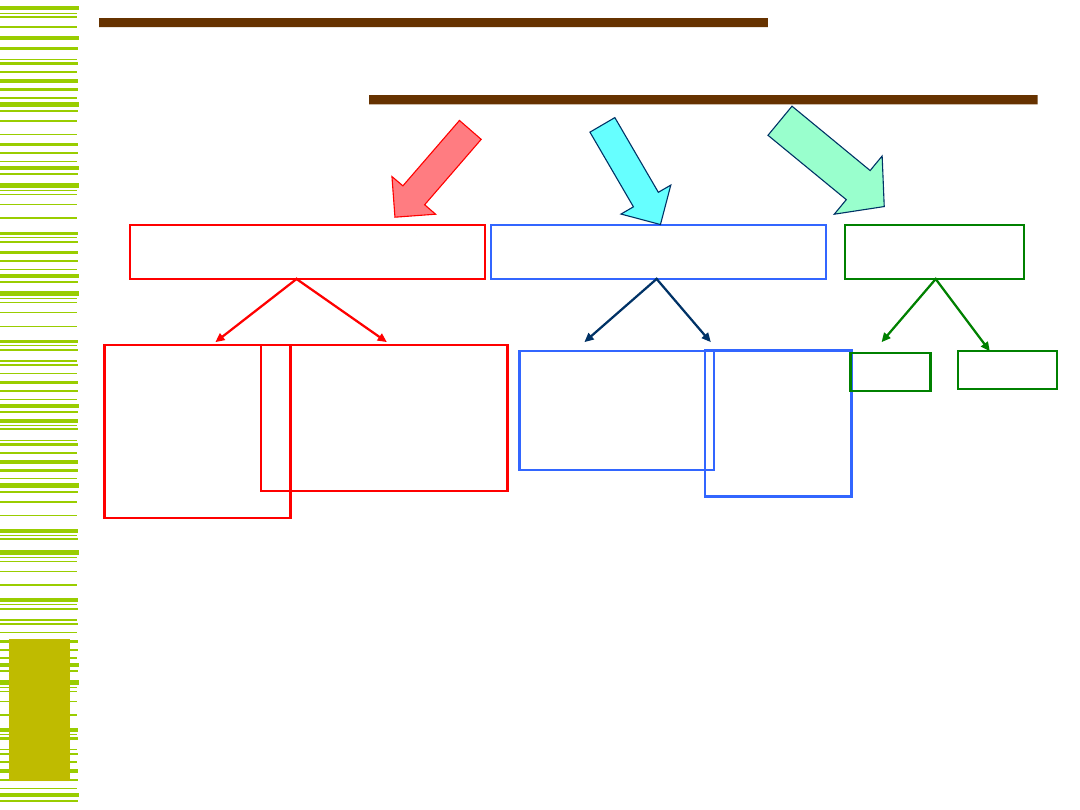

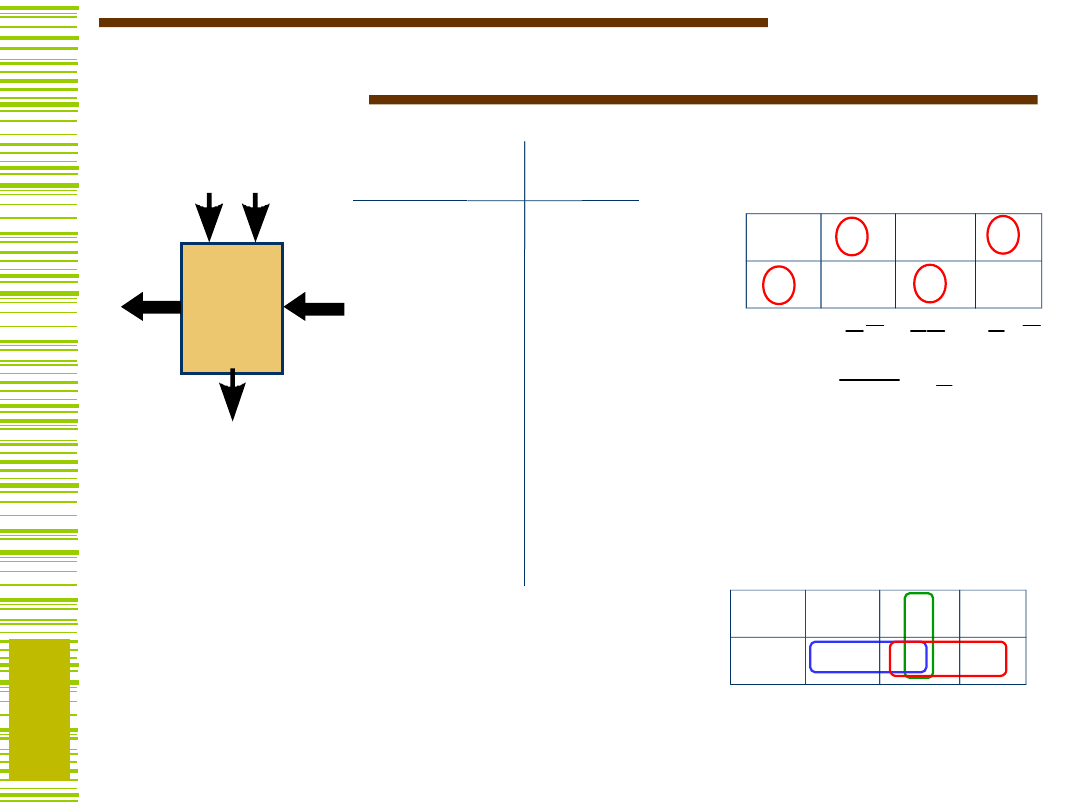

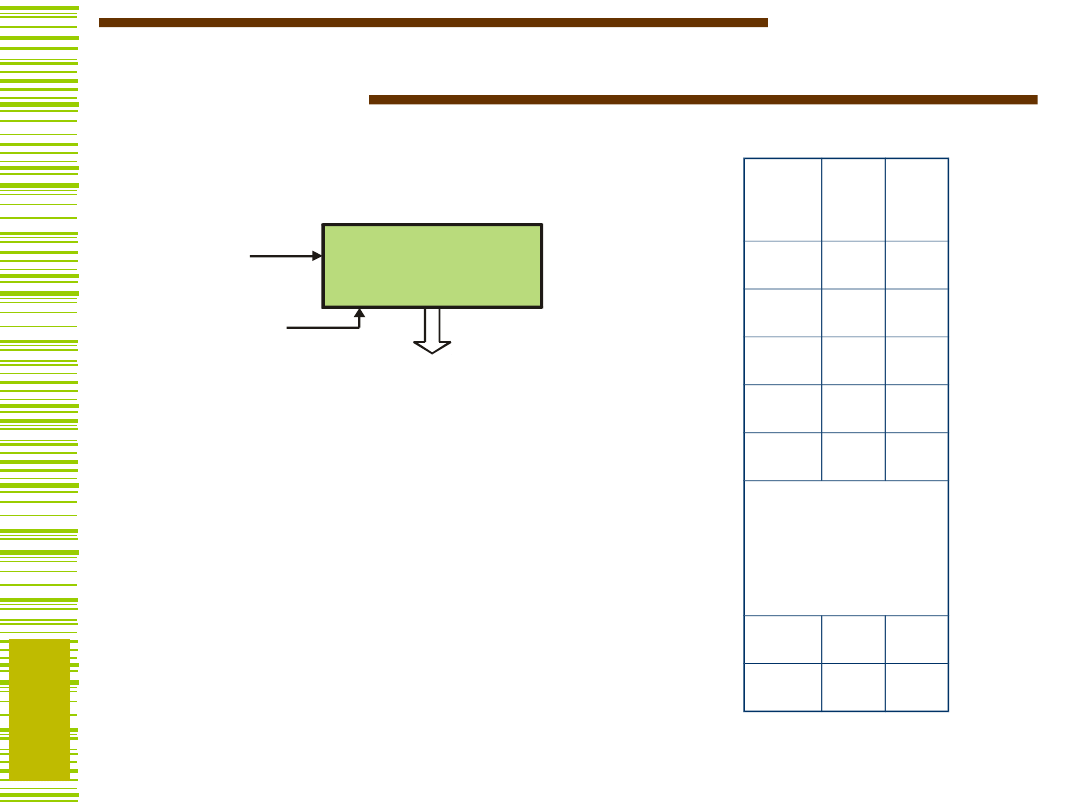

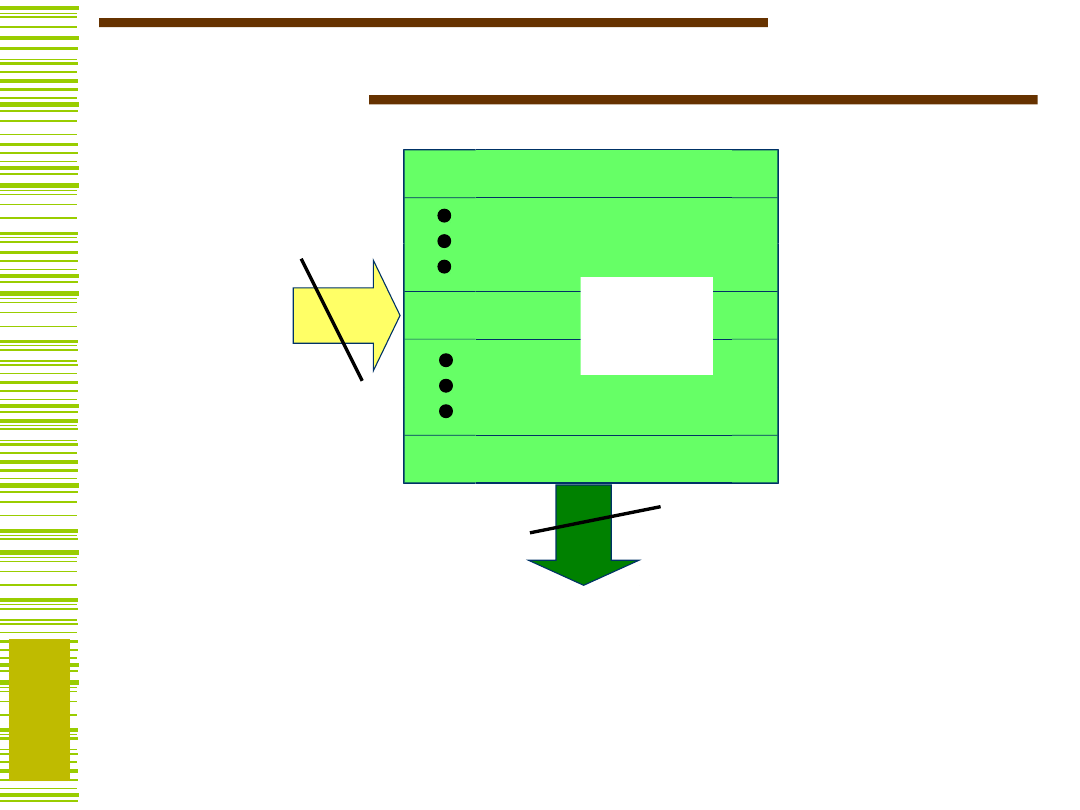

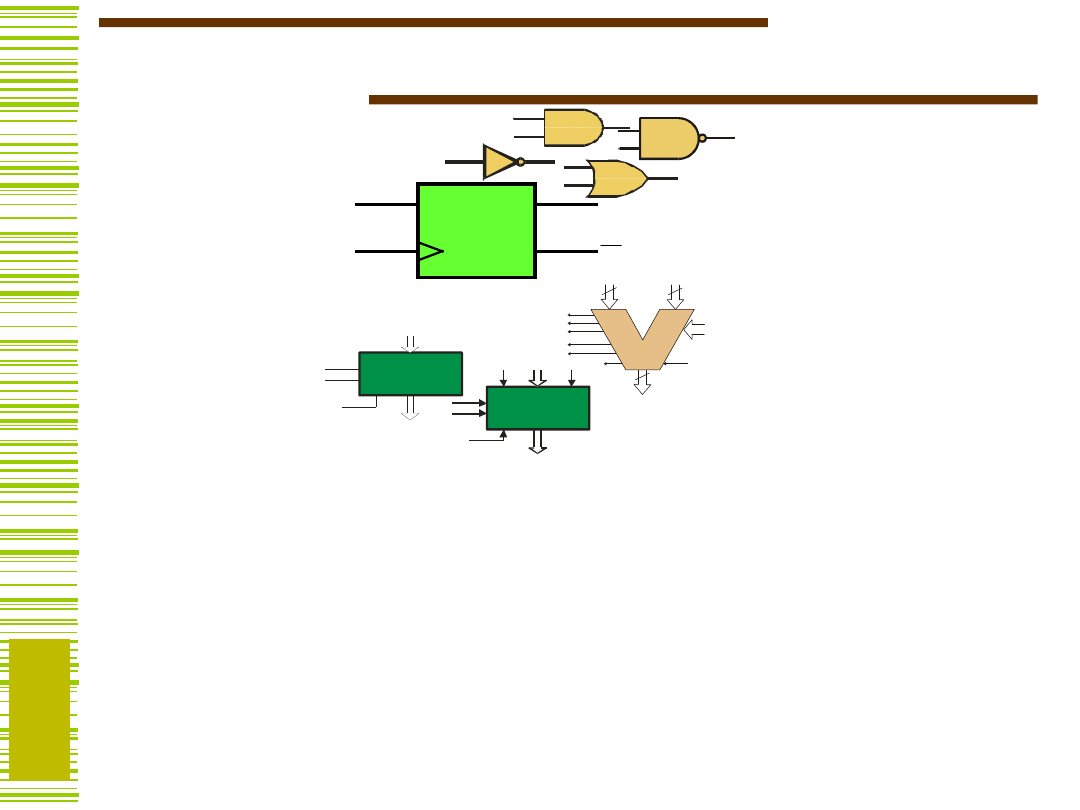

Bloki funkcjonalne

P

S

X

Y

BF

clk

X – wejścia sygnałów

reprezentujących

dane wejściowe

S – wejścia sterujące,

Y – wyjścia sygnałów

reprezentujących dane

wyjściowe,

P – wyjścia predykatowe,

sygnalizujące pewne

szczególne stany

przetwarzania danych,

clk – wejście zegarowe

6

I

T

P

W

ZPT

Bloki

funkcjonalne

B. kombinacyjne B. sekwencyjne Pamięci

Układy

arytmetyczne

Sumator

Układ odejmujący

Komparator

Układy

Komutacyjne

MUX

DMUX

DEC

Rejestry

Równoległe

Przesuwające

Liczniki

Zliczające

W górę

W dół

ROM

(RAM)

7

I

T

P

W

ZPT

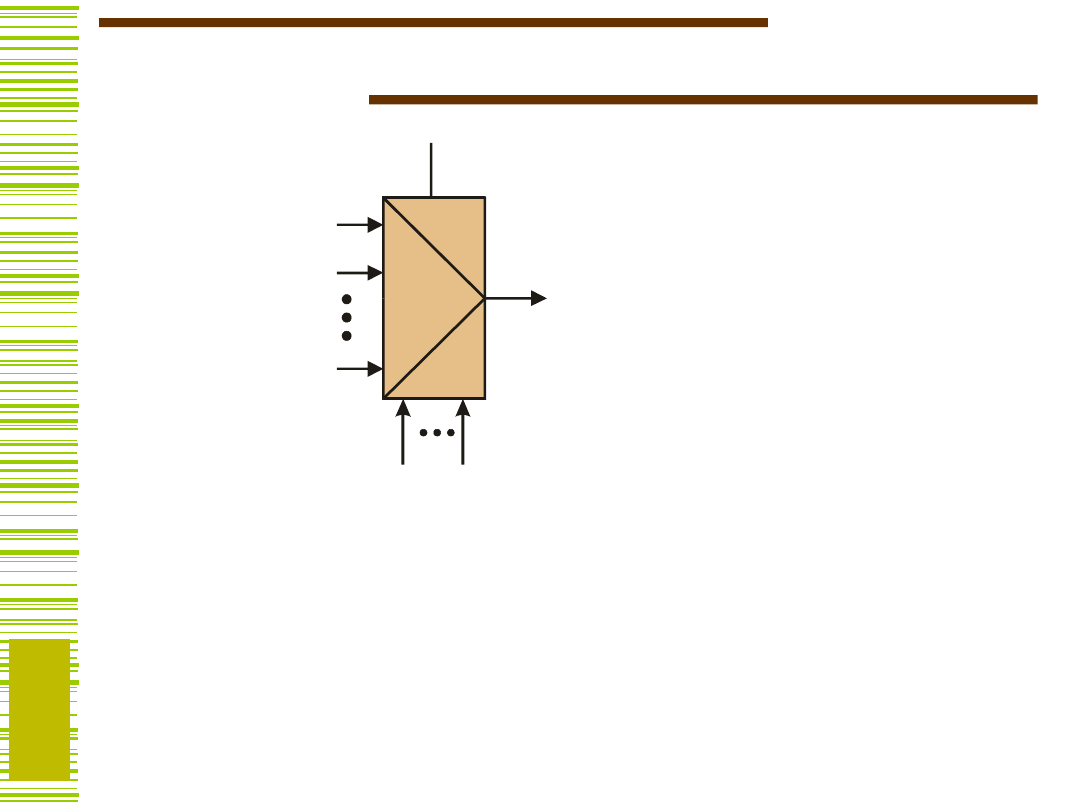

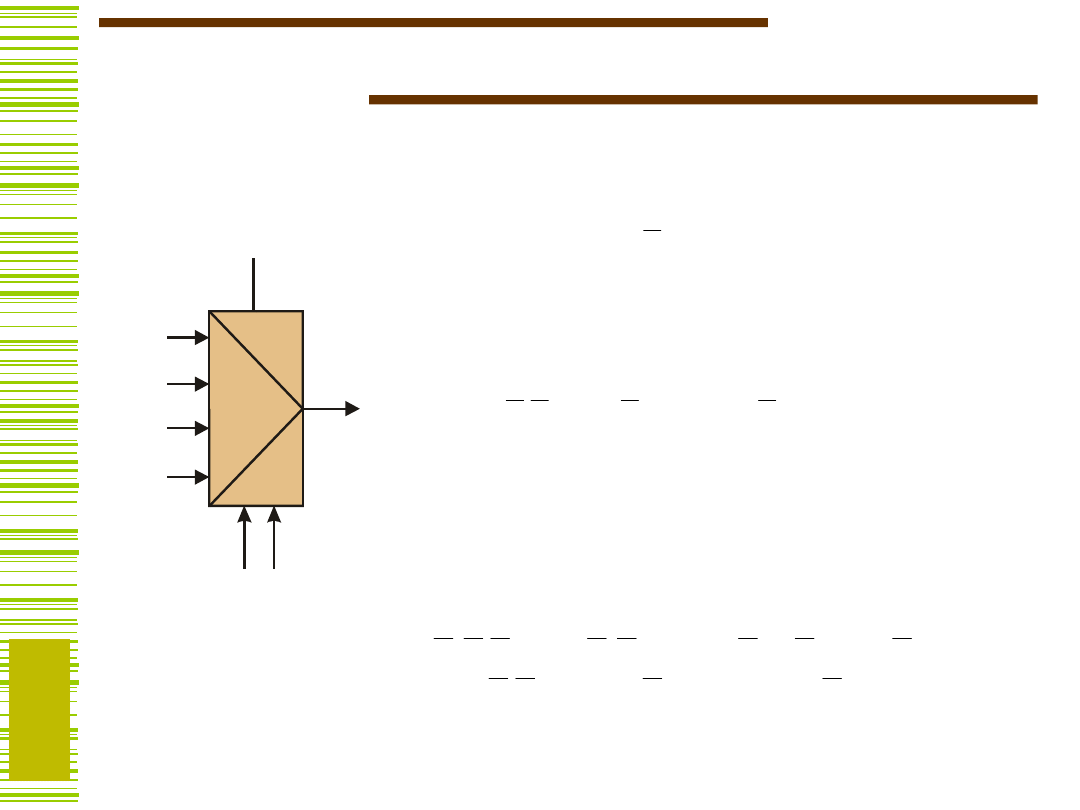

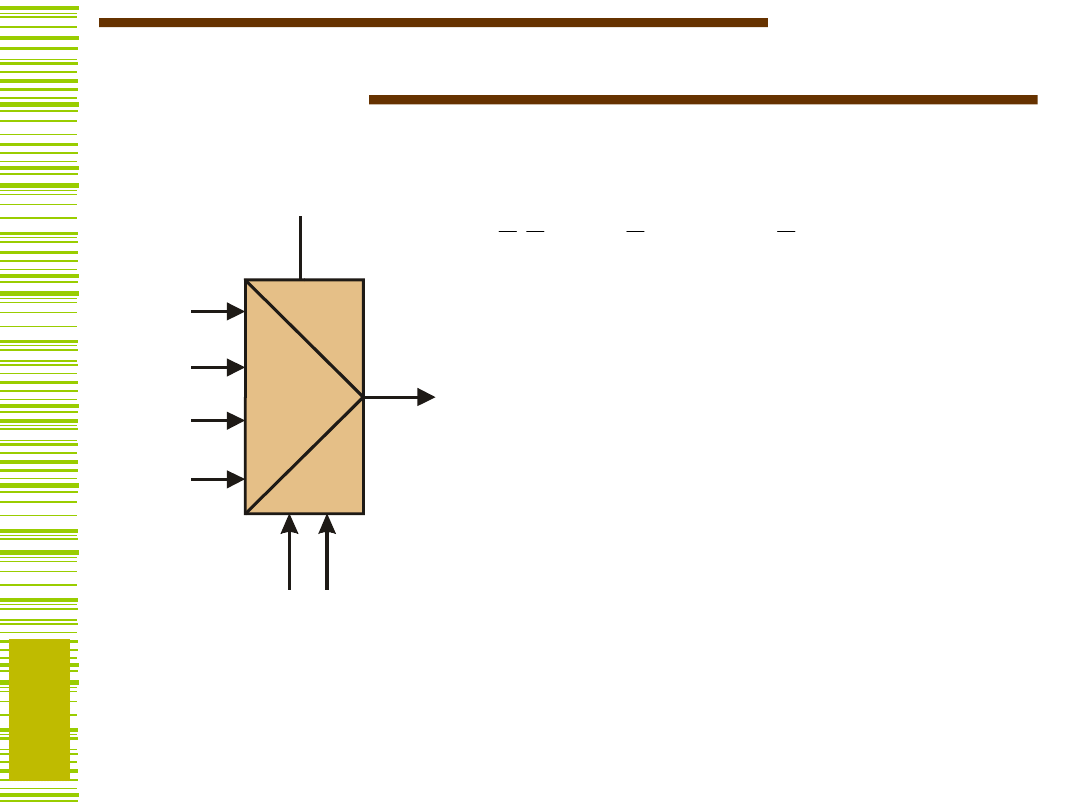

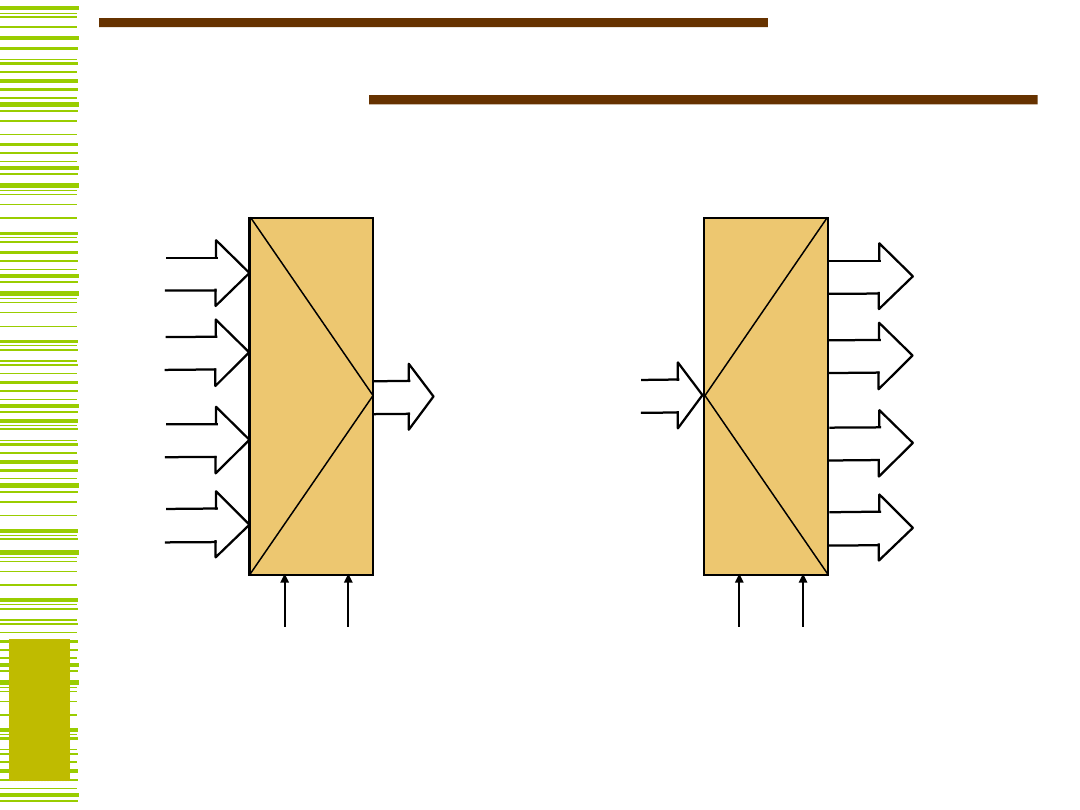

Multiplekser (MUX)

N =

2

n

P

k

(A) oznacza pełny iloczyn zmiennych a

n–

1

,...,a

0

, prostych lub zanegowanych, zgodnie z

reprezentacją binarną liczby k = L(A).

a

n-1

a

0

e

d

d

d

0

1

N-1

1

N

0

k

k

k

(A)d

P

e

y

A = (a

n–1

,..., a

j

,..., a

0

)

8

I

T

P

W

ZPT

Multipleksery

1

0

ad

d

a

y

3

0

1

2

0

1

1

0

1

0

0

1

d

a

a

d

a

a

d

a

a

d

a

a

y

7

0

1

2

6

0

1

2

5

0

1

2

4

0

1

2

3

0

1

2

2

0

1

2

1

0

1

2

0

0

1

2

d

a

a

a

d

a

a

a

d

a

a

a

d

a

a

a

d

a

a

a

d

a

a

a

d

a

a

a

d

a

a

a

y

Dla n = 1 (MUX 2 : 1):

dla n = 2 (MUX 4 : 1):

dla n = 3 (MUX 8 : 1):

e = 1

0

1

2

3

a

1

a

0

d

d

d

0

1

3

d

d

2

d

1

N

0

k

k

k

(A)d

P

e

y

9

I

T

P

W

ZPT

Multiplekser jako przełącznik

e = 1

0

1

2

3

0 0

0

3

0

1

2

0

1

1

0

1

0

0

1

d

a

a

d

a

a

d

a

a

d

a

a

y

0 1

1 1

0

1

1

0

1

1

10

I

T

P

W

ZPT

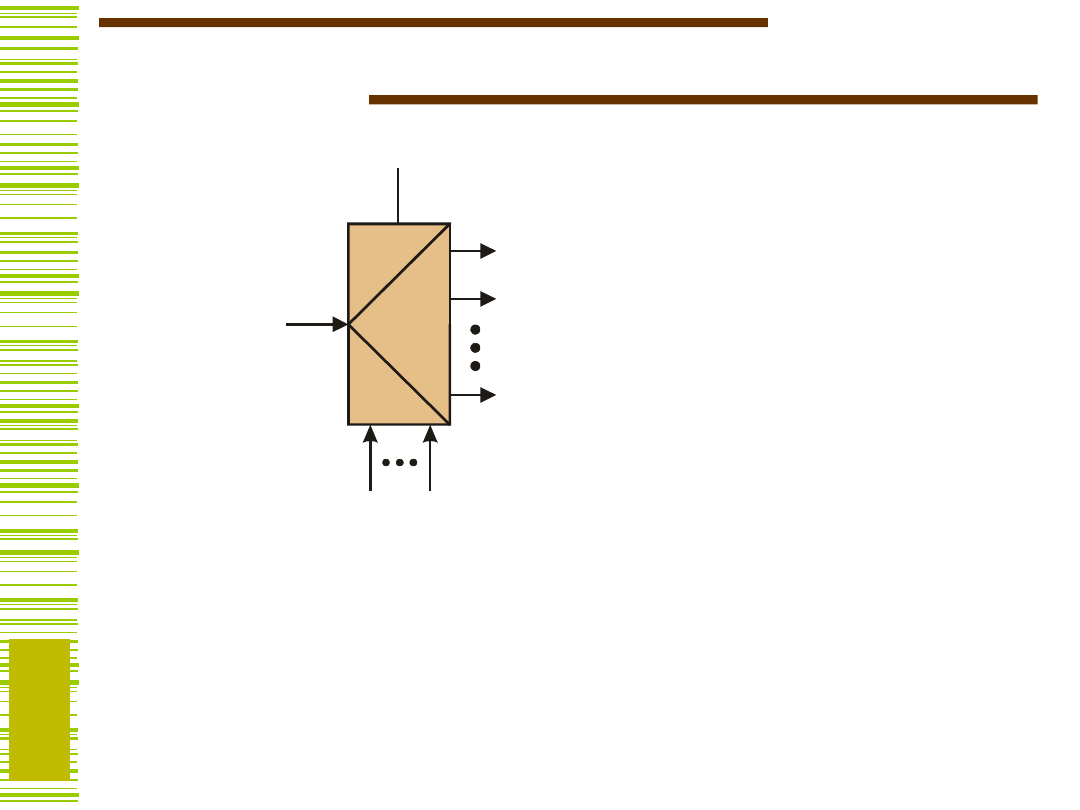

Demultiplekser

a

n - 1

a

0

e

d

y

y

y

0

1

N - 1

(N = 2

n

)

(A)d

eP

y

k

k

P

k

(A) oznacza pełny iloczyn zmiennych a

n–

1

,...,a

0

, prostych lub zanegowanych, zgodnie

z reprezentacją binarną liczby k = L(A).

11

I

T

P

W

ZPT

Demultiplekser jako przełącznik

e = 1

0

1

2

3

0

0

0

d

a

a

y

d

a

a

y

d

a

a

y

d

a

a

y

0

1

3

0

1

2

0

1

1

0

1

0

0

0

0

0

0

0

0 0

0 1

1 1

1

1

1

1

12

I

T

P

W

ZPT

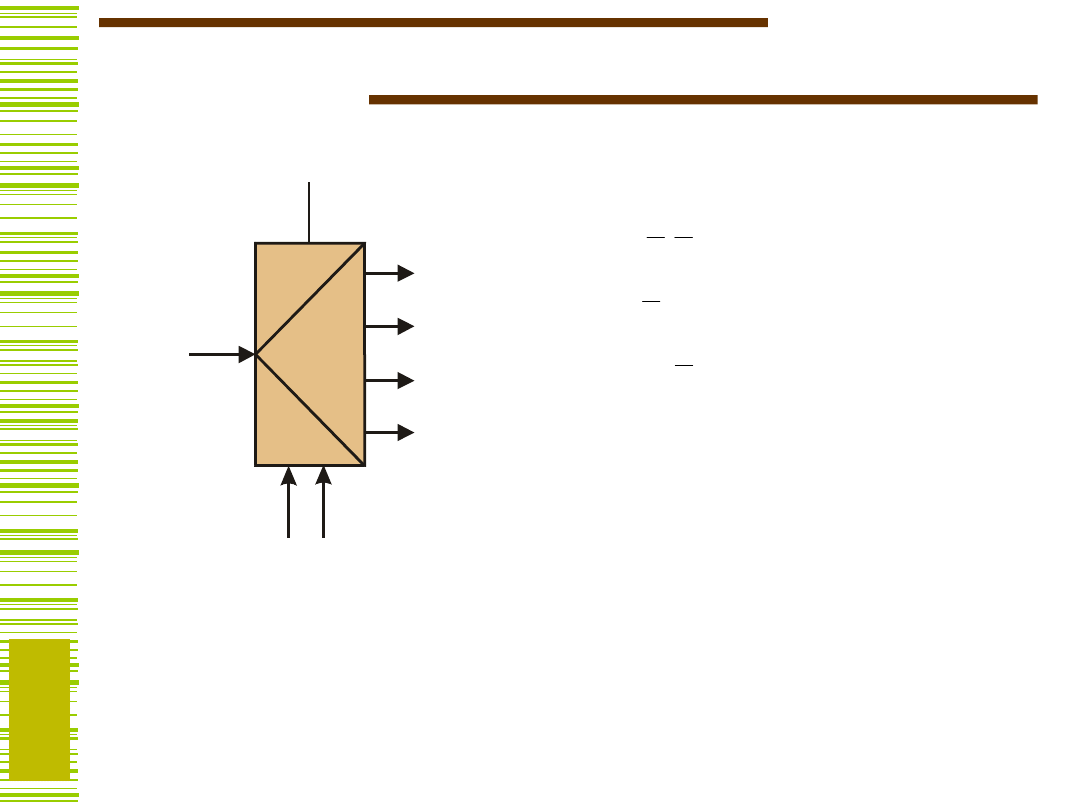

Dekoder

a

n - 1

a

0

e

d

y

y

y

0

1

N - 1

y

y

y

0

1

N - 1

a

a

a

0

1

n - 1

N =

2

n

DMU

X

d=1

e=1

DEKODER

13

I

T

P

W

ZPT

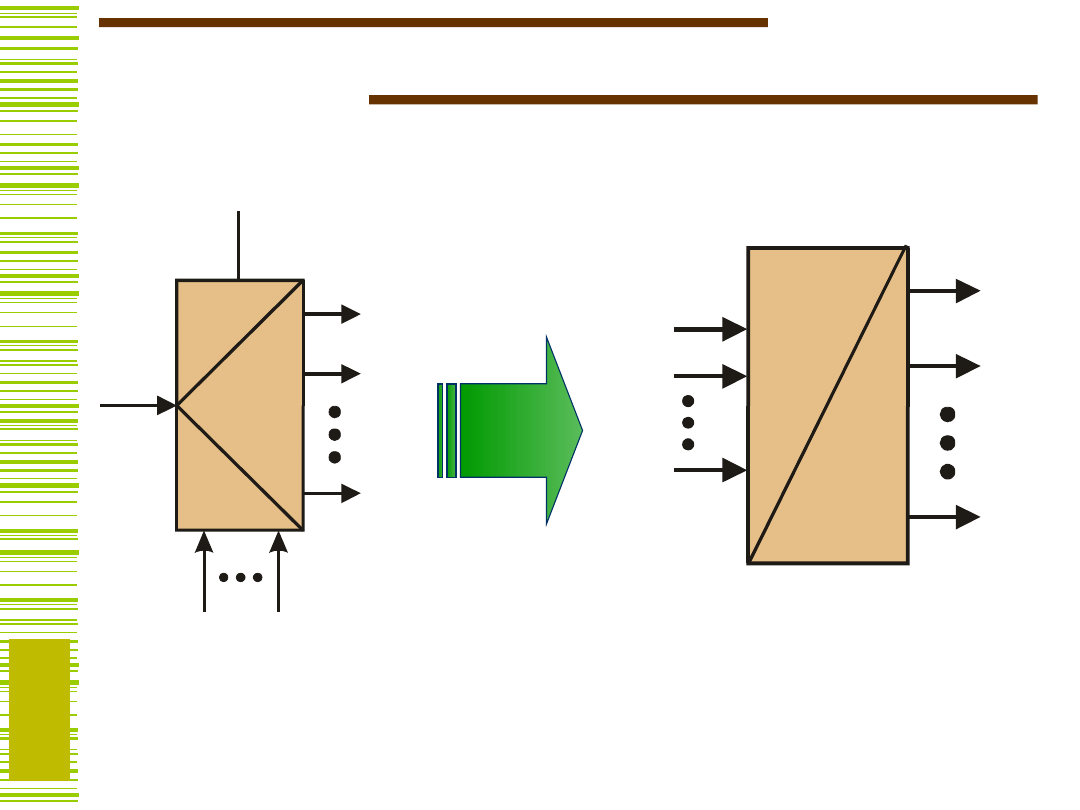

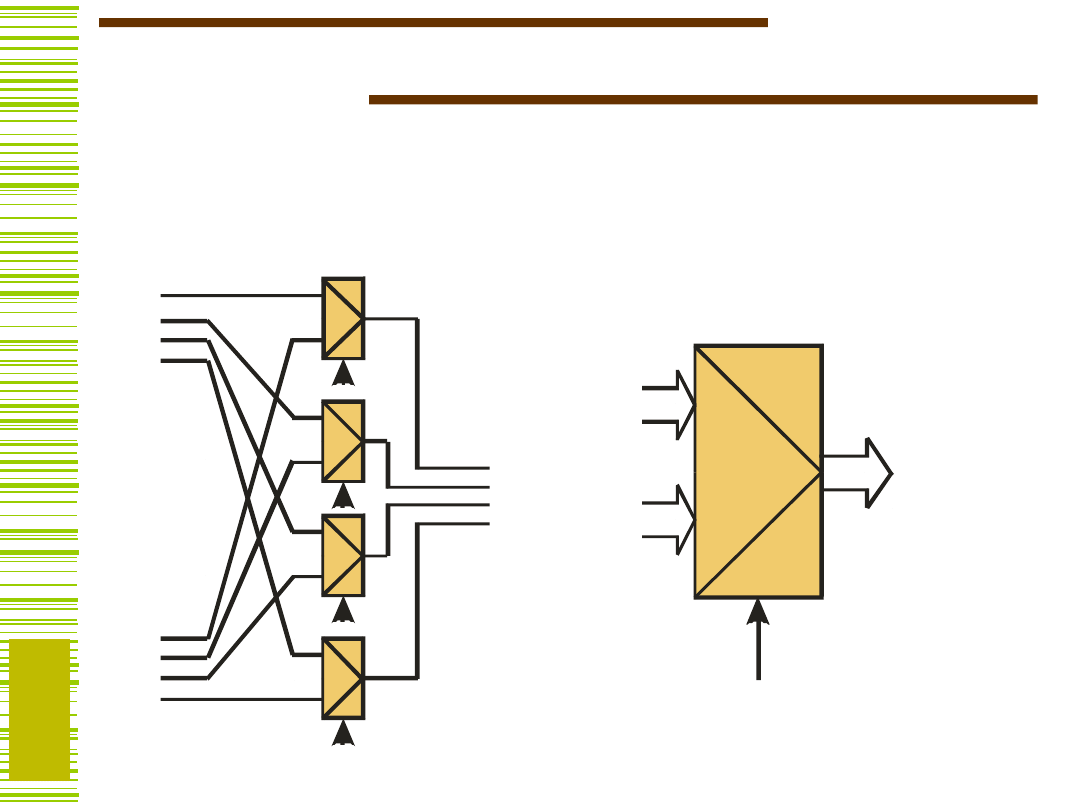

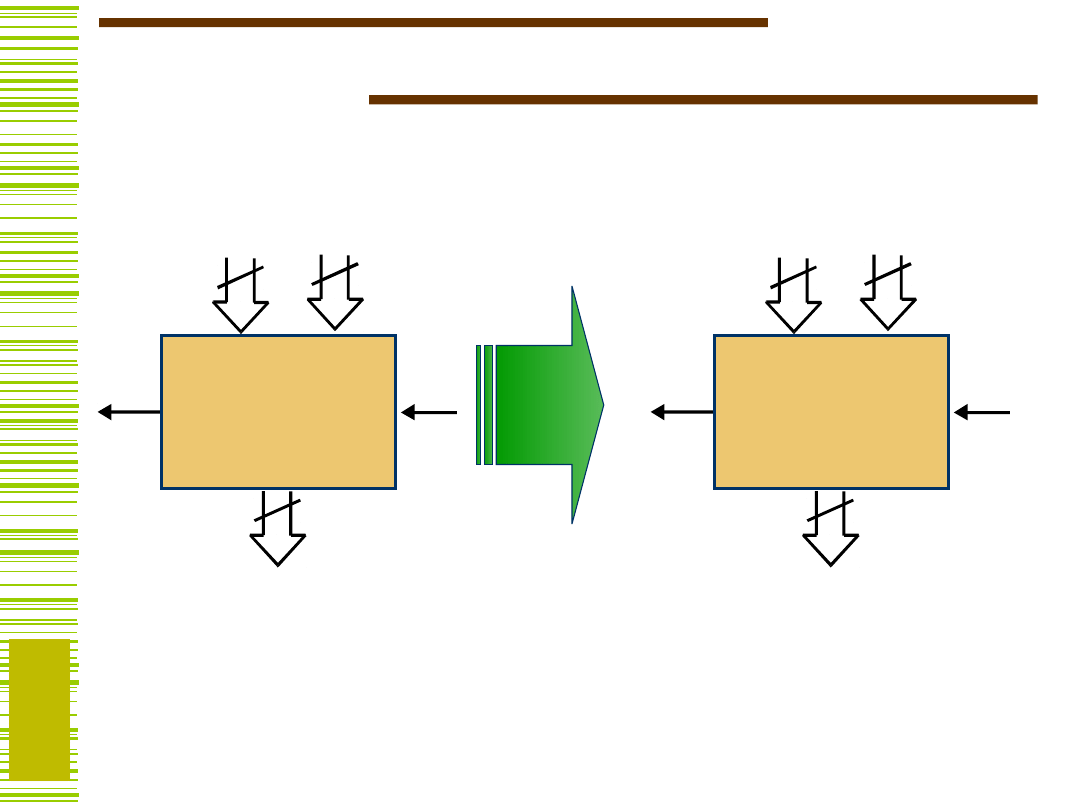

Multipleksery grupowe

A

B

Y=A

0 1

Y=B

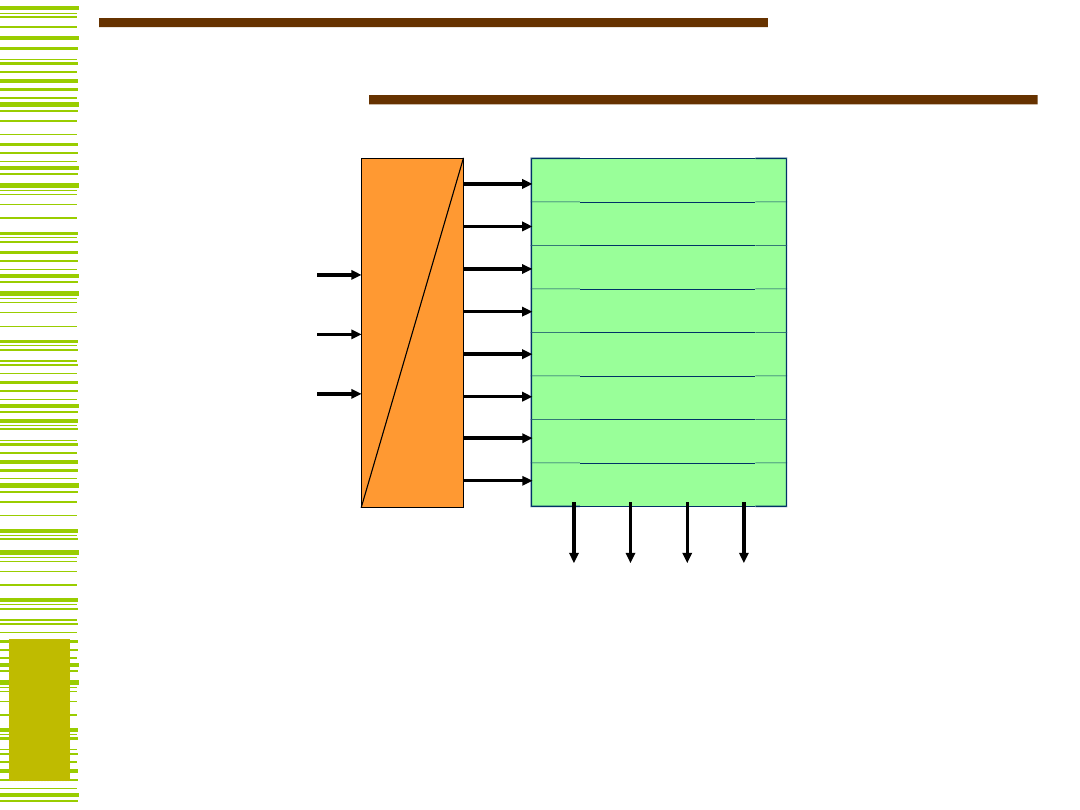

MUX-y i DMUX-y można przystosować do przełączania

(komutacji) sygnałów wielobitowych (grupowych)

Y

A

B

14

I

T

P

W

ZPT

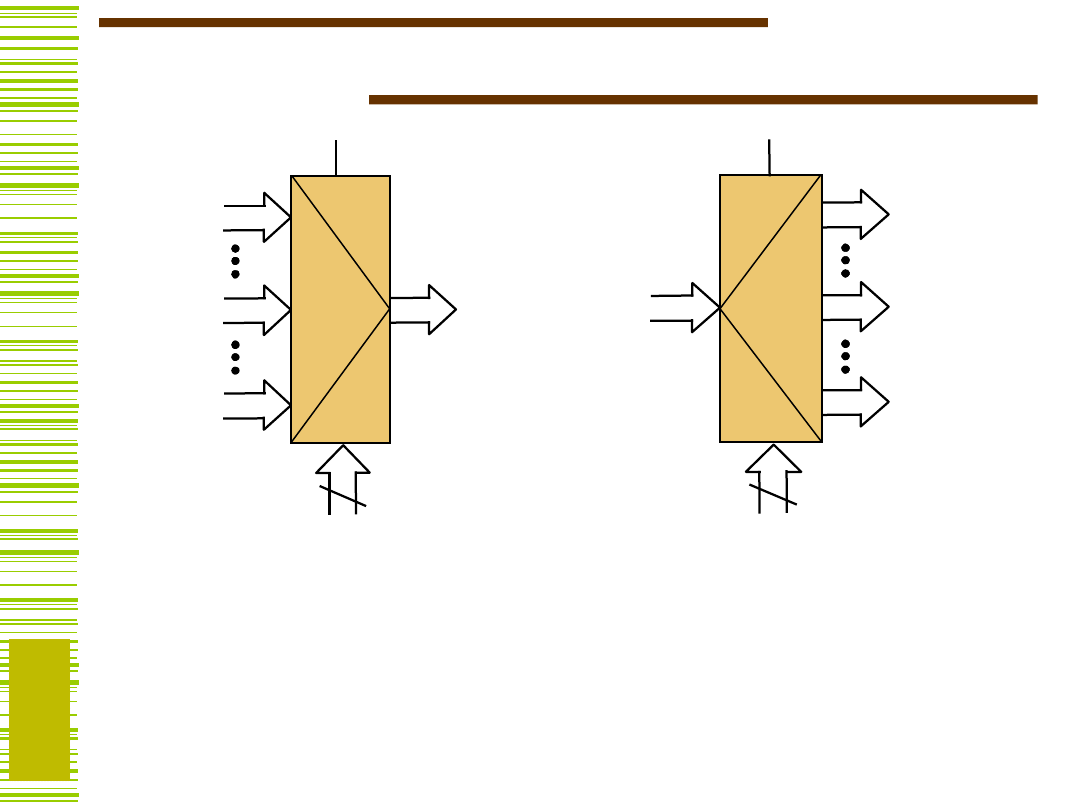

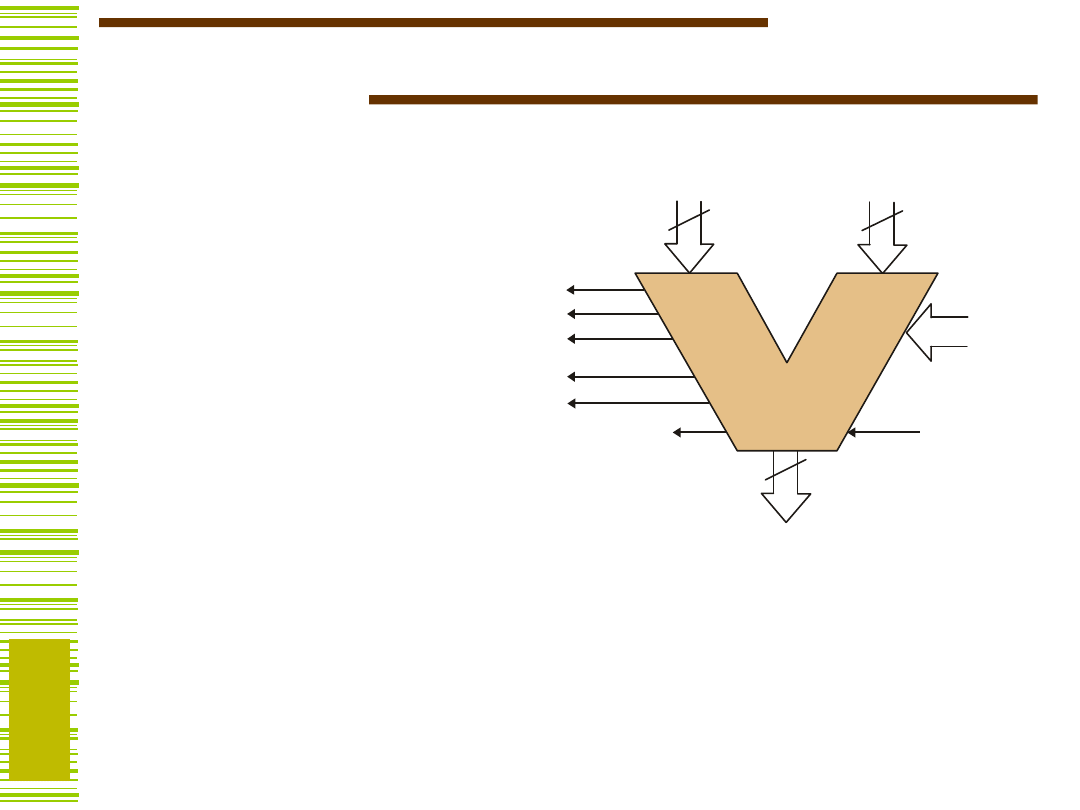

Bloki komutacyjne

Multiplekser służy do

wybierania jednego z wielu słów

wejściowych i przesyłania go na

wyjście. Na wyjściu Y pojawia

się słowo wejściowe wskazane

adresem A (wg naturalnego

kodu binarnego).

Demultiplekser służy do

przesyłania słowa X

wejściowego na jedno z

wielu wyjść; numer tego

wyjścia jest równy

aktualnej wartości adresu.

X

0

X

j

X

N-1

Y

n

A

e

Y

0

Y

j

Y

N-1

n

A

e

X

15

I

T

P

W

ZPT

Bloki komutacyjne

1 0

0 0

1 1

a

1

a

0

0

1

2

3

0

1

0

a

1

a

0

0

1

2

3

1 0

0 0

1 1

0

1

0

0

1

1

0

0

0

1

1

1

0

1

0

0

0

0

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

1

0

Najważniejsze zastosowanie:

16

I

T

P

W

ZPT

Inne zastosowania…

y =

(1,7,11,13,14,15)

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

y

0

1

0

0

0

0

0

1

0

0

0

1

0

1

1

1

x

3

x

2

x

1

x

0

Zastosowanie MUX do realizacji

funkcji boolowskich

17

I

T

P

W

ZPT

y =

(1,7,11,13,14,15)

0

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

x

3

x

2

x

1

x

0

y

Zastosowanie dekodera do

realizacji

funkcji boolowskich

Inne zastosowania…

… należy odłożyć do kosza!

18

I

T

P

W

ZPT

Sumatory

Sumator –

podstawowy BF

powszechnie

stosowany w

technice cyfrowej

Inne układy

arytmetyczne:

układy odejmowania

układy mnożące

układy dzielenia

...są budowane z sumatorów

c

n

c

0

A

n

B

n

Y

n

A

19

I

T

P

W

ZPT

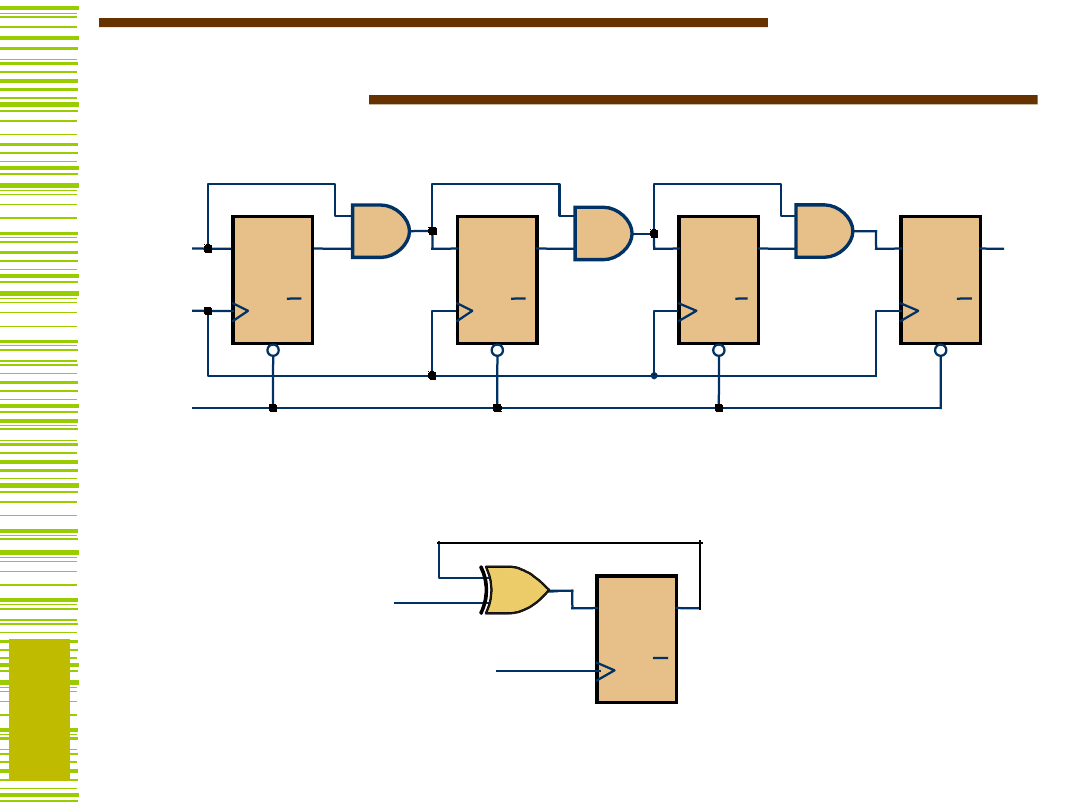

Najprostszy sumator

Najprostsza realizacja:

kaskadowy

(ripple carry adder)

a b

i

i

y

i

c

i+1

c

i

a b

0

0

y

0

c

1

c

0

a b

c

n-1

n-1

y

n-1

c

n

n-1

c

n

c

0

A

n

B

n

Y

n

1001 0110

1111

C

4

=0

0111

0000

C

4

=1

Jak jest zbudowane pojedyncze ogniwo?

20

I

T

P

W

ZPT

Funkcje logiczne sumatora

0

0

0

1

0

1

1

1

b)

c(a

ab

b)

c(a

ab

o

c

i

c

i

b

i

a

i

y

)

b

(a

c

b

a

c

i

i

i

i

i

1

i

a

b

c

c

o

y

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

y

c

o

c

a b

ab

c

00

01

11

10

0

0

1

0

1

1

1

0

1

0

ab

c

00

01

11

10

0

0

0

1

0

1

0

1

1

1

b

a

c

y

b

a

c

b

a

c

b

a

c

b

a

c

b

a

c

cab

y

0

1

1

0

1

0

0

1

21

I

T

P

W

ZPT

Co z odejmowaniem?

c

n

c

0

A

n

B

n

Y

n

A

c

n

c

0

A

n

B

n

Y

n

–

A

?

22

I

T

P

W

ZPT

Reprezentacje liczb – NKB/U2

A = <

a

n–1

,..., a

j

,..., a

0

> gdzie a

j

{0,1}

1

n

0

j

j

j

NKB

D

2

a

A

L

A

2

n

0

j

j

j

1

n

1

n

U2

D

2

a

2

a

A

L

A

NKB:

U2:

23

I

T

P

W

ZPT

Kod U2

A

U2

= <a

n–1

,..., a

j

,..., a

0

>, gdzie a

j

{0,1}

Zakres: –2

n–1

≤ A

D

≤ 2

n–1

– 1

2

n

0

j

j

j

1

n

1

n

U2

D

2

a

2

a

A

L

A

Bit a

n–1

można interpretować jako bit znaku.

Jeśli a

n–1

= 0, to liczba jest dodatnia;

jeśli a

n–1

= 1 to liczba jest ujemna; pozostałe bity

stanowią uzupełnienie (różnicę) wartości liczby do

najwyższej potęgi liczby 2

<0101>│

U2

= +5│

D

; <1011>│

U2

= –

5│

D

24

I

T

P

W

ZPT

Sumator/układ odejmujący

Jak z sumatora zbudować układ odejmujący?

Y

A

c

n

c

0

n

n

B

n

X O R

n

–

+

1

B

C

o

=1

B

C

o

=0

B

Y = A – B = A + (–B|

U2

)

B

–B|

U2

= +1 = B1 + 1

–B|

U2

= +1 = B1 + 1

–B|

U2

= +1 = B1 + 1

Dla c

0

= 1

Y = A + + 1 = A –

B

B

B

B

B

0

Dla c

0

= 0

Y = A + B 0 + 0 = A + B

25

I

T

P

W

ZPT

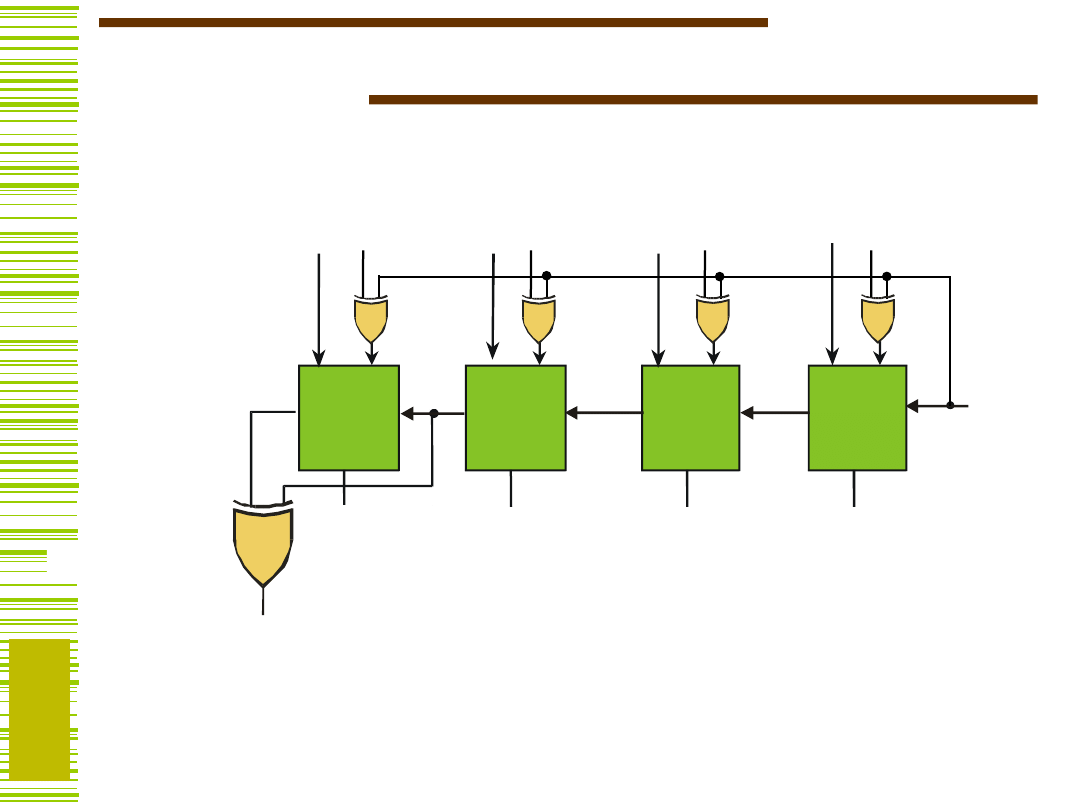

Sumator/układ odejmujący

OVR = c

n–1

c

n

A

B

CO

S

+ CI

A

B

CO

S

+ CI

A

CO

S

+ CI

A

B

CO

S

+ CI

Dodawanie/

odejmowanie

S

3

S

2

S

1

S

0

B

a

3

b

3

a

2

b

2

a

1

b

1

a

0

b

0

Overflow

OVR = c

3

c

4

c

4

c

3

26

I

T

P

W

ZPT

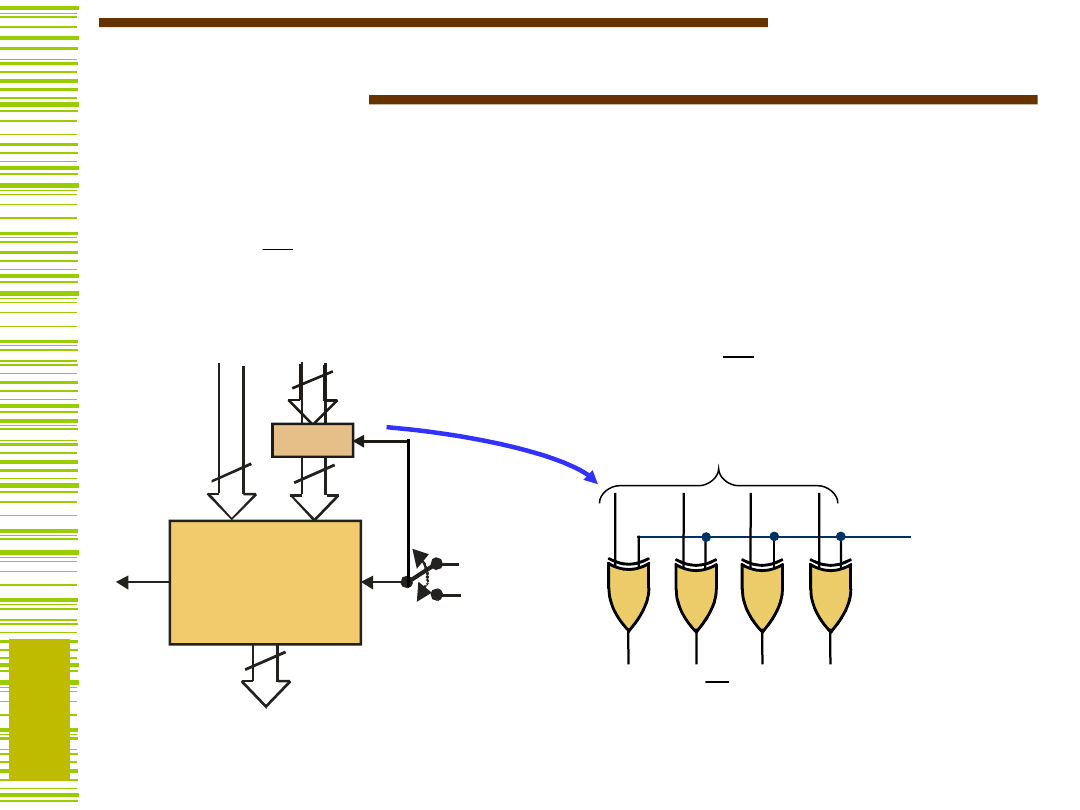

Zastosowania

Jednostka arytmetyczno-logiczna

Y

B

A

n

n

n

Y

n - 1

Z

O V R

P

G

c

n

c

0

S

A L U

Arytmometr (układ

wykonawczy:

mikrokontrolera, procesora

sygnałowego)

Inne układy

arytmetyczne:

układy mnożące

układy

kryptograficzne

...są budowane z sumatorów

27

I

T

P

W

ZPT

Komparator

A

n

B

n

K

„1 z 3”

A < B

A = B

A > B

0100 0101

1

0

0

0

1

0

0

0

1

0101 0101

0101 0100

28

I

T

P

W

ZPT

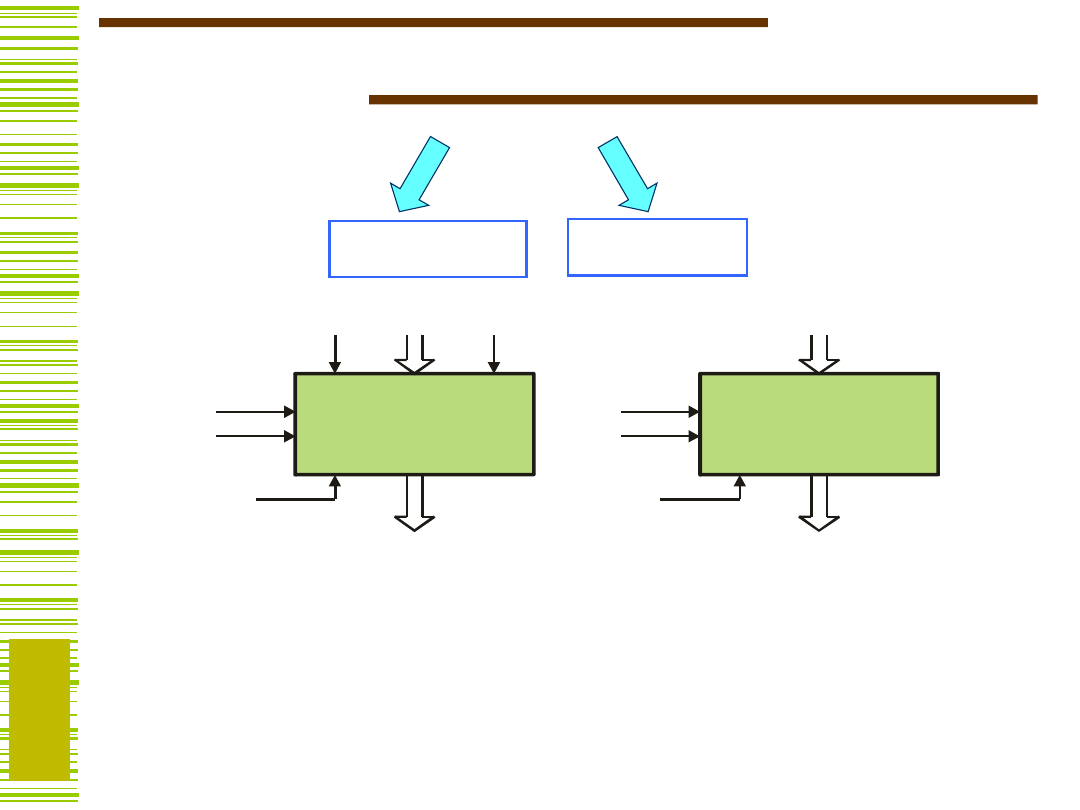

Sekwencyjne bloki funkcjonalne

Rejestry

Liczniki

L

( Q )

s

1

s

2

c lo c k

X

Y

R

( Q )

s

1

s

2

c lo c k

X

Y

x

l

x

p

Y := X LOAD

Y := Y HOLD

Y := <0...0> RESET

(CLEAR)

Y := SHR(x

p

,

Y)

Y := SHL(Y, x

l

)

Y := Y + 1 = INC(Y)

Y := Y – 1 = DEC(Y)

29

I

T

P

W

ZPT

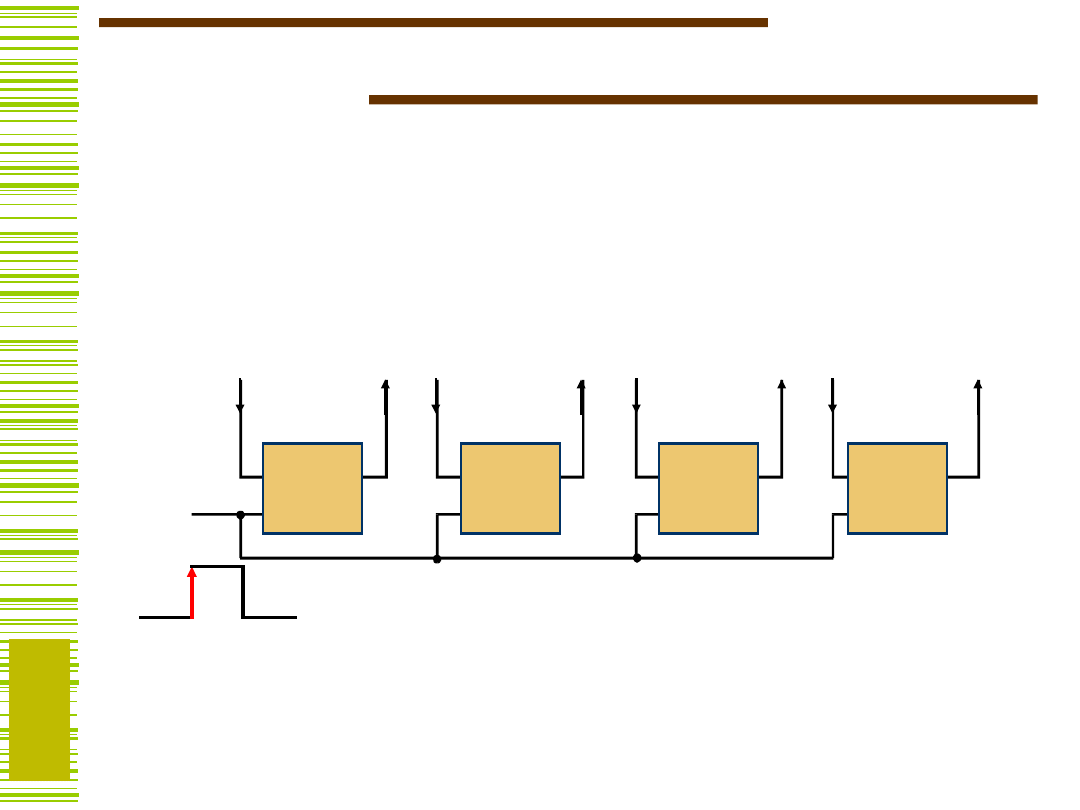

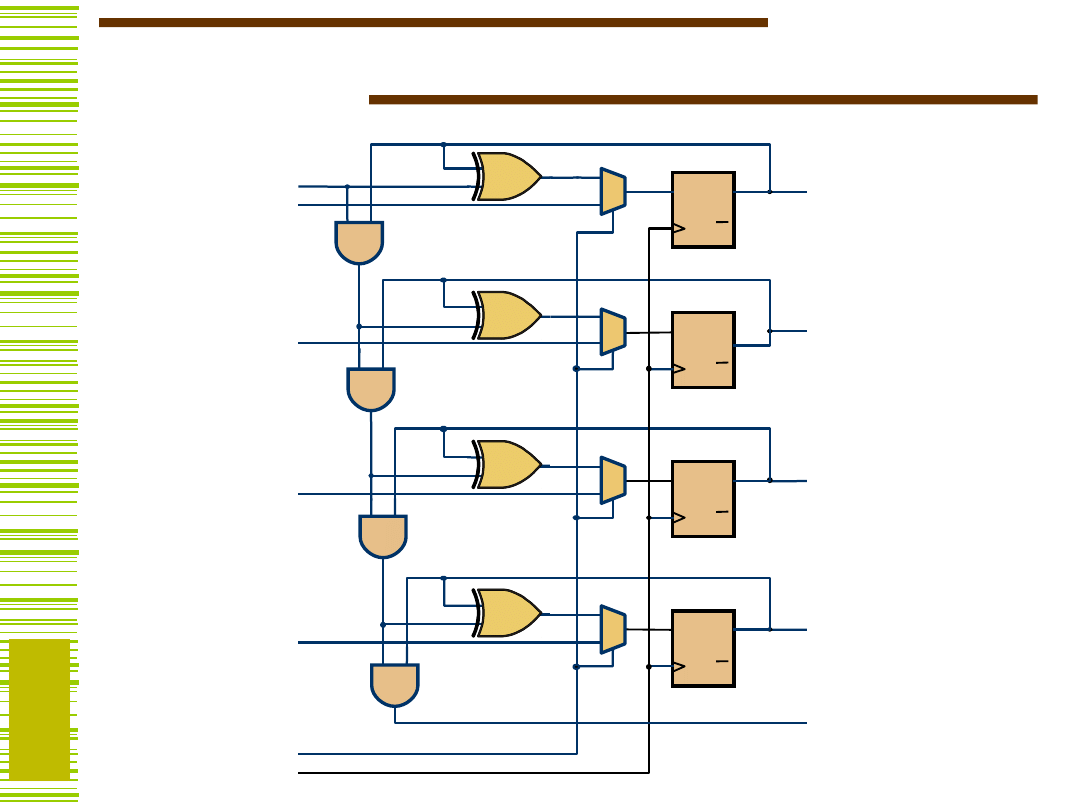

Prosty

rejestr

Rejestr zbudowany z przerzutników

– ładowanie (load) i pamiętanie

CLK

P

1

P

2

P

3

P

4

D

1

D

3

D

2

D

4

Q

1

Q

3

Q

2

Q

4

0

1

0

0

LOAD

0

1

0

0

30

I

T

P

W

ZPT

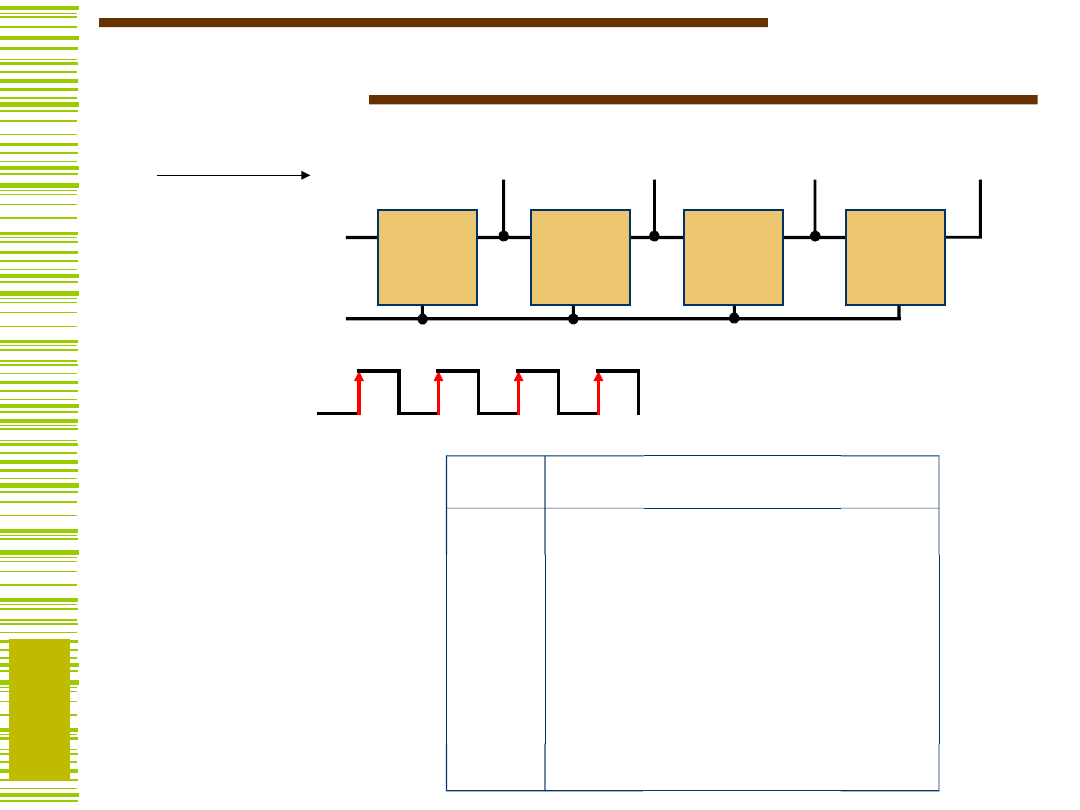

Rejestr przesuwający

WE

Q

1

Q

2

Q

3

Q

4

0

0

0

0

0

1

1

0

0

0

0

0

1

0

0

0

0

0

1

0

0

0

0

0

1

0

0

0

0

0

Q

1

Q

3

Q

2

Q

4

wejście

szeregowe

D

1

D

2

D

3

D

4

0

SHR

clk

0000 10

31

I

T

P

W

ZPT

Rejestr przesuwający

Q

1

Q

3

Q

2

Q

4

CLK

wejście

szeregowe

D

1

D

2

D

3

D

4

Clock

D1

D0

D

Q

Q

Sel

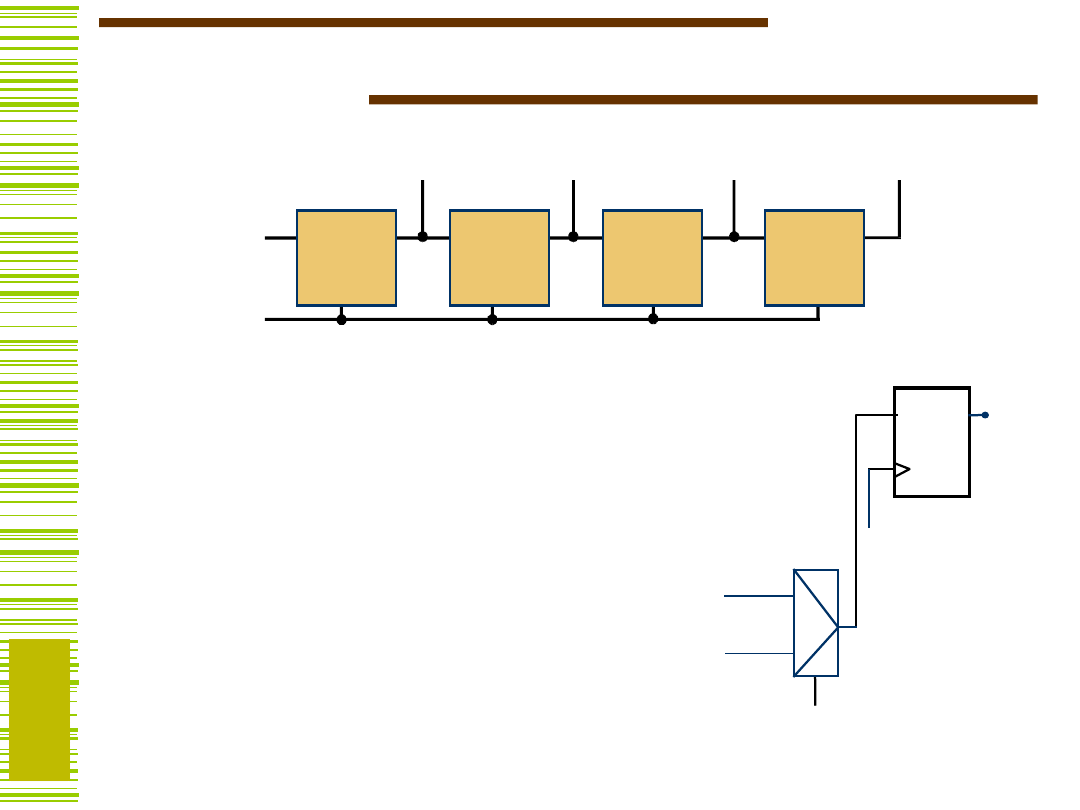

Łatwo można zbudować rejestr, w

którym obie funkcje (ładowanie,

przesuwanie) wykonywane byłyby w

jednym układzie

32

I

T

P

W

ZPT

Rejestr przesuwający z wpisem

równoległym

Q

3

Q

2

Q

1

Q

0

Clock

Wejścia równoległe

Wyjścia równoległe

Wejście

szeregowe

D

Q

Q

D

Q

Q

D

Q

Q

D

Q

Shift/Load

Q

33

I

T

P

W

ZPT

Mikrooperacje licznika

L ic z n ik

c lo c k

1100

Zliczanie

LOAD

COUNT

LOAD

HOLD

COUNT

LOAD

HOLD

0010

1101

1110

111

1

1100

34

I

T

P

W

ZPT

E

A

0

1

A

0

A

0

A

1

A

1

A

1

A

2

A

2

A

2

A

3

A

3

A

3

A

4

A

4

A

4

A

5

A

14

A

14

A

15

A

15

A

15

A

0

2

2

2

1

0

3

1

1

1

0

2

0

1

0

Q

T

Q

Q

EQ

T

Q

T

Q

EQ

T

EQ

T

E

T

Przykład licznika z wejściem Enable

Licznik

E

clock

Q

35

I

T

P

W

ZPT

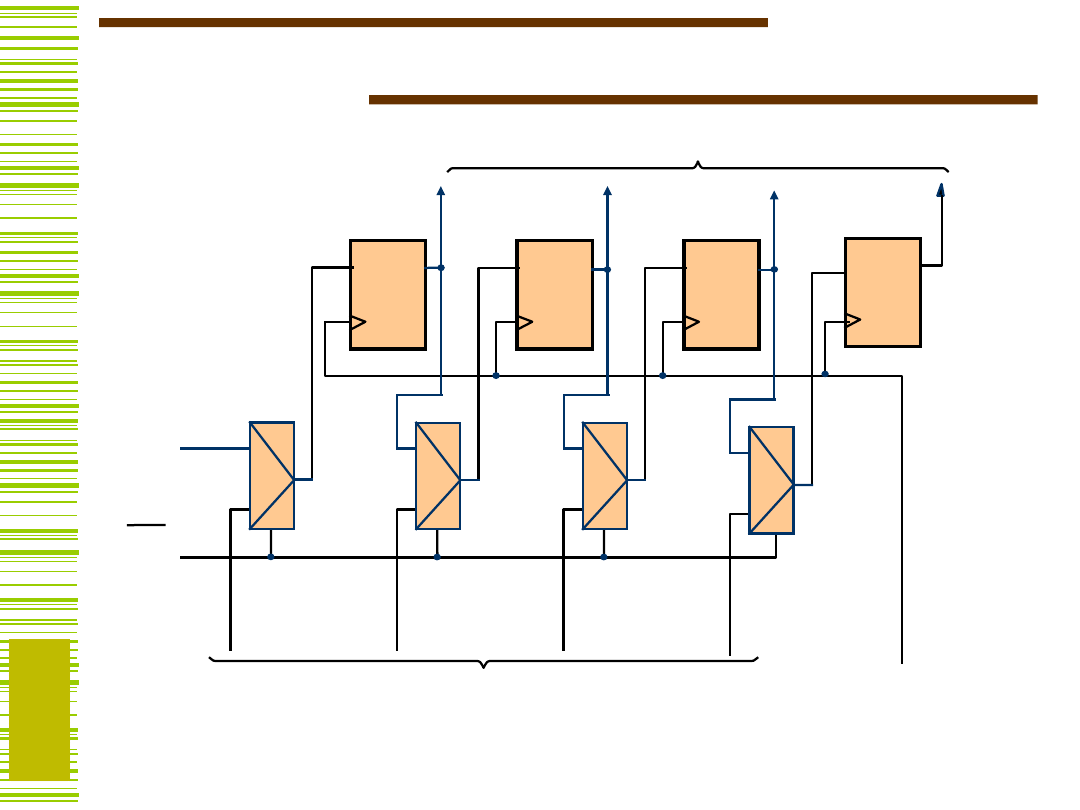

Licznik w górę

T Q

Q

Clock

T Q

Q

Enable

Rst

T Q

Q

T Q

Q

D Q

Q

T

clk

36

I

T

P

W

ZPT

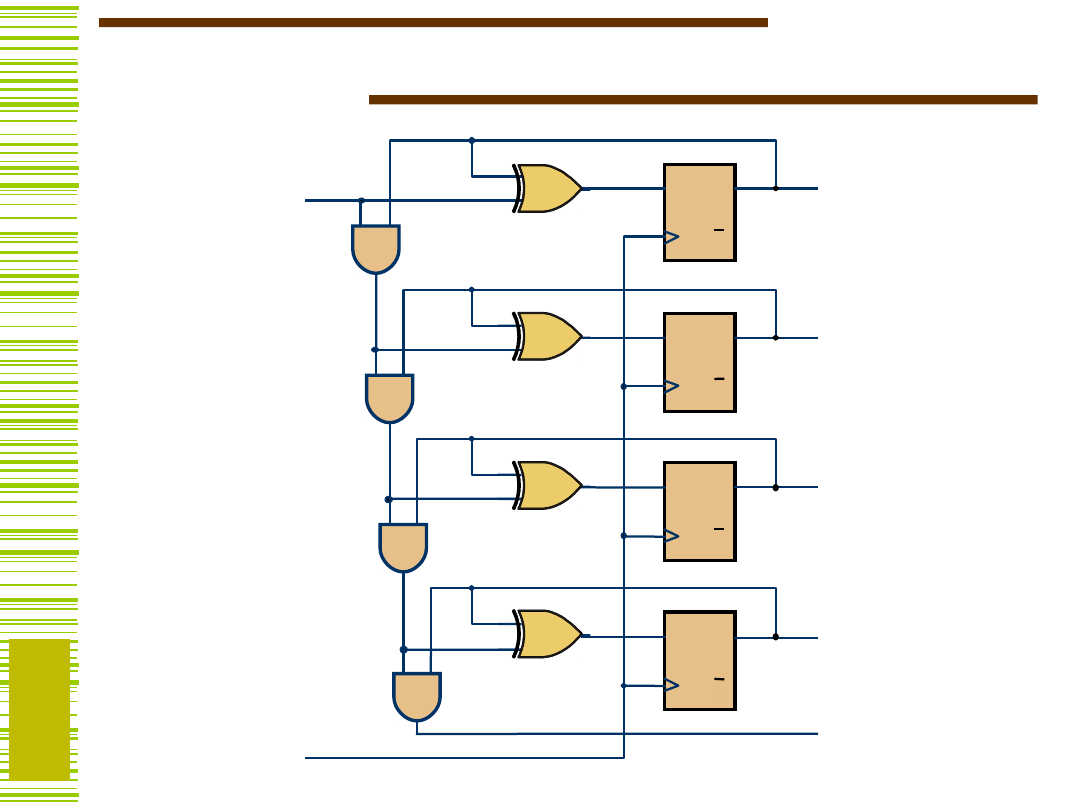

Licznik z przerzutnikami D

Clock

Enable

D Q

Q

D Q

Q

D Q

Q

D Q

Q

Q

0

Q

1

Q

2

Q

3

Output

carry

37

I

T

P

W

ZPT

Licznik z wpisywaniem równoległym

Enable

D Q

Q

Q

0

D Q

Q

Q

1

D Q

Q

Q

2

D Q

Q

Q

3

D

0

D

1

D

2

D

3

Load

Clock

Output

carry

0

1

0

1

0

1

0

1

38

I

T

P

W

ZPT

Bloki funkcjonalne

Pamięci

ROM

RAM

39

I

T

P

W

ZPT

Pamięci

Dostęp swobodny (Random

Access) - czas dostępu do

informacji zapisanej w komórce

pamięci jest niezależny od

położenia tej komórki

w matrycy pamięci.

Pamięci o dostępie swobodnym

Czas dostępu t - czas, jaki upływa

od momentu podania adresu

komórki na wejścia adresowe

pamięci do momentu ustalenia

informacji na wyjściu pamięci.

Adres

Wyjście

Matryca

pamięci

Komórki

Adres 1

Adres 2

y

1

t

1

y

2

t

2

t

1

=

t

2

y

2

y

1

40

I

T

P

W

ZPT

Pamięci

ROM, PROM, EPROM, E

2

PROM

DRAM, SRAM

(non-volatile)

ROM

(Read Only Memory)

RAM

(Random Access memory)

41

I

T

P

W

ZPT

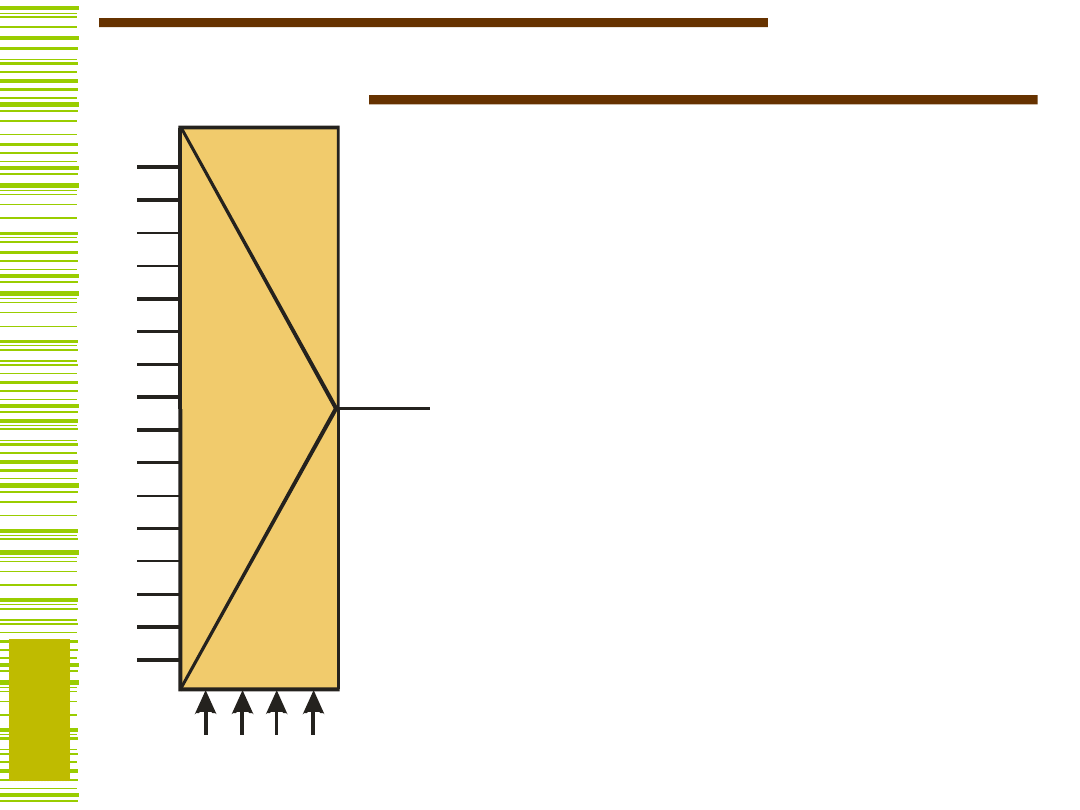

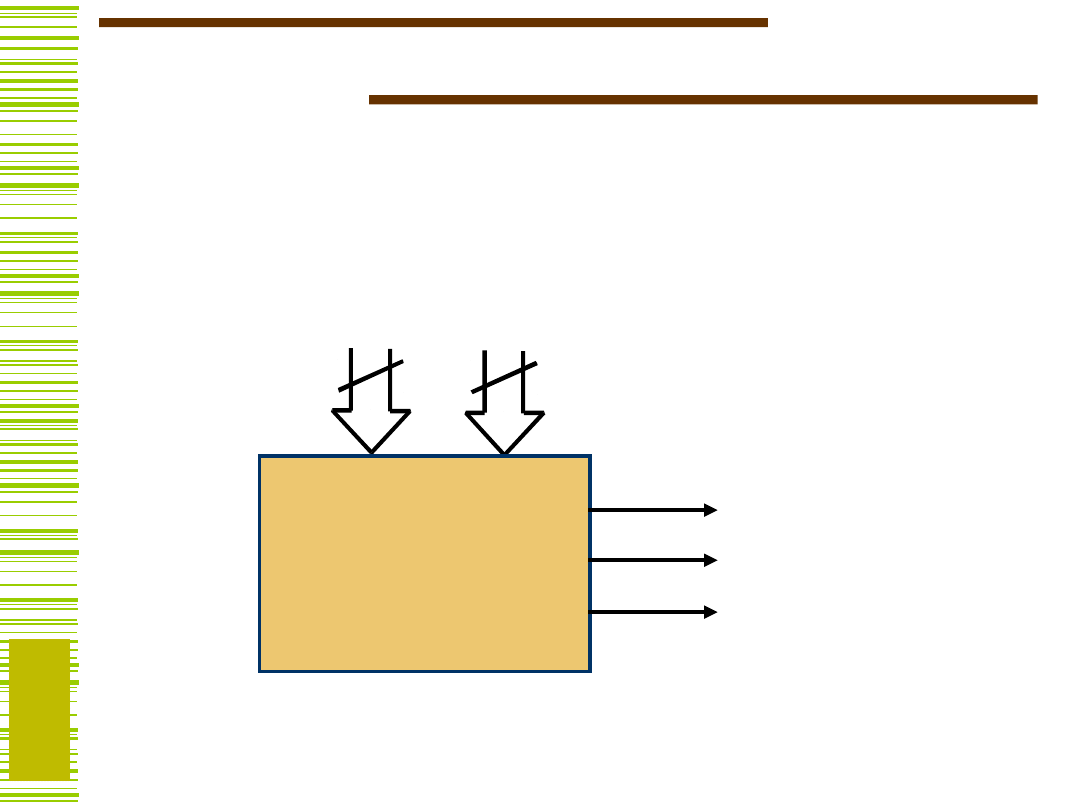

Pamięci typu ROM

ROM – uniwersalny układ kombinacyjny

A

ROM

m n

X

0

X

i

X

m-1

p

Y

n

42

I

T

P

W

ZPT

Pamięci typu ROM

Adres

ROM

8 4

0

1

2

3

4

5

6

7

0

0

0

0

0

1

1

0

1

1 1 1 1

0 1 1 0

1 1 1 0

0 1 1 0

0 1 1 0

0 1 0 1

0 0 0 0

0 1 1 0

1 1 1 0

0 1 0 1

1 1 1 1

43

I

T

P

W

ZPT

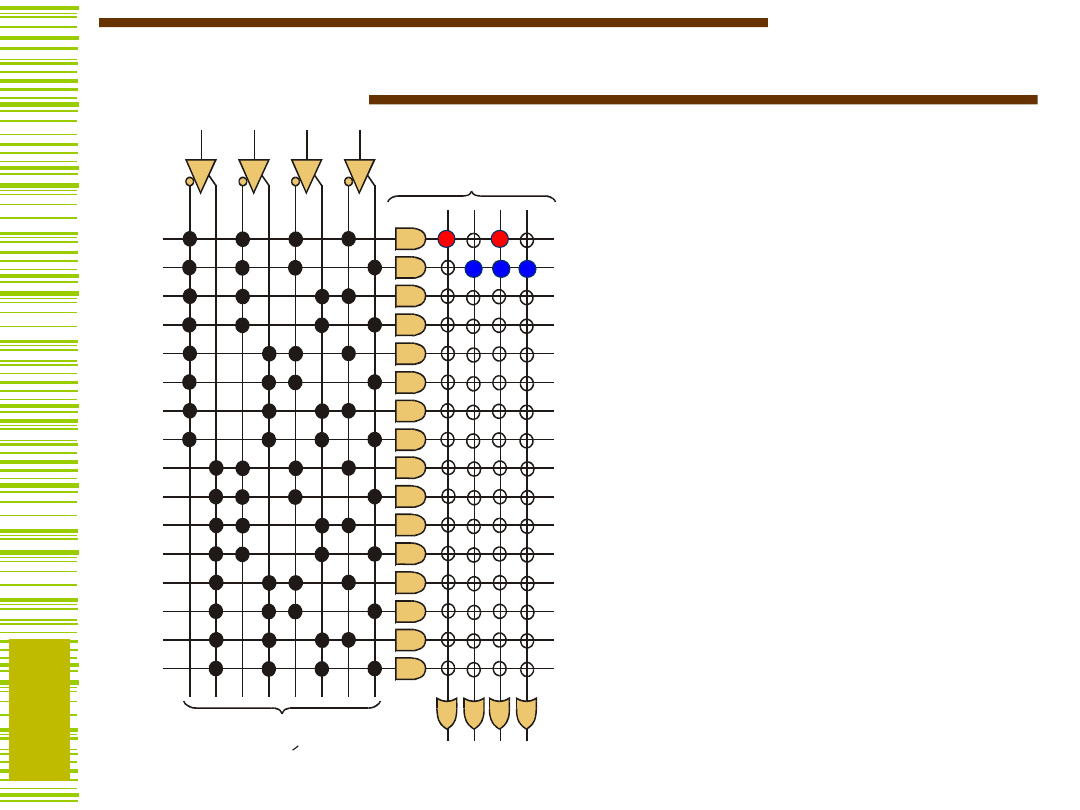

Pamięci typu ROM

(struktura)

y 3 y 2 y 1 y 0

M A T R Y C A O R

( P R O G R A M O W A L N A )

D

C

B

A

M A T R Y C A A N D

( S T A L A )

1010

0111

44

I

T

P

W

ZPT

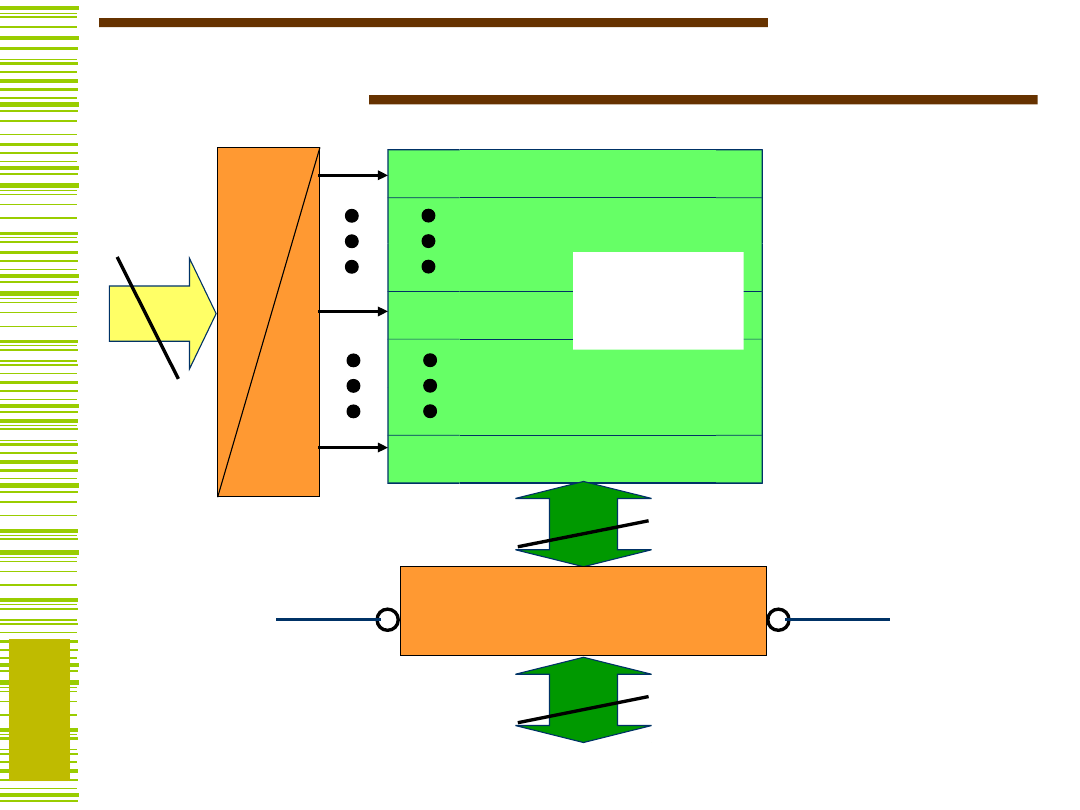

Pamięci typu RAM

matryca

m n

A

X

0

X

i

X

m-1

p

Zapis:

X

i

= DMUX(Y,A,w/r)

Odczyt –

jak w pamięciach

typu ROM

we/wy

danych

n

n

cs

w/r

45

I

T

P

W

ZPT

Pamięci typu RAM - zapis

We danych

matryca

8 4

A

X

0

X

i

X

7

p

w/r

cs

Zapis:

X

i

= DMUX(Y,A,w/r)

1

0

1

5

0 1 0 1

= 0

46

I

T

P

W

ZPT

Synteza strukturalna

Bloki funkcjonalne są stosowane w syntezie:

układów wykonawczych (operacyjnych),

układów sterujących.

Przerzutn

ik

typu D

D

D

Clk

Clk

Q

Q

Y

B

A

n

n

n

Y

n -1

Z

O V R

P

G

c

n

c

0

S

A L U

R

(Q)

s

1

s

2

clock

X

Y

x

l

x

p

L

(Q)

s

1

s

2

clock

X

Y

47

I

T

P

W

ZPT

Synteza strukturalna

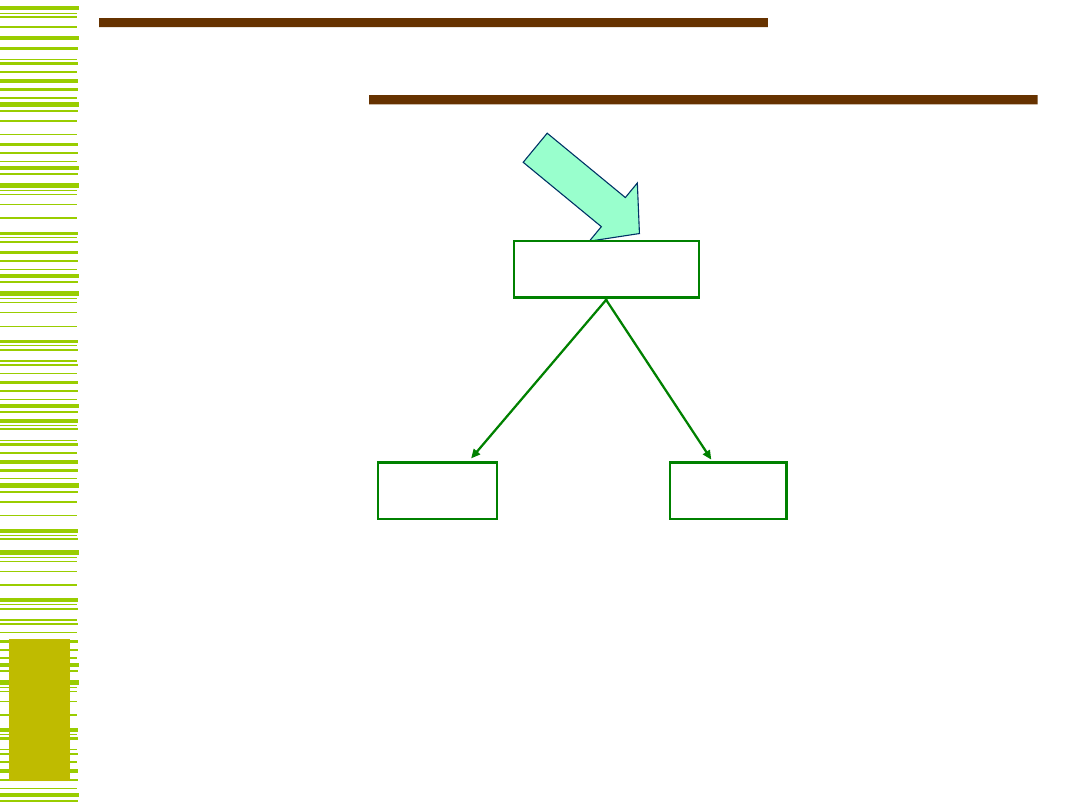

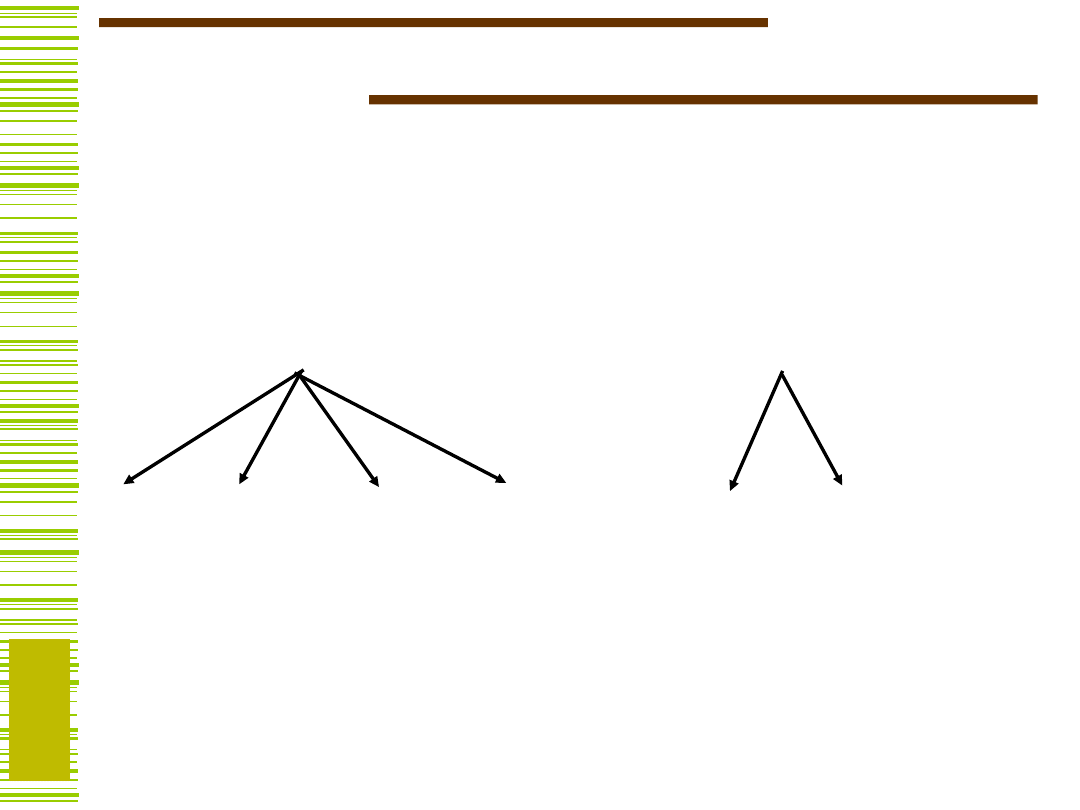

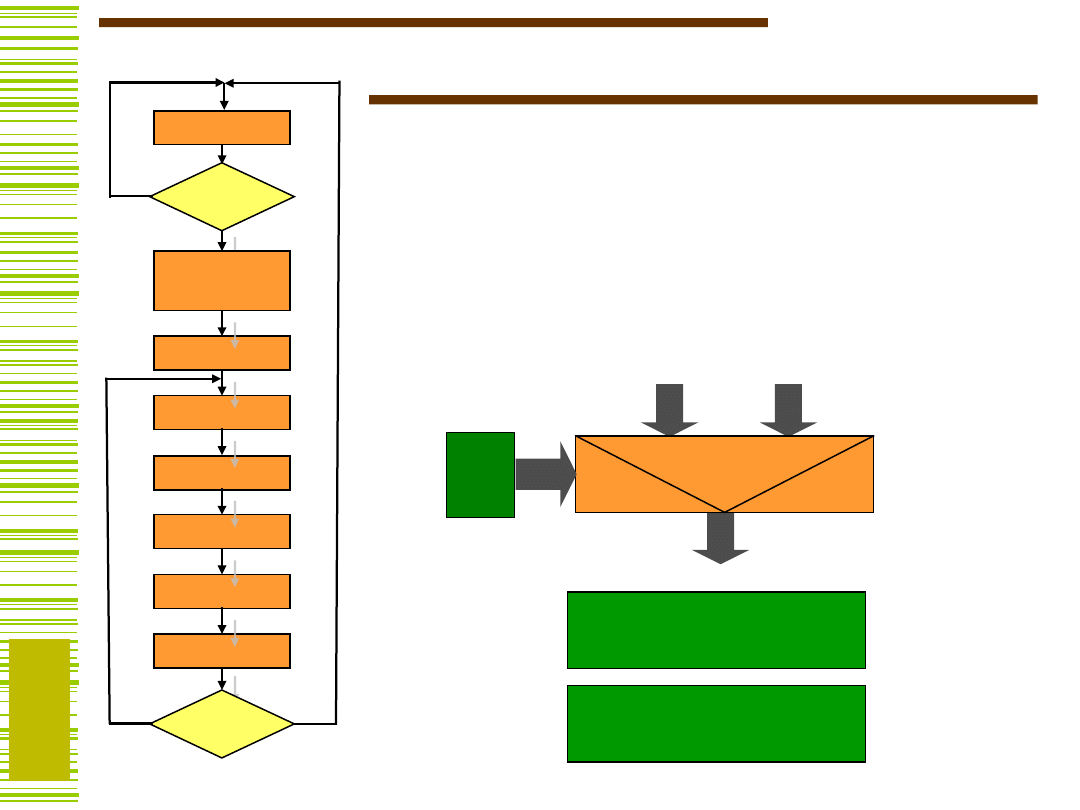

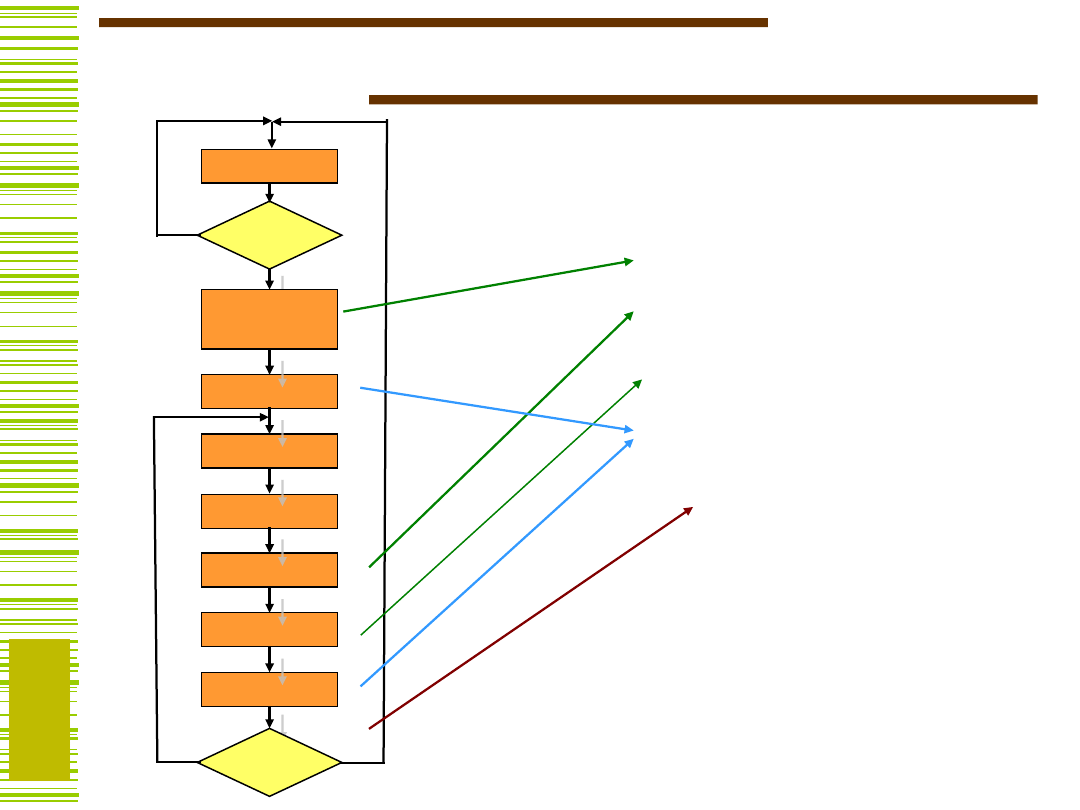

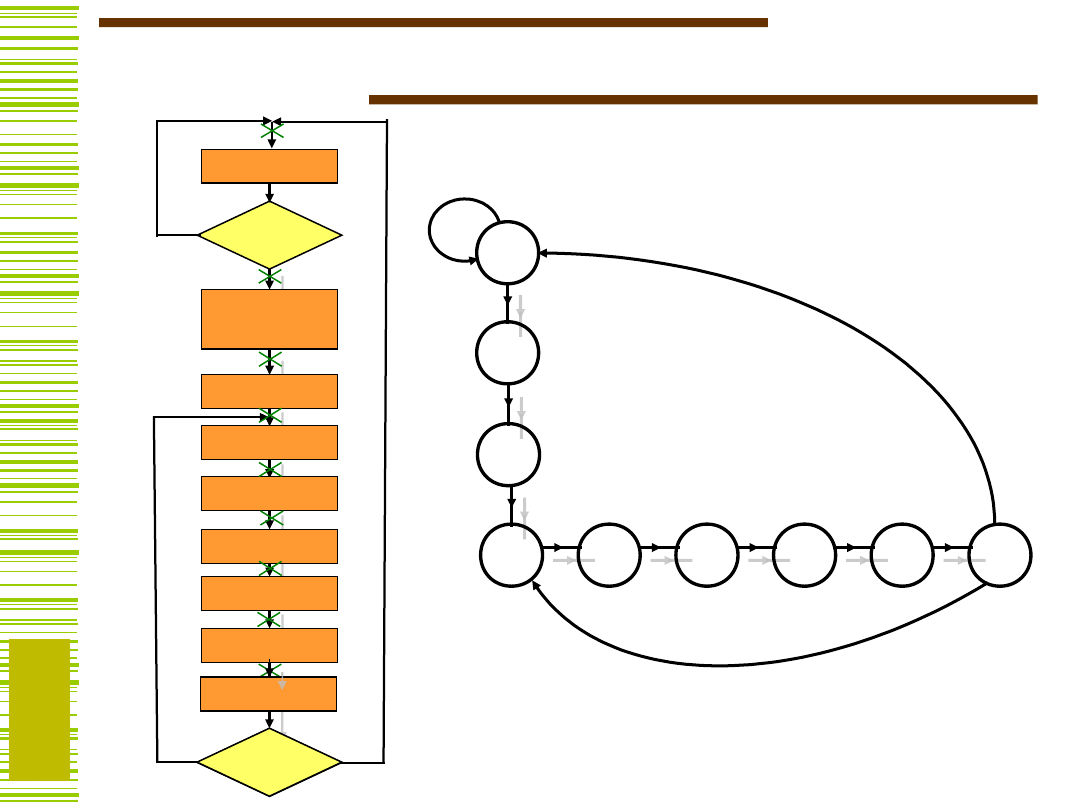

1. Analiza algorytmu pracy układu (sieci działań)

– zmienne, operacje

2. Dobór bloków funkcjonalnych do przechowywania

zmiennych i wykonywania operacji

3. Dobór bloków komutacyjnych

Bloki funkcjonalne są stosowane w syntezie układów

wykonawczych (operacyjnych).

48

I

T

P

W

ZPT

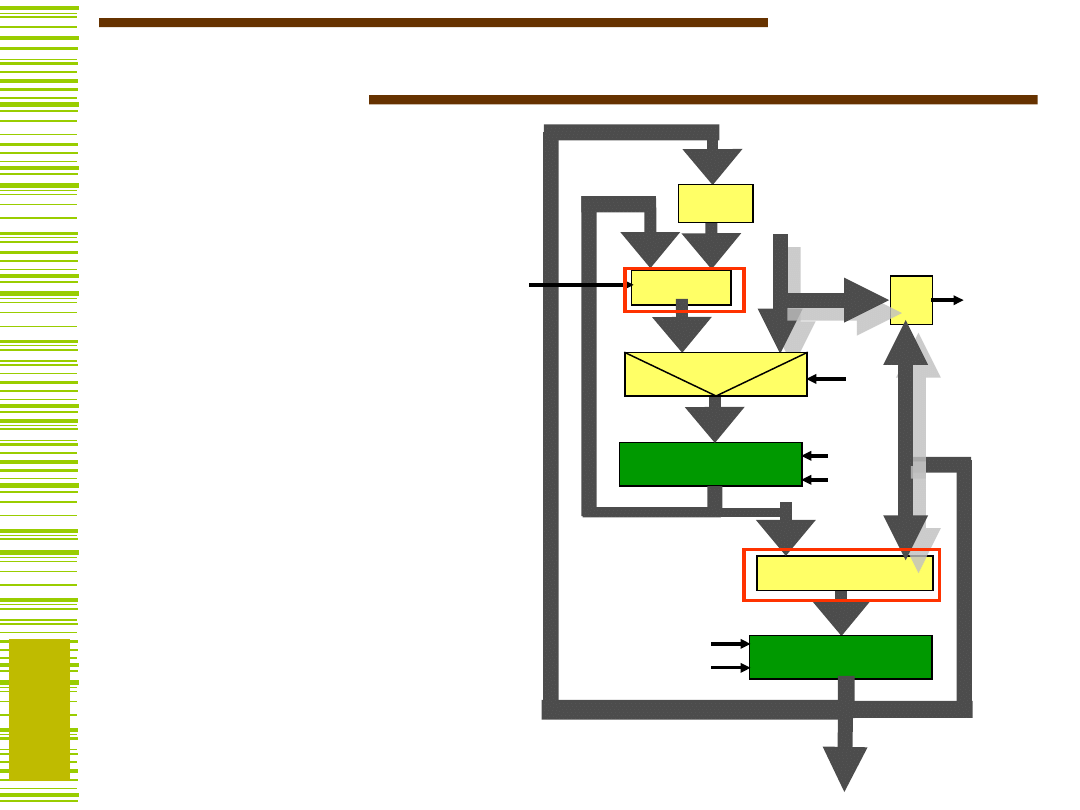

Przykład

B

D

0

D

n-1

Y

M

M(I)

I

S

B := M(I)

Y := 0

B := M(I)

Y := 0

Y = M(I)

Y = M(I)

Y := B + Y

Y := B + Y

I := I + 1

I := I + 1

B := M(I)

B := M(I)

B := B Y

B := B Y

B := B/2

B := B/2

Y := B + Y

Y := B + Y

I := 0

I := 0

NIE

0

1

TAK

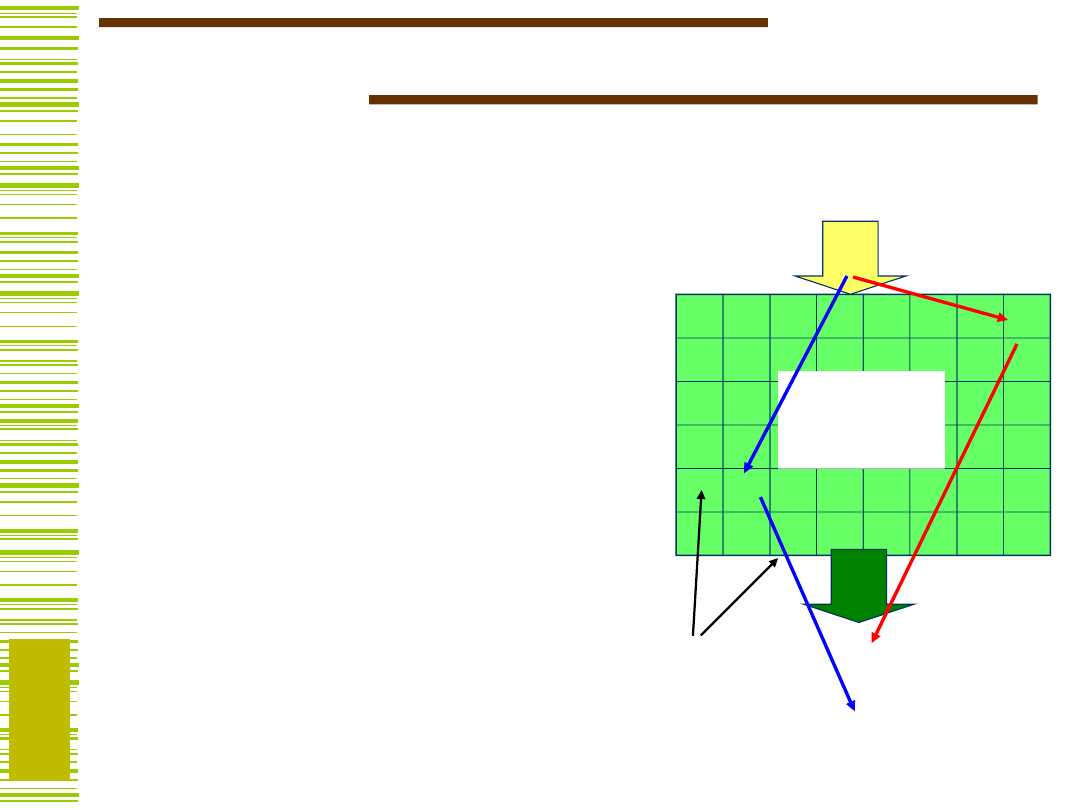

Rozważmy przykład syntezy układu

cyfrowego pobierającego dane z wejść

D

0

,..., D

n–1

w celu ich przetworzenia w

rejestrach B i Y. Układ operacyjny ma

przetwarzać informację M(I ) pobieraną z

n źródeł D

0

,...,D

n–1

za pośrednictwem

multipleksera M adresowanego licznikiem

I.

49

I

T

P

W

ZPT

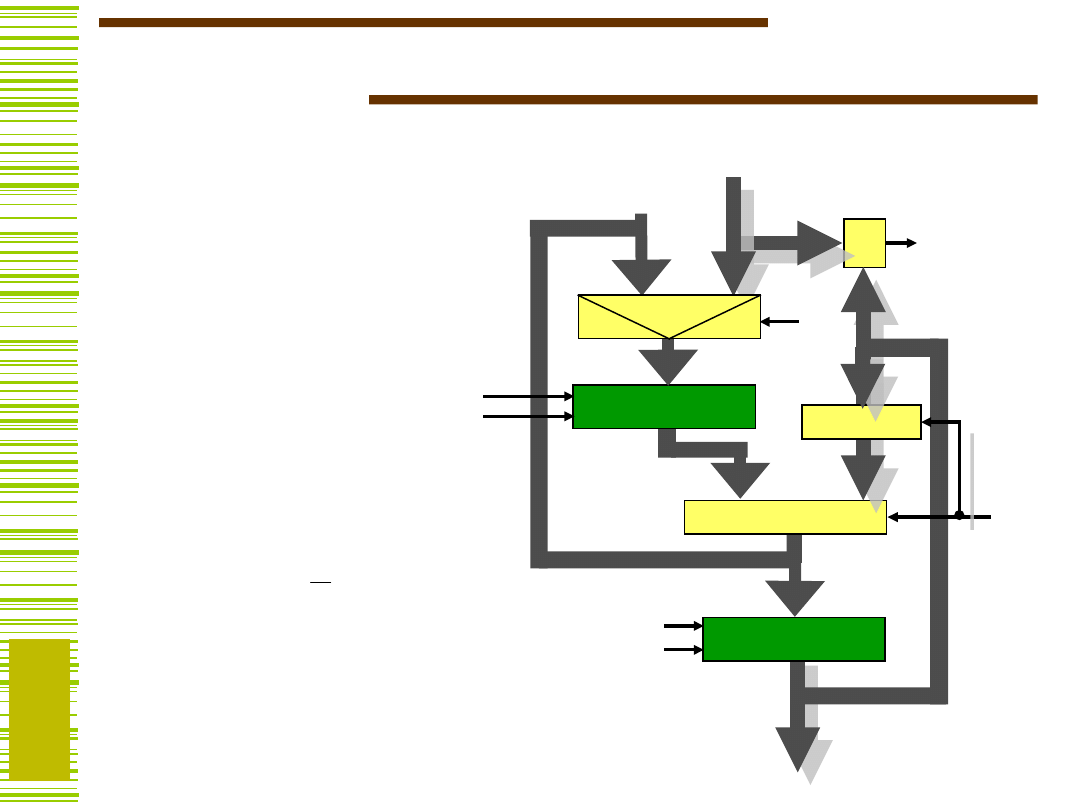

Przykład

S

B := M(I)

Y := 0

B := M(I)

Y := 0

Y = M(I)

Y = M(I)

Y := B + Y

Y := B + Y

I := I + 1

I := I + 1

B := M(I)

B := M(I)

B := B Y

B := B Y

B := B/2

B := B/2

Y := B + Y

Y := B + Y

I := 0

I := 0

NIE

0

1

TAK

B := M(I)

B := M(I)

B := B/2

B := B/2

B := B Y

B := B Y

Y := B + Y

Y := B + Y

Warunek Y = M(I)

Warunek Y = M(I)

50

I

T

P

W

ZPT

B

Y

M(I)

Y

c

0

K

do US

Y = M(I)

Y := 0

Y := B + Y

B := X

B := B/2

X

Przykład c.d.

NOT

B := M(I)

B := M(I)

B := B/2

B := B/2

B := B Y

B := B Y

Y := B + Y

Y := B + Y

Warunek Y = M(I)

Warunek Y = M(I)

(SHR(B))

B := B Y

B := B Y

Y := B + Y

Y := B + Y

51

I

T

P

W

ZPT

Y

Y

K

do US

Y = M(I)

Y := 0

Y := B + Y

X

v

M(I)

B := X

B := B/2

B

Przykład c.d.

B := B Y

B := B Y

Y := B + Y

Y := B + Y

EXOR

1

gdy V

,

Y

0

gdy V

Y,

Y

V

52

I

T

P

W

ZPT

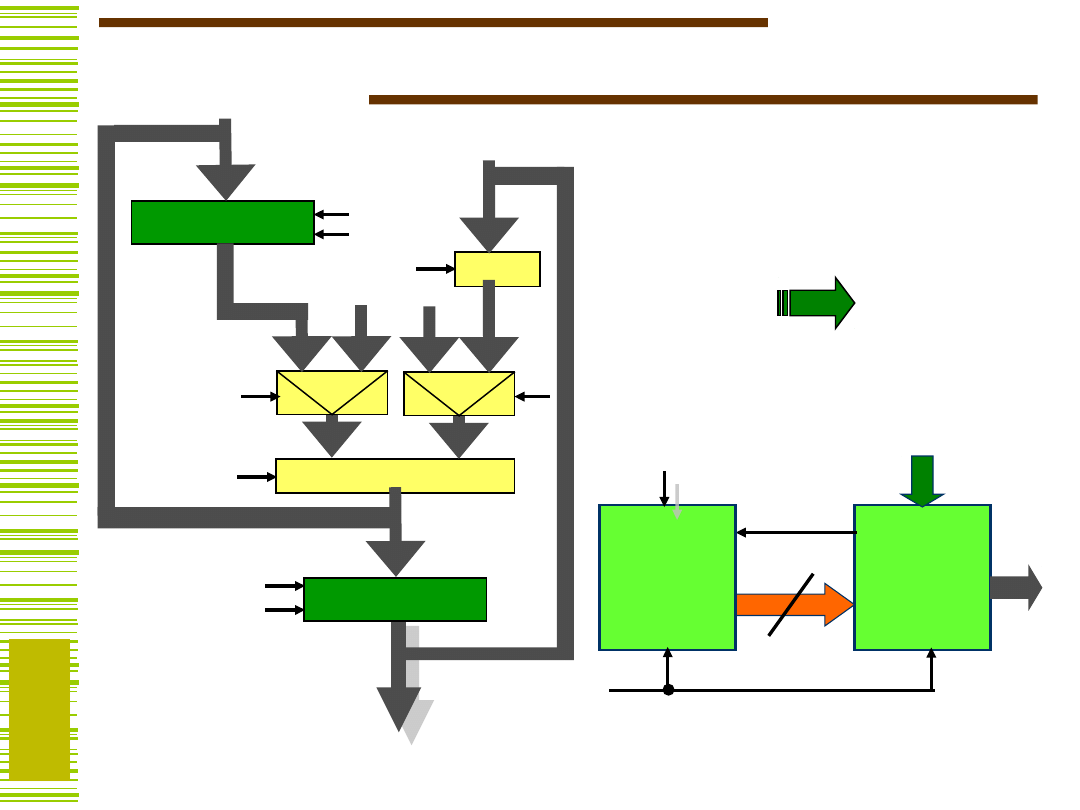

Przykład c.d.

UO

M(I)

Y

Y = M(I)

7 (+2)

US

S

B

Y

M(I)

Y := 0

Y := B + Y

X

B := X

B := B/2

EXOR

v

c

0

Y

0

v

B Y

B Y

B + Y

B + Y

Warunek

Y = M(I)

Warunek

Y = M(I)

Warunek

F = M(I) – Y = 0

Warunek

F = M(I) – Y = 0

F

53

I

T

P

W

ZPT

Przykład c.d.

S

B := M(I)

Y := 0

B := M(I)

Y := 0

Y := B + Y

Y := B + Y

I := I + 1

I := I + 1

B := M(I)

B := M(I)

B := B Y

B := B Y

B := B/2

B := B/2

Y := B + Y

Y := B + Y

I := 0

I := 0

NIE

0

1

TAK

A

8

A

1

Y = M(I)

Y = M(I)

A

0

A

2

A

3

A

4

A

5

A

6

A

7

F = M(I) – Y

F = M(I) – Y

F = 0

F = 0

S = x

0

S = x

0

[F = 0] = x

1

[F = 0] = x

1

- -

A

0

/Z

1

A

0

/Z

1

A

1

/Z

2

A

1

/Z

2

A

2

/Z

3

A

2

/Z

3

A

3

/Z

4

A

3

/Z

4

A

4

/Z

5

A

4

/Z

5

A

5

/Z

6

A

5

/Z

6

A

6

/Z

7

A

6

/Z

7

A

7

/Z

8

A

7

/Z

8

A

8

/Z

9

A

8

/Z

9

- -

- -

- -

- 1

- 0

- -

- -

- -

1 -

0 -

x

1

x

0

x

1

x

0

54

I

T

P

W

ZPT

Przykład c.d.

x

1

x

0

A

00 01 11 10

Z

A

0

A

0

A

1

A

1

A

0

Z

1

A

1

A

2

A

2

A

2

A

2

Z

2

A

2

A

3

A

3

A

3

A

3

Z

3

A

3

A

4

A

4

A

4

A

4

Z

4

A

4

A

5

A

5

A

5

A

5

Z

5

A

5

A

6

A

6

A

6

A

6

Z

6

A

6

A

7

A

7

A

7

A

7

Z

7

A

7

A

8

A

8

A

8

A

8

Z

8

A

8

A

3

A

3

A

0

A

0

Z

9

- -

A

0

/Z

1

A

0

/Z

1

A

1

/Z

2

A

1

/Z

2

A

2

/Z

3

A

2

/Z

3

A

3

/Z

4

A

3

/Z

4

A

4

/Z

5

A

4

/Z

5

A

5

/Z

6

A

5

/Z

6

A

6

/Z

7

A

6

/Z

7

A

7

/Z

8

A

7

/Z

8

A

8

/Z

9

A

8

/Z

9

- -

- -

- -

- 1

- 0

- -

- -

- -

1 -

0 -

x

1

x

0

x

1

x

0

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Slide 46

- Slide 47

- Slide 48

- Slide 49

- Slide 50

- Slide 51

- Slide 52

- Slide 53

- Slide 54

Wyszukiwarka

Podobne podstrony:

W9a

ulogt w9b

ulogt w9

ulogt pr 07, Teoria automatów, ŁubaT

ulogt w13

W9A Obrobka cieplno chemiczna

ulog w9a

w9A Statycznie wyznaczalne konstr pretowe

W9a 2014 Podatek od towarów i us ug

W9A Obróbka wykończeniowa TS

więcej podobnych podstron