Procesory sygnałowe

Wykład 6

Architektura procesora

ADSP-21065L (pamięć Cache,

adresowanie)

Dr inż. Robert

Wielgat

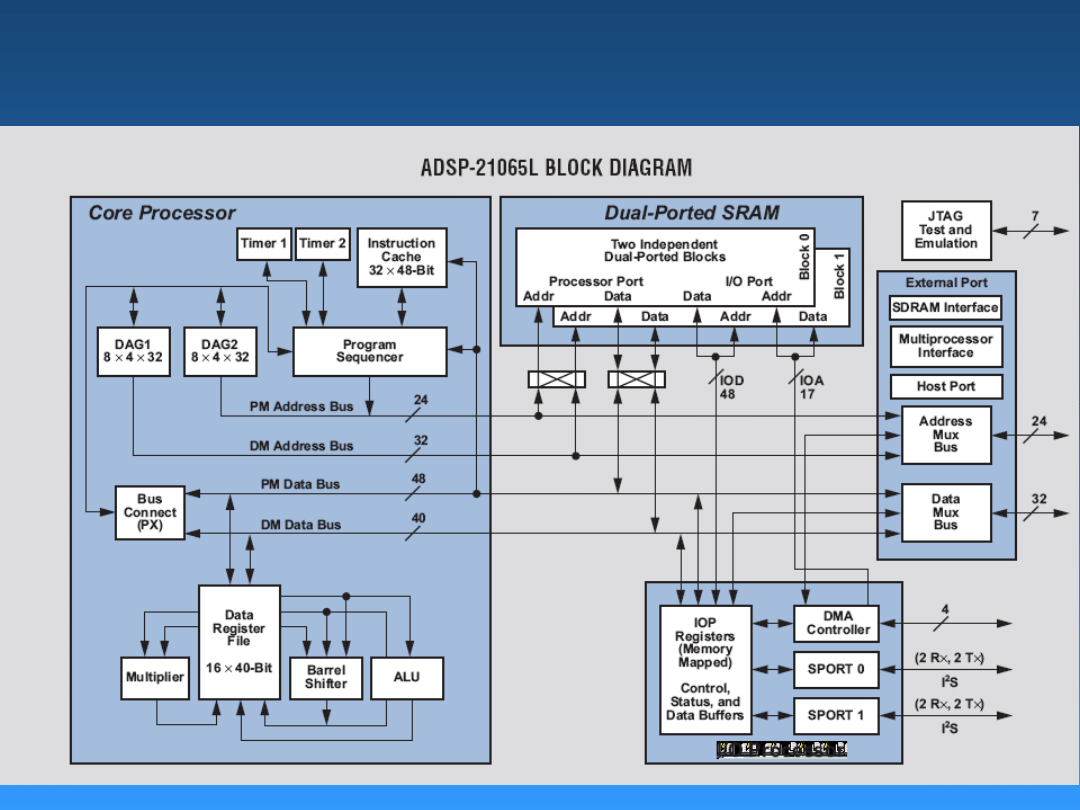

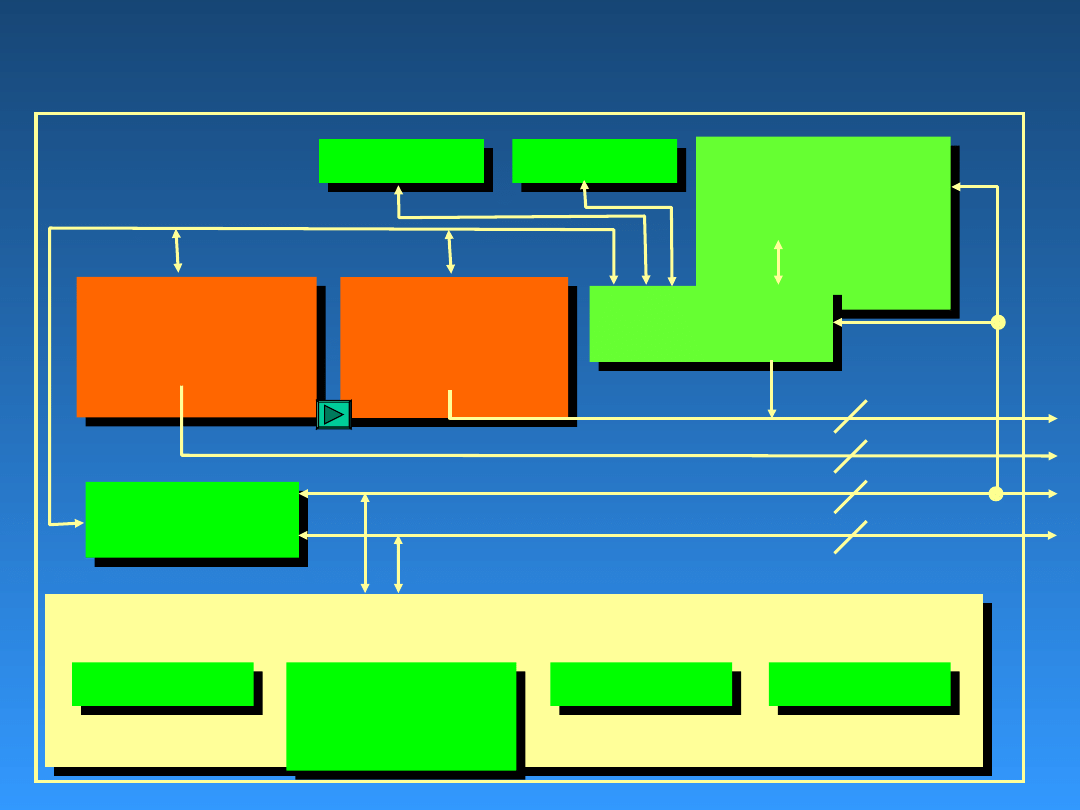

Schemat blokowy ADSP-

21065L

Rdzeń procesora ADSP-

21065L

Timer 1

Timer 1

Timer 2

Timer 2

Pamięć

podręczna

(cache)

instrukcji

32 x 48 bitów

Pamięć

podręczna

(cache)

instrukcji

32 x 48 bitów

Generator

adresu 1 (DAG

1)

8 x 4 x 32

Generator

adresu 1 (DAG

1)

8 x 4 x 32

Generator

adresu 2 (DAG

2)

8 x 4 x 24

Generator

adresu 2 (DAG

2)

8 x 4 x 24

Sekwenter

programowy

Sekwenter

programowy

Bus Connect

(PX)

Bus Connect

(PX)

Mnożarka

Mnożarka

Zbiór

rejestrów

16 x 40 bitów

Zbiór

rejestrów

16 x 40 bitów

Przesuwni

k bitowy

Przesuwni

k bitowy

ALU

ALU

Jednostki obliczeniowe

32

24

40

48

DMA Bus

PMA Bus

DMD Bus

PMD Bus

Pamięć Cache

Procesor posiada wbudowaną pamięć podręczną do

przechowywania instrukcji (nie danych)

Własności:

• Procesor zapisuje do pamięci podręcznej tylko te instrukcje,

które powodują konflikt w dostępie do danych z pamięci

programu przesyłanych przez magistralę PMD, gdzie adres danej

jest wystawiany przez generator adresów DAG2 .

• Ze względu na realizację rozkazów przez trójetapowy Potok

instrukcja wykonywana

(Faza I) wymagająca dostępu do danych z

pamięci programu powoduje

konflikt z instrukcją

o adresie o 2

większym, która znajduje się

w fazie pobrania

(Faza III). Ta

ostatnia instrukcja zostaje pobrana do pamięci podręcznej.

• Jeżeli wymagana instrukcja znajduje się w pamięci Cache

(trafienie ang. cache hit)

, to może być z niej pobrana w trakcie

odczytu przez procesor danej z magistrali danych pamięci

programu. W przeciwnym razie

(cache miss)

instrukcja jest

pobierana z pamięci programu w cyklu następującym po

pobraniu danej z magistrali danych pamięci programu. Pobrana

instrukcja jest umieszczana w pamięci Cache.

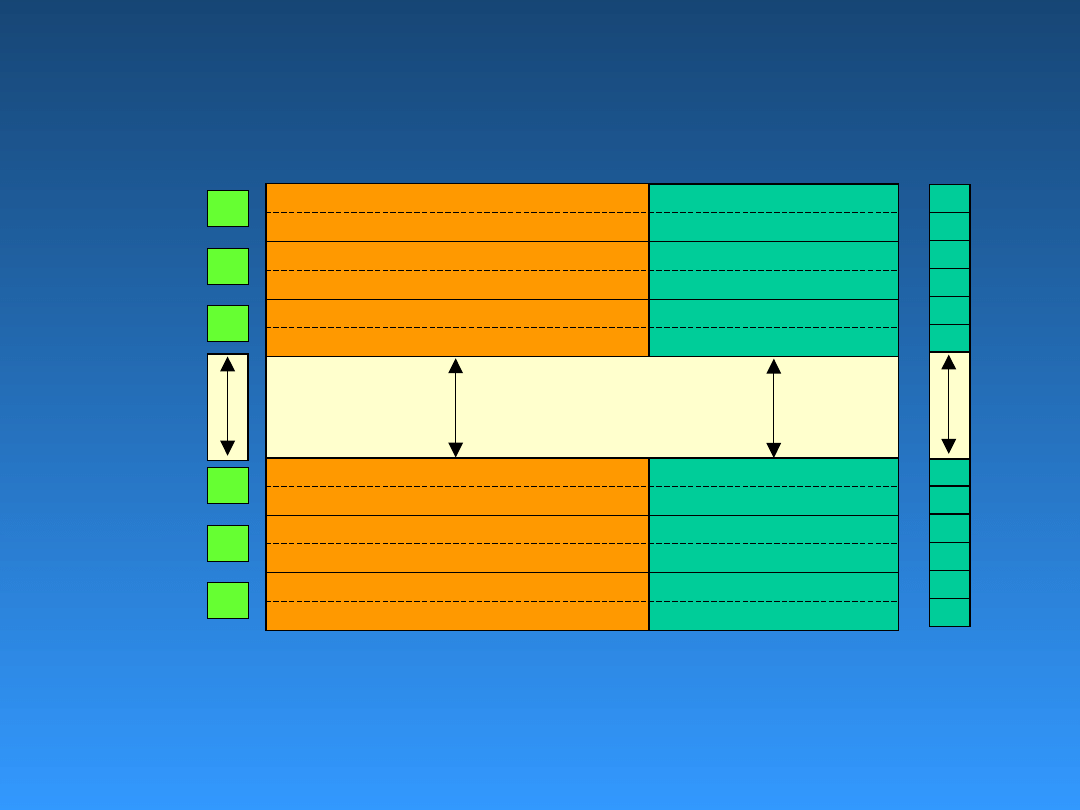

Architektura pamięci Cache

Pamięć Cache zawiera 32 wpisy zorganizowane w 16 zbiorów

po 2 wpisy.

LRU (ang. Least Recently Used) – bit, którego wartość

wskazuje na zbiór z wpisem najmniej używanym.

Bit ważności - ustawiany, jeżeli wpis zawiera ważną instrukcję.

1

Zbiór

0

W p i s 0

W p i s 1

0

Zbiór

1

W p i s 2

W p i s 3

1

Zbiór

2

W p i s 4

W p i s 5

1

Zbiór

13

W p i s

26

W p i s

27

1

Zbiór

14

W p i s

28

W p i s

29

0

Zbiór

15

W p i s

30

W p i s

31

Bit

LRU

Bit

ważności

Kod

rozkaz

u

Adres

Działanie pamięci Cache

• Umieszczenie w Cach’u instrukcji wraz z adresem dokonywane

jest na podstawie 4 najmłodszych bitów adresu rozważanej

instrukcji np. adres 234h spowoduje wybranie 4 zbioru wpisów

• W polu adres są zapisywane bity 23:4,

• Procesor wykorzystuje 4 najmłodsze bity adresu jako wskaźnik

do pamięci podręcznej. Wskaźnik ten pokazuje na dwa wpisy

umieszczone w zbiorze o indeksie wskazywanym przez 4

najmłodsze bity. Jeżeli procesor pobiera instrukcję sprawdza

obydwa wpisy.

• Jeżeli nastąpiło trafienie procesor uaktualnia bit LRU.

• Jeżeli trafienie nie wystąpiło procesor ładuje nową instrukcję

wraz z adresem na pozycję wskazaną przez 4 najmłodsze bity

adresu, która była najmniej używana.

• Pamięć Cache może być:

Zamrożona

. Zabezpiecza to przed dokonywaniem jakichkolwiek

zmian w pamięci w przypadku braku trafienia. (bit CAFRZ=1,

rejestr MODE2)

Wyłączona.

Wszystkie operacje na pamięci zablokowane.

Wszystkie pobrania powodujące konflikt następują z

opóźnieniem. (bit CADIS=1, rejestr MODE2)

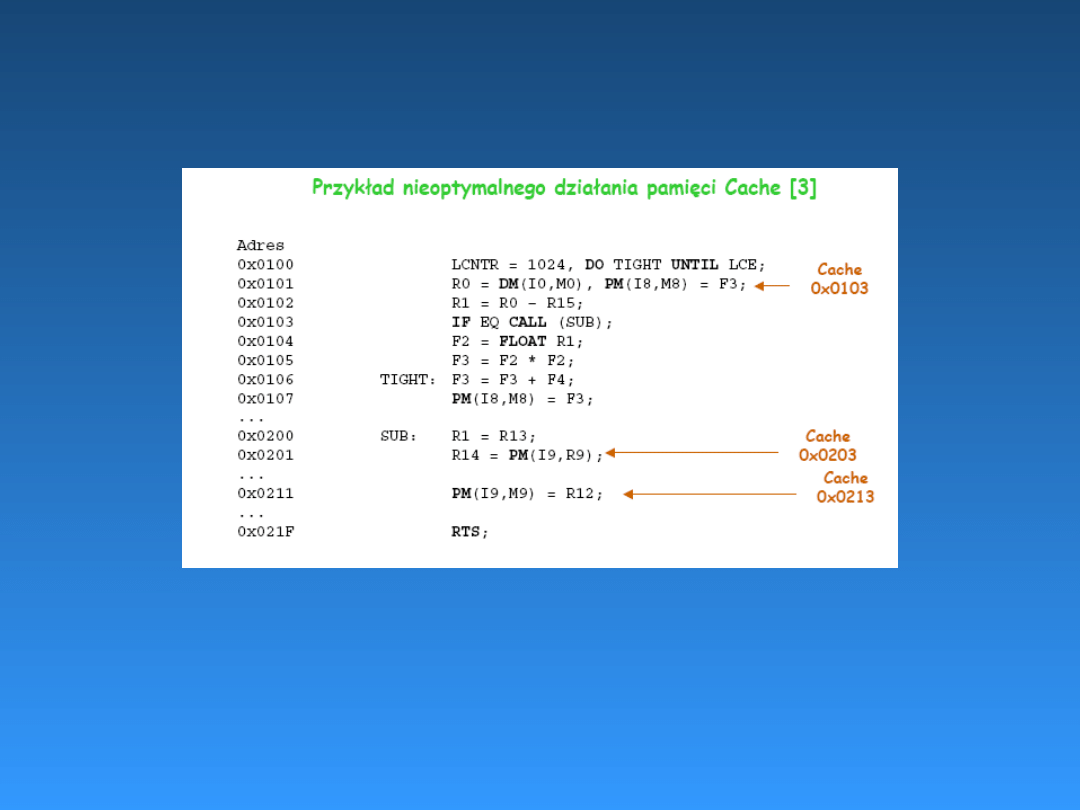

Nieoptymalne działanie

pamięci podręcznej - przykład

W przedstawionym powyżej kodzie programu do pamięci

podręcznej do tego samego zbioru (czyli do 3 zbioru) są

naprzemiennie pobierane trzy instrukcje przez co przy każdym

pobraniu występuje sytuacja chybienia pamięci podręcznej

(Cache miss). Powoduje to nieefektywne działanie pamięci

podręcznej.

Rdzeń procesora ADSP-

21065L

Timer 1

Timer 1

Timer 2

Timer 2

Pamięć

podręczna

(cache)

instrukcji

32 x 48 bitów

Pamięć

podręczna

(cache)

instrukcji

32 x 48 bitów

Generator

adresu 1 (DAG

1)

8 x 4 x 32

Generator

adresu 1 (DAG

1)

8 x 4 x 32

Generator

adresu 2 (DAG

2)

8 x 4 x 24

Generator

adresu 2 (DAG

2)

8 x 4 x 24

Sekwenter

programowy

Sekwenter

programowy

Bus Connect

(PX)

Bus Connect

(PX)

Mnożarka

Mnożarka

Zbiór

rejestrów

16 x 40 bitów

Zbiór

rejestrów

16 x 40 bitów

Shifter

Shifter

ALU

ALU

Jednostki obliczeniowe

32

24

40

48

DMA Bus

PMA Bus

DMD Bus

PMD Bus

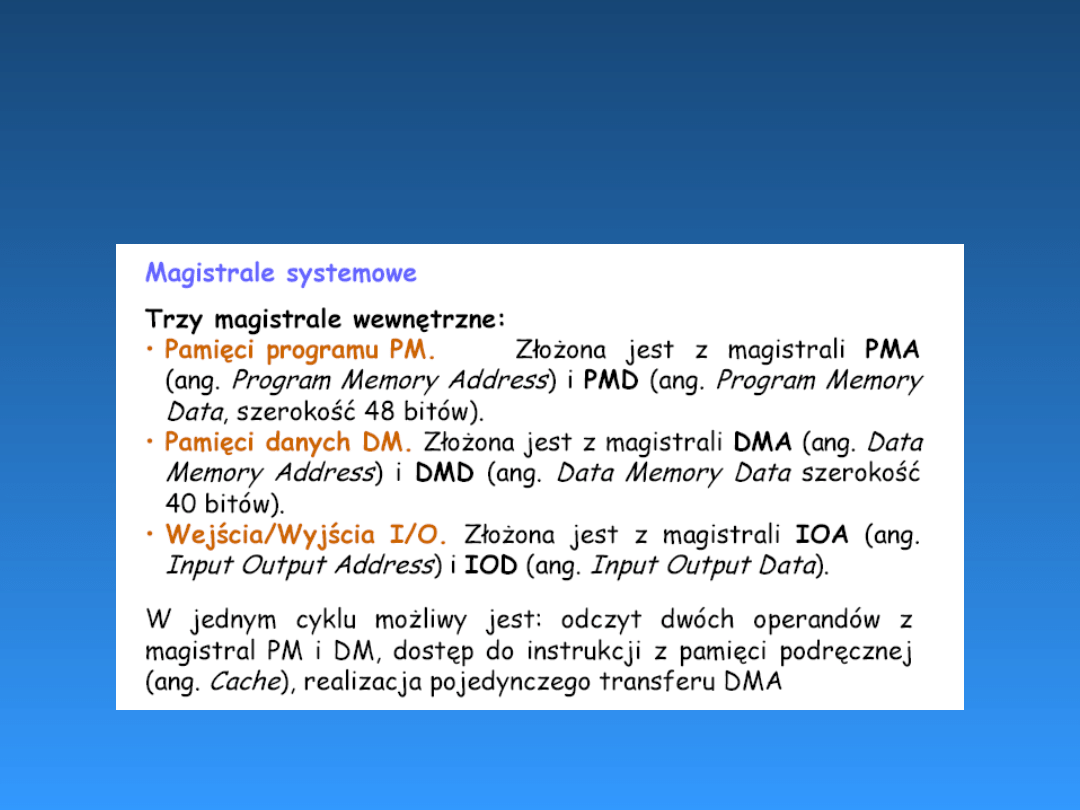

Adresowanie

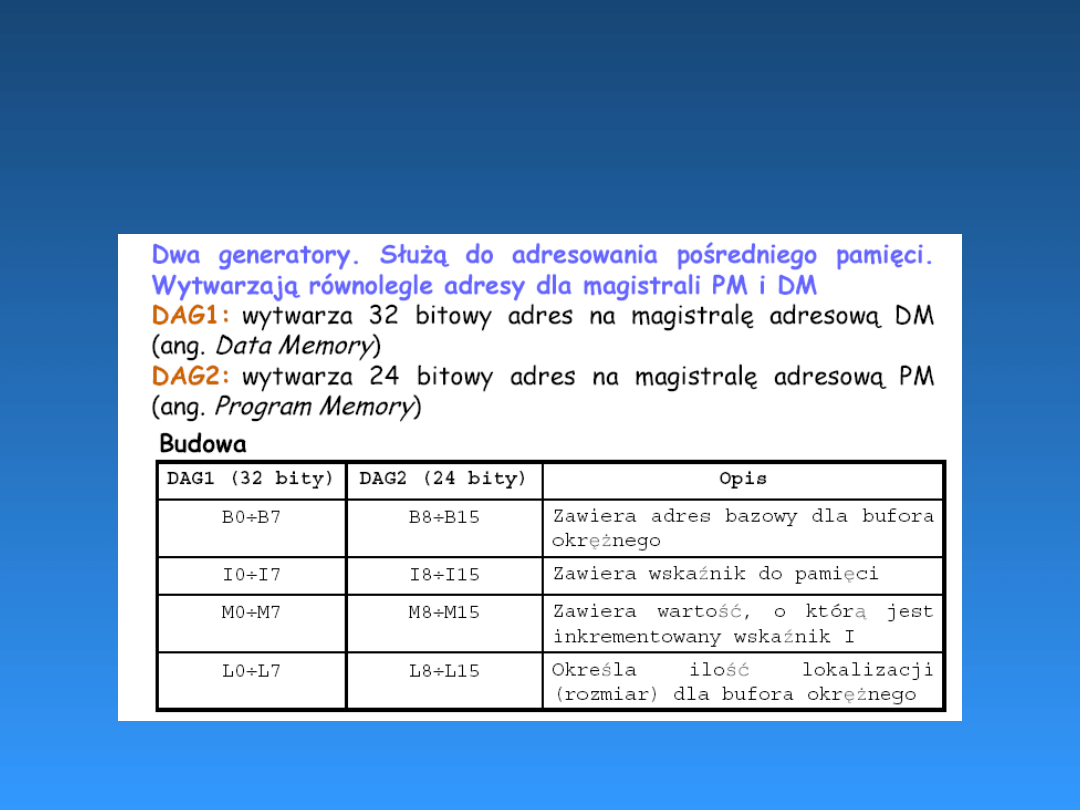

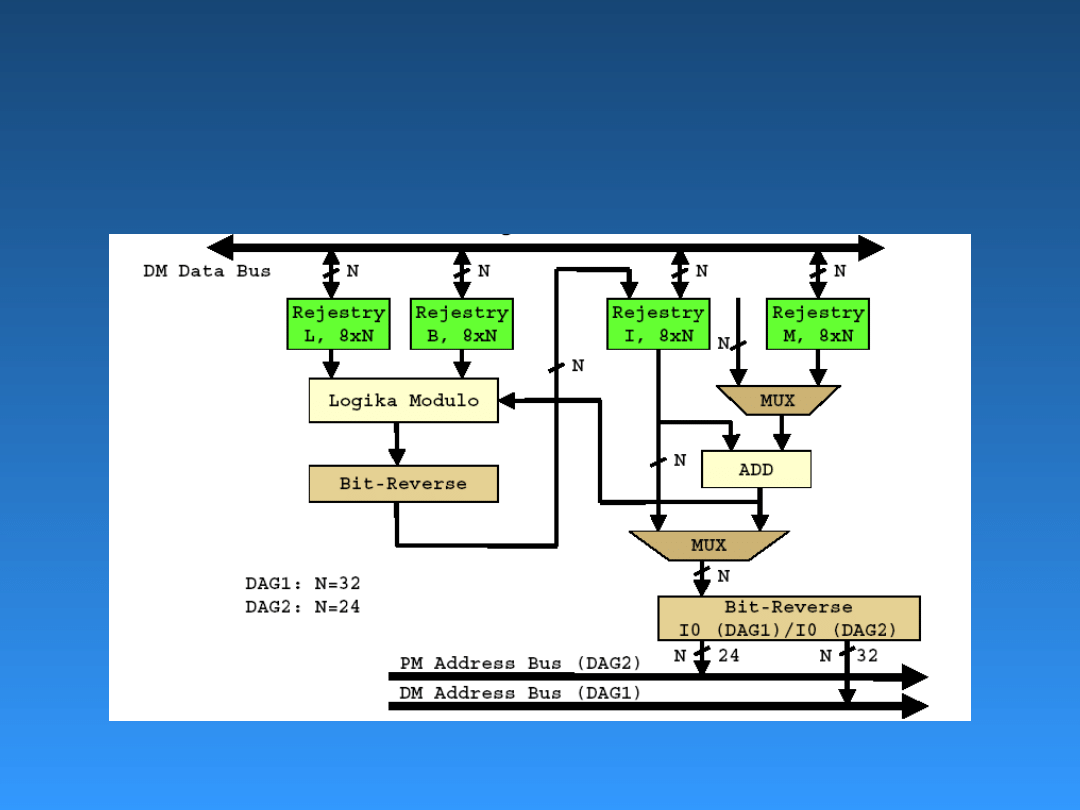

Generatory adresów

Architektura generatorów

adresów DAG

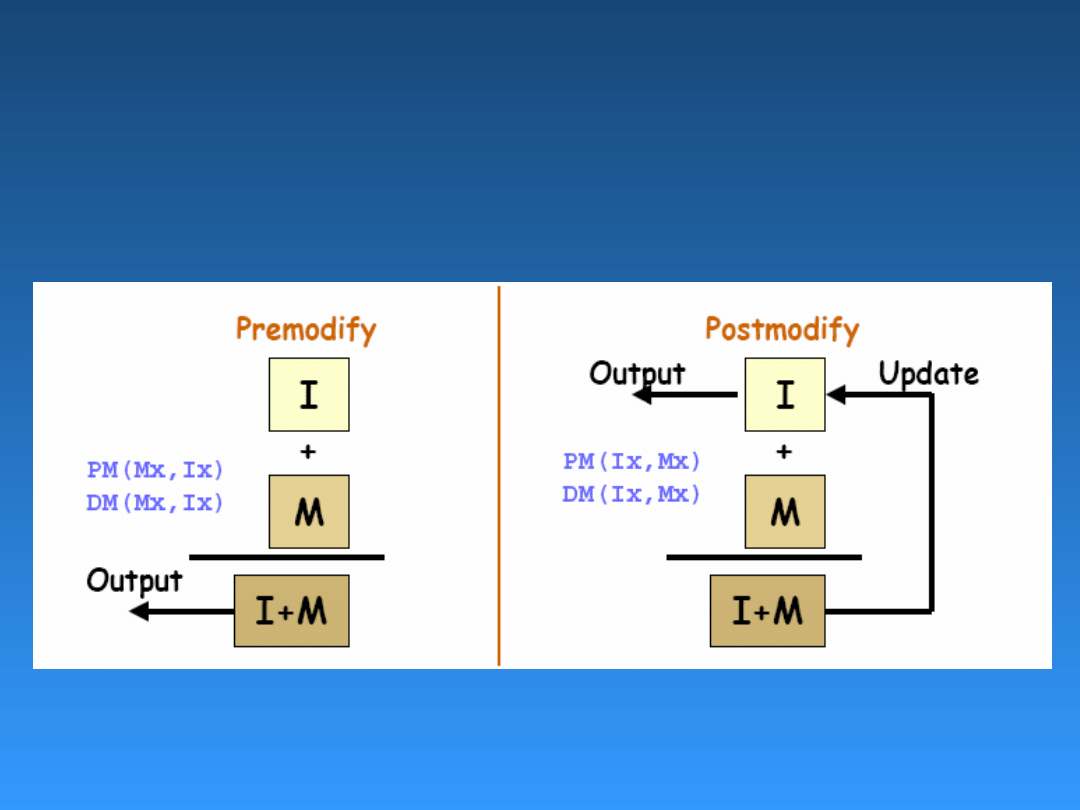

Tryby adresowania

pośredniego

W trakcie używania adresowania z postmodyfikacją bez

implementacji bufora kołowego do rejestru Lx należy wpisać

zero.

Są możliwe następujące tryby adresowania

pośredniego:

Liniowe

typu

premodify

i

postmodify

,

Modulo

– umożliwiające realizację bufora

kołowego,

Bit-reverse

- wykorzystywane przy obliczeniach

FFT.

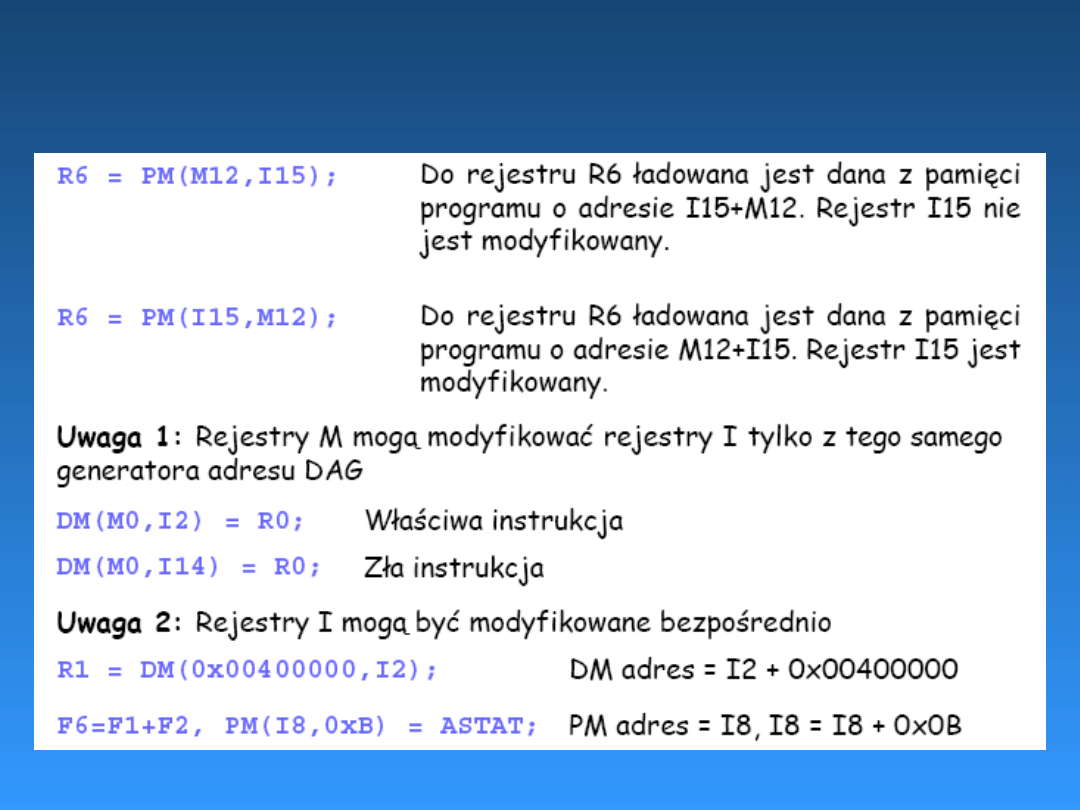

Przykłady adresowania

liniowego

Błędy !

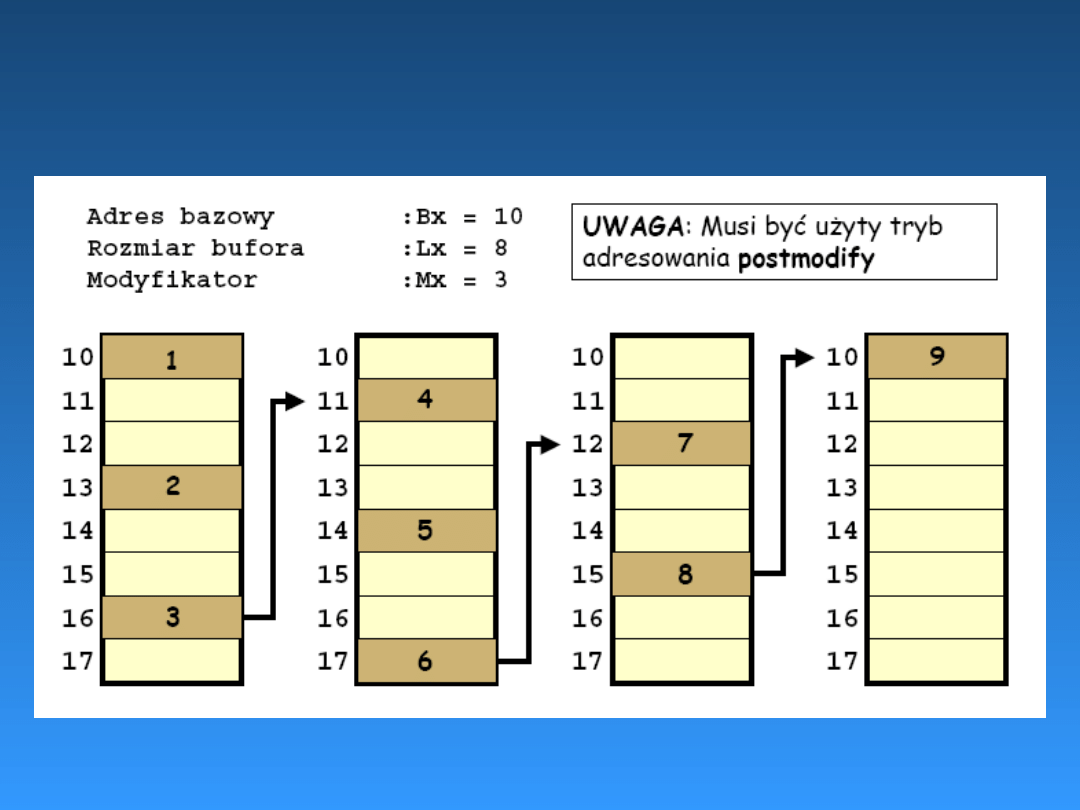

Realizacja bufora kołowego

Realizacja bufora kołowego

w asemblerze

B0=0xC000;

// inicjalizacja rejestru bazowego B0 określającego

początek

// bufora kołowego w pamięci. Procesor

automatycznie

// załaduje tą wartość do rejestru I0.

L0 = 7;

// Inicjalizacja rejestru L0 określającego

rozmiar bufora

// cyklicznego.

M1=1;

// Inicjalizacja rejestru M1 określającego

modyfikator adresu

// (rejestru I0)

LCNTR=16, DO (lop1-1) UNTIL LCE;

R2 = DM(I0,M0);

// Realizacja odczytu z pamięci w

ramach bufora

lop1:

//kołowego

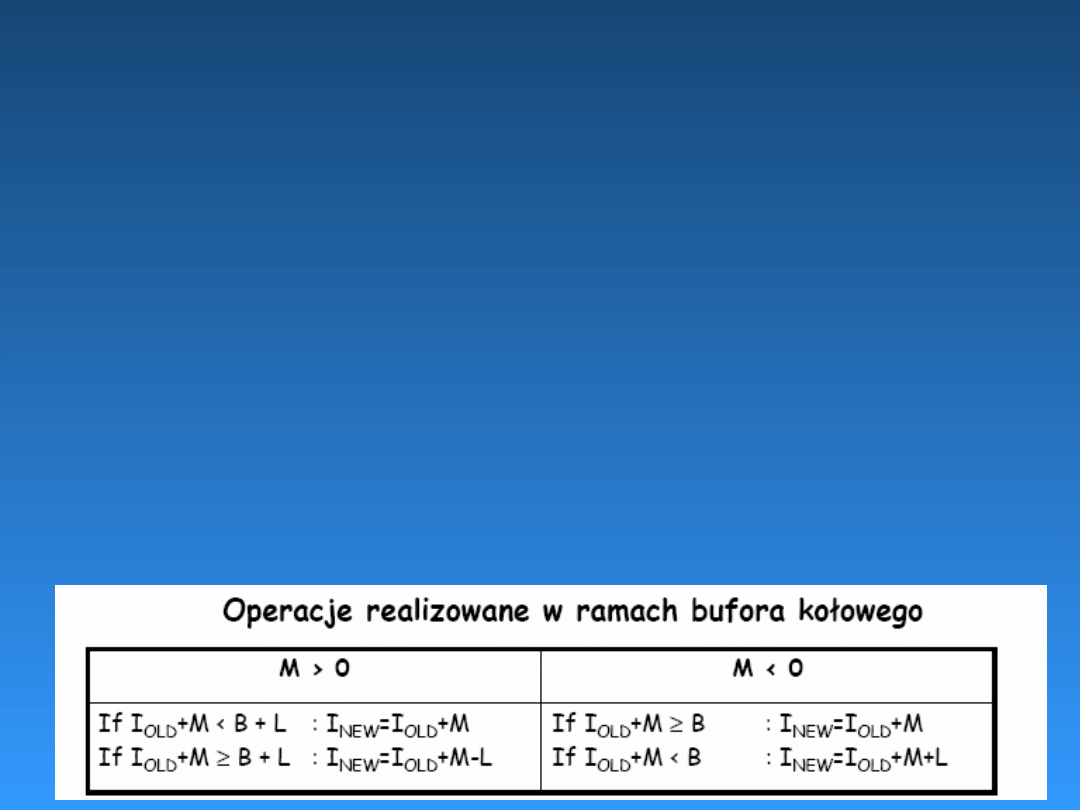

Uwagi do realizacji bufora

kołowego

•Załadowanie wartości do rejestru

Bx

powoduje

automatyczne przepisanie tej wartości do rejestru

Ix

(w

odwrotnym kieunku operacja nie zachodzi)

•Rejestry

Mx

i

Ix

muszą być użyte w ramach tego samego

układu

DAG

, przy czym numer rejestru

Mx

nie musi

korespondować z numerem rejestru

Ix

•Do modyfikacji adresu można użyć bezpośrednio wartości

liczbowej np.

R0=DM(I0,0x00002314)

,

•Wartość ładowana do rejestrów

Lx

musi być > 0 i nie

może być większa niż

2

31

-1

(

DAG1

) lub

2

23

-1

(

DAG2

),

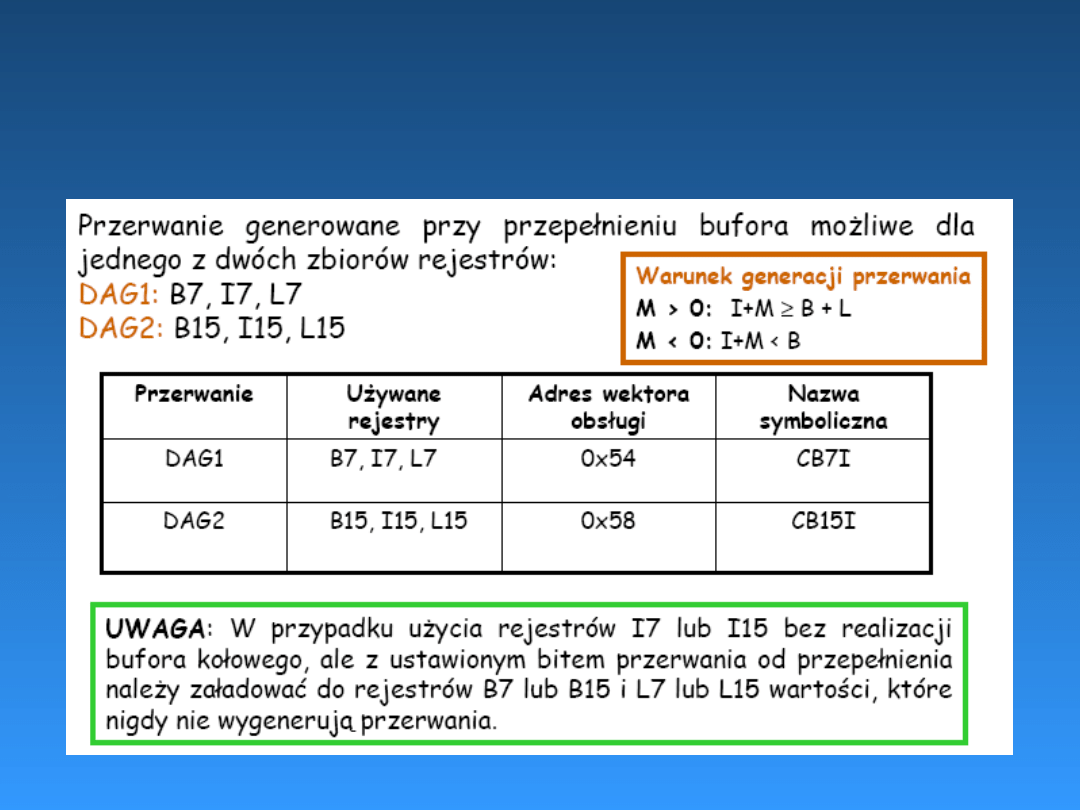

Przerwanie od przepełnienia

bufora kołowego

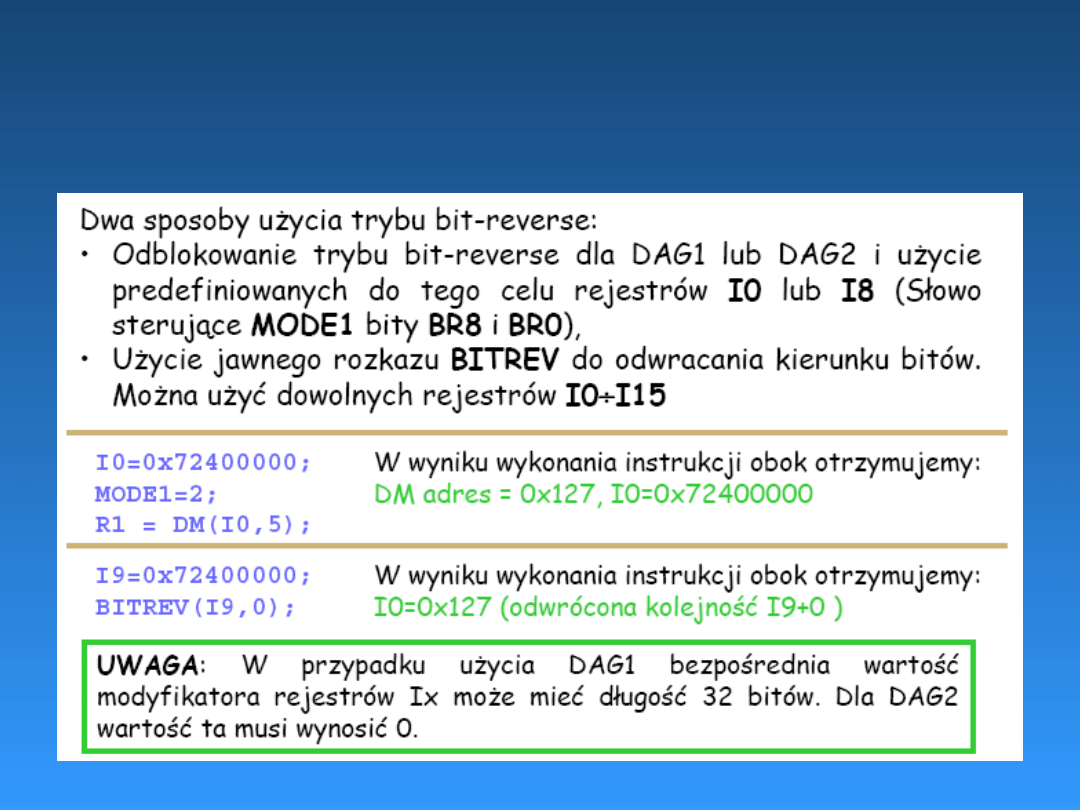

Adresowanie typu bit-

reversed

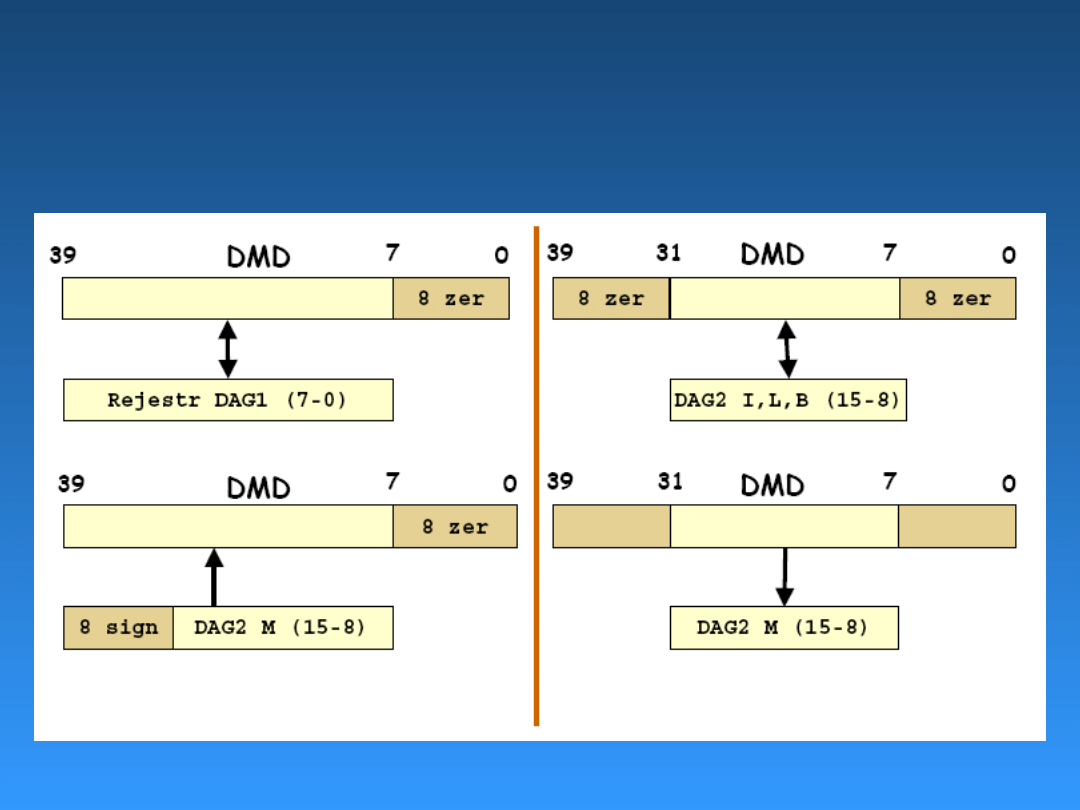

Transfer danych z

generatorów adresów

Literatura

1) Analog Devices, ADSP-21065L SHARC

®

DSP.

User’s Manual, USA, 2003. Strony (160-181)

Dokumentację można pobrać ze strony

2) Jacek Augustyn, „Asemblery μC51, ADSP-

21065L SHARC”, Wydawnictwa Naukowo-

Dydaktyczne PWSZ w Tarnowie, Wyd.

IGSMiE PAN, Kraków 2006, str. 247 – 278

(Rozdział 8)

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

Wyszukiwarka

Podobne podstrony:

Lab4 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

lab9 procesory sygnalowe, LABORATORIUM

6 Procesy i sygnaly

16 procesory sygnalowe ADSP21

Procesory sygnałowe 1

Procesory sygnałowe 2

Procesory sygnałowe 4

Lab1 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Lab5 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Procesory sygnałowe 3

Sitek-wykłady, Komunikacja między procesami, Komunikacja między procesami: sygnały

ele4 z2, 7 semestr, Procesory Sygnałowe, Laboratoria

Instrukcja PS1, 7 semestr, Procesory Sygnałowe, Laboratoria

Procesory sygnałowe 3

Ćwiczenie 18 & 19 Procesory Sygnalowe

Procesory sygnałowe 7

Procesory sygnałowe 2

Lab2 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Lab3 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

więcej podobnych podstron