Procesory sygnałowe

Wykład 2

Płyta uruchomieniowa

ADSP 21065L EZ-KIT Lite,

przykłady w języku C

Dr inż. Robert

Wielgat

Tarnów 2014

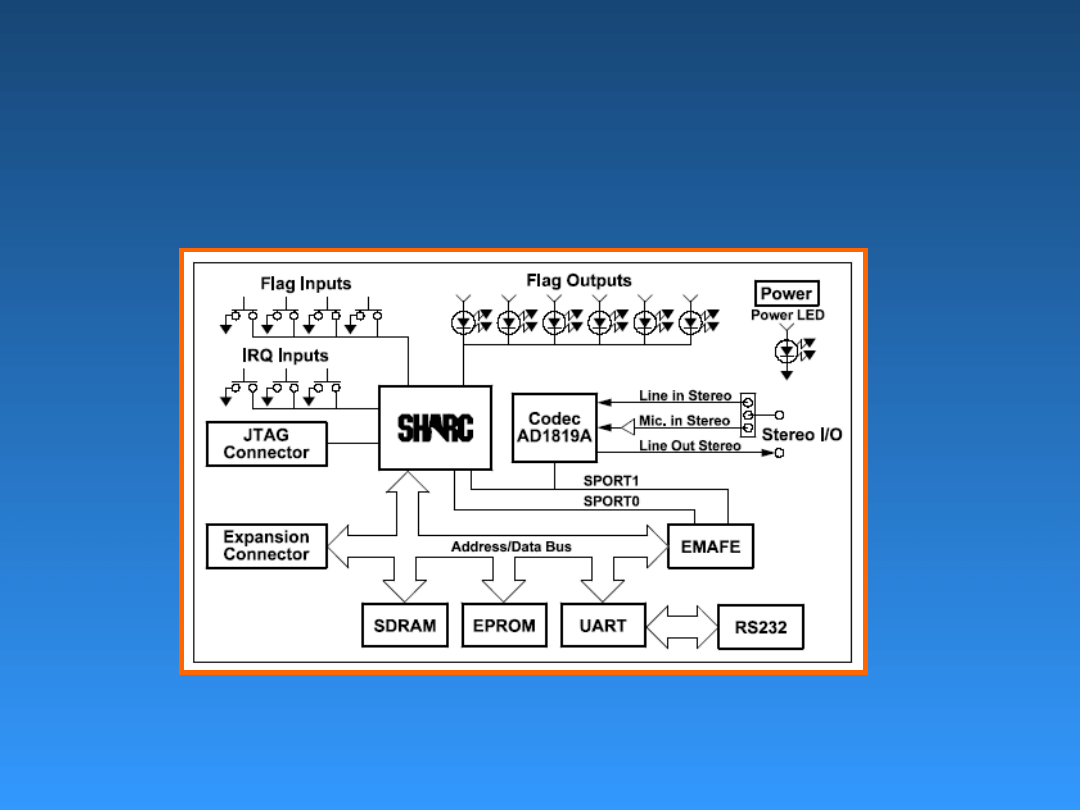

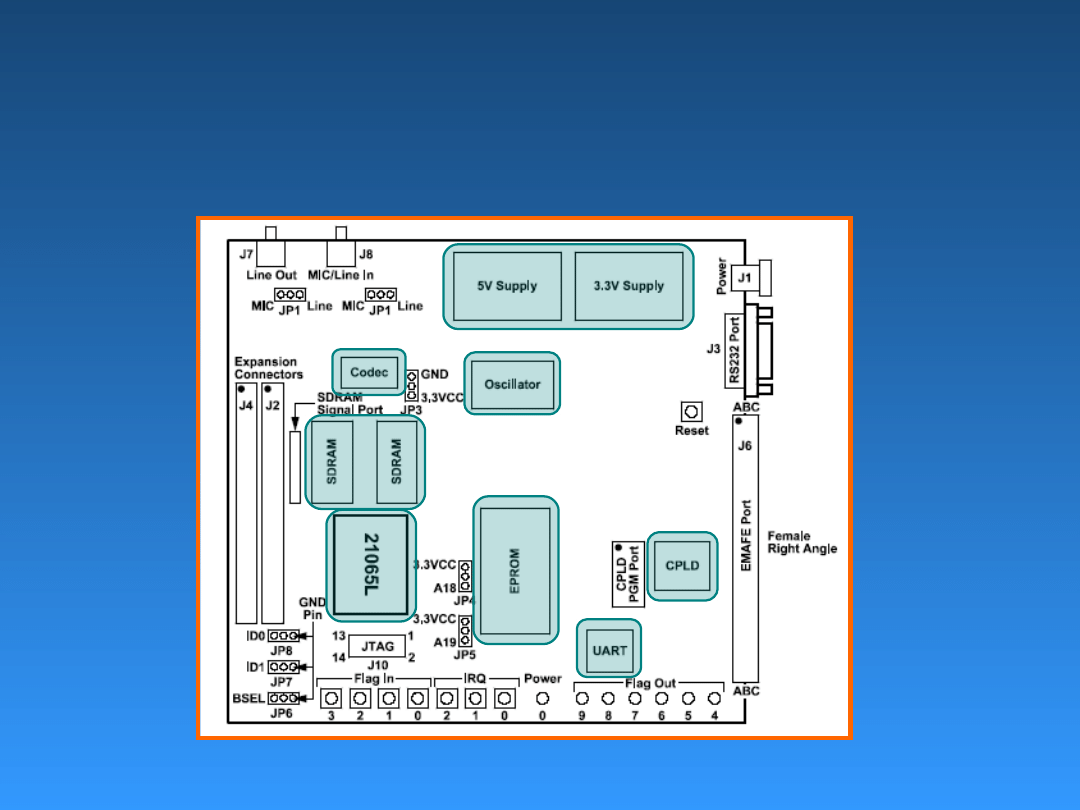

Opis płyty ADSP 21065L EZ-KIT

Lite

W płycie

ADSP 21065L EZ-KIT Lite

zaimplementowano

rozwiązania sprzętowe ułatwiające interaktywne

demonstracje. Użytkownik ma do dyspozycji przyciski

oraz programowalne diody LED. Za pomocą kodeka

AD1819A SoundPort® Kodek

jest możliwy dostęp do

wejścia audio (wybieranego za pomocą zwory jako

wejście line lub mikrofonowe) oraz wyjścia audio (wyjście

line). Na płycie EZ-KIT Lite znajduje się

nieulotna pamięć

,

w której zapisano

program monitora

. Program monitora

pozwala użytkownikowi wgrywać, wykonywać oraz

debugować programy. Zastępując pamięć EPROM na

płycie pamięcią EPROM zawierającą kod użytkownika

płyta EZ-KIT Lite staje się samodzielnym urządzeniem

działającym bez pomocy komputera klasy IBM PC.

Dostęp do procesora ADSP-21065L jest możliwy z

poziomu

komputera PC

, który jest połączony z płytą za

pomocą portu szeregowego lub opcjonalnie za pomocą

emulatora JTAG

.

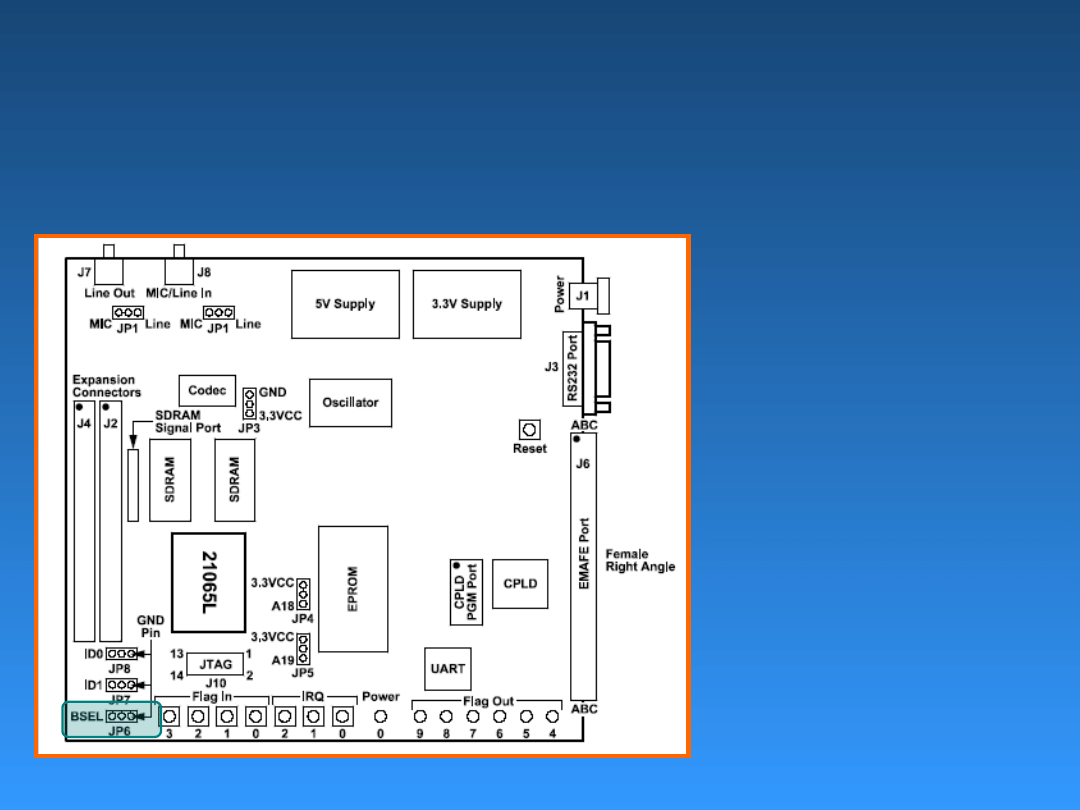

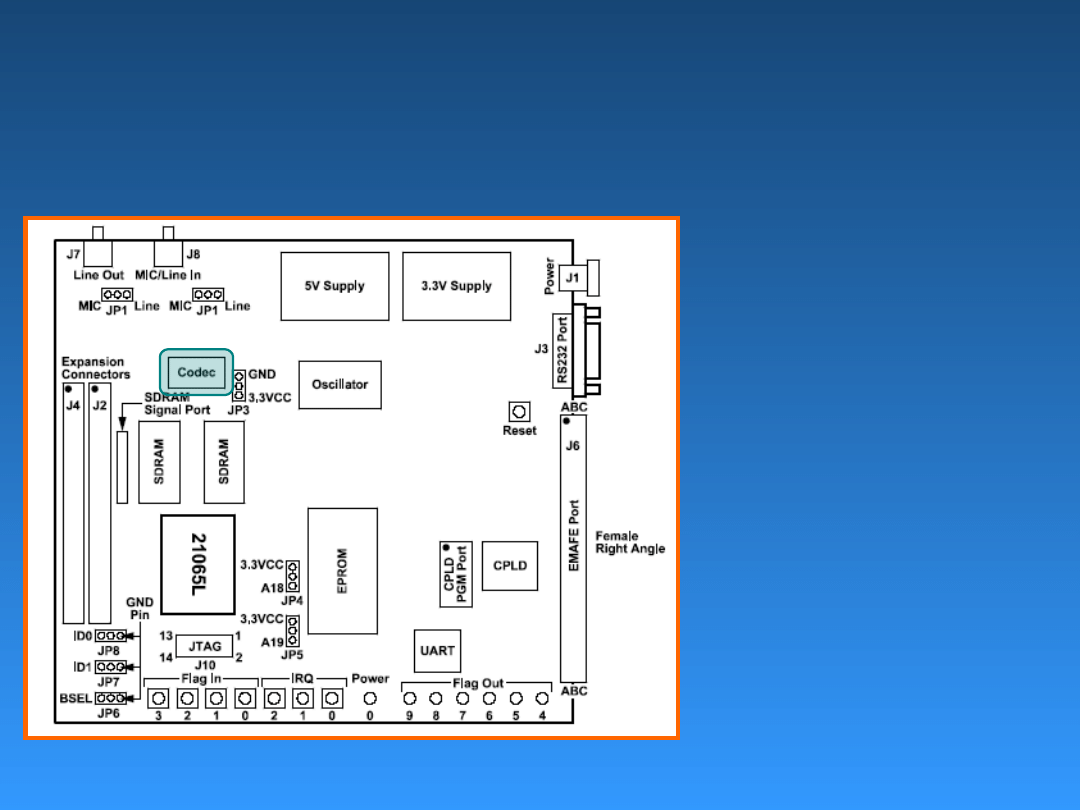

Schemat blokowy płyty

ADSP 21065L EZ-KIT Lite

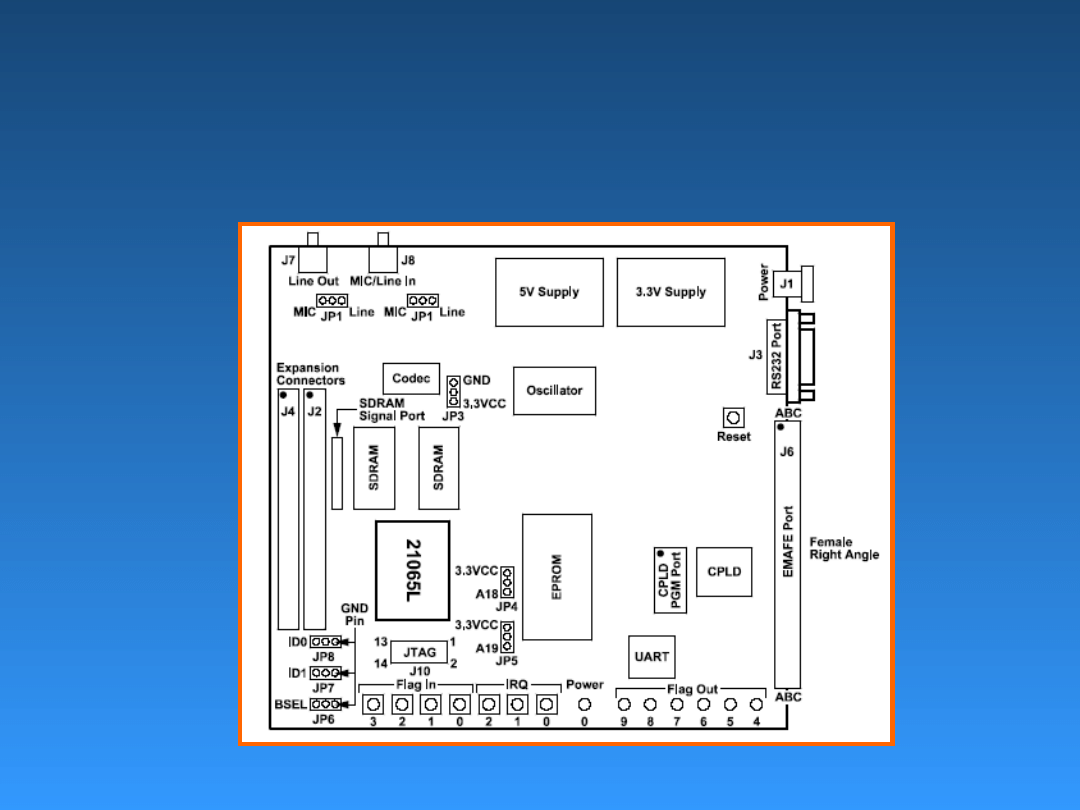

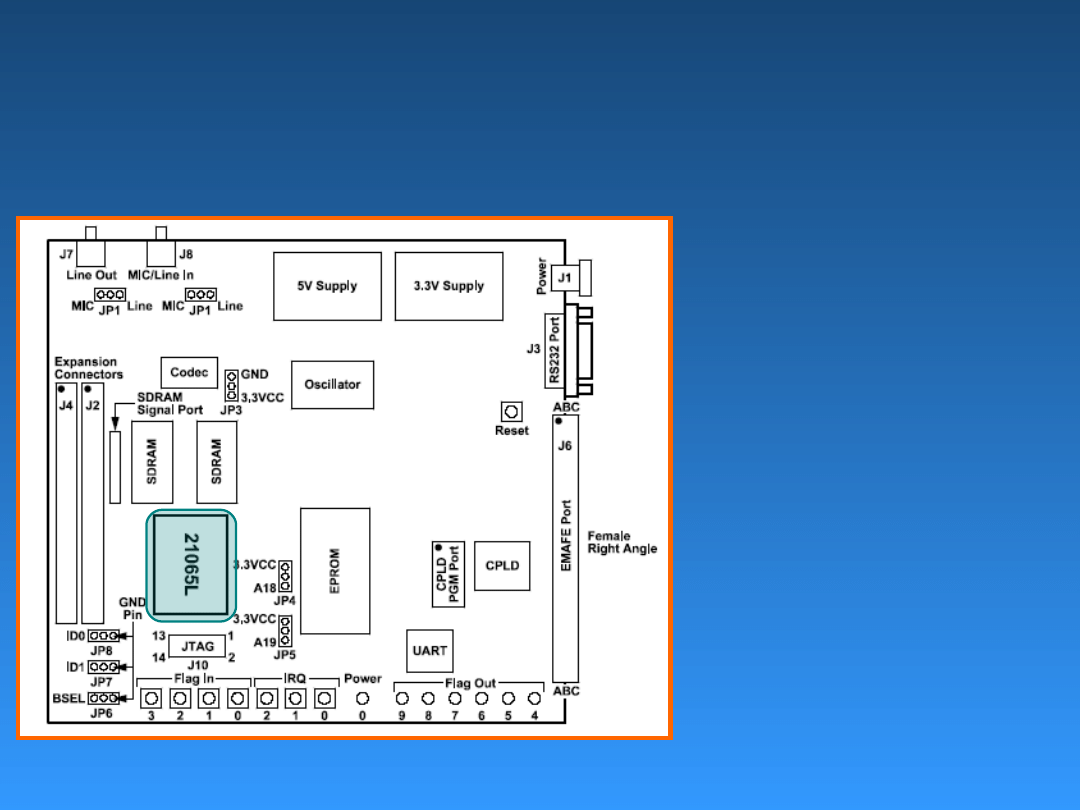

Layout płyty

ADSP 21065L EZ-KIT Lite

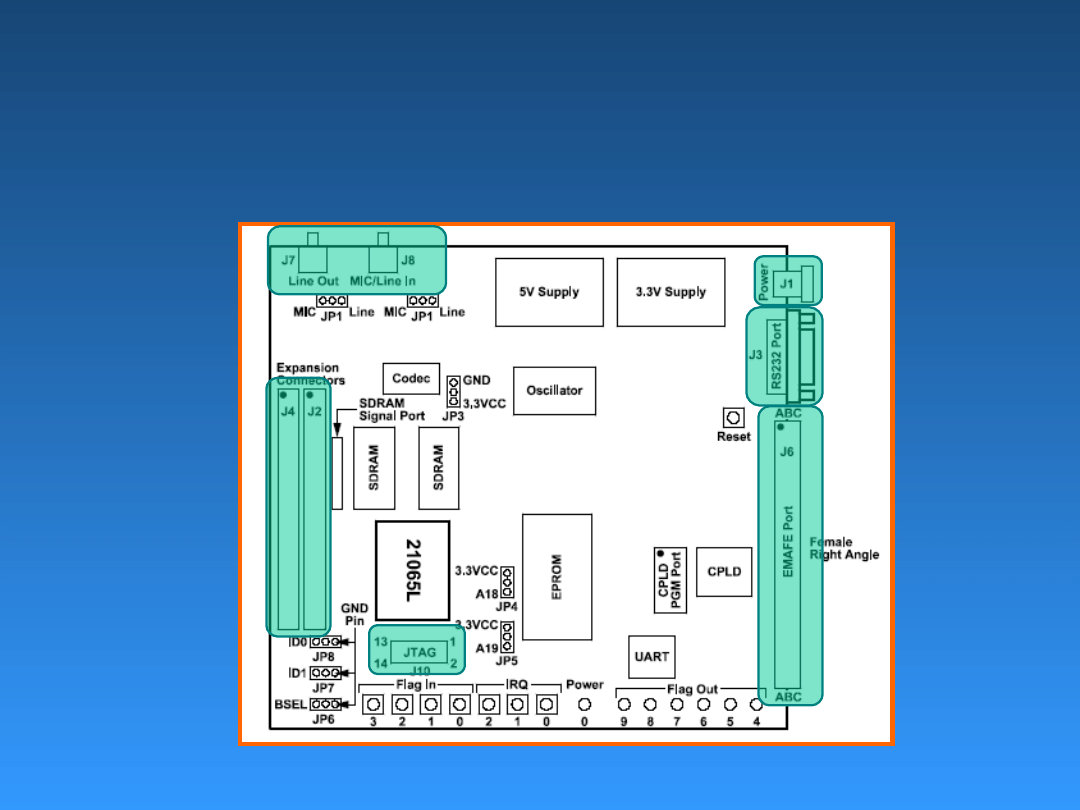

Wejścia/wyjścia na płycie

ADSP 21065L EZ-KIT Lite

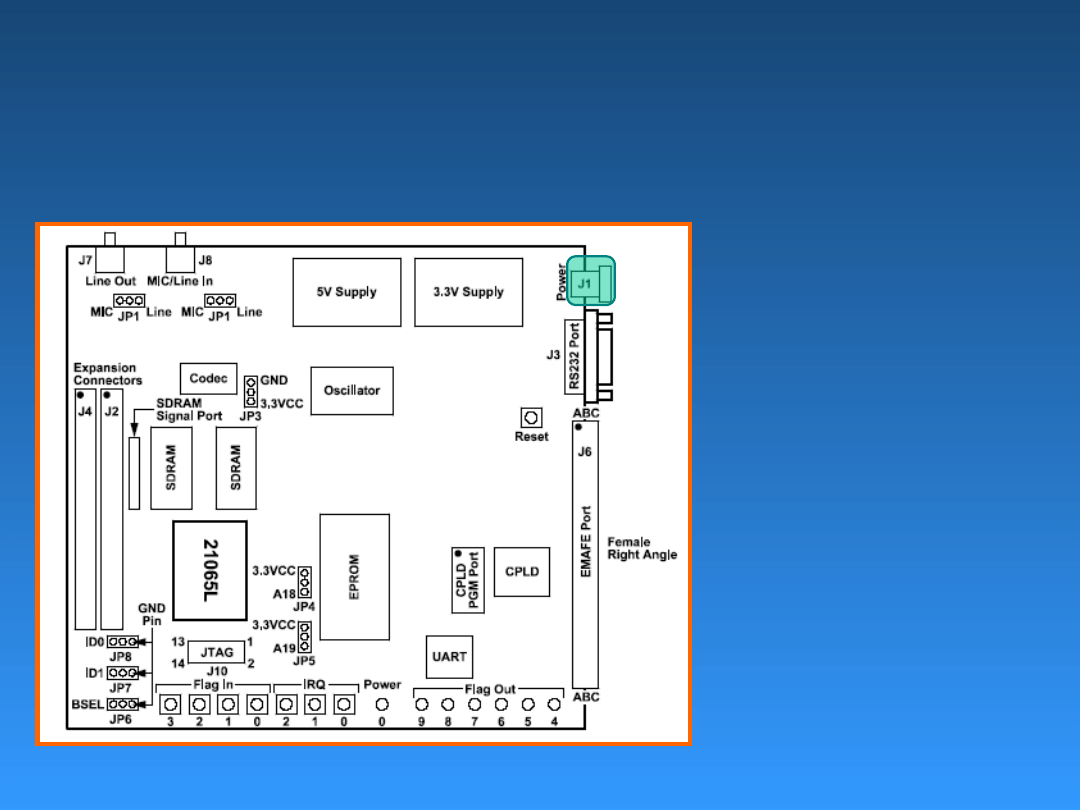

Wejście zasilania

ADSP 21065L EZ-KIT Lite

Podstawowym

gniazdem

zamontowanym na

płycie jest wejście

zasilacza. Według

rys. 2. złącze J1.

Zalecane

parametry

używanego

zasilacza są

następujące: 6,5 –

9,0 V 1,2 A. Przy

czym napięcie

doprowadzane jest

do pinu

centralnego, masa

znajduje się na

pierścieniu

okalającym

wejście.

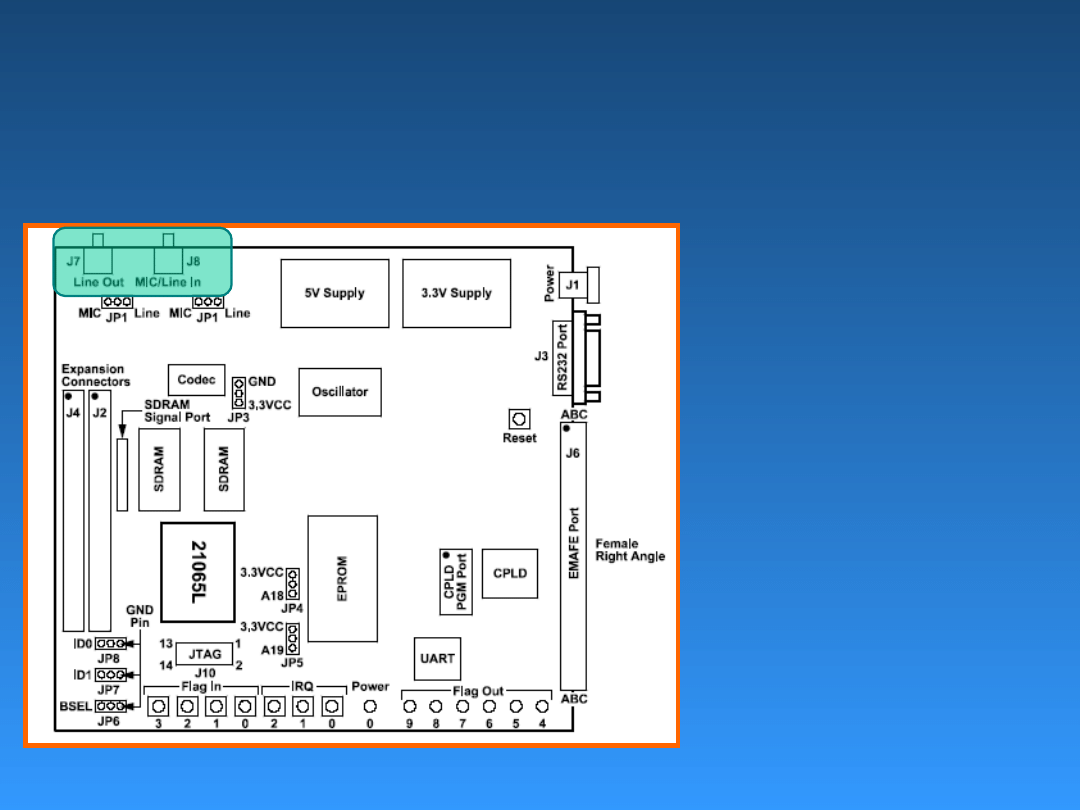

Wejścia/wyjścia audio

ADSP 21065L EZ-KIT Lite

Na płycie znajdują

się złącza stereo mini

jack stereo na rys 2 –

J7, J8. J7 – Line out

pozwala na dołączenie

do układu urządzeń

odbiorczych takich jak

słuchawki

stereofoniczne, daje to

możliwość na ciągłe

śledzenie efektów

przetwarzania lub

generowania dźwięku.

J8 – Mic/ Line in

pozwala na dołączenie

urządzeń typu

mikrofon, zewnętrzne

źródło dźwięku. W celu

korzystania z opisanych

wyprowadzeń

konieczne jest

odpowiedzenie

połączenie zworek

pomiędzy wyjściami, a

układem AD1819A.

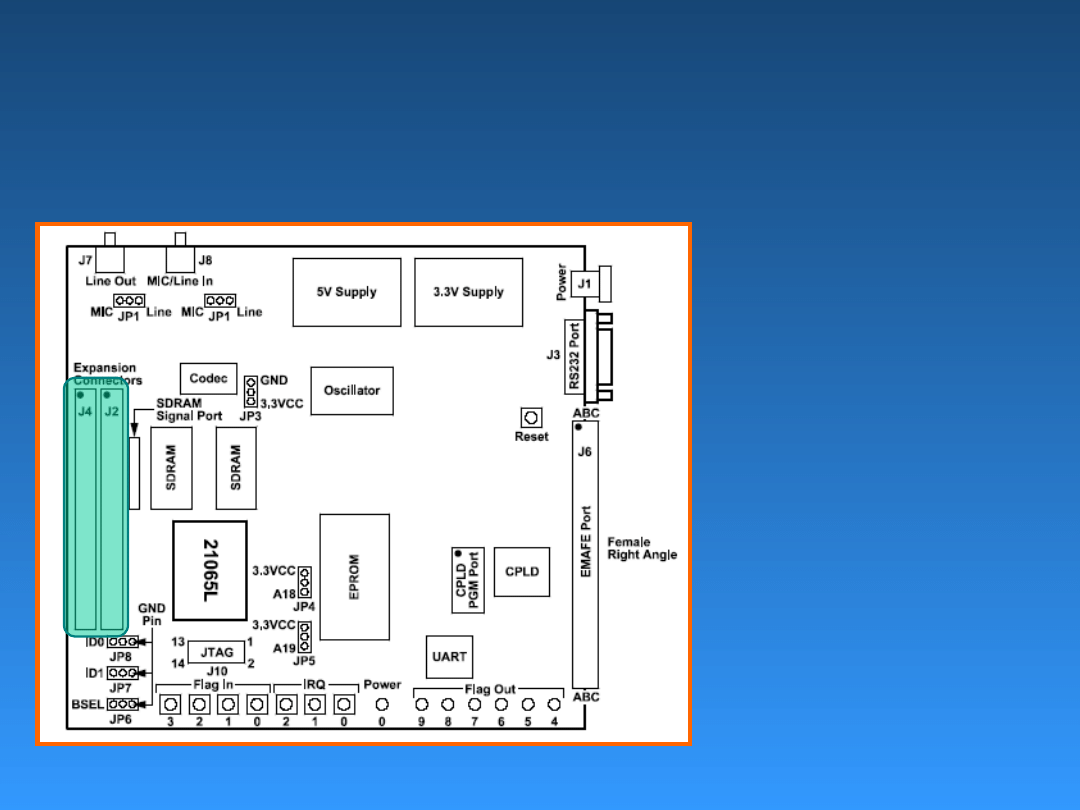

Porty rozszerzeń

ADSP 21065L EZ-KIT Lite

Złącza oznaczone J2

J4 to dwa

wyprowadzenia portów

rozszerzeń. Zapewniają

one dostęp do sygnałów

magistrali procesora.

Jedną z możliwości

korzystania z tych złącz

poza debugowaniem

jest kontrola hosta.

Wszystkie przerwania,

sygnały magistrali i

sygnały PWM są

dostępne za

pośrednictwem tego

portu. Obciążanie

portów zewnętrznych

może wpłynąć na

szybkość magistrali oraz

wydajność procesora.

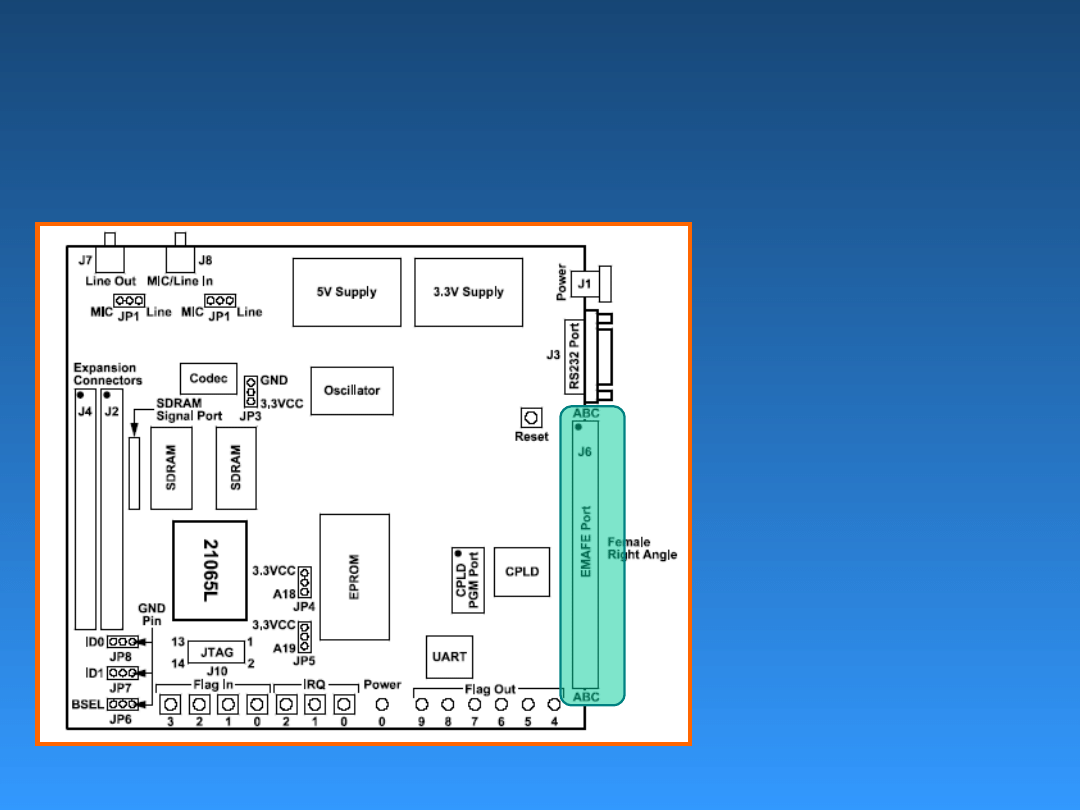

Złącze EMAFE

ADSP 21065L EZ-KIT Lite

Złącze EMAFE -

Enhanced Modular

Analog Front End

dostarcza

standardowego

interfejsu do

podłączenia urządzeń z

wejściami/wyjściami

analogowymi. Złącze

jest oznaczone jako J6,

posiada 96 pinów

ułożonych w trzech

rzędach po 32 piny.

Interfejs obsługuje:

16 linii danych

8 linii adresowych

3 linie sterujące

magistralą równoległą

16 synchronicznych

portów szeregowych

1 wyjście przerwań

1 wejście flagi

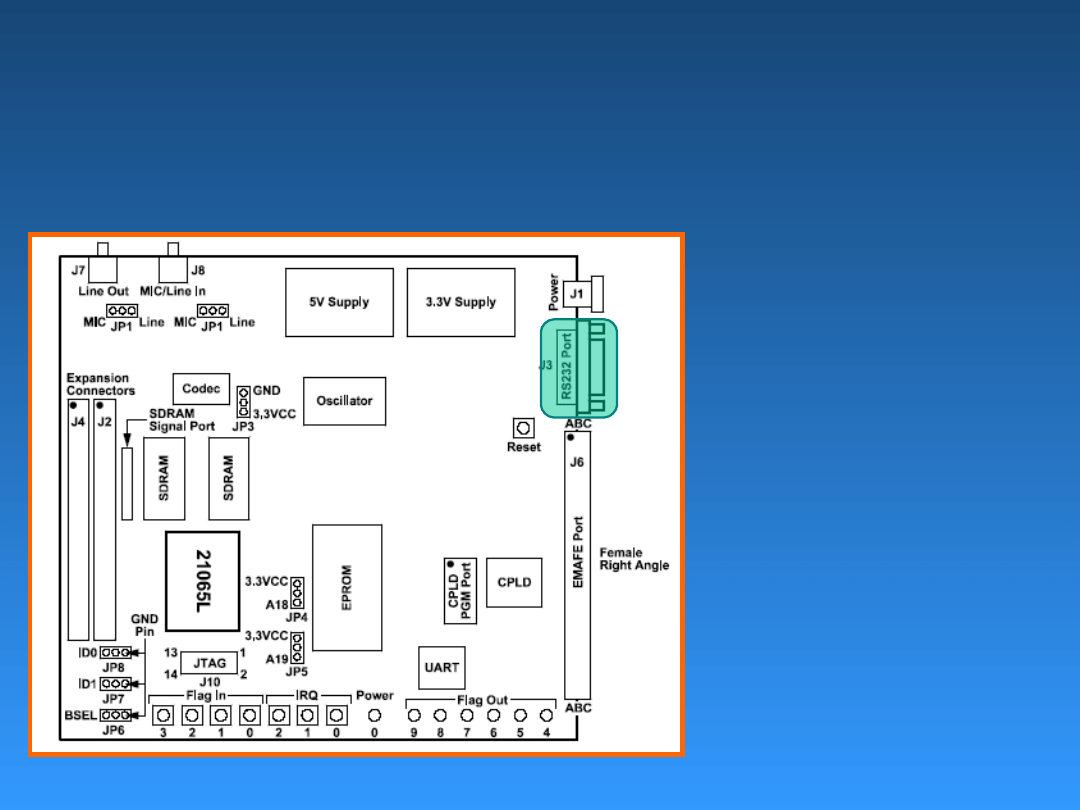

Port RS232

ADSP 21065L EZ-KIT Lite

Złącze J3 to

wyprowadzenie

interfejsu UART

służącego do

komunikacji z

zewnętrznymi

urządzeniami w

standardzie RS 232.

Za pomocą tego

portu jest podłączony

min. komputer

nadrzędny, klasy IBM PC.

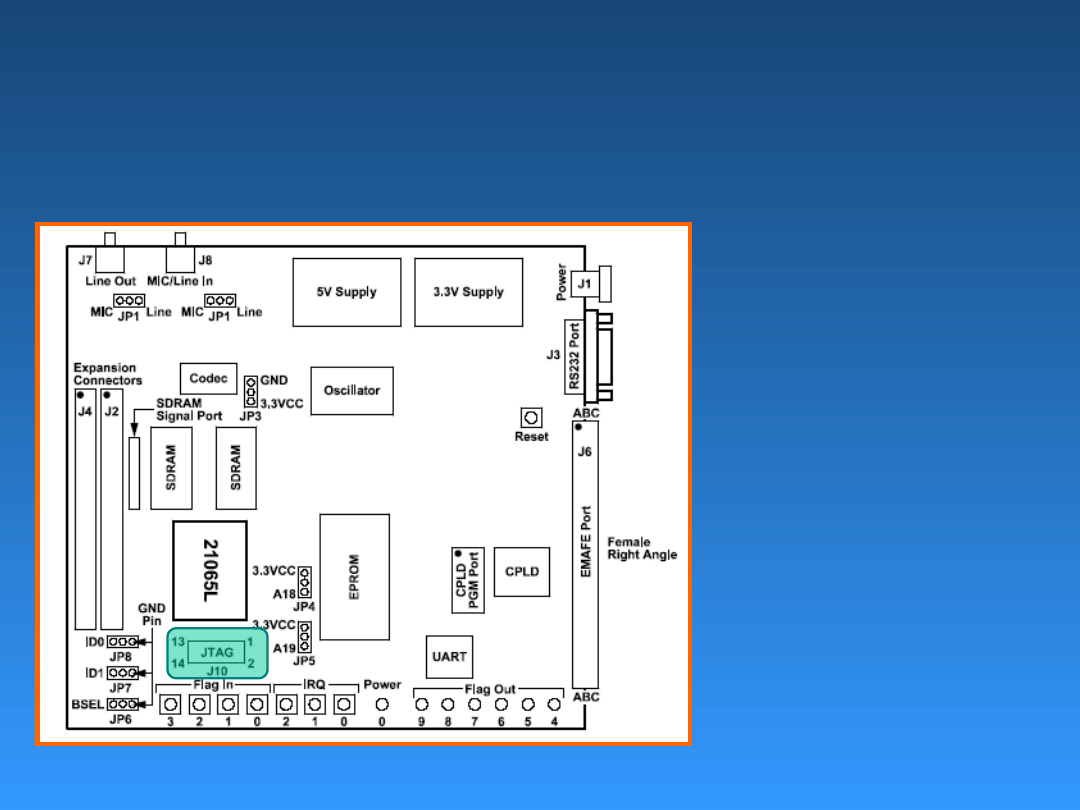

Złącze JTAG

ADSP 21065L EZ-KIT Lite

Złącze J10 jest

wyprowadzeniem

portu emulatora. Służy

do uruchamiania i

programowania

procesora. Jednym z

najważniejszych

założeń standardu

JTAG jest możliwość

programowania

układu w gotowym

urządzeniu, bez

konieczności

odłączania. W celu

zapewnienia

odpowiedniego

zasilania przy

odłączonym złączu

należy w odpowiedni

sposób zewrzeć

wybrane piny za

pomocą zworek.

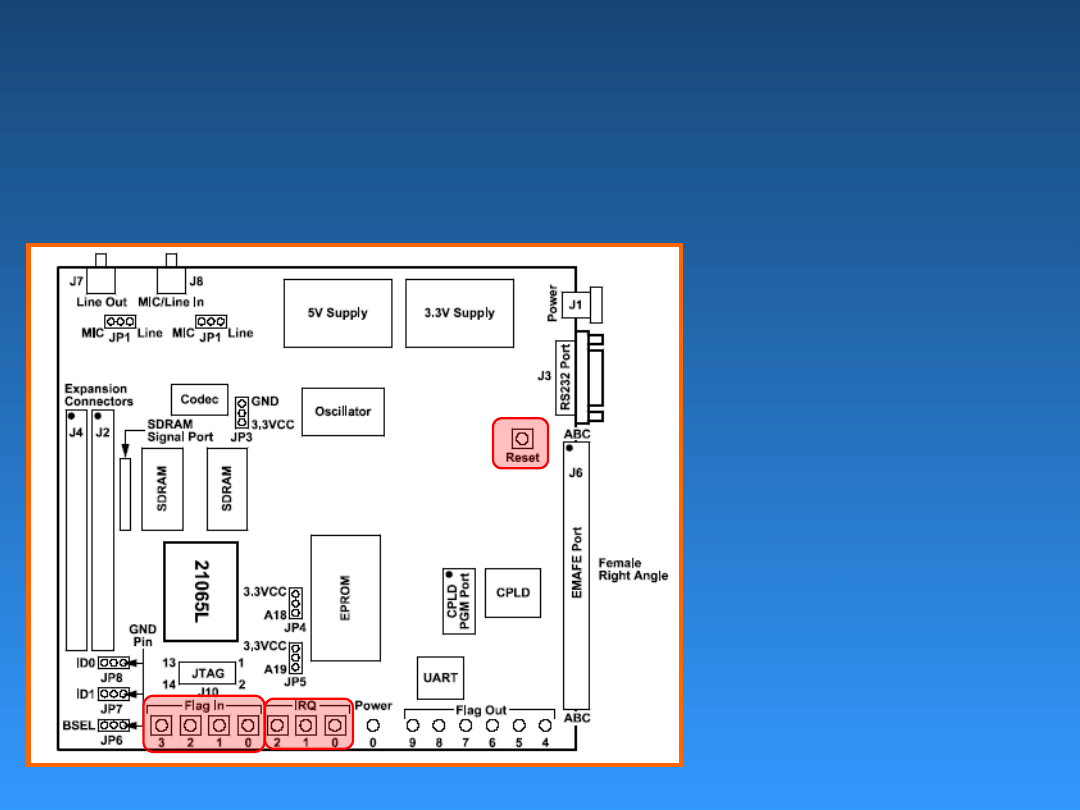

Rola przycisków

ADSP 21065L EZ-KIT Lite

Na płycie ewaluacyjnej

zamontowano osiem

przycisków push-button

typu mikro switch.

- Przycisk

RESET

pozwala

zainicjować układ DSP.

Przycisk pomocny jest w

przypadku utraty

komunikacji pomiędzy EZ-

KIT Lite, a komputerem, z

którego uruchamiane są

programy. W celu

nawiązania powtórnej

komunikacji należy wcisnąć

przycisk RESET.

- Przyciski

FLAG 0-3

pozwalają zmienić status

czterech flag na pinach

procesora DSP.

- Przyciski

IRQ 0-2

umożliwiają wysyłanie

zewnętrznego przerwania

do procesora. IRQ0 jest

wspólne z interfejsem

UART, IRQ1 jest wspólne ze

złączem EMAFE.

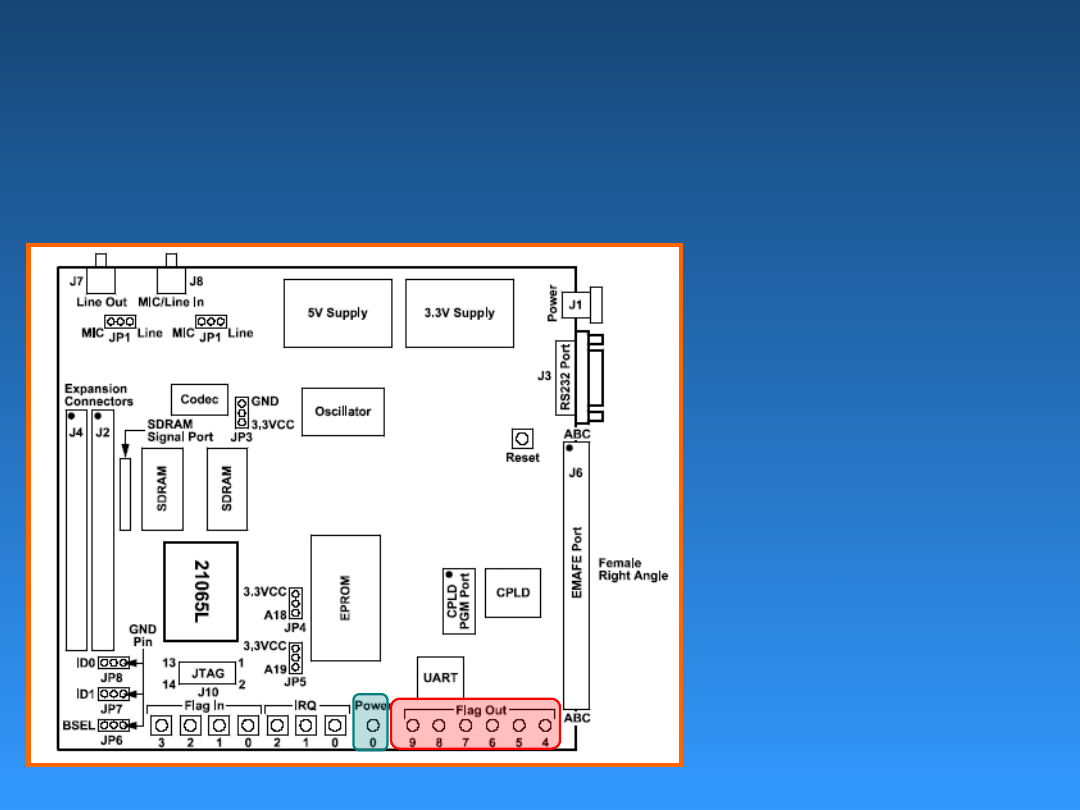

Diody sygnalizacyjne

ADSP 21065L EZ-KIT Lite

Na płycie znajduje

się sześć diod

LED, które są

sterowane przez

wyjścia procesora

DSP. Są one

oznakowane

zgodnie z

wyjściami flag,

które je

kontrolują.

Ponadto na płycie

zamontowana jest

dioda zasilania

sygnalizująca

podłączenie

zasilacza.

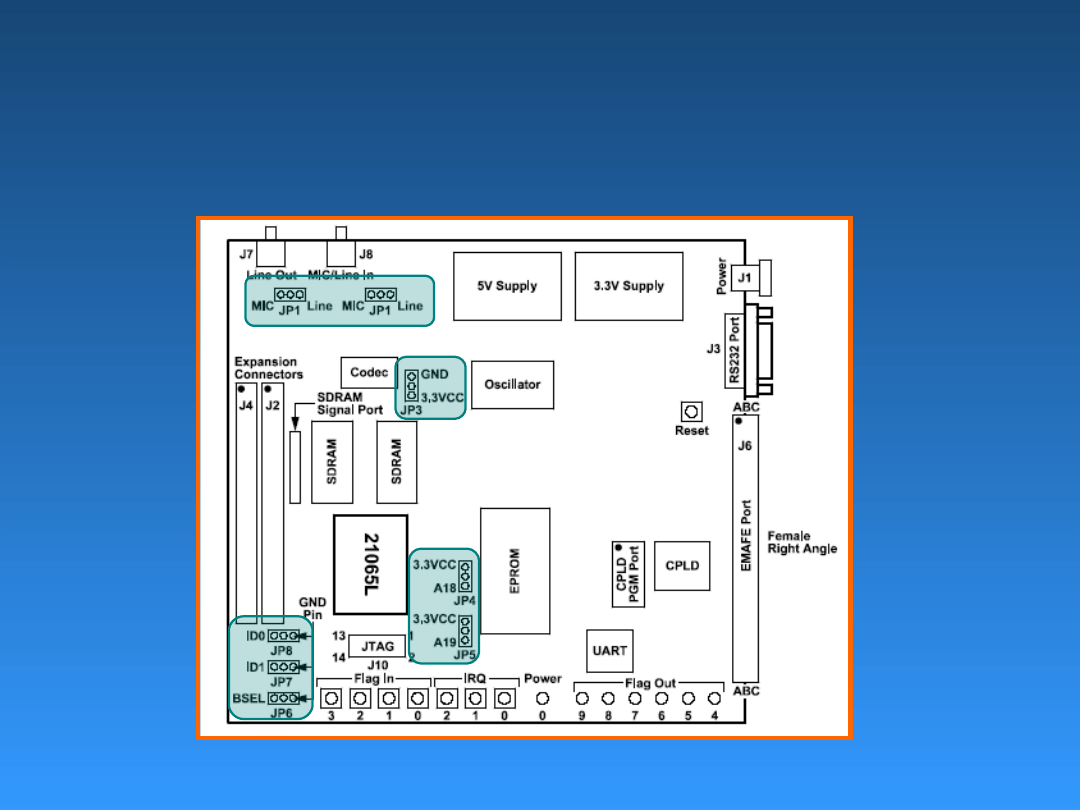

Zwory

ADSP 21065L EZ-KIT Lite

Wybór trybu rozruchu

ADSP 21065L EZ-KIT Lite

Zworka JP6 kontroluje

zachowanie procesora

ADSP, gdy system jest

resetowany

( w wyniku

podłączenia zasilania

lub przyciskiem

RESET).

Kiedy zworka nie jest

podłączona do GND

system ładowany jest

z pamięci EPROM. Jeśli

zworka jest

podłączona do GND,

procesor usiłuje się

uruchomić poprzez

interfejs hosta

(expansion port).

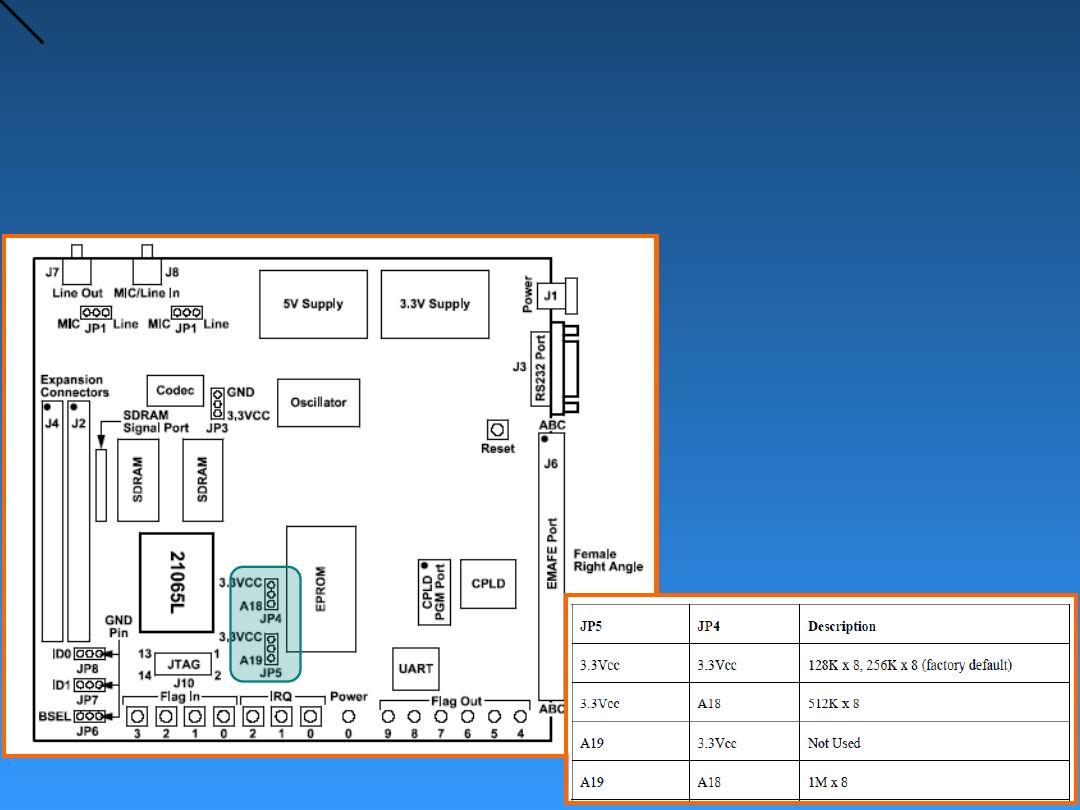

Wybór rozmiaru pamięci

EPROM

ADSP 21065L EZ-KIT Lite

EZ-KIT Lite obsługuje

pamięci: 128K x 8, 256K x

8, 512K x 8, oraz 1M x 8,

poszczególne z nich

wybierane są poprzez

zwory, JP4 i JP5.

Fabrycznie na płytce jest

montowana pamięć

EPROM 256K x 8, jeżeli

zostanie zastosowana

inna pamięć zwory

powinny zostać

ustawione według

poniższej tabeli:

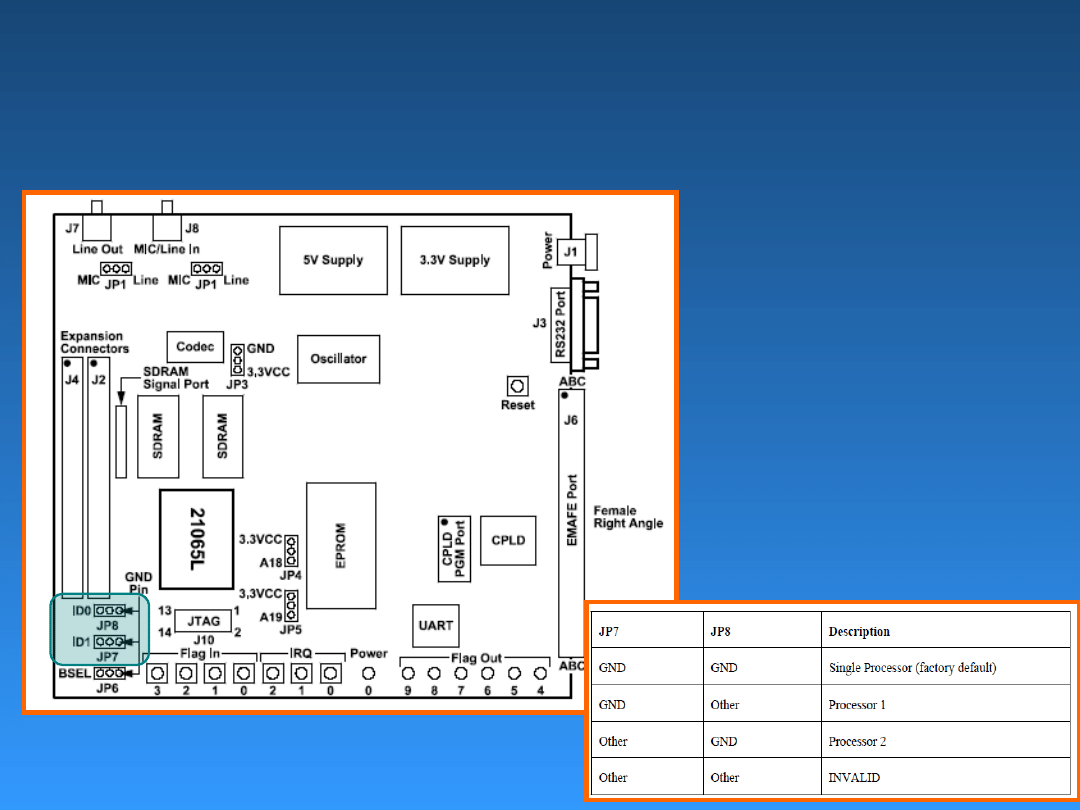

Wybór ID Procesora

ADSP 21065L EZ-KIT Lite

Podczas typowej pracy na

pokładzie EZ-KIT Lite

znajduje się tylko jeden

procesor. W takim

przypadku należy

sprawdzić ustawienie

zworek JP7 i JP8 dla

zapewnienia poprawności

działania systemu jedno

procesorowego. W

przypadku dołączenia do

układu dodatkowego

procesora poprzez złącze

rozszerzeń zworki

powinny być połączone

według poniższej tabeli:

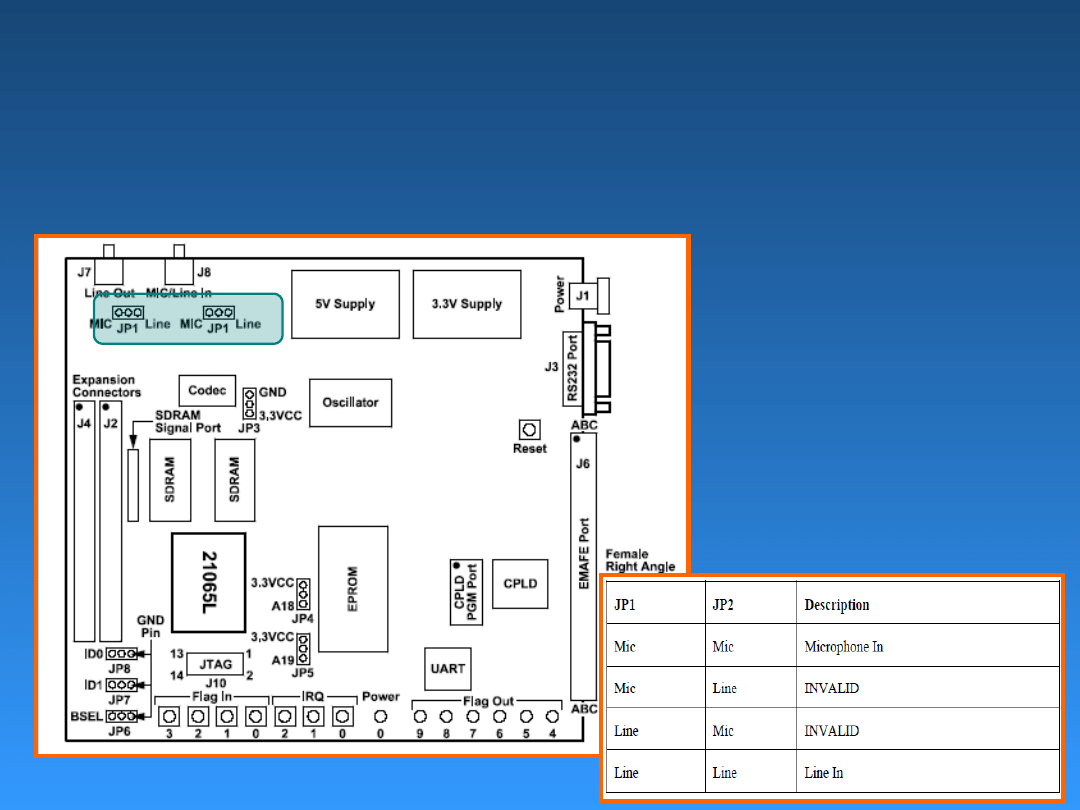

Wybór funkcji wejścia

Mic/Line in

ADSP 21065L EZ-KIT Lite

Użyte złącze jack jest

wykorzystywane do

podłączenia

zewnętrznych źródeł

dźwięku oraz

mikrofonu. Aby wybrać

czy wejście ma

pracować jako wejście

mikrofonowe, czy też

jako wejście Line

należy ustawić zworki

JP1 i JP2 zgodnie z

poniższą tabelą:

Wybór kodeka AD1819

ADSP 21065L EZ-KIT Lite

Magistrala płytki

dzielona jest pomiędzy

zastosowany kodek a

interfejs EMAFE.

Zworka JP3 wyłącza

dostęp kodeka do

magistrali co

zapobiega błędom w

transmisji pomiędzy

dwoma urządzeniami.

Jeżeli EMAFE nie jest

używane zworę JP3

należy dołączyć do

GND w celu

umożliwienia pracy

układowi AD1819

Najważniejsze podukłady

ADSP 21065L EZ-KIT Lite

Procesor

ADSP 21065L EZ-KIT Lite

Procesor ADSP

21065L jest

zmiennoprzecinkowy

m 32-bitowym

procesorem

I generacji do

wydajnych

i niskobudżetowych

zastosowań w

cyfrowym

przetwarzaniu

sygnałów.

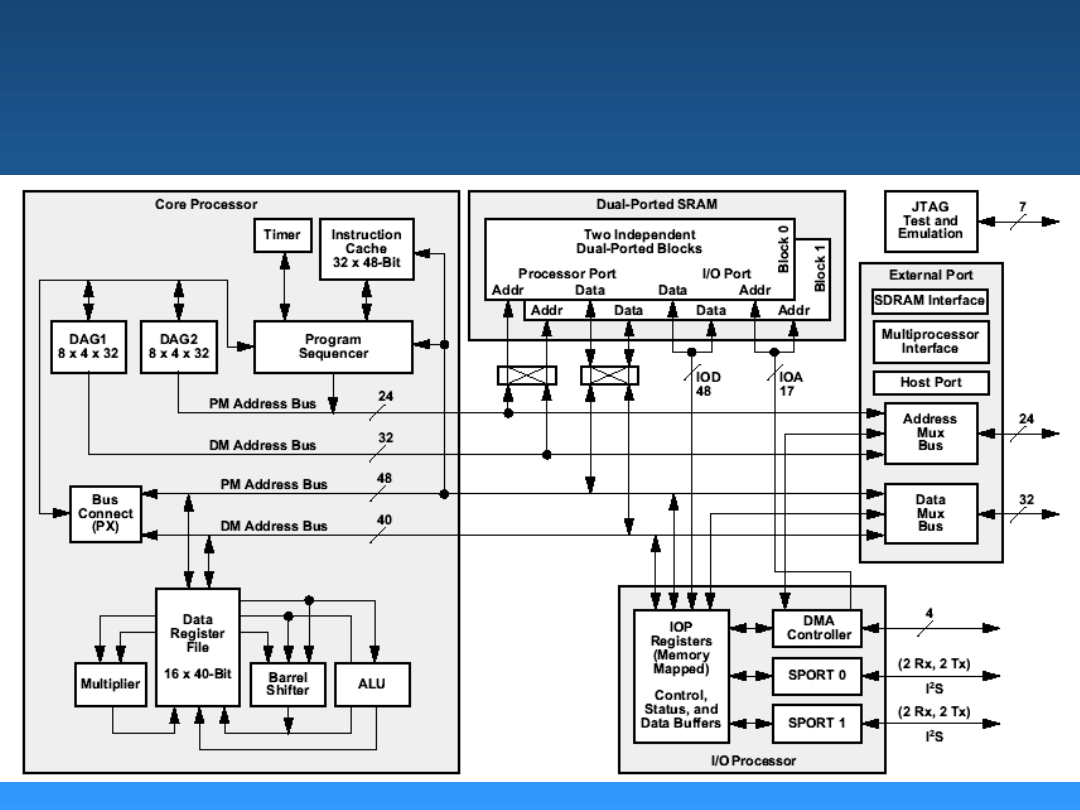

Schemat blokowy procesora

ADSP 21065L

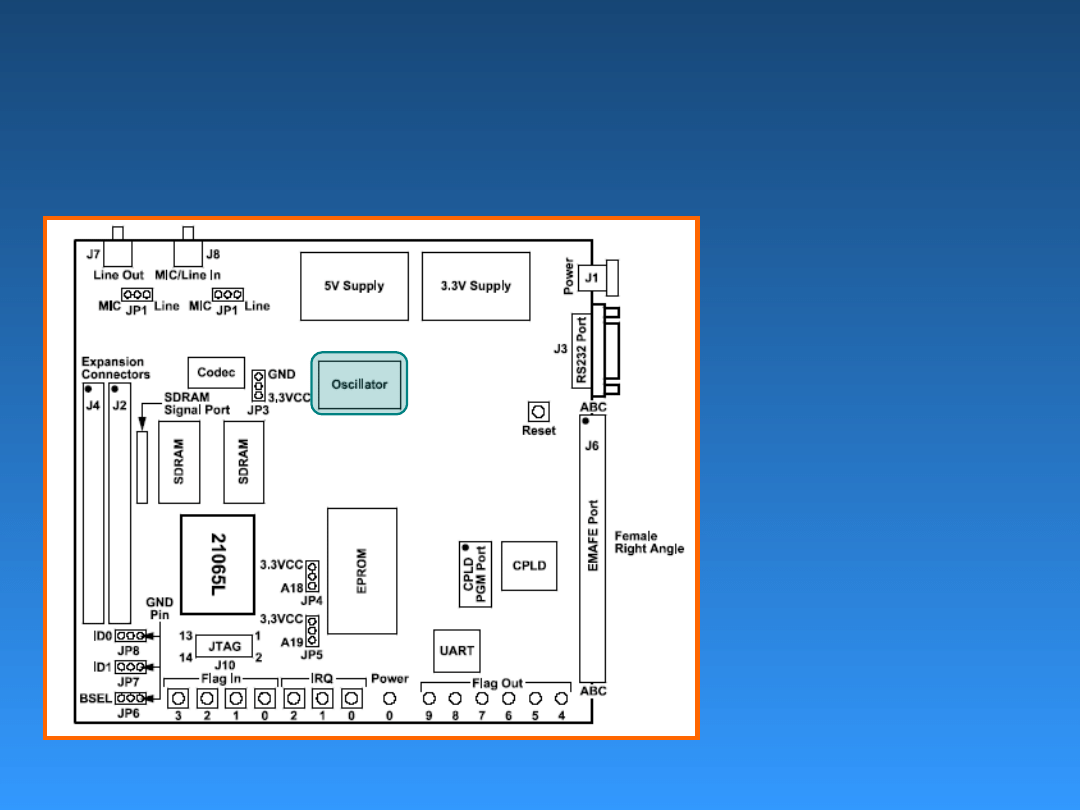

Oscylator

ADSP 21065L EZ-KIT Lite

Zastosowany

oscylator

taktuje

procesor z

częstotliwością

30 MHz.

Wewnątrz

procesora

częstotliwość

ta jest

podwajana,

dzięki temu

procesor jest

taktowany

wewnętrznie z

częstotliwością

60 MHz.

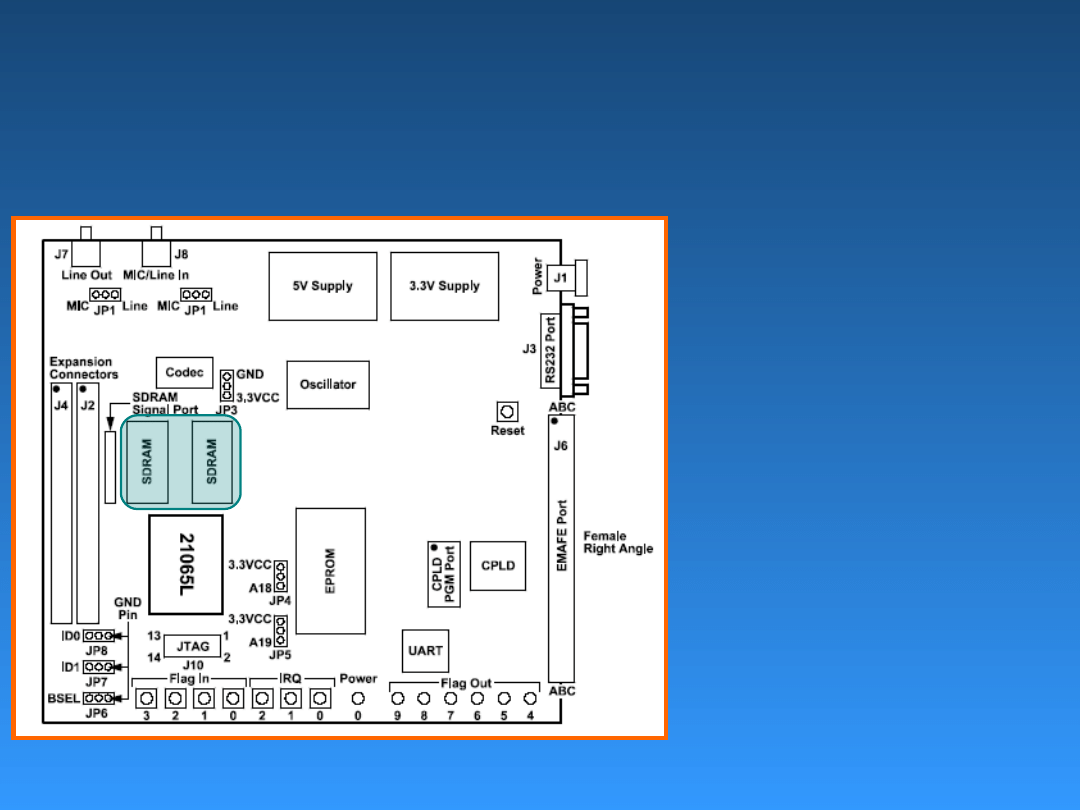

Pamięć SDRAM

ADSP 21065L EZ-KIT Lite

2 bloki pamięci SDRAM

(Synchroniczna

dynamiczna pamięć

dostępu swobodne-go) o

wielkości 1Mb x 16 bit

są połączone z linią MS3

procesora. ADSP-21065L

używa linii adresowej 13

do wyboru banku.

Dodatkowo ADSP ma

rozłączoną linię

adresową służącą do

od-świeżania pamięci

SDRAM. Magistrala

umożliwia przesył

danych do i z pamięci z

prędkością 2xCLKIN, co

daje prędkość do 240

MB/s. Wszy-stkie wejścia

są próbkowane zegarem

SDCLK. Natomiast

wyjścia można

odczytywać na

narastającym zboczu

impulsów zegara SDCLK.

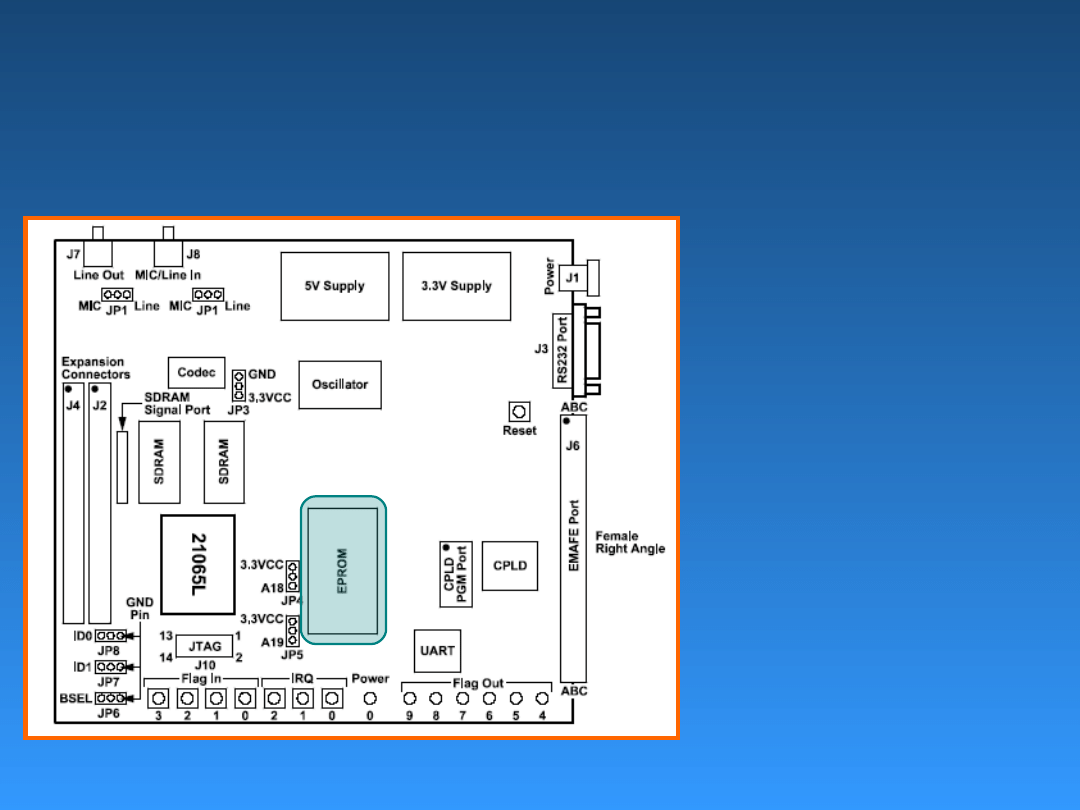

Pamięć EPROM

ADSP 21065L EZ-KIT Lite

PAMIEĆ EPROM

(kasowalna

półprzewodnikowa

pamięć stała) o

wielkości do 1Mb x 8 bit

przechowuje programy,

które mogą być

wykorzystane przez

ADSP-21065L. Operacja

wyboru źródła

restartowania

kontrolowana jest przez

wyprowadzenia BMS

(Boot Memory Select) i

BSEL (Boot EPROM).

Pierwsze 256 instrukcji

(1536 bajtów) jest

automatycznie

ładowane przez ADSP-

21065L po kasowaniu.

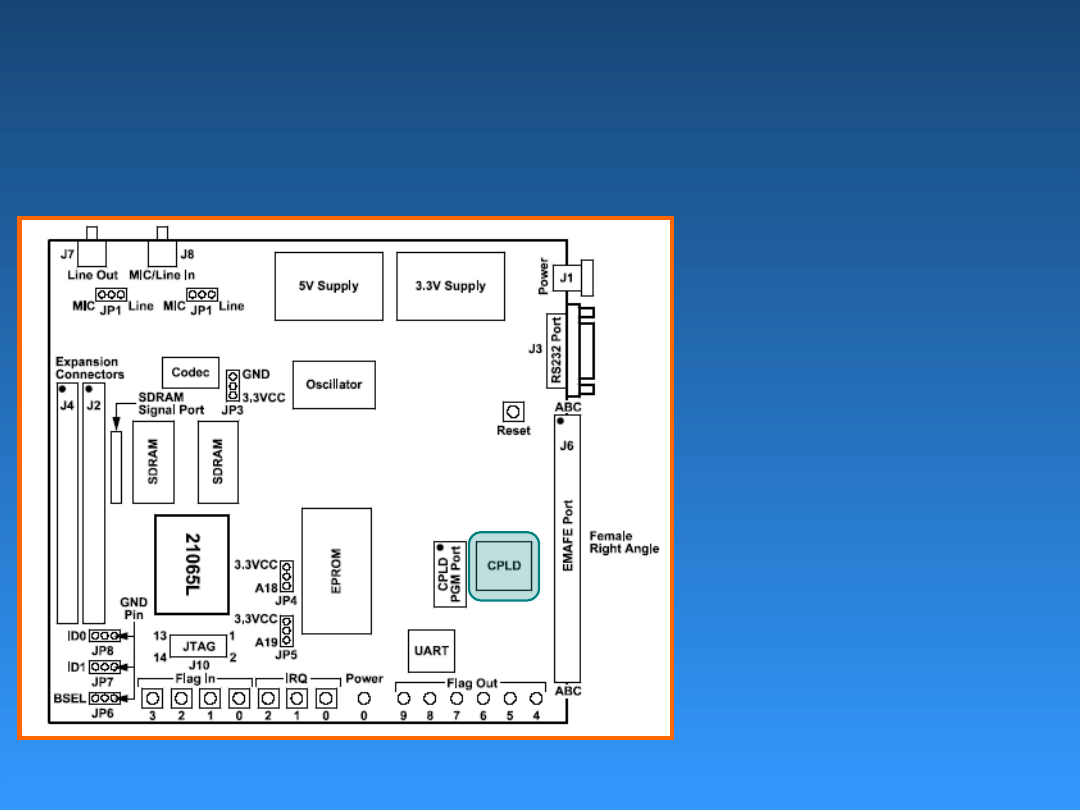

Układ CPLD

ADSP 21065L EZ-KIT Lite

Programowalny

układ CPLD realizuje

indeksowane

adresowanie

wymagane przez

interfejs EMAFE.

Układ

programowalny

kontroluje

ustawianie adresu,

a także kierunek

przesyłania danych

po magistrali.

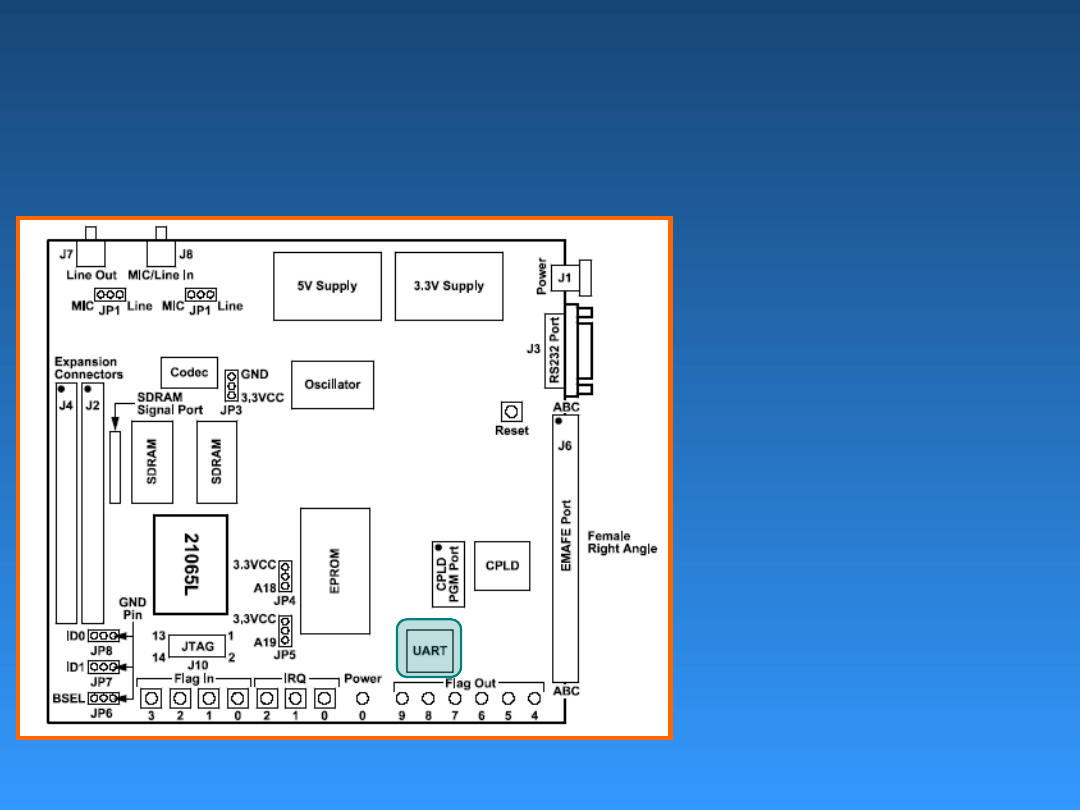

Układ UART

ADSP 21065L EZ-KIT Lite

UART jest układem

używanym do

asynchronicznego

przesyłania danych

z magistrali danych

i adresowej

procesora poprzez

znajdujący się na

płycie port

szeregowy RS232.

UART zawiera

również bufor do

tymczasowego

gromadzenia

danych w przypadku

szybkiej transmisji.

Kodek AD1819

ADSP 21065L EZ-KIT Lite

Kodek zawiera

dwukanałowy

przetwornik Σ∆ AC i

parę dwukanało-wych

przetworników ∑∆ CA.

Wejścia przetwornika

AC mogą zostać

wybrane z czterech par

dwukanałowych

sygnałów

analogowych: LINE1,

LINE2, pomocnicze

("aux”) LINE#1 i

wyjście DAC z

mieszacza.

Kontrolowane

programowo

wzmocnienie pozwala

na niezależne

wzmocnienie dla

każdego kanału

wchodzącego do

przetwornika AC.

Kodek AD1819

ADSP 21065L EZ-KIT Lite

Parametry AD1819

- jednoukładowy zintegrowany 16-bitowy kodek

audio stereo Σ/∆*,

- programowane wzmocnienie i tłumienie,

- wejścia i wyjścia stereo ,

- analogowe i cyfrowe mieszanie sygnałów,

- filtry sygnałowe zintegrowane w układzie

scalonym: cyfrowa interpolacja i decymacja;

filtracja dolnoprzepustowa wyjść analogowych,

- Cyfrowa zmiana częstotliwość próbkowania od

7 kHz do 48 kHz,

- szeregowy cyfrowy interfejs kompatybilny z

rodziną

ADSP-21XX/21XXX,

- zasilanie 5V ( Imax = 140mA).

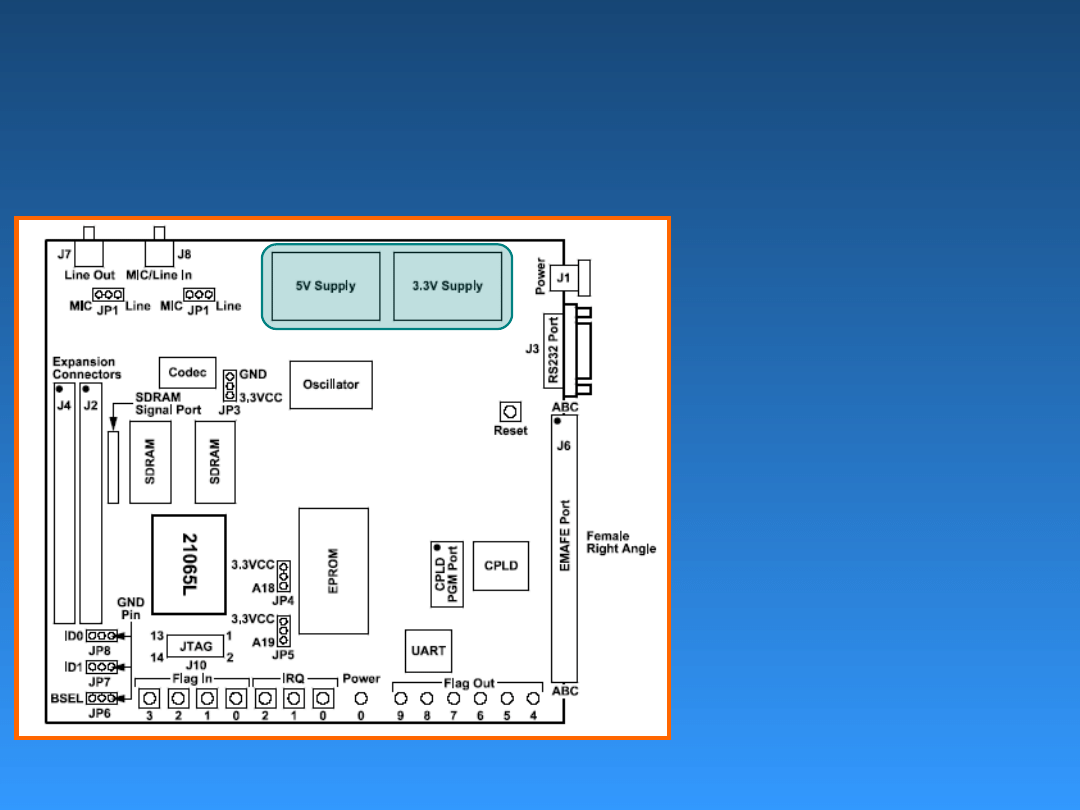

Układy zasilania

ADSP 21065L EZ-KIT Lite

Większość

układów na płycie

wymaga napięcia

zasilania 3,3V, za

wyjątkiem

Kodeka 1819 oraz

układu UART,

które wymagają

napięcia 5V.

Zatem na płycie

są umieszczone

dwa niezależne

źródła zasilania

dające napięcia

5V oraz 3,3V.

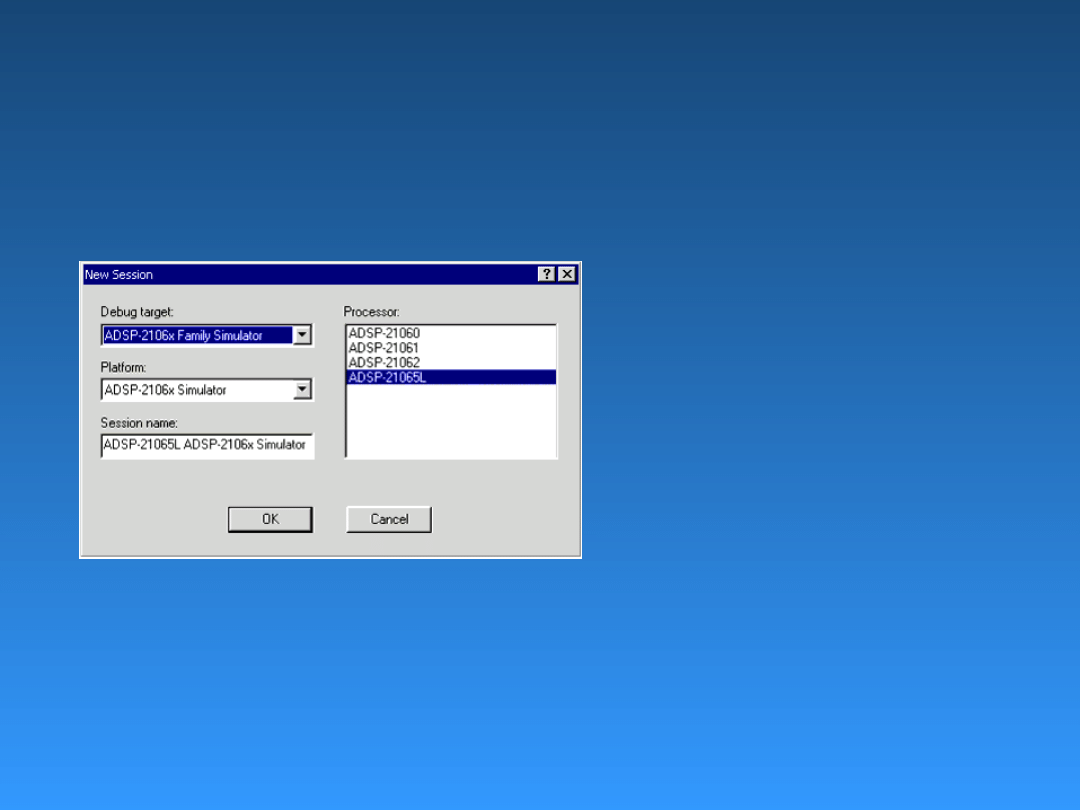

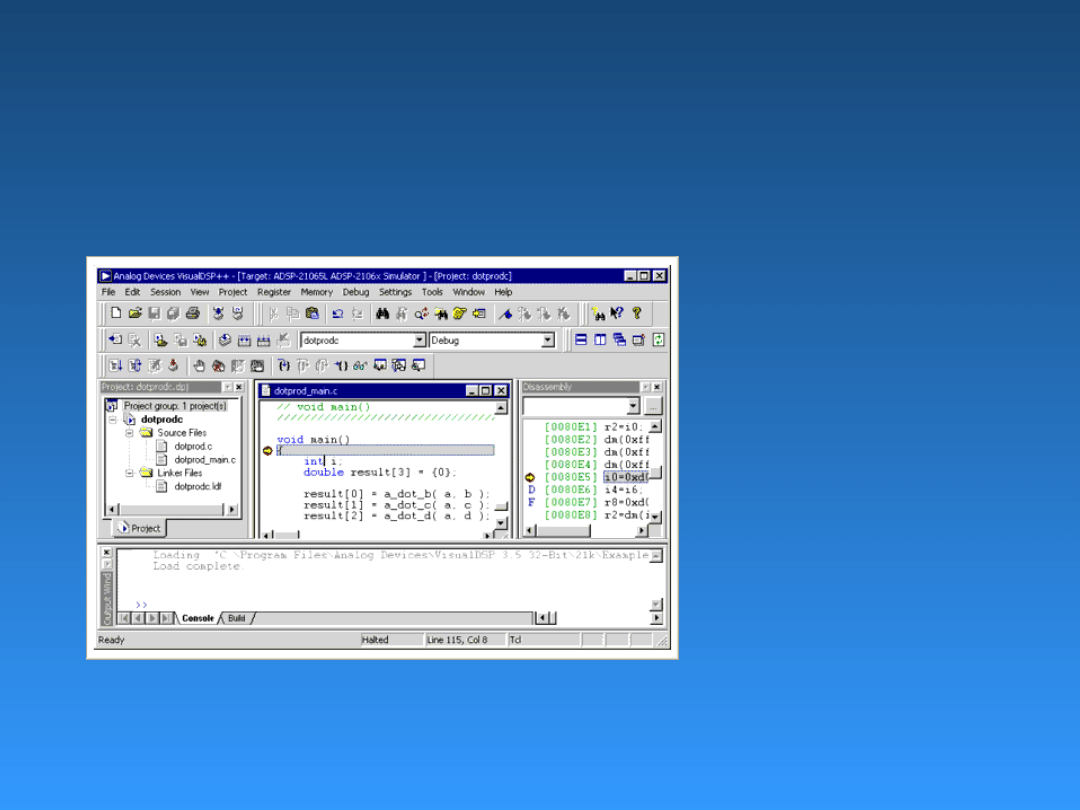

Visual DSP++

Uruchamianie nowej sesji

Okno New Session

pojawia się w

momencie

pierwszego

uruchomienia

programu

Visual DSP++

Środowisko

uruchomieniowe

Środowisko

uruchomieniow

e Visual DSP++

pozwala na

edycję,

kompilację i

uruchamianie

programów na

płycie ADSP

21065L.

Przykłady programów

Program demonstracyjny

„Blink”

Program ten steruje dwoma diodami LED

podłączonymi do flag (6 i 7). Diody te są

zapalane naprzemiennie. W celu uzyskania

ciągłego świecenia diod użyto timera oraz

przerwania generowanego w wyniku

osiągnięcia przez rejestr TCOUNT wartości

umieszczonej w rejestrze TPERIOD.

Procedura obsługująca przerwanie

naprzemiennie ustawia lub zeruje flagi

wyjściowe 6 i 7 w zależności od stanu

poprzedniego. Wyzerowanie flagi powoduje

zapalenie się diody, natomiast ich ustawienie

powoduje wyłączenie. W programie szybkość

migania diód uzyskuje się poprzez zmianę:

define flash_PERIOD 0x0300000 na

0x0900000.

Program „Blink” - kod

#include <def21065l.h>

// dołączenie plików do programu

#include <21065l.h>

#include <signal.h>

#include <macros.h>

------------------------------------------------------------

DEFNICJE MAKR I STAŁYCH

------------------------------------------------------------

#define FLASH_PERIOD 0x5300000

// określenie tempa cyklów

// migania diod

#define SetIOP(addr, val) (*(int*)addr) = (val)

//

definicja

#define GetIOP(addr) (*(int*)addr)

// makr

------------------------------------------------------------

-

DECLARACJE ZMIENNYCH GLOBALNYCH

------------------------------------------------------------

int odd_or_even_flag;

// deklaracja zmiennej flagi

(parzysta,

// nieparzysta)

Program „Blink” - kod

// PROTOTYPY FUNKCJI

//------------------------------------------------------------

void timer_int(int);

void set_timer(int);

void init_timer(void);

void timer_int(int);

//************************************************************

// Definicja funkcji init_timer(): ustawienie priorytetu

// timer a 0 na niski, zapisanie w wektorze przerwań,

// zdjęcie maski i wystartowanie timera.

//************************************************************

void init_timer(void)

// deklaracja funkcji inicjującej timer

{ asm("#include <def21065l.h>");

//dołączenie

pliku<def21065l.h>

asm("bit clr mode2 TIMEN1 | TIMEN0;");

//zatrzymanie timera 1

// i timera 0

interrupt(SIG_TMZ, timer_int);

// wskazanie na podprogram

// obsługi przerwania

asm("bit clr mode2 TIMEN0;

//zatrzymanie timera 0

bit set imask TMZLI;

bit clr mode2 INT_HI0 | INT_HI1;

bit set mode2 PWMOUT0 | TIMEN0;");

//ustawienie trybu PWM dla

//timera 0 i jego wystartowanie

}

Program „Blink” - kod

//***********************************************************

// Definicja funkcji set_timer(). Start timera 0 po

// okresie równym ilości cyklów zegarowych zawartych

// w zmiennej t_period

*************************************************************

void set_timer(int t_period)

//deklaracja funkcji ustawiającej

// i startującej timer 0

{

if (t_period > 1)

{

asm("bit clr mode2 TIMEN0;");

//zatrzymanie timera 0

SetIOP(TPERIOD0, t_period);

// ustawienie cyklu

//timera na wartość zmiennej t_period

SetIOP(TPWIDTH0, 1);

//ustawienie szerokości

//impulsow na 1

asm("bit set mode2 TIMEN0;");

// wystartowanie timera 0

}

}

Program „Blink” - kod

//**********************************************************

*

// Definicja funkcji timer_int(). Podprogram obsługi

// przerwania od timera 0

//**********************************************************

void timer_int( int sig_num )

// deklaracja funkcji

{

sig_num=sig_num;

if (1 & odd_or_even_flag++)

// Jeżeli wartość operandu

// „odd_or_even_flag” nie jest zerem, inkrementuj operand

// i wykonaj:

{

asm("R0 = DM(IOSTAT);

R0 = BCLR R0 BY 2;

// Wyzerowanie flagi nr. 6

DM(IOSTAT) = R0;");

asm("R0 = DM(IOSTAT);

R0 = BSET R0 BY 3;

// Ustawienie flagi nr. 7

DM(IOSTAT) = R0;");

}

...

Program „Blink”

...

else

// Jeżeli warunek (1 & odd_or_even_flag++) nie jest

// spełniony, wykonaj:

{

asm("R0 = DM(IOSTAT);

R0 = BSET R0 BY 2;

// Ustawienie flagi nr. 6

DM(IOSTAT) = R0;");

asm("R0 = DM(IOSTAT);

R0 = BCLR R0 BY 3;

// Wyzerowanie flagi nr. 7

DM(IOSTAT) = R0;");

}

return;

// zakończenie działania funkcji

}

Program „Blink”

//**********************************************************

// Definicja funkcji main(). Główna funkcja. Początkowe

// ustawienie flag, ustawienie i wystartowanie timera,

// przejście w pętle

//**********************************************************

*

void main ( void )

// deklaracja funkcji

{

asm("R0 = DM(IOSTAT);

R0 = BCLR R0 BY 2;

// Wyzerowanie flagi nr. 6

DM(IOSTAT) = R0;");

asm("R0 = DM(IOSTAT);

R0 = BSET R0 BY 3;

// Ustawienie flagi nr. 7

DM(IOSTAT) = R0;");

set_timer(FLASH_PERIOD);

// Wywołanie funkcji „Set_timer” z

// argumentem = wartości zmiennej

„FLASH_PERIOD”

init_timer();

// Wywołanie funkcji “Init_timer”

while( 1 )

// Przejście do nieskończonej pętli

{

idle();

// Zatrzymanie procesora , będzie reagował

// tylko na przerwania

}

}

Generacja przebiegu

sinusoidalnego

ADSP 21065L

#define M_2PI 6.28318530717958647692

#define FS 48000

void main ( void )

{

float output, t, A, f, dt;

A=10000; // Amplituda

f=1000; // Czestotliwosc [Hz]

dt=f/(float)FS;

init_codec();

user_tx_ready = 0;

t=0;

…

Generacja przebiegu

sinusoidalnego

ADSP 21065L – c.d.

…

for(;;)

{

user_rx_ready = 1;

idle();

while (user_tx_ready);

//---------------- Tu wpisz swoj kod -------------------

output=A*sin(M_2PI*t);

t+=dt;

if(t>=1)

t=0;

//------------------------------------------------------

user_tx_buf[RIGHT_CHNL] = output;

user_tx_buf[LEFT_CHANL] = output;

user_tx_buf[TAG] = DOUT_TAG;

user_tx_ready = 1;

};

}

Generacja przebiegu

piłokształtnego narastającego

ADSP 21065L

#define FS 48000

void main ( void )

{

float output, t, A, f, dt;

A=10000; // Amplituda

f=1000; // Częstotliwość [Hz]

dt=2*f/(float)FS;

init_codec();

user_tx_ready = 0;

t=0;

…

Generacja przebiegu

piłokształtnego narastającego

ADSP 21065L – c.d.

…

for(;;)

{

user_rx_ready = 1;

idle();

while (user_tx_ready);

//---------------- Tu wpisz swoj kod -------------------

output=A*t;

t+=dt;

if(t>=1)

t=-1;

//------------------------------------------------------

user_tx_buf[RIGHT_CHNL] = output;

user_tx_buf[LEFT_CHANL] = output;

user_tx_buf[TAG] = DOUT_TAG;

user_tx_ready = 1;

};

}

Generacja figur Lissajou

ADSP 21065L

void Ellipse(float R1, float R2)

{

//---------------- Tu wpisz swoj kod -------------------

static float t=0;

t+=FS_INV1000;

if(t>=1)

t=0;

OutX=R1*sin(M_2PI*t);

OutY=R2*sin(M_2PI*t+M_PI2);

}

Funkcja rysująca

elipsę:

Generacja figur Lissajou

ADSP 21065L – c.d.

void main ( void )

{

float t=0;

float Ax=10000, Ay=10000;

init_codec();

user_tx_ready = 0;

for(;;)

{

user_rx_ready = 1;

idle();

while (user_tx_ready);

//---------------- Tu wpisz swoj kod

-------------------

Ellipse(Ax, Ay);

//-----------------------------------------------

-------

user_tx_buf[RIGHT_CHNL] = OutX;

user_tx_buf[LEFT_CHANL] = OutY;

user_tx_buf[TAG] = DOUT_TAG;

user_tx_ready = 1;

};

}

Program

główny z

wywołaniem

funkcji

rysującej

elipsę:

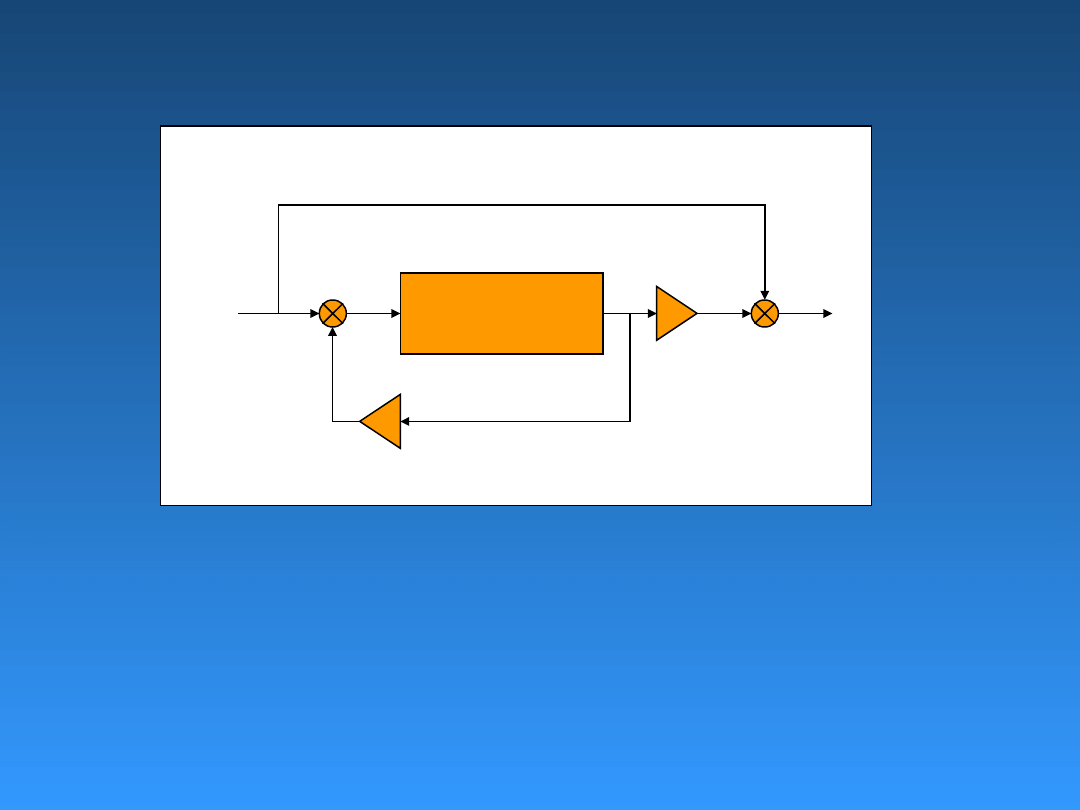

Generacja echa

Ou

t

+

+

Gain

1

In

+

+

Direct

Signal

Reverb

feedback

FIFO

Gain 2

W schemacie blokowym generacji echa kluczową rolę

odgrywa pamięć FIFO, która opóźnia sygnał bezpośredni o

n

próbek. Poziom sygnału odbicia jednokrotnego i

wielokrotnego kontroluje element wzmacniający Gain2 a

poziom sygnału przy odbiciach wielokrotnych Gain1.

Współczynniki Gain1 i Gain2 są z reguły mniejsze od

jedności.

Generacja echa

float sound_delay(float in, int time, float *buff)

{

float out;

static int n=0;

out=buff[n];

buff[n]=in;

n++;

if(n>=time*48)

n=0;

return out;

}

Generacja echa

void main ( void )

{

int i;

float filter_input;

float filter_output;

float fifo;

float gain1=1.0;

float gain2=0.8;

int delay=100;

for( i=0; i<BUFFSIZE; i++)

buffer[i]=0;

// Initialize some codec registers.

init_codec();

Generacja echa

// Loop forever.

user_tx_ready = 0;

for(;;)

{

user_rx_ready = 1;

idle();

while (user_rx_ready);

while (user_tx_ready);

filter_input = user_rx_buf[RIGHT_CHNL];

fifo=gain2*sound_delay(fifo,100,buffer)+filter_input;

filter_output=filter_input+gain1*fifo;

user_tx_buf[RIGHT_CHNL] = filter_output;

user_tx_buf[LEFT_CHANL] = filter_output;

user_tx_buf[TAG] = DOUT_TAG;

user_tx_ready = 1;

};

}

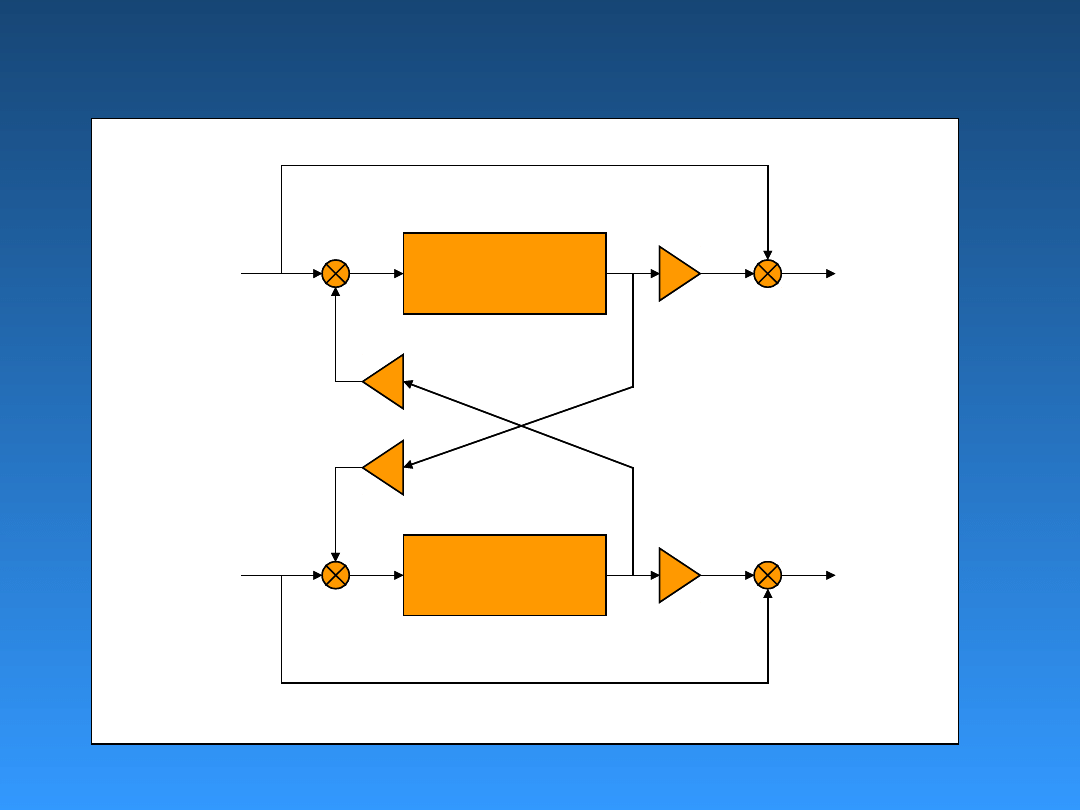

Efekt Ping-pong

Ga

in

2

Gain

4

Out

L

+

+

Gain

1

In

L

+

+

Direct

Signal

Reverb

feedback

FIFO

Ou

t

R

+

+

In

R

+

+

Dir

ect

Sig

na

l

Rev

erb

feed

ba

ck

FIF

O

Gain

3

Ga

in

2

Gain

4

Out

L

+

+

Gain

1

In

L

+

+

Direct

Signal

Reverb

feedback

FIFO

Ou

t

R

+

+

In

R

+

+

Dir

ect

Sig

na

l

Rev

erb

feed

ba

ck

FIF

O

Gain

3

Koniec

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Slide 46

- Slide 47

- Slide 48

- Slide 49

- Slide 50

- Slide 51

- Slide 52

Wyszukiwarka

Podobne podstrony:

Lab4 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

lab9 procesory sygnalowe, LABORATORIUM

6 Procesy i sygnaly

16 procesory sygnalowe ADSP21

Procesory sygnałowe 1

Procesory sygnałowe 6

Procesory sygnałowe 4

Lab1 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Lab5 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Procesory sygnałowe 3

Sitek-wykłady, Komunikacja między procesami, Komunikacja między procesami: sygnały

ele4 z2, 7 semestr, Procesory Sygnałowe, Laboratoria

Instrukcja PS1, 7 semestr, Procesory Sygnałowe, Laboratoria

Procesory sygnałowe 3

Ćwiczenie 18 & 19 Procesory Sygnalowe

Procesory sygnałowe 7

Procesory sygnałowe 2

Lab2 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Lab3 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

więcej podobnych podstron