Procesory sygnałowe

Wykład 7

Architektura procesora

ADSP-21065L (mapa pamięci,

pamięć SRAM, kontroler DMA)

Dr inż. Robert

Wielgat

Mapa pamięci systemu z

procesorem ADSP-21065L

Przestrzeń adresowa systemu z procesorem ADSP-21065L

jest zamapowana w sposób następujący:

256 rejestrów IOP procesora ADSP-21065L .

Rejestry

pozwalają konfigurować, odczytywać status oraz

wymieniać dane z urządzeniami peryferyjnymi

Adresy od 0x0000 0000 do 0x0000 00FF

Pamięć dla współpracy wieloprocesorowej -2*256 rejestrów

IOP

innych procesorów w systemie wieloprocesorowym

Rejestry IOP (proc. IDO1)

Adresy od 0x0000 0100 do

0x0000 01FF

Rejestry IOP (proc. IDO2)

Adresy od 0x0000 0200 do

0x0000 02FF

Obszar zarezerwowany

Adresy od 0x0000 0300 do

0x0000 7FFF

Mapa pamięci systemu z

procesorem ADSP-21065L –

pamięć wewnętrzna

Pamięć wewnętrzna.

Obejmuje nieciągły obszar pamięci

adresów od 0x0000 8000 do 0x0001 FFFF. Dla użytkownika

są dostępne następujące zakresy adresów:

Adresy od 0x0000 8000 do 0x0000 9FFF –

Blok 0, słowa

normalne 32-bitowe lub 48-bitowe

Adresy od 0x0000 C000 do 0x0000 DFFF –

Blok 1, słowa

normalne 32-bitowe lub 48-bitowe

Adresy od 0x0001 0000 do 0x0001 3FFF –

Blok 0, słowa

krótkie

16-bitowe

Adresy od 0x0001 8000 do 0x0001 BFFF –

Blok 1, słowa

krótkie

16-bitowe

Różne przestrzenie adresowe dotyczą tej samej fizycznej

pamięci

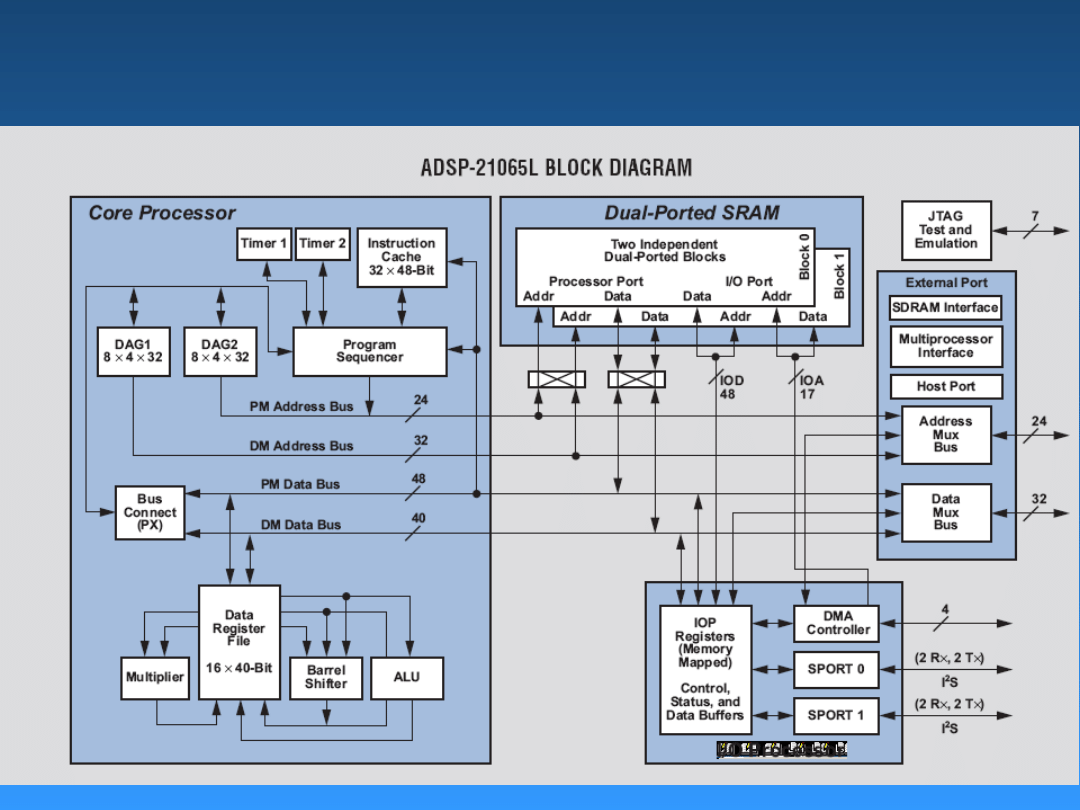

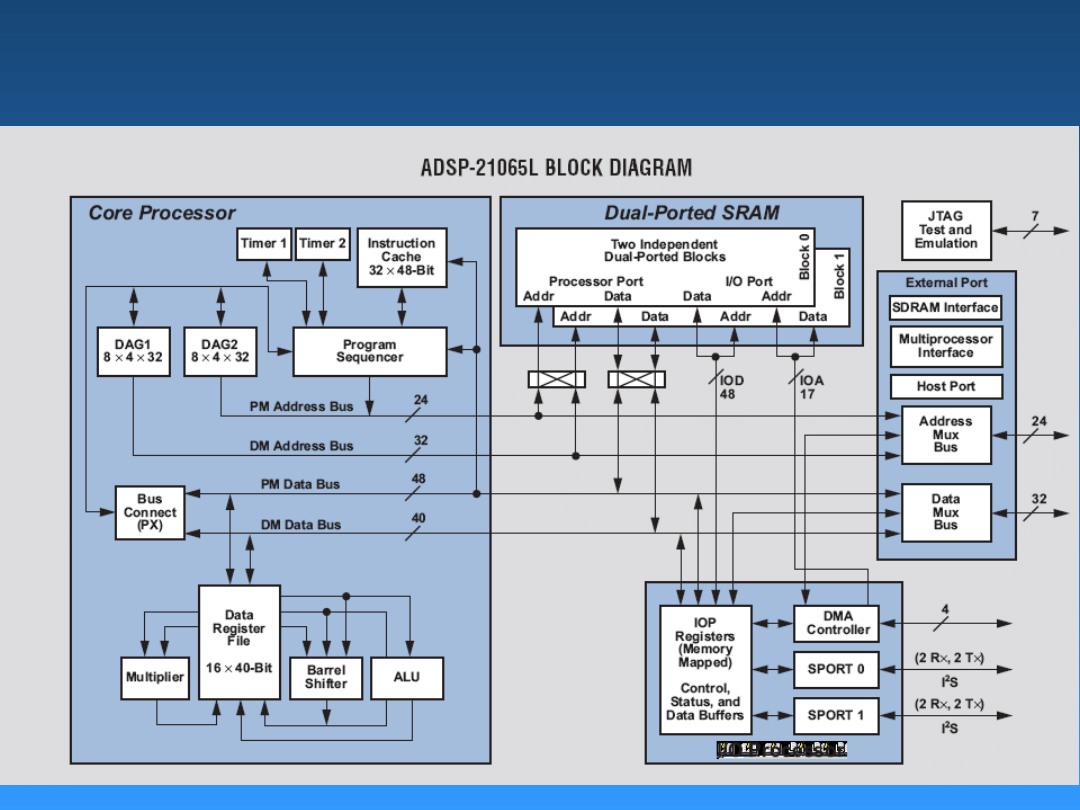

Schemat blokowy ADSP-

21065L

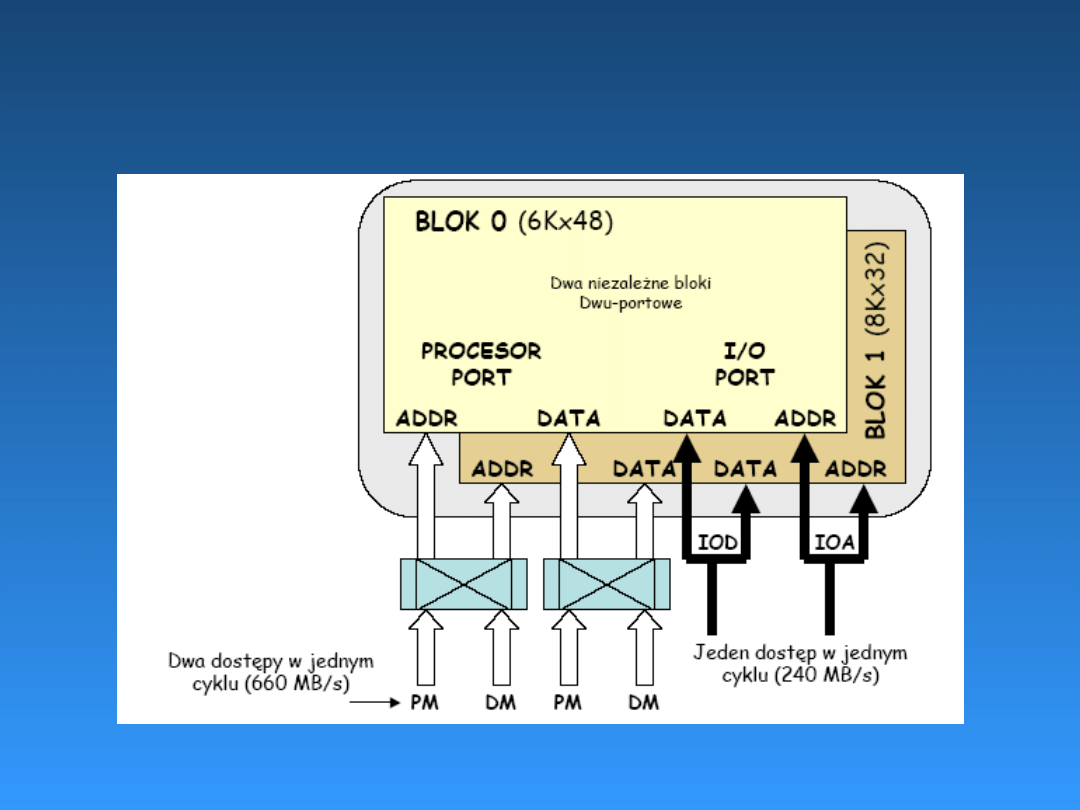

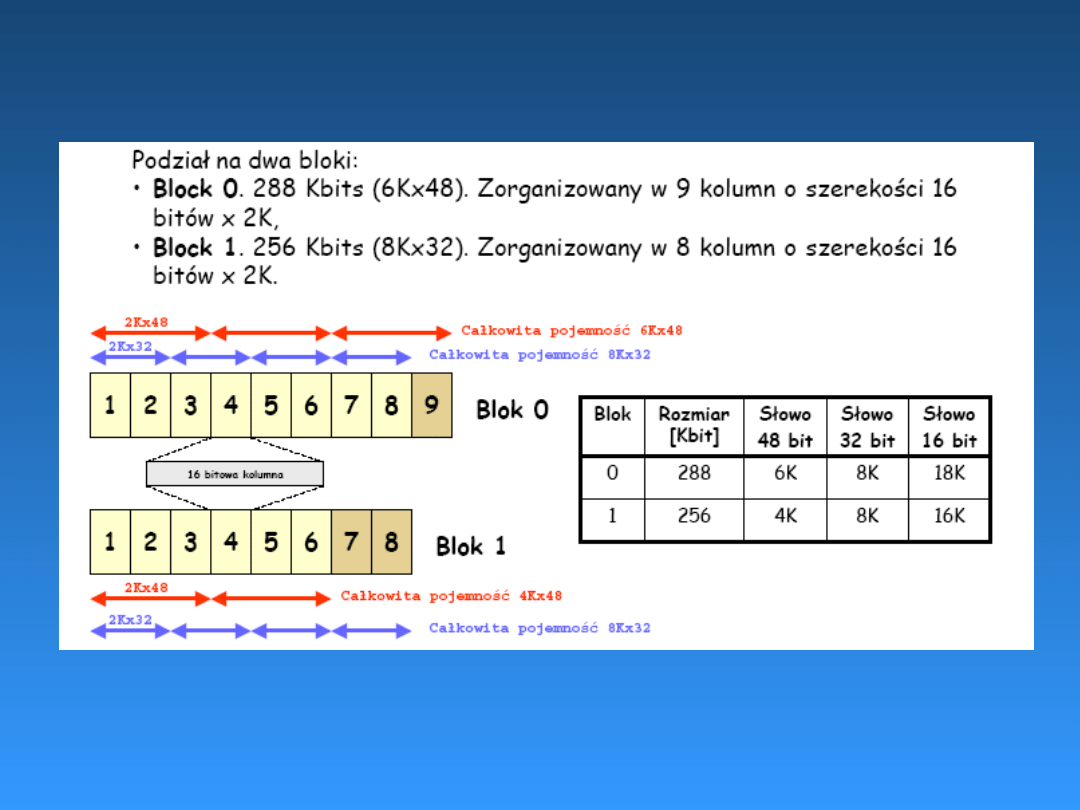

Struktura pamięci wewnętrznej

SRAM

Organizaja pamięci wewnętrznej

Mapa pamięci systemu z

procesorem ADSP-21065L –

pamięć zewnętrzna

Pamięć zewnętrzna.

Obejmuje ciągły obszar

pamięci adresów od 0x0002 0000 do 0x03FF

FFFF. Pamięć zewnętrzna jest podzielona na 4

banki do 16 Msłów

32-bitowych:

Adresy od 0x0002 0000 do 0x00FF FFFF –

Bank

0

Adresy od 0x0100 0000 do 0x01FF FFFF –

Bank

1

Adresy od 0x0200 0000 do 0x02FF FFFF –

Bank

2

Adresy od 0x0300 C000 do 0x03FF FFFF –

Bank3

Każdy z banków może mieć do 16 Msłów 32-

bitowych, za wyjątkiem banku 0, którego

pojemność jest pomniejszona o 128 ksłów.

Programowe umieszczanie kodu i

danych w pamięci

Domyślne nazwy segmentów pamięci używanych przez

kompilator języka C:

•seg_rth.

Nazwa segmentu z tablicą wektorów przerwań

oraz startowym kodem inicjalizującym

•seg_init.

Nazwa segmentu zawierającego inicjalizację

rejestrów procesora

•seg_init.

Nazwa segmentu z kodem inicjalizującym

•seg_pmco.

Nazwa segmentu, do którego ładowany jest

kod programu

•seg_dmda.

Nazwa segmentu w pamięci danych, do

którego ładowane są zmienne globalne i statczne.

•seg_pmda.

Nazwa segmentu w pamięci programu, do

którego są ładowane zmienne globalne i statyczne

•seg_stack.

Nazwa segmentu dla obszaru stosu

•seg_heap.

Nazwa segmentu dla obszaru sterty – obszaru

pamięci przeznaczonego do dynamicznej alokacji pamięci

UWAGA! Wszystkie informacje dotyczące obszaru pamięci

przydzielonego do każdego z segmentów znajdują się w

pliku LDF (ang. Linker Description File)

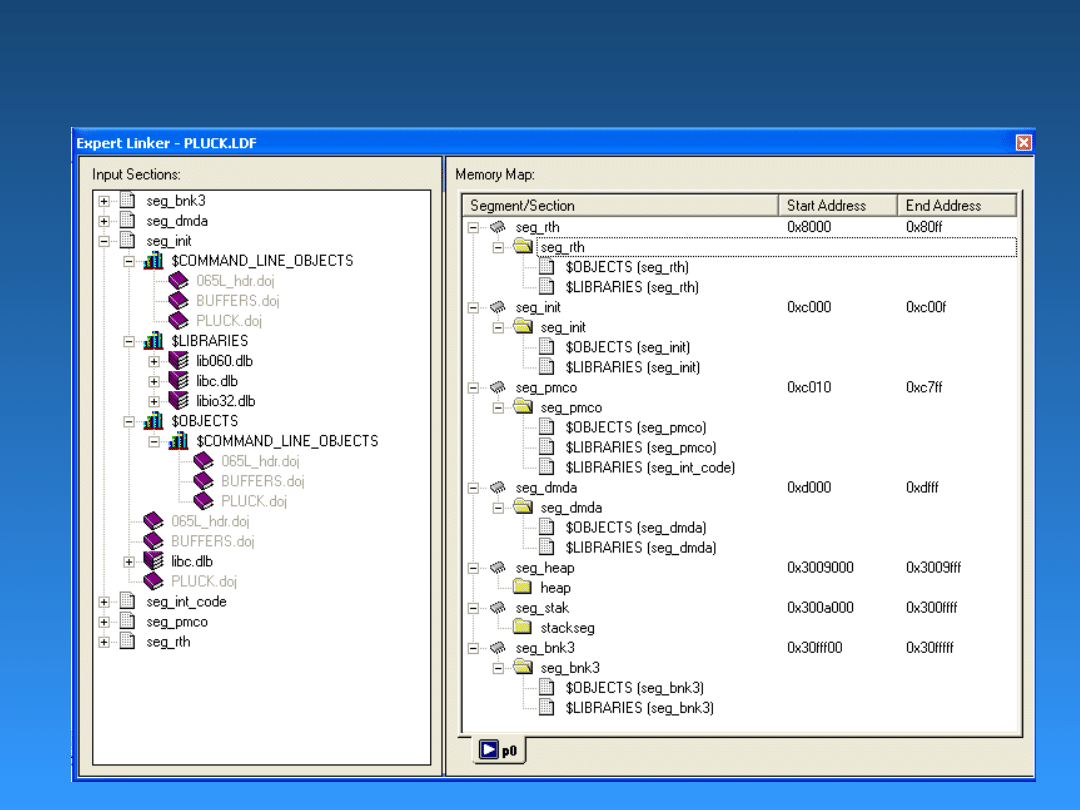

Expert Linker

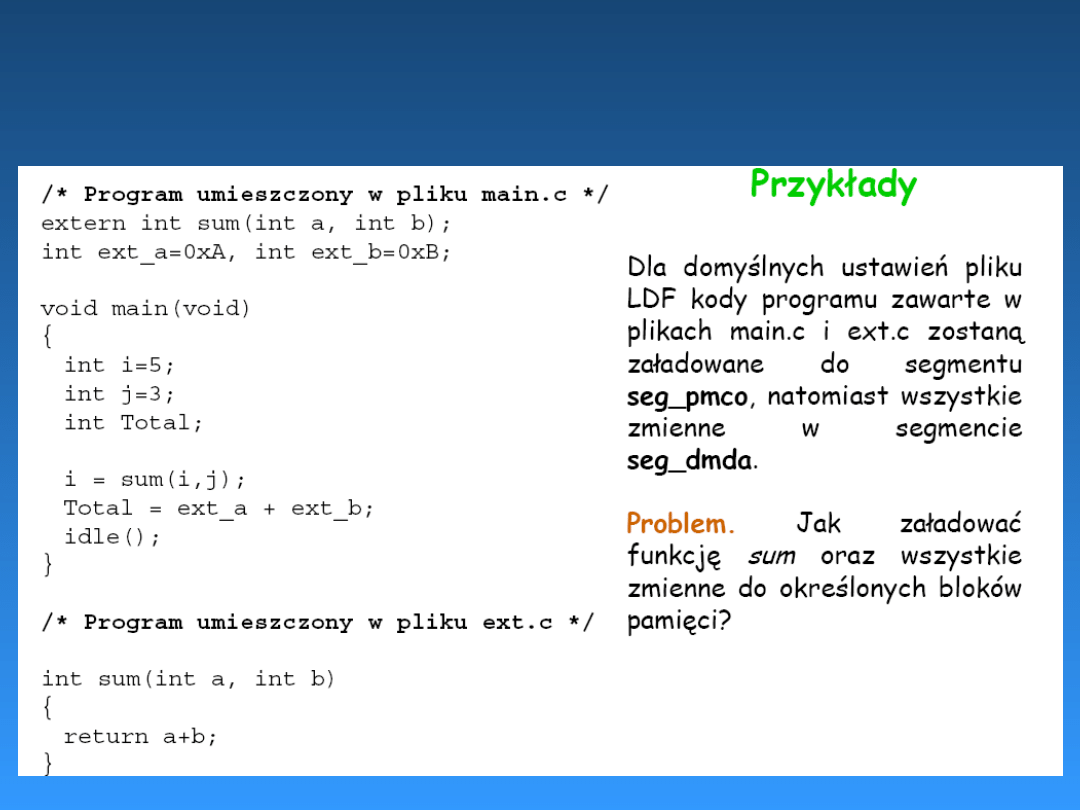

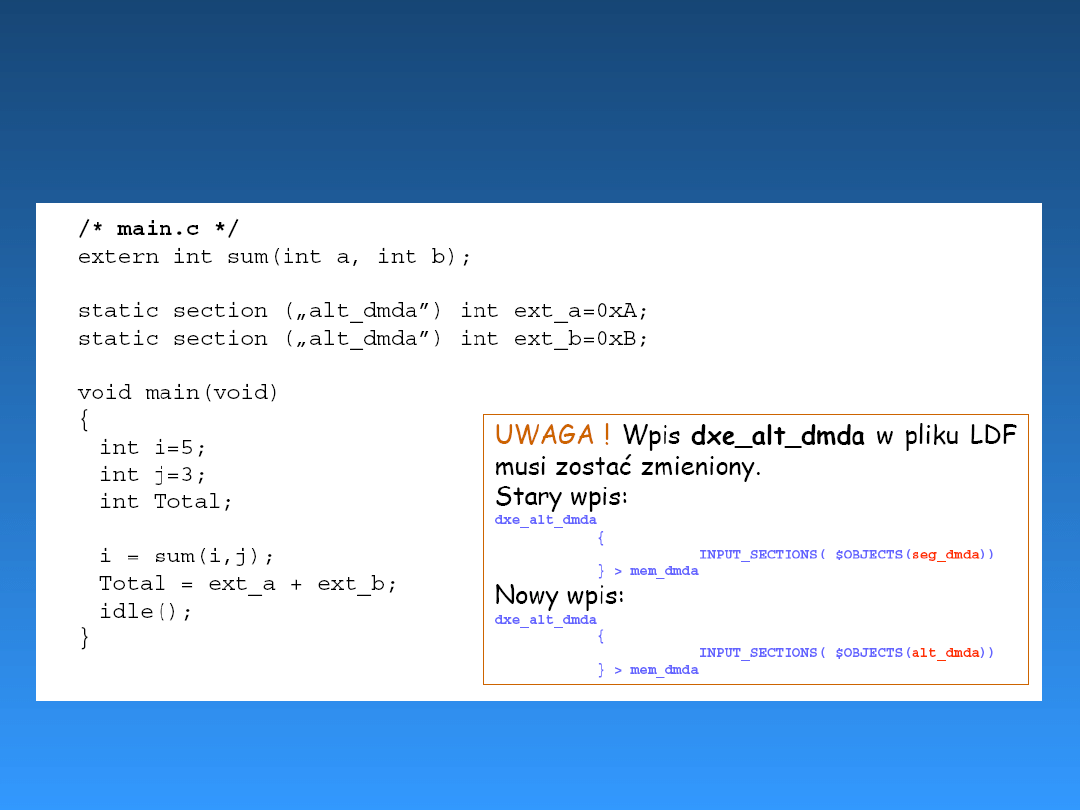

Przykład umieszczania kodu i

danych w pamięci

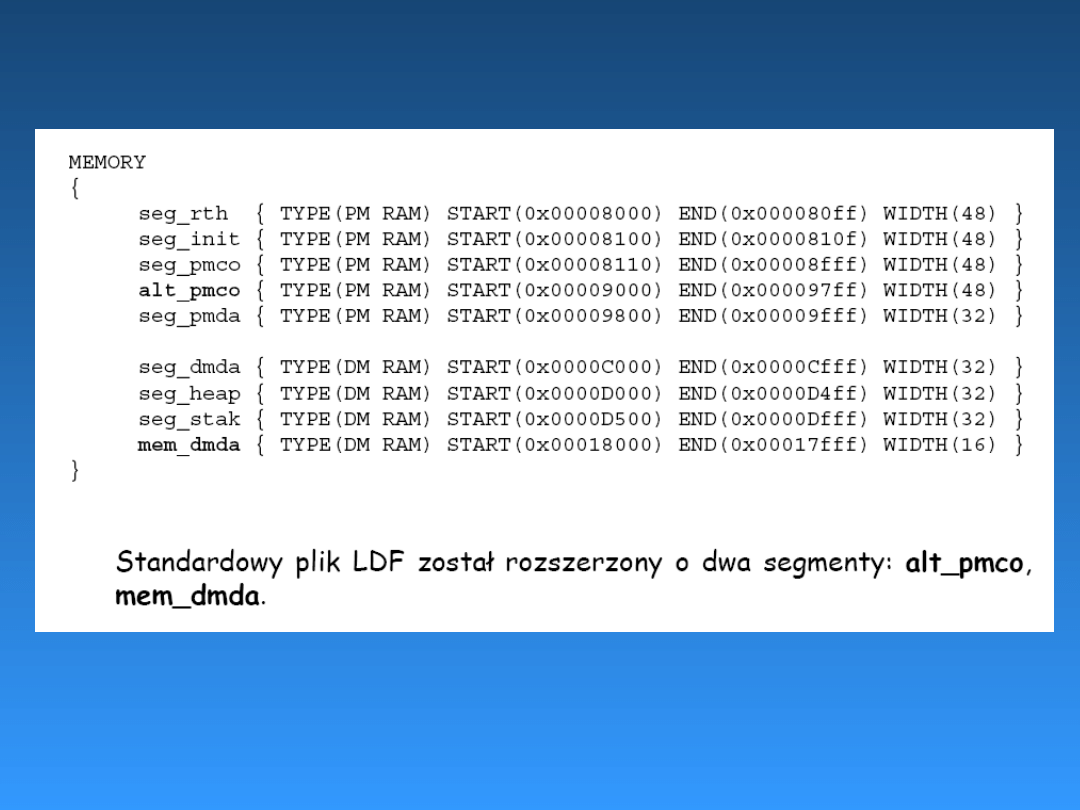

Zawartość pliku LDF

Dyrektywa linkera ‘MEMEORY’ opisuje pożądane

rozmieszczenie segmentów wyjściowych w systemie

docelowym

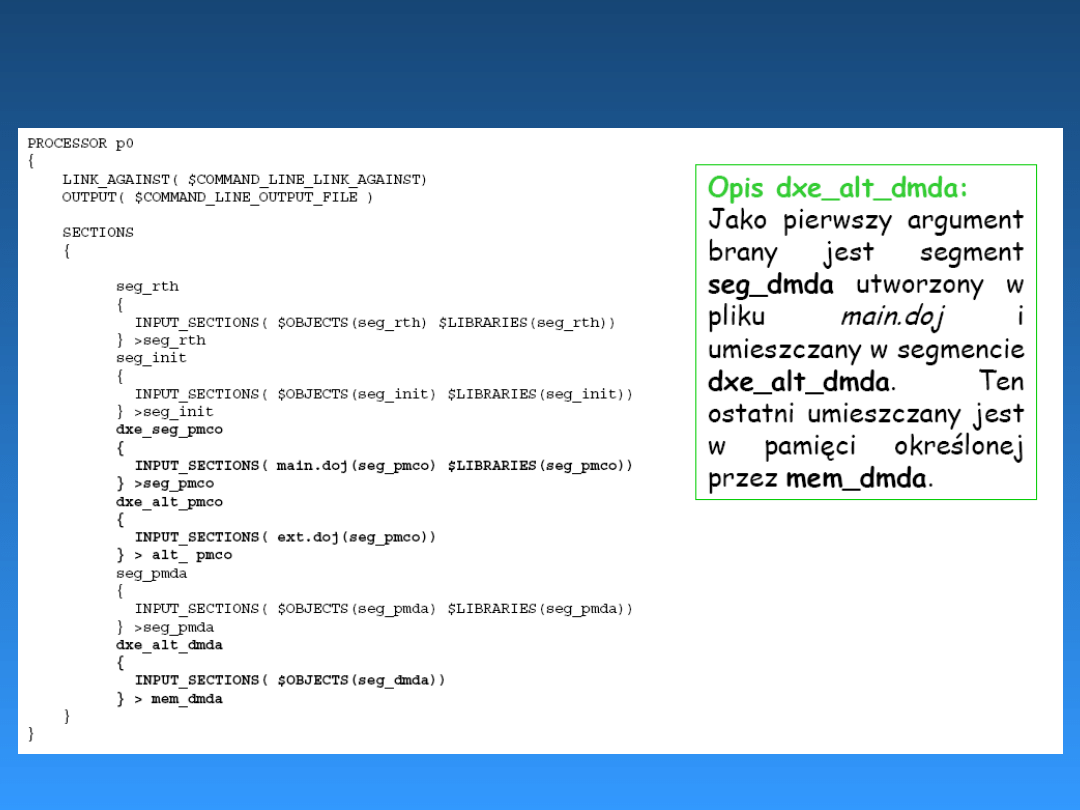

Zawartość pliku LDF c.d.

Dyrektywy linkera w pliku LDF

PROCESOR p0 { }

- Dyrektywa nakazująca linkerowi utworzenie

pliku wykonywalnego. p0 określa numer procesora w systemie.

LINK_AGAINST

– Dyrektywa używana przy pracy

wieloprocesorowej

OUTPUT

– Dyrektywa określa nazwę pliku wykonywalnego.

Nazwa

$COMMAND_LINE_OUTPUT_FILE

jest makrem

zawierającym nazwę pliku wykonywalnego. Makro definiuje się

dyrektywą preprocesora

#define

.

SECTIONS

– Dyrektywa opisuje jak rozmieszczać sekcje

wejściowe zawarte w plikach obiektowych w pamięci systemu

opisanej przez dyrektywę

MEMORY

.

seg_rth

{ INPUT_SECTIONS ($OBJECTS(seg_rth) $LIBRARIES(seg_rth)) }

>seg_rth

Powyższa linia określa, że sekcje wejściowe o nazwie seg_rth

zawarte we wszystkich plikach obiektowych (.DOJ)

specyfikowanych makrem

$OBJECTS

oraz w plikach

bibliotecznych specyfikowanych makrem

$LIBRARIES

zostaną

umieszczone w segmencie wyjściowym seg_rth. Nazwa seg_rth

na początku linii, jest nazwą rekordu.

Słowo kluczowe SECTION

Schemat blokowy ADSP-

21065L

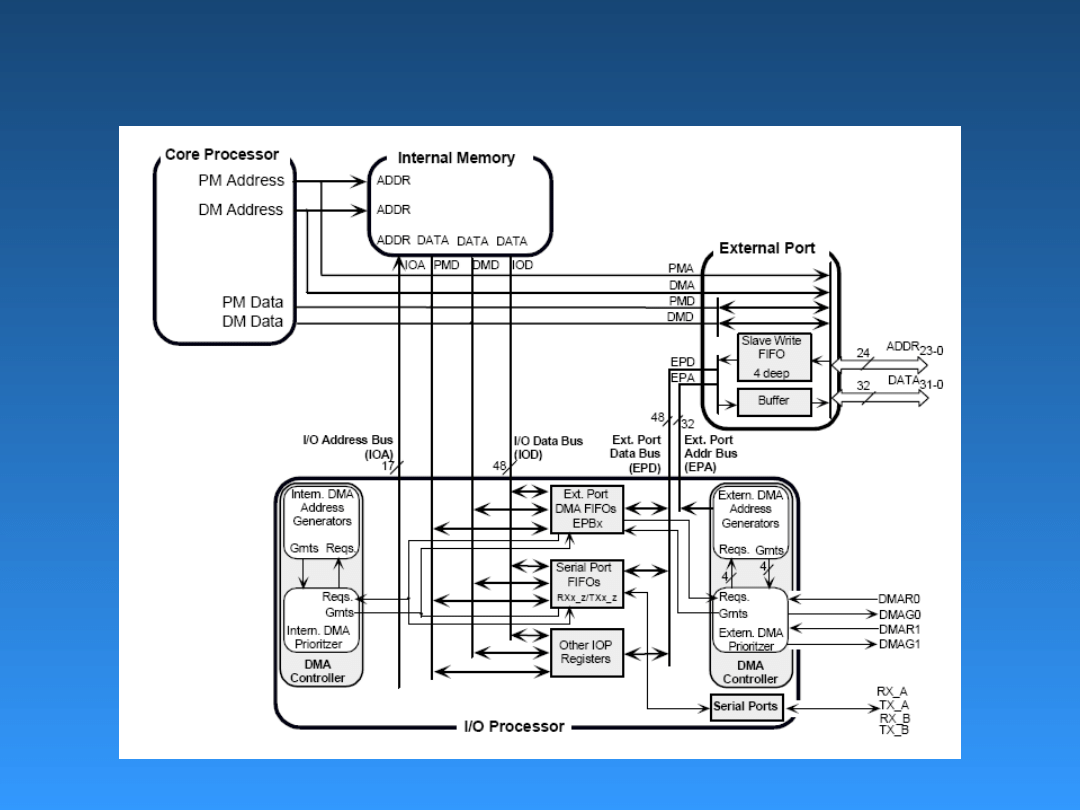

Kontroler DMA – schemat

blokowy

Kontroler DMA

Kontroler DMA umożliwia procesorowi lub urządzeniu

zewnętrznemu zlecenia przesyłu danych pozwalającego na

powrót procesora lub urządzenia do normalnej pracy w

czasie, gdy kontroler DMA zajmuje się przesyłem danych.

Kontroler DMA posiada możliwość przesyłania bloków

danych między:

• pamięcią wewnętrzną a pamięcią zewnętrzną

• pamięcią wewnętrzną a rejestrem IOP innego procesora

ADSP-21065L

• pamięcią wewnętrzną a procesorem nadrzędnym (host

processor)

• pamięcią wewnętrzną a portem szeregowym I/O

• pamięcią zewnętrzną a urządzeniami zewnętrznymi

Kontroler DMA – sposoby

przesyłania danych

Kontroler DMA może przesłać dane w jeden z czterech

sposobów:

1. Przesyłanie bloków danych przez port zewnętrzny

Ten tryb transmisji umożliwia przesyłanie bloków

danych między pamięcią wewnętrzną a pamięcią

zewnętrzną, procesorem nadrzędnym, innym

procesorem lub zamapowanym w pamięci urządzeniem

zewnętrznym.

Istnieją cztery tryby transmisji DMA przez port

zewnętrzny:

master, handshake, external handshake, paced master

2. Transmisja danych przez porty szeregowe

Zarówno transmisja danych przez port zewnętrzny jak i

transmisja przez porty szeregowe wymaga

skonfigurowania bufora pamięci wewnętrznej. W

przypadku transmisji przez porty szeregowe są

wykorzystywane bufory Tx oraz Rx, a w przypadku

transmisji przez port zewnętrzny bufor EPBx.

Kontroler DMA – sposoby

przesyłania danych c.d.

3. Transmisja między urządzeniami zewnętrznymi a

pamięcią zewnętrzną

Ten typ transmisji może odbywać się na dwa sposoby:

•

Poprzez odczyt lub zapis danych do jednego z

buforów kontrolera DMA

•

Poprzez wykorzystanie wejść sterujących DMARx

4. Transfer kanałami DMA

W tym typie transmisji po wykonaniu jednej transmisji

jest inicjalizowana automatycznie kolejna transmisja

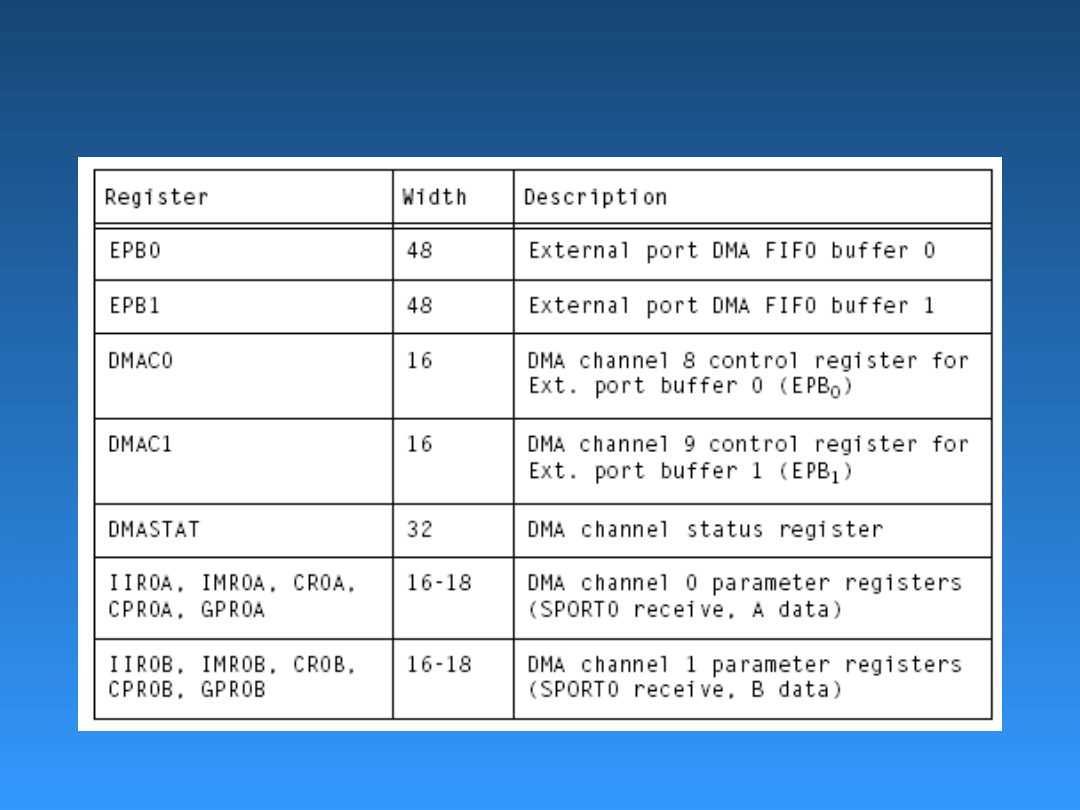

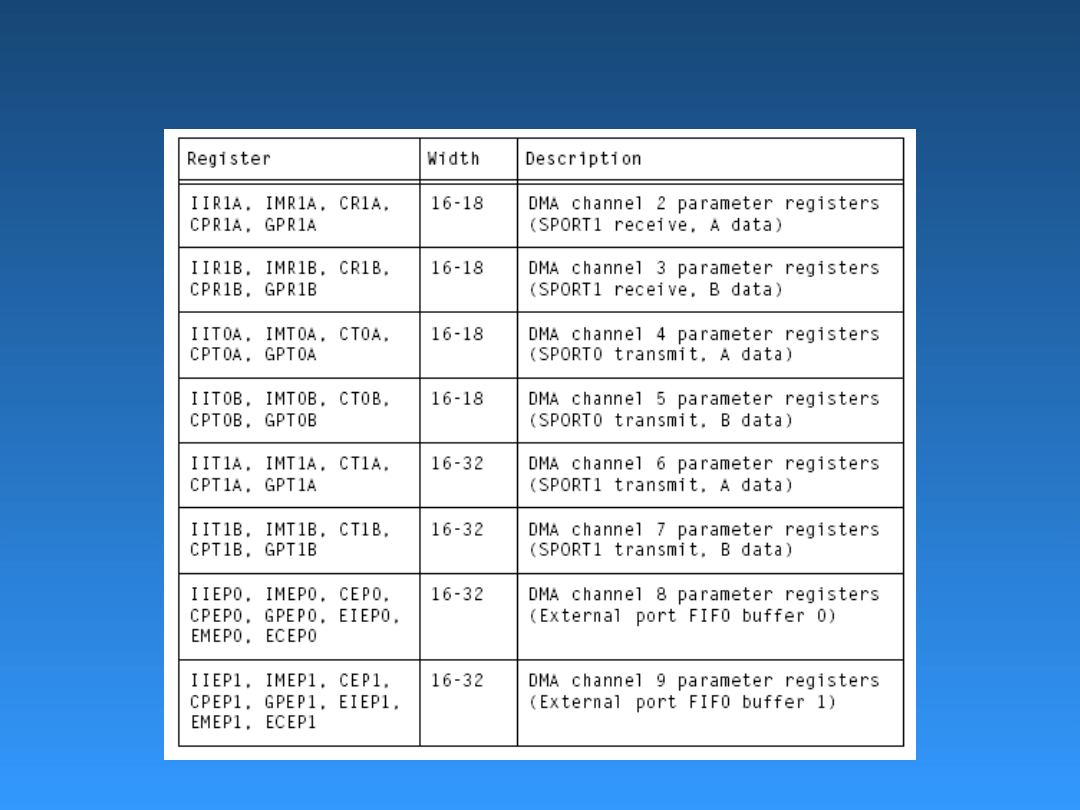

Kontroler DMA – rejestry

Kontroler DMA – rejestry c.d.

Literatura

1) Analog Devices, ADSP-21065L SHARC® DSP.

DSP Microcomputer, Data Sheet, USA,

2) Analog Devices, ADSP-21065L SHARC

®

DSP.

Technical Reference,

3) Analog Devices, ADSP-21065L SHARC® DSP.

User’s Manual, USA, 2003. Strony (183-326)

4) Analog Devices, E-132, Placing C Code and

Data Modules in SHARC Memory Using

VisualDSP++, USA, 2000.

Dokumentację można pobrać ze strony

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

Wyszukiwarka

Podobne podstrony:

Lab4 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

lab9 procesory sygnalowe, LABORATORIUM

6 Procesy i sygnaly

16 procesory sygnalowe ADSP21

Procesory sygnałowe 1

Procesory sygnałowe 2

Procesory sygnałowe 6

Procesory sygnałowe 4

Lab1 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Lab5 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Procesory sygnałowe 3

Sitek-wykłady, Komunikacja między procesami, Komunikacja między procesami: sygnały

ele4 z2, 7 semestr, Procesory Sygnałowe, Laboratoria

Instrukcja PS1, 7 semestr, Procesory Sygnałowe, Laboratoria

Procesory sygnałowe 3

Ćwiczenie 18 & 19 Procesory Sygnalowe

Procesory sygnałowe 2

Lab2 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

Lab3 Procesory sygnałowe sprawozdanie PWR, PWr, sprawozdania

więcej podobnych podstron