Przerzutniki

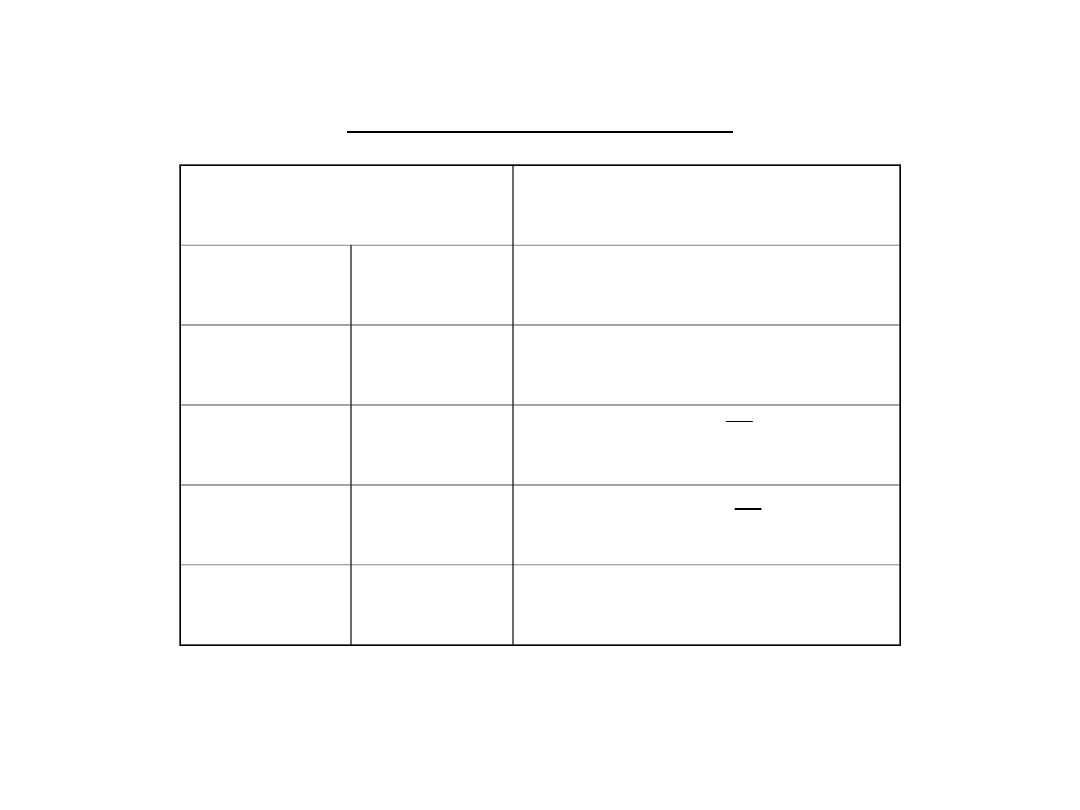

RS Flip-Flop - definicja

Inputs

Output

S

R

0

0

Brak zmiany

1

0

0

1

1

1

Niedozwolone

0

1

X

X

1

0

X

X

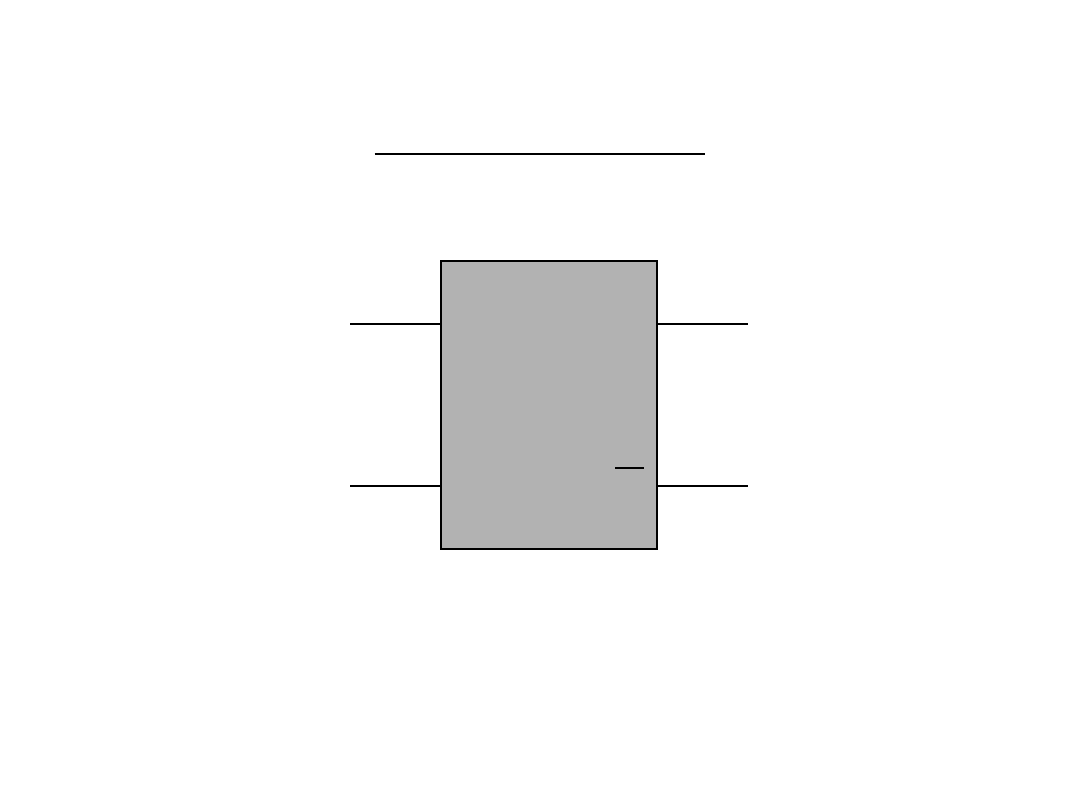

RS Flip-Flop – zapis

S

R

Outputs

Inputs

X

X

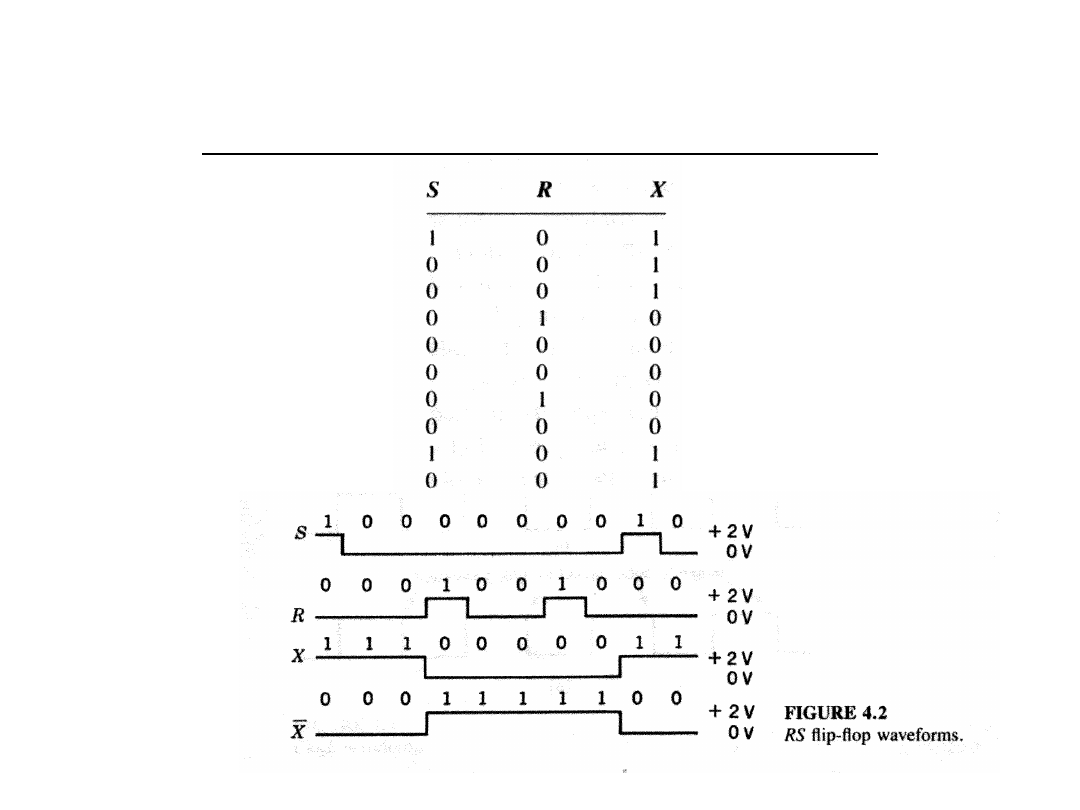

RS Flip-Flop – przykład sekwencji zmian

0

1

X

X

0

1

X

X

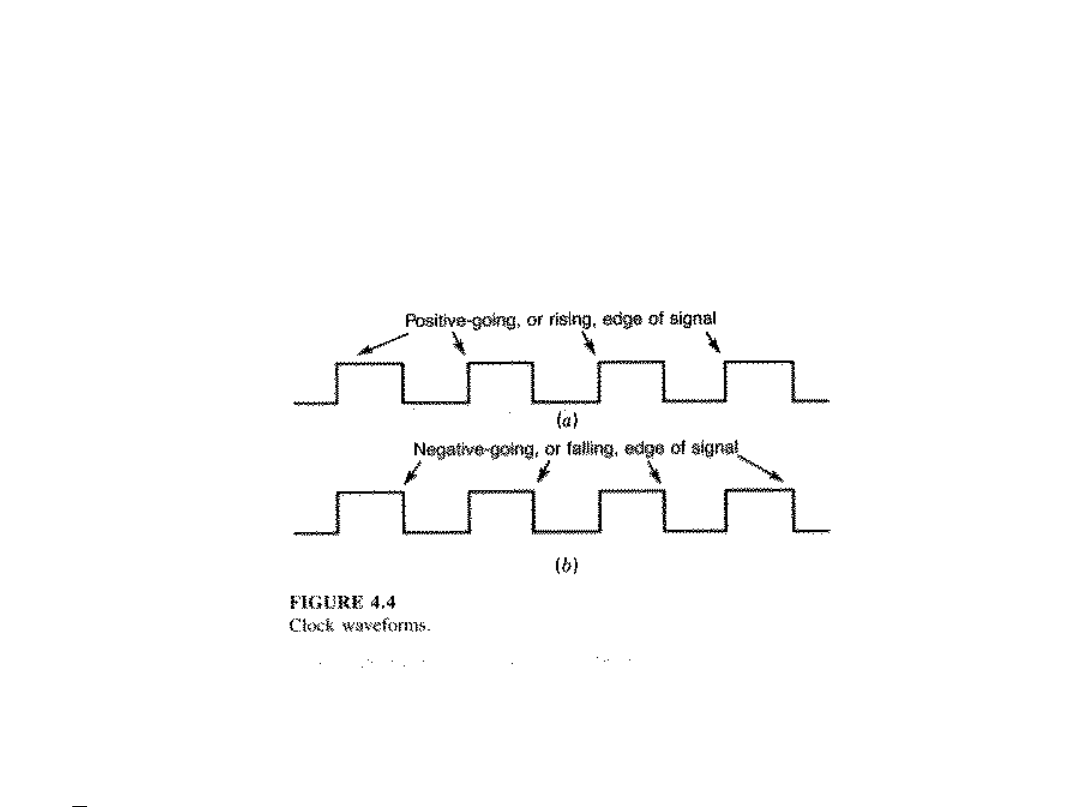

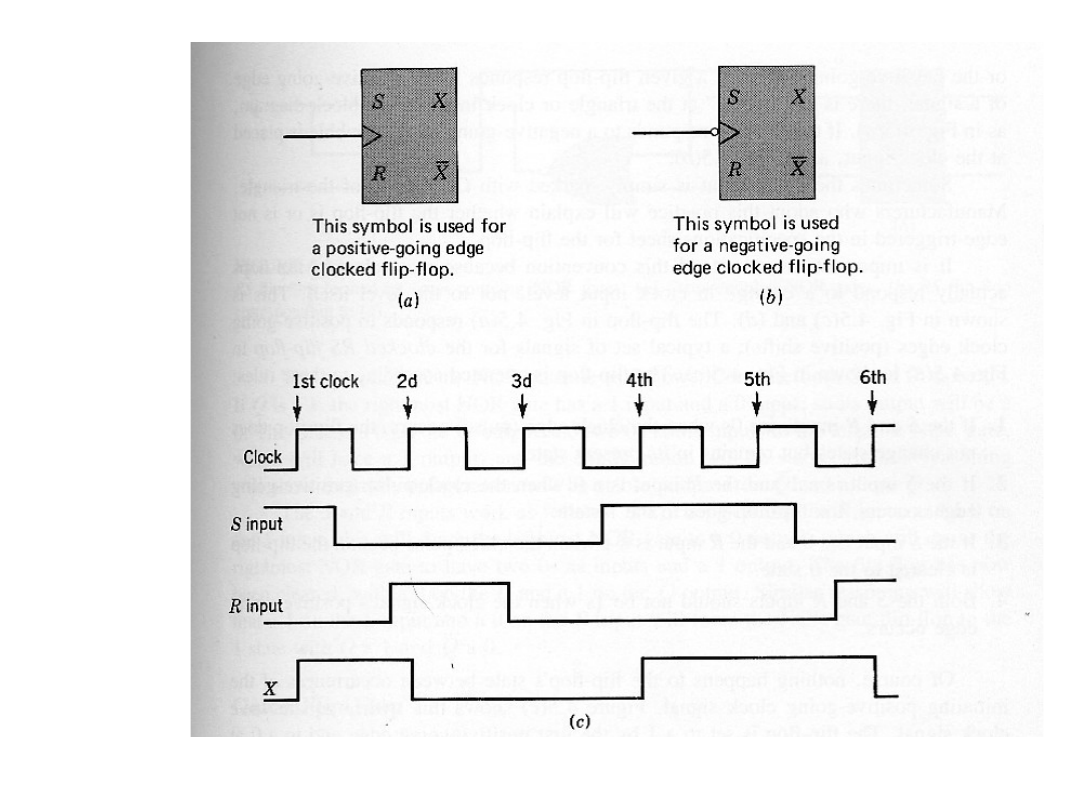

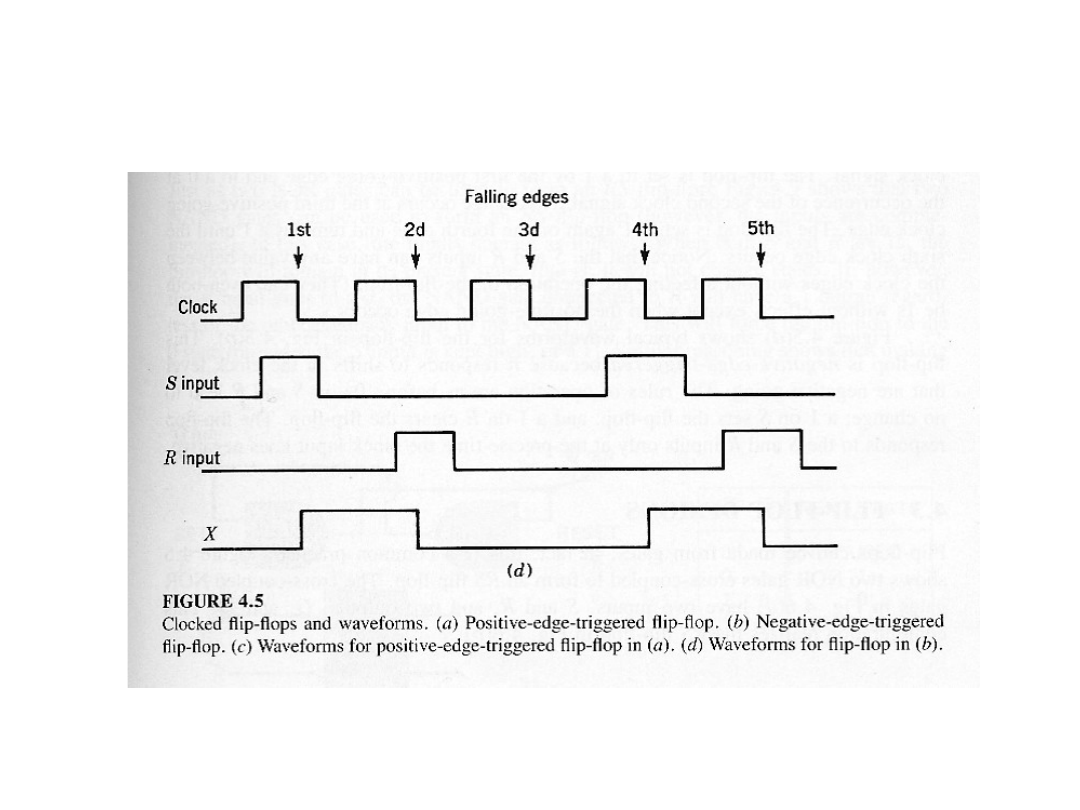

Kategorie przerzutników:

a) dynamiczne

b) synchronizowane

P

r

z

y

k

ł

a

d

Przykład ć.d.

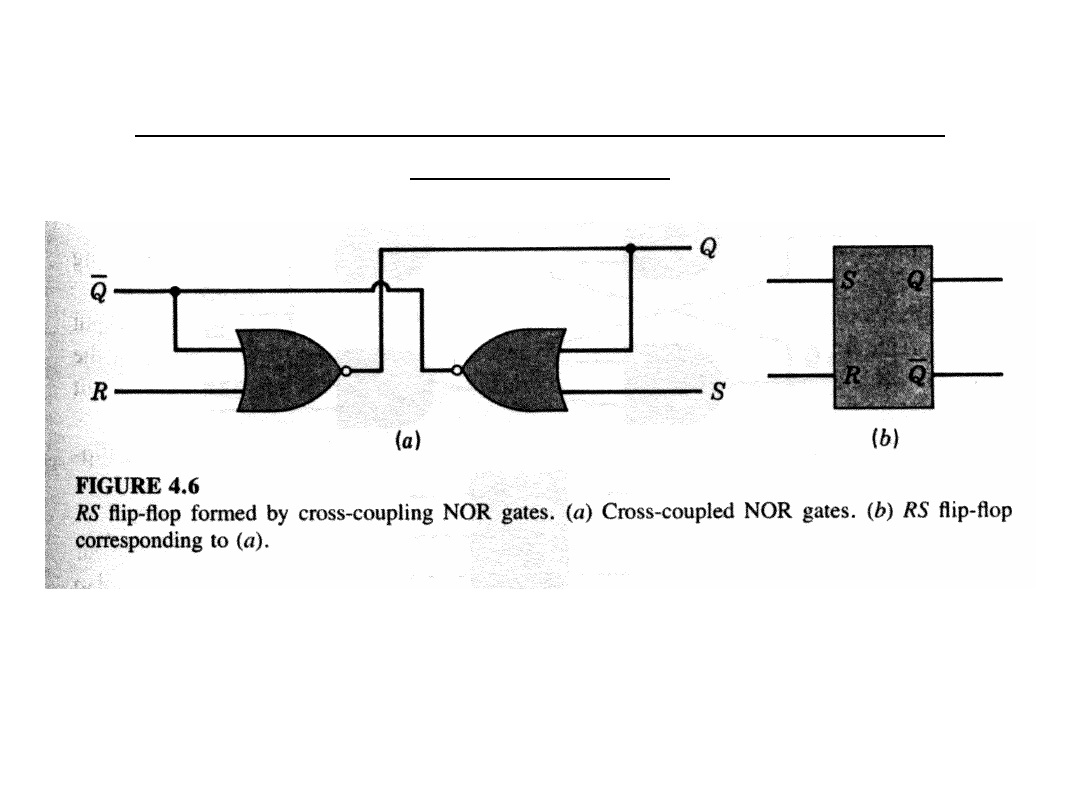

Realizacja przerzutnika RS przy pomocy

bramek NOR

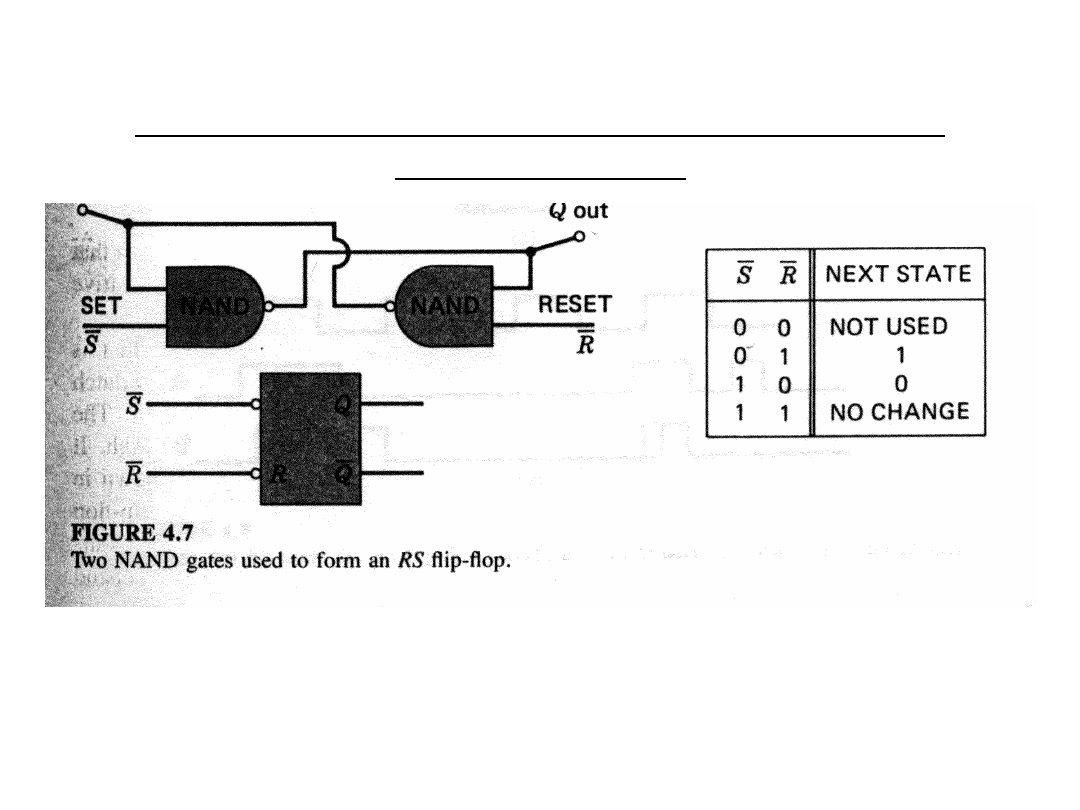

Realizacja przerzutnika RS przy pomocy

bramek NAND

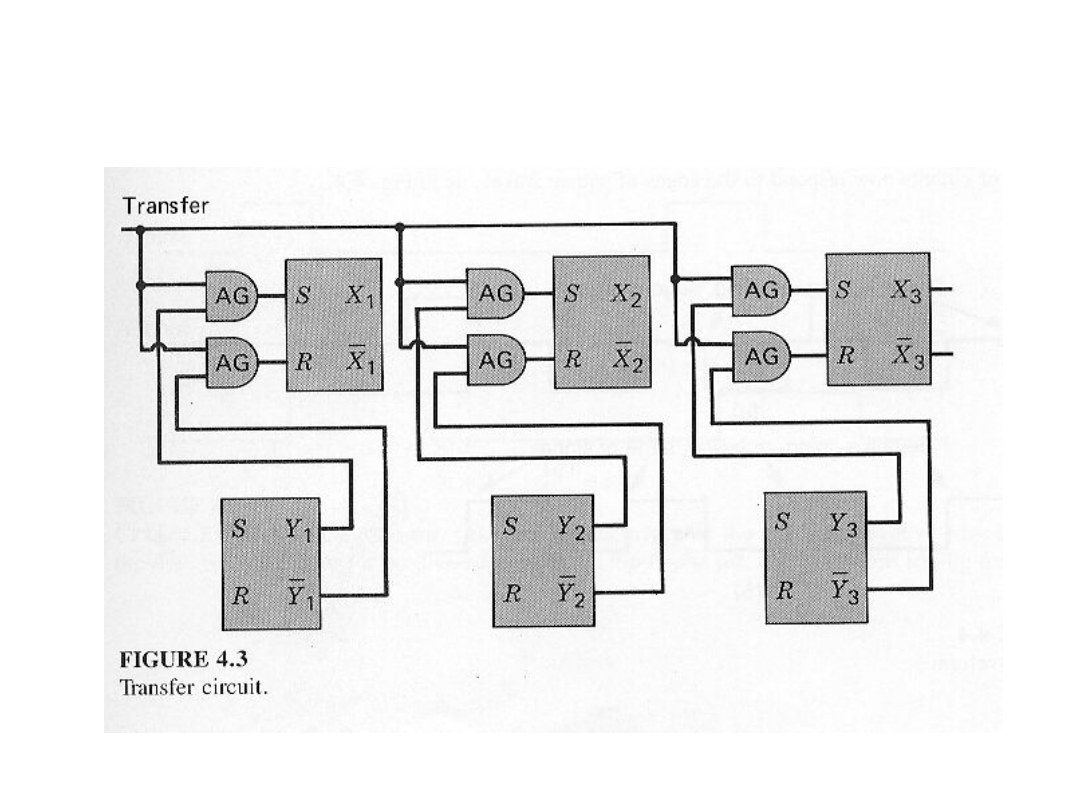

Układ realizujący transfer

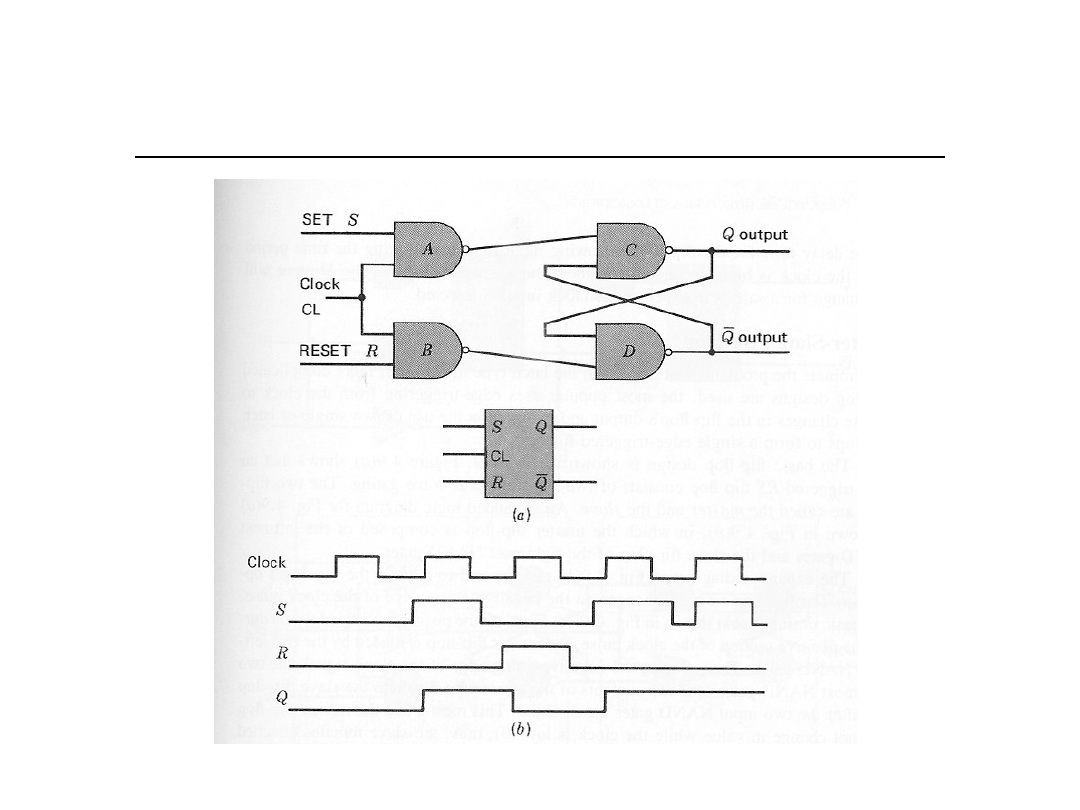

RS przerzutnik typu latch (zatrzaskowy)

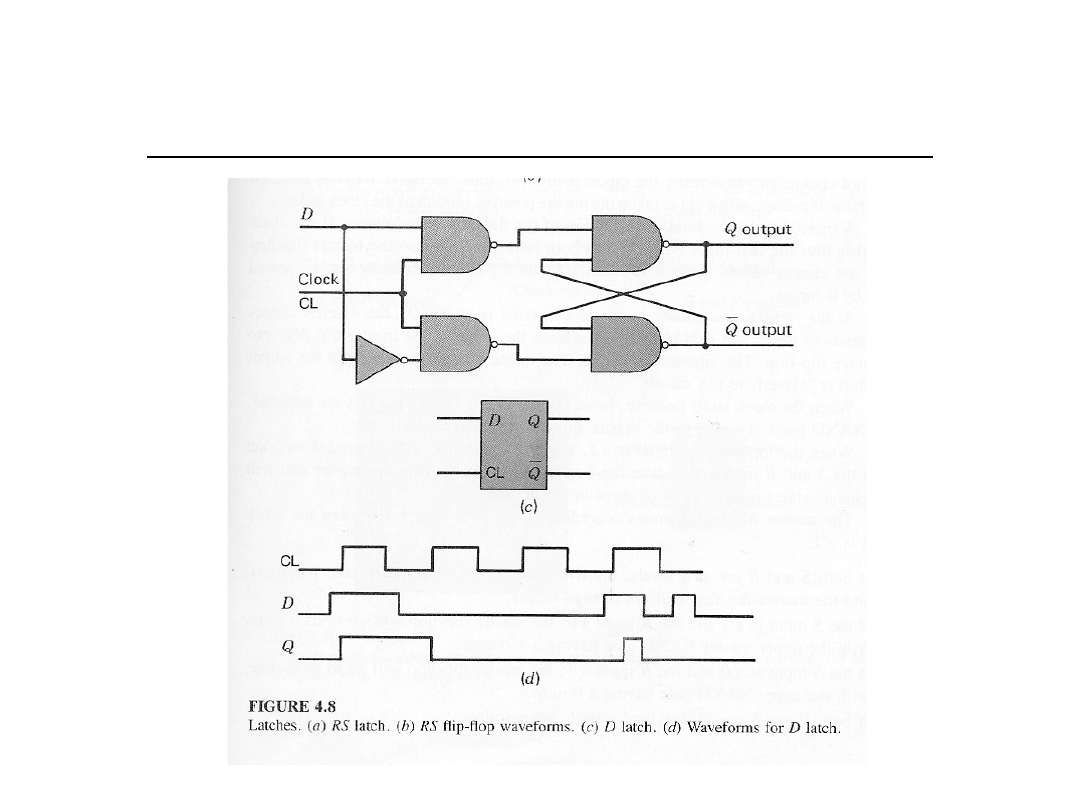

D przerzutnik typu latch (zatrzaskowy)

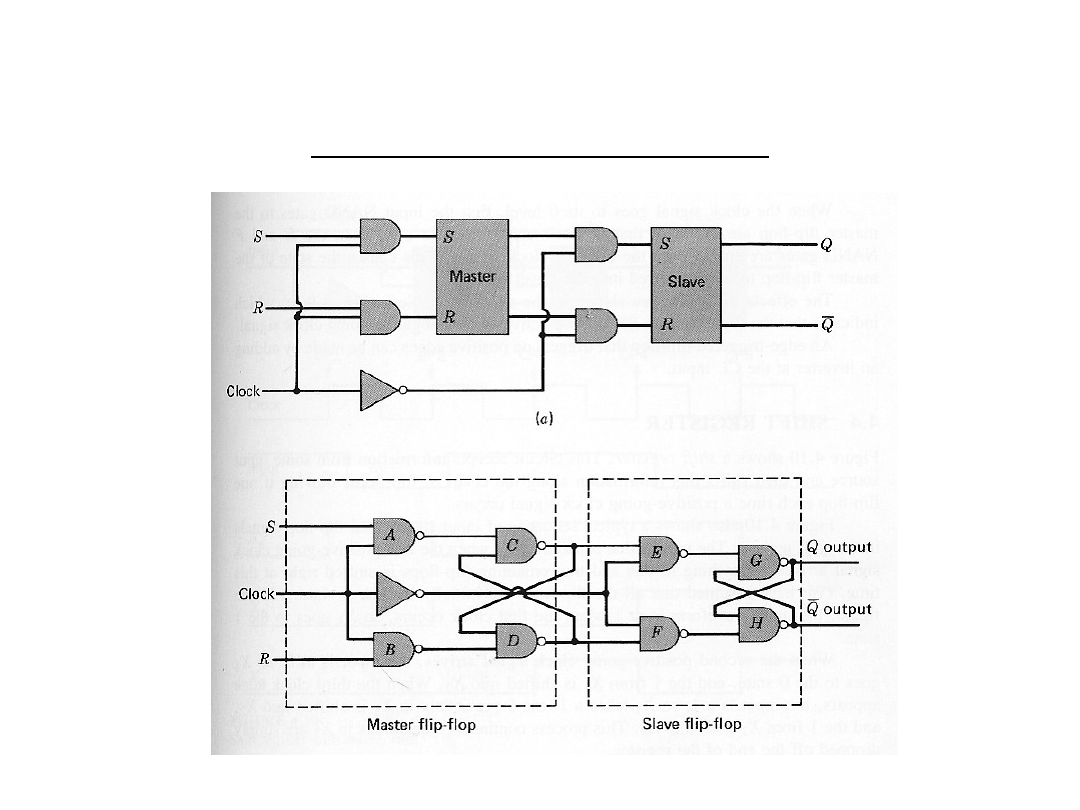

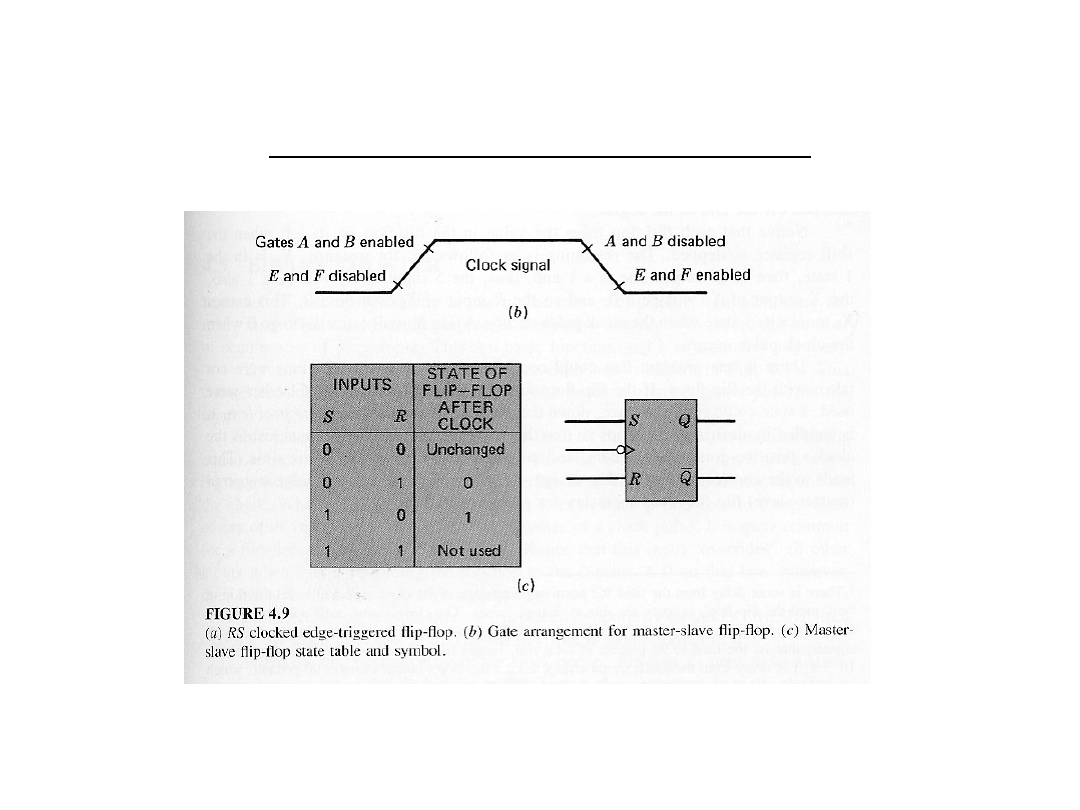

Master-Slave Flip-Flop

Master-Slave Flip-Flop ć.d.

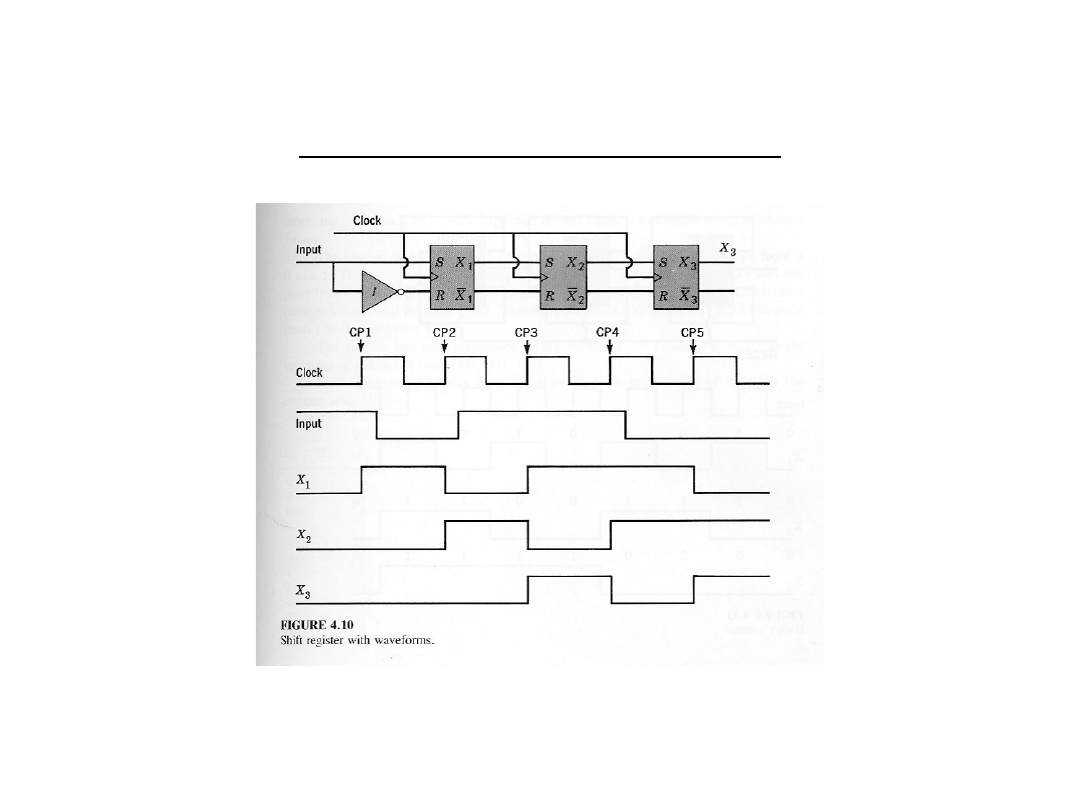

Przykład: Shift Register

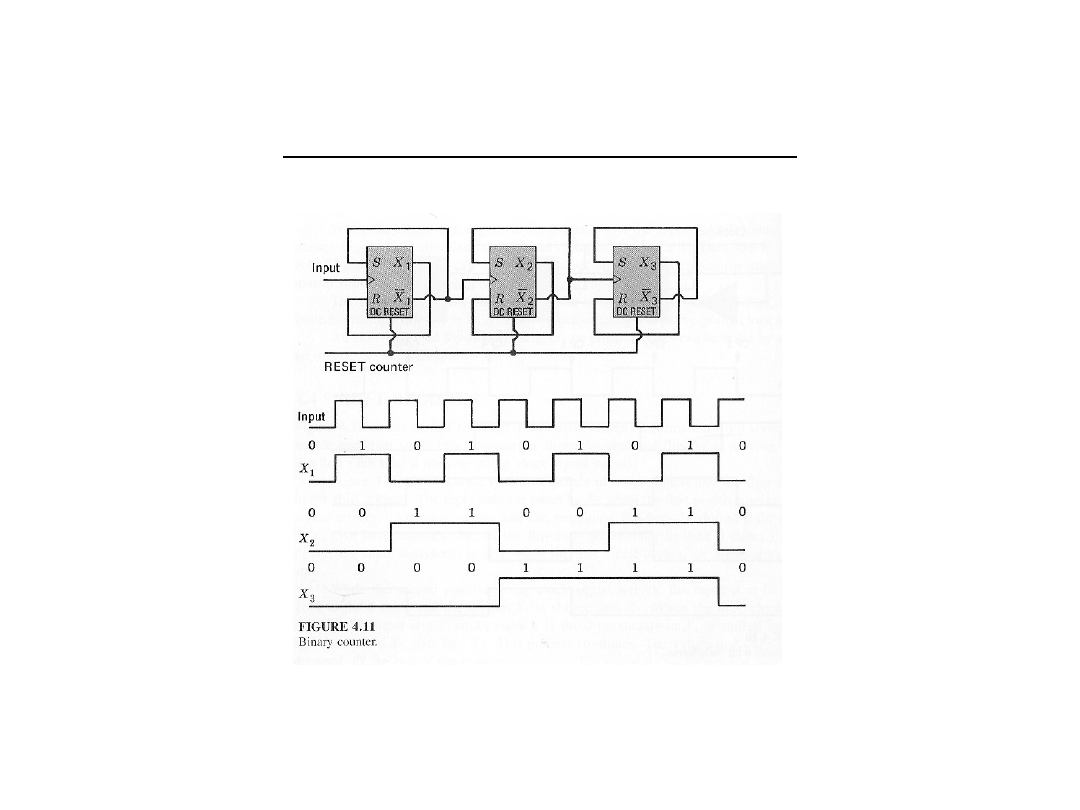

Przykład: Licznik binarny

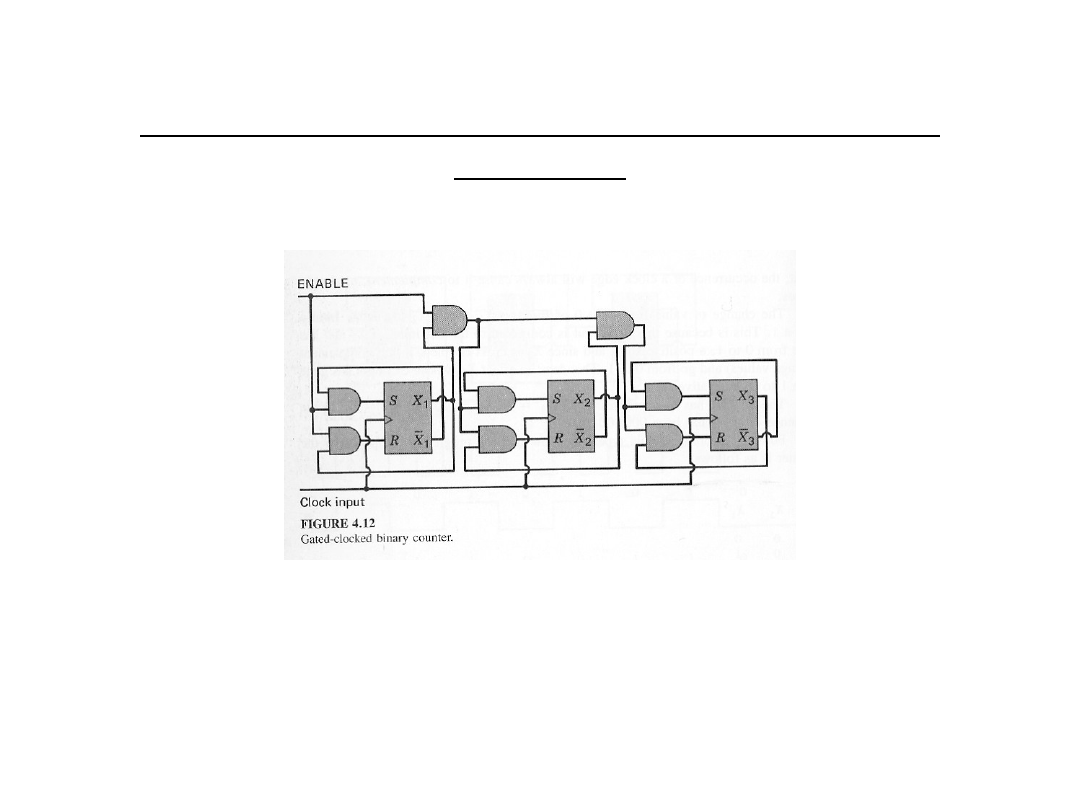

Przykład: Licznik binarny kontrolowany

zegarem

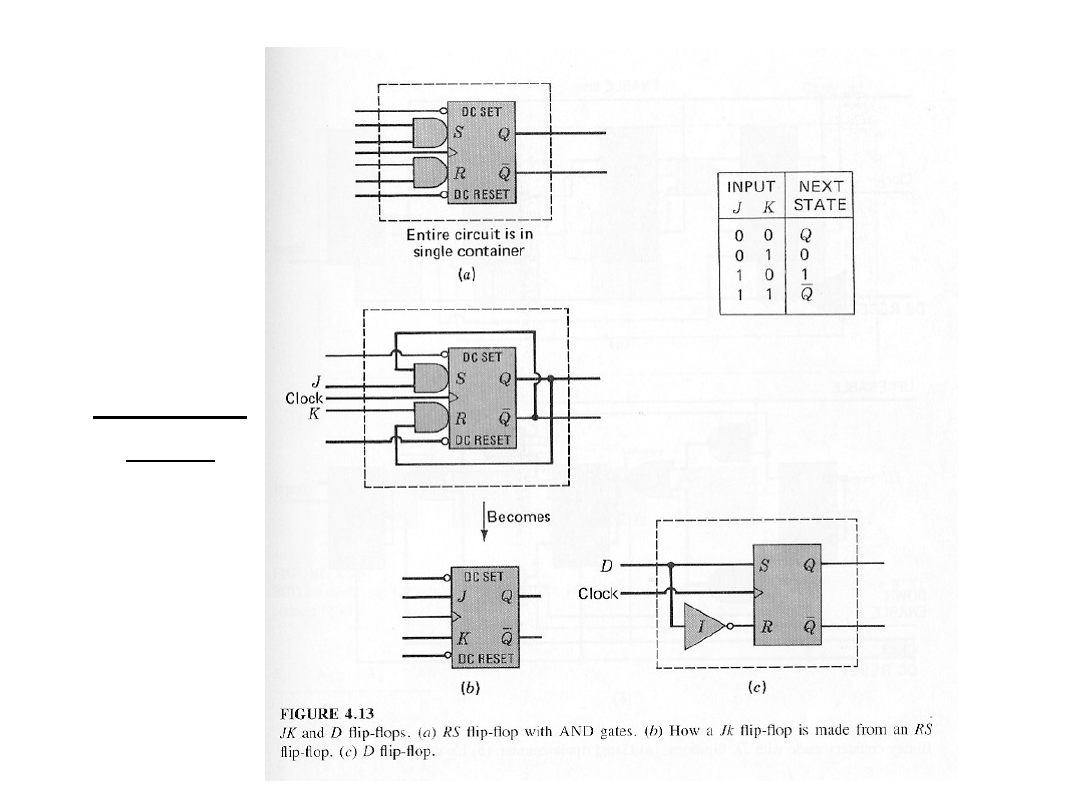

JK Flip-

Flop

Przykład

zastosowa

nia JK

Flip-

Flop’ów:

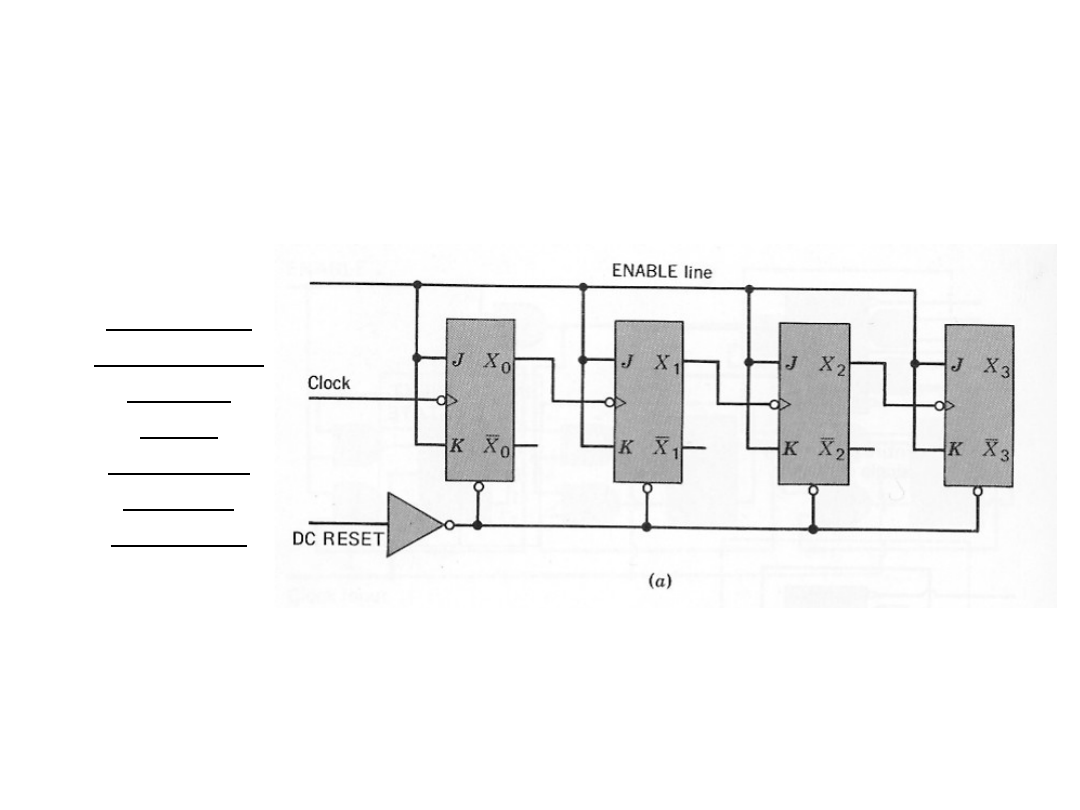

Binary

Counter

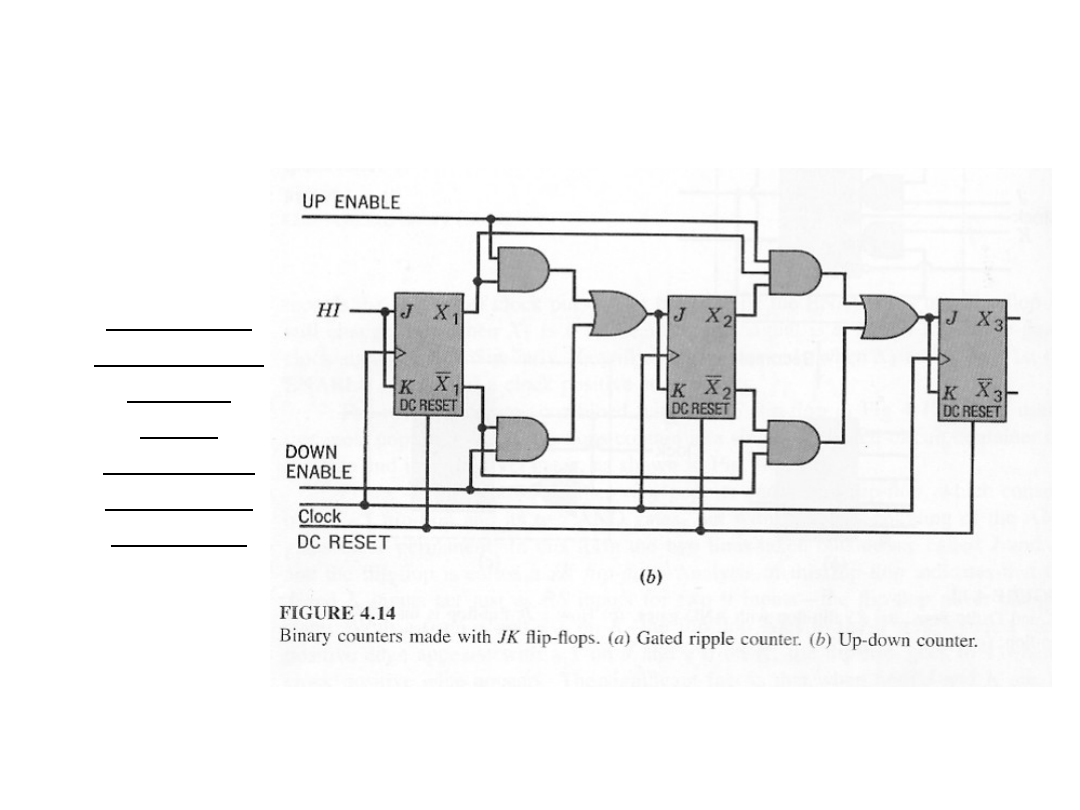

Przykład

zastosowa

nia JK

Flip-

Flop’ów:

Up-down

Counter

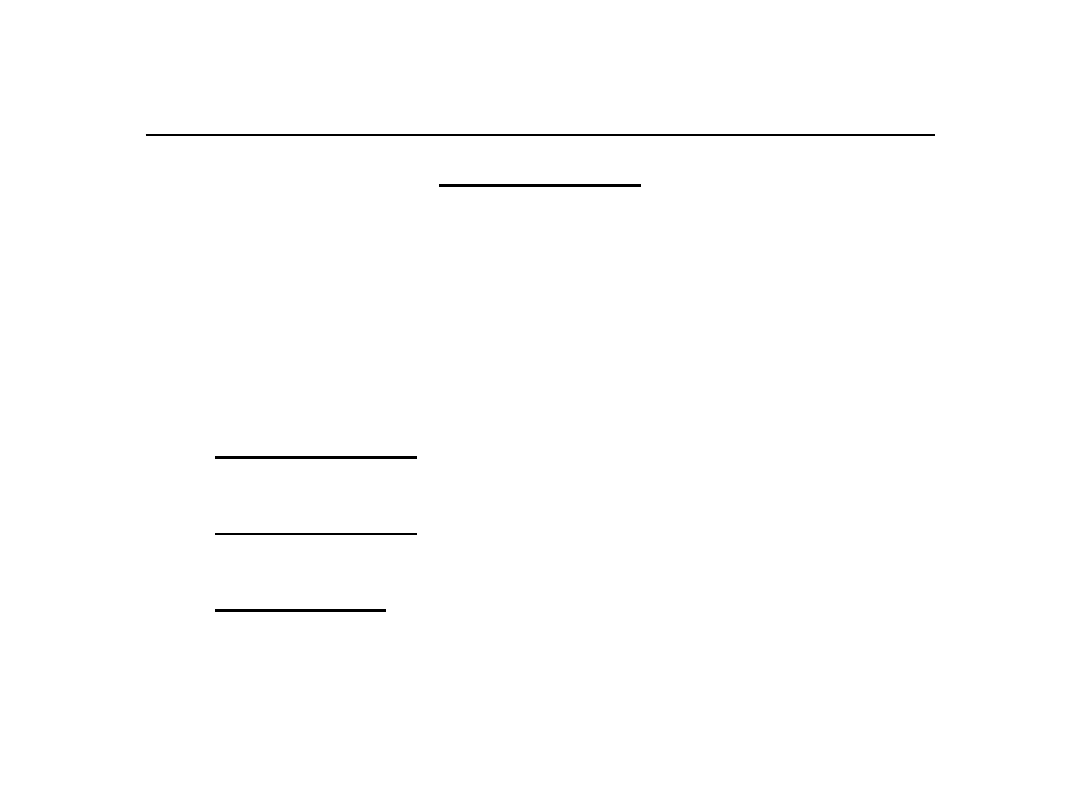

Kodowanie dwójkowo-dziesiętne

Cyfra

dziesiętna Kod 8-4-2-

1

Kod 2-4-2-

1

Kod z

nadmiare

m 3

0

0 0 0 0

0 0 0 0

0 0 1 1

1

0 0 0 1

0 0 0 1

0 1 0 0

2

0 0 1 0

0 0 1 0

0 1 0 1

3

0 0 1 1

0 0 1 1

0 1 1 0

4

0 1 0 0

0 1 0 0

0 1 1 1

5

0 1 0 1

1 0 1 1

1 0 0 0

6

0 1 1 0

1 1 0 0

1 0 0 1

7

0 1 1 1

1 1 0 1

1 0 1 0

8

1 0 0 0

1 1 1 0

1 0 1 1

9

1 0 0 1

1 1 1 1

1 1 0 0

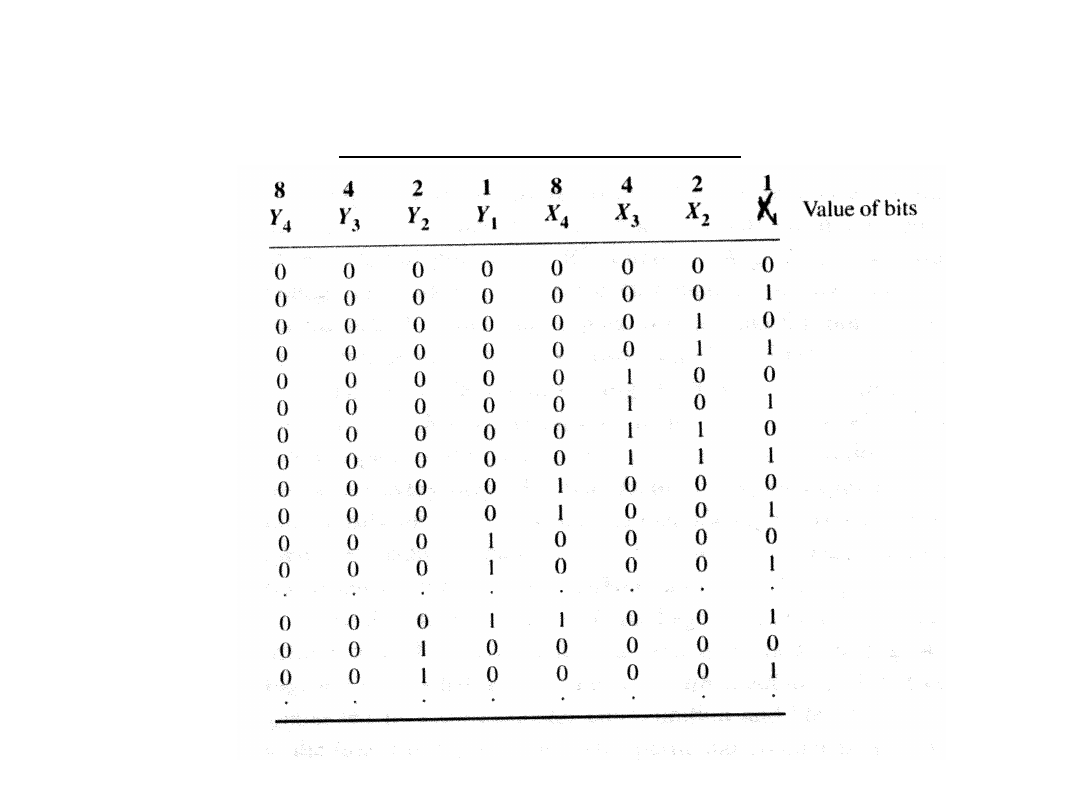

Kodowanie dwójkowo-dziesiętne -

przykład

Zakodowanie liczby 1897 w

różnych systemach:

Kod 8421: 0001 1000 1001 0111

Kod 2421: 0001 1110 1111 1101

Kod +3: 0100 1011 1100 1010

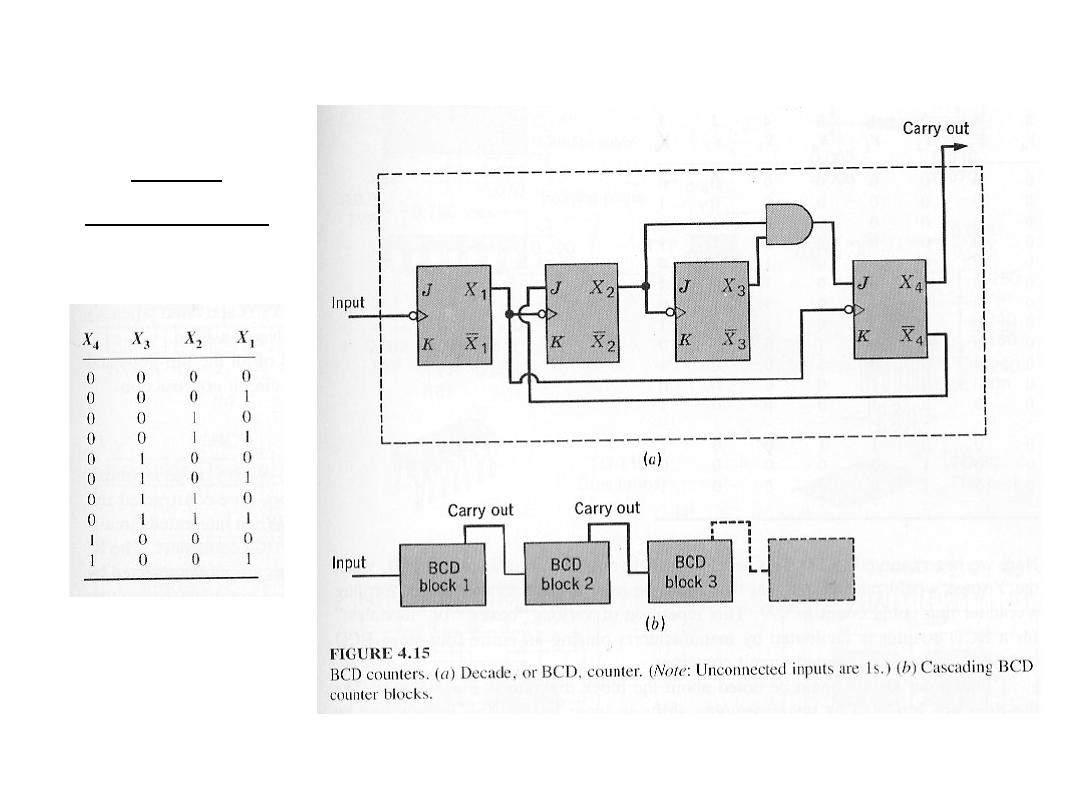

BCD

Counters

BCD Counters – c.d.

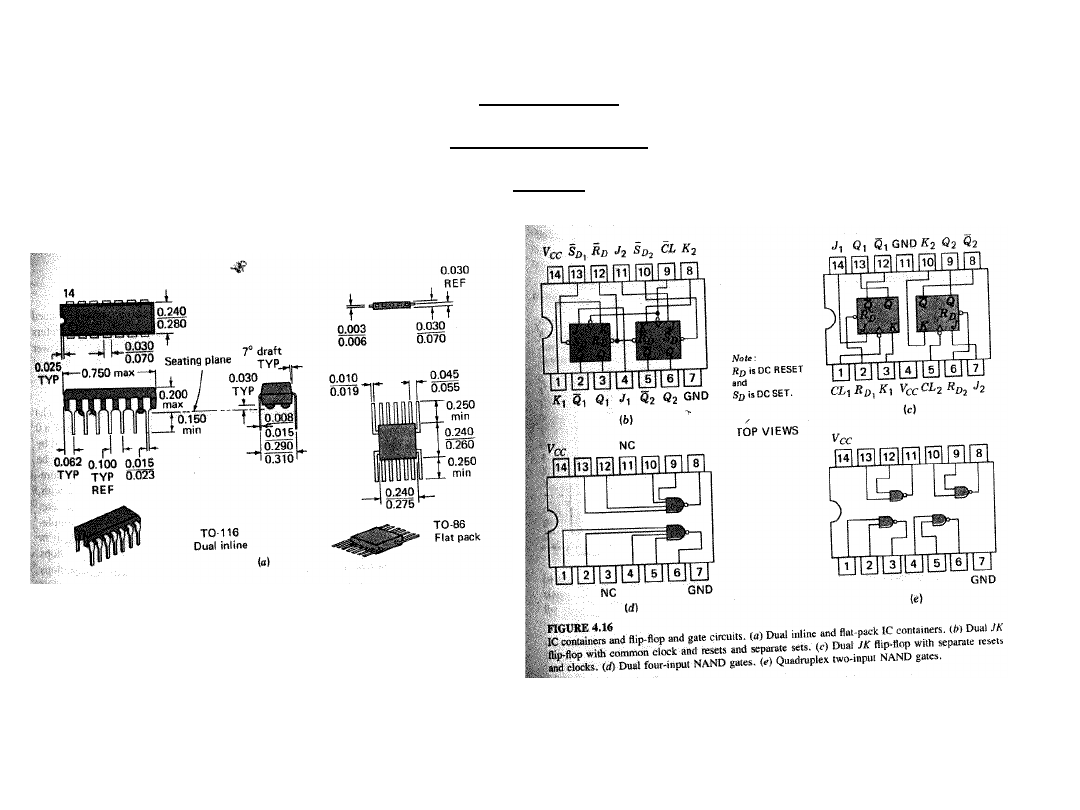

Układy

zintegrow

ane

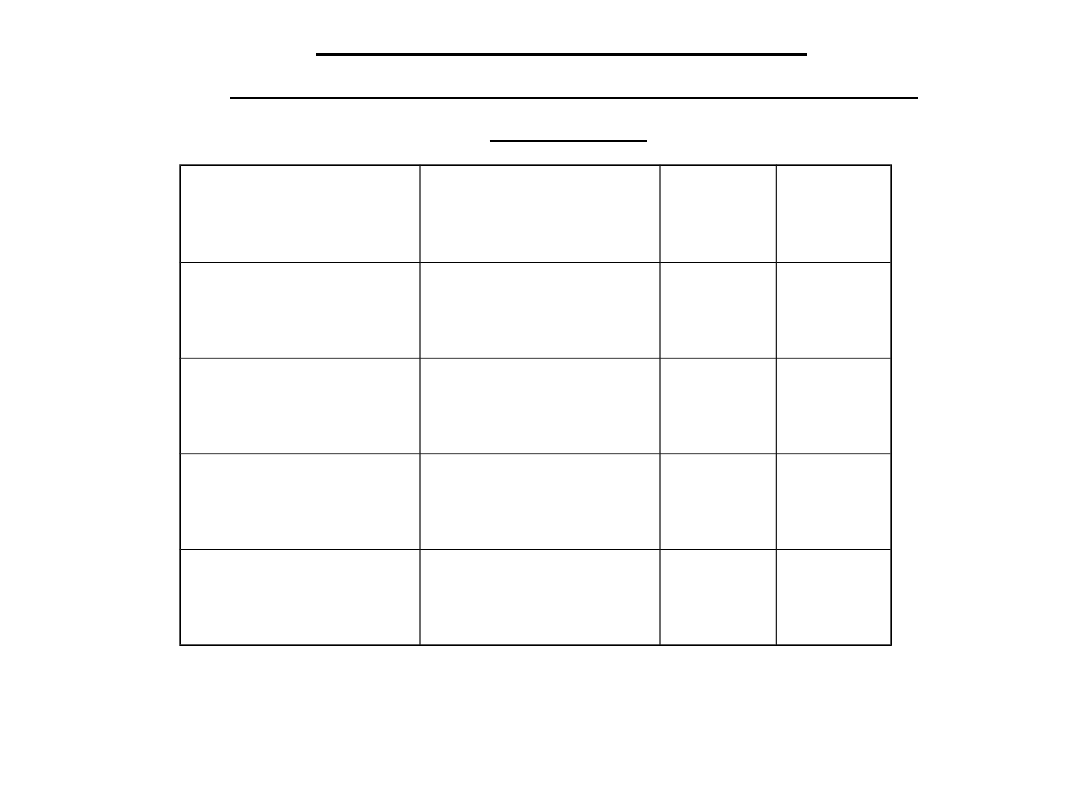

Projektowanie liczników:

zasady sterowania przerzutnikiem

typu RS

Stan

bieżący

Następny

stan

S

R

0

0

0

d

1

1

d

0

0

1

1

0

1

0

0

1

Projektowanie liczników: zadanie (wersja

RS)

Zaprojektować licznik zbudowany z RS

Flip-Flopów

realizujący sekwencję wskazań:

A

B

C

0

0

0

1

1

1

1

0

1

1

1

0

0

0

1

0

1

0

0

0

0

1

1

1

1

0

1

...

...

...

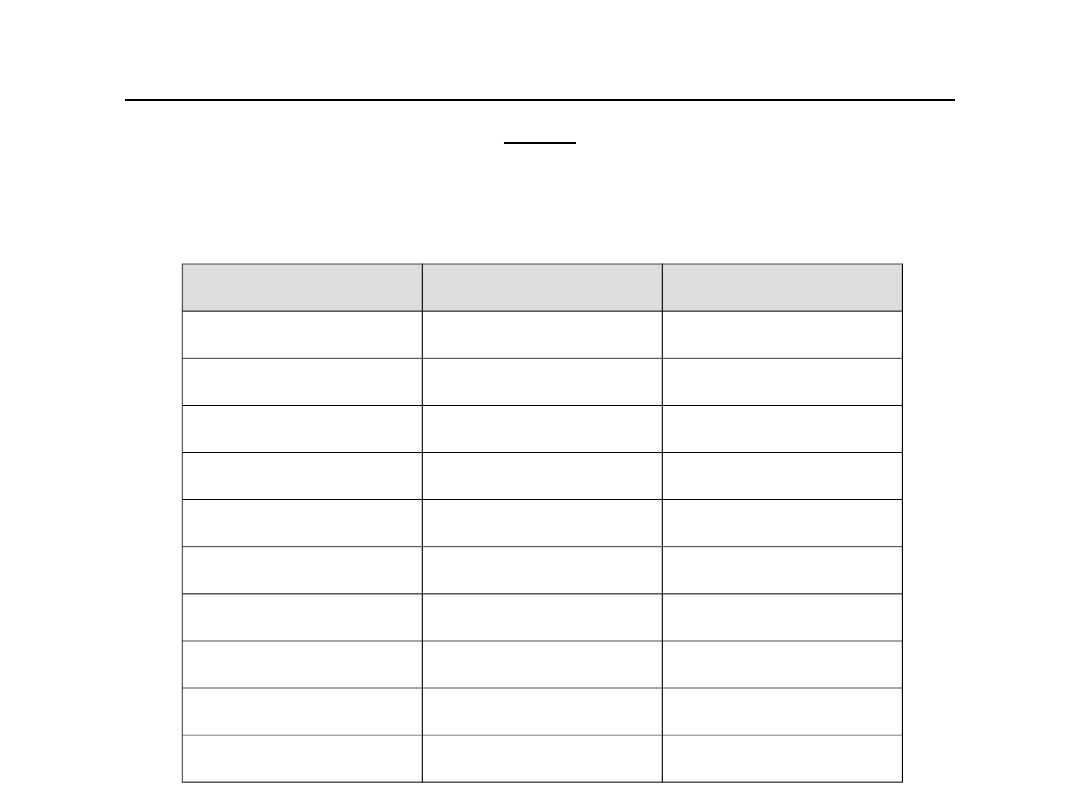

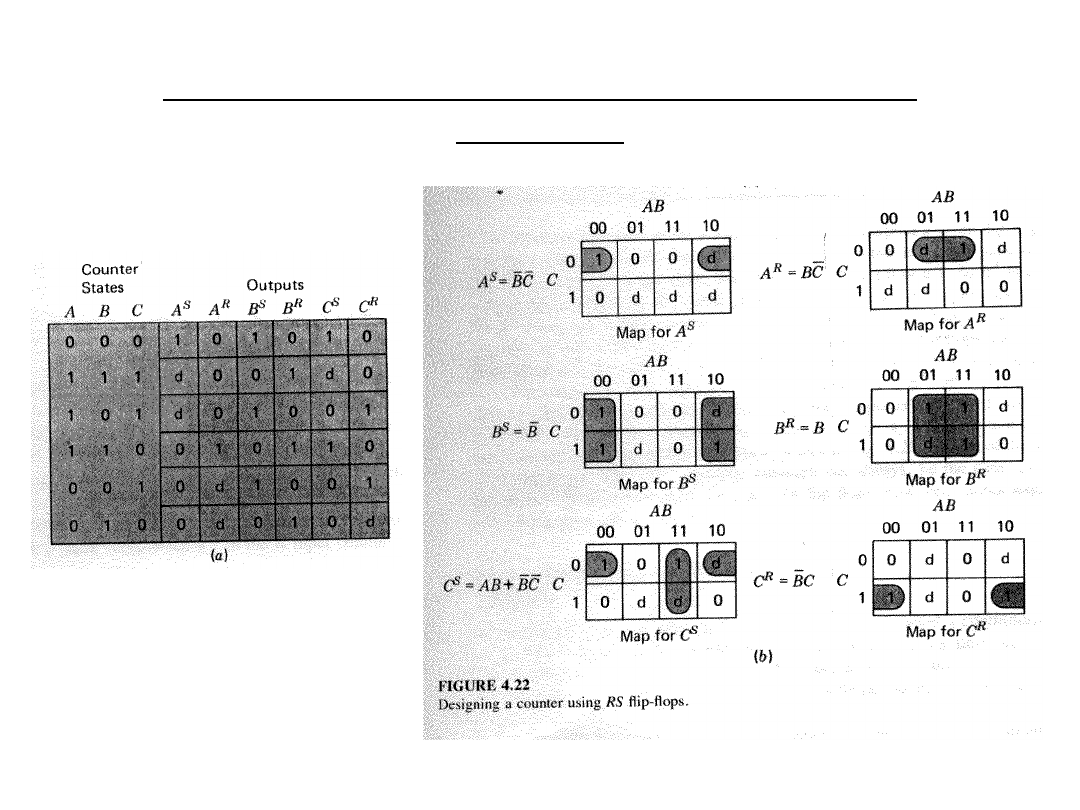

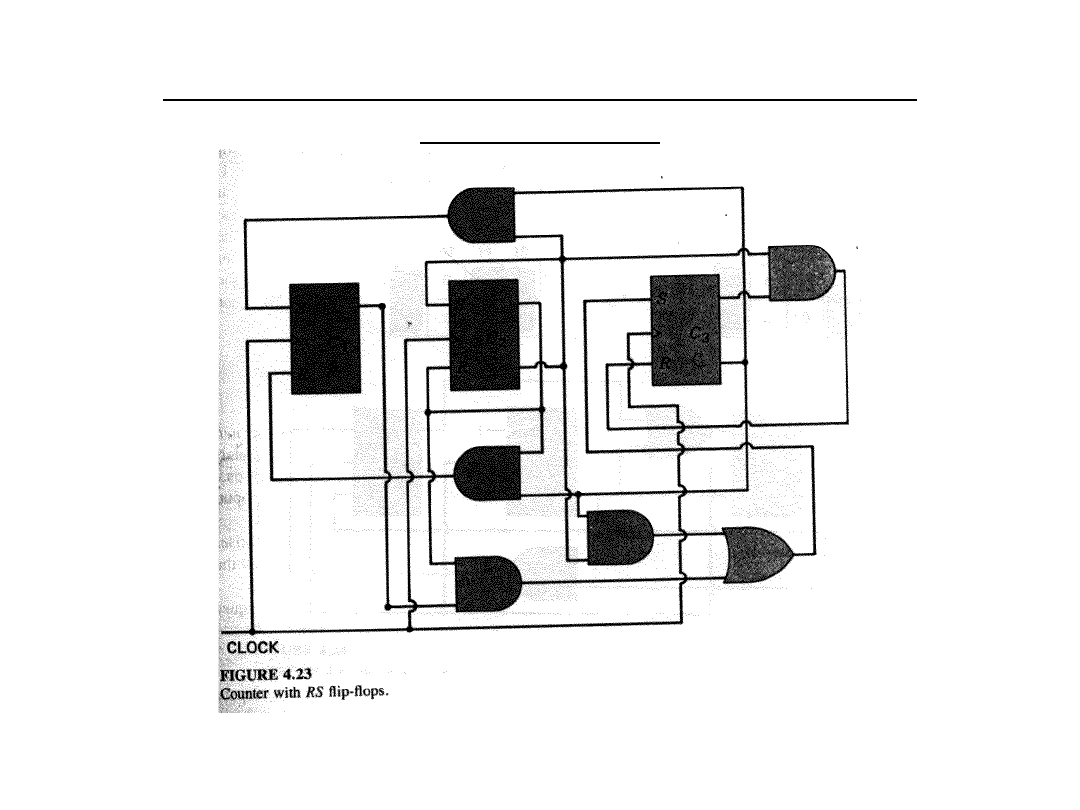

Projektowanie liczników: rozwiązanie

zadania

Projektowanie liczników: rozwiązanie

zadania ć.d.

A

S

R

B

S

R

S

R

C

Projektowanie liczników:

zasady sterowania przerzutnikiem

typu JK

Stan

bieżący

Następny

stan

J

K

0

0

0

d

1

1

d

0

0

1

1

d

1

0

d

1

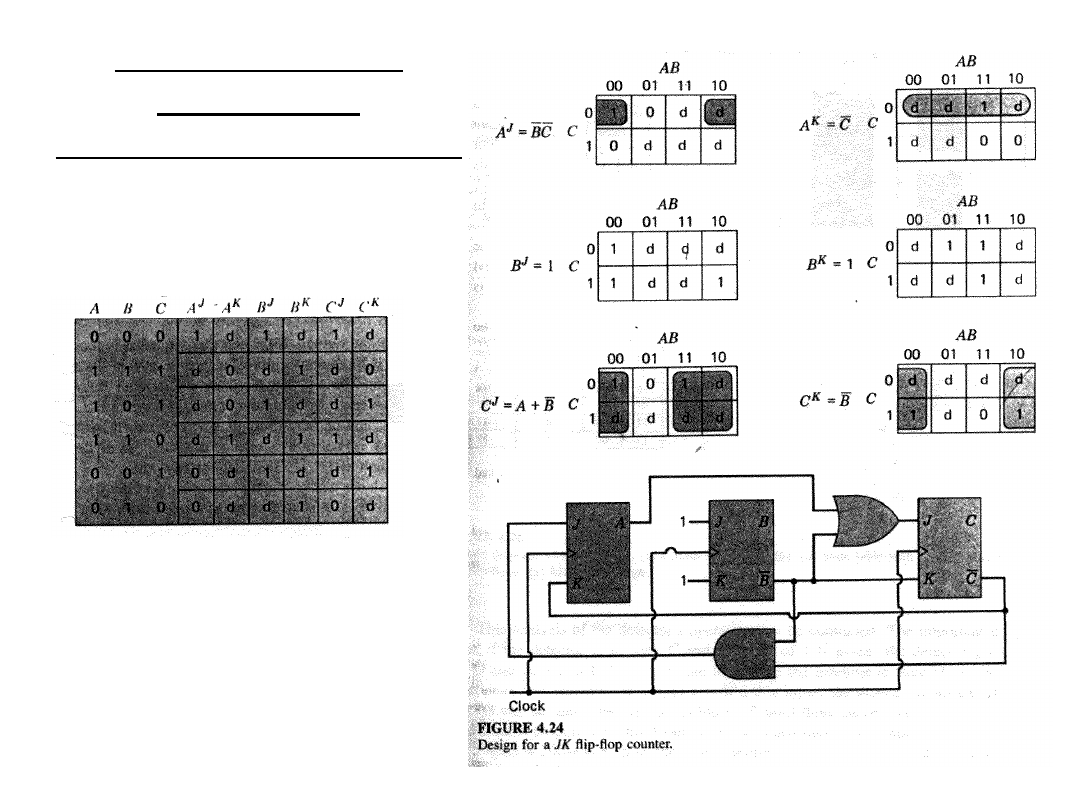

Projektowanie liczników: zadanie (wersja

JK)

Zaprojektować licznik zbudowany z JK

Flip-Flopów

realizujący sekwencję wskazań:

A

B

C

0

0

0

1

1

1

1

0

1

1

1

0

0

0

1

0

1

0

0

0

0

1

1

1

1

0

1

...

...

...

Projektowanie

liczników:

rozwiązanie zadania

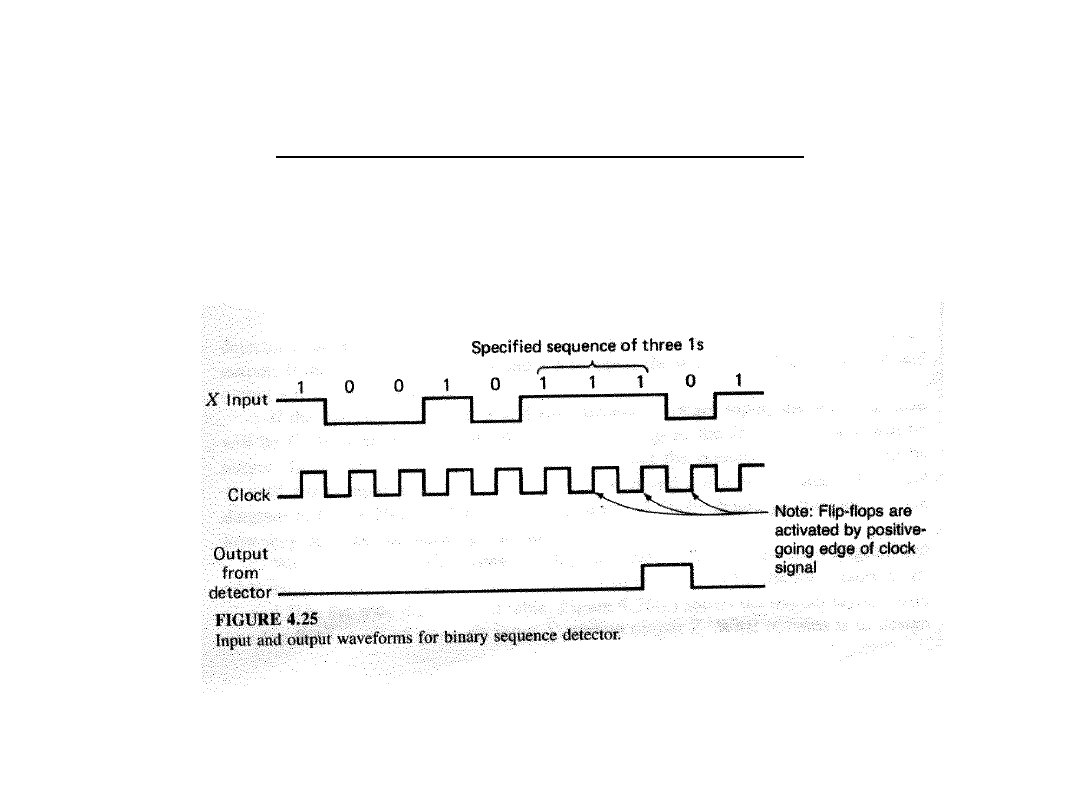

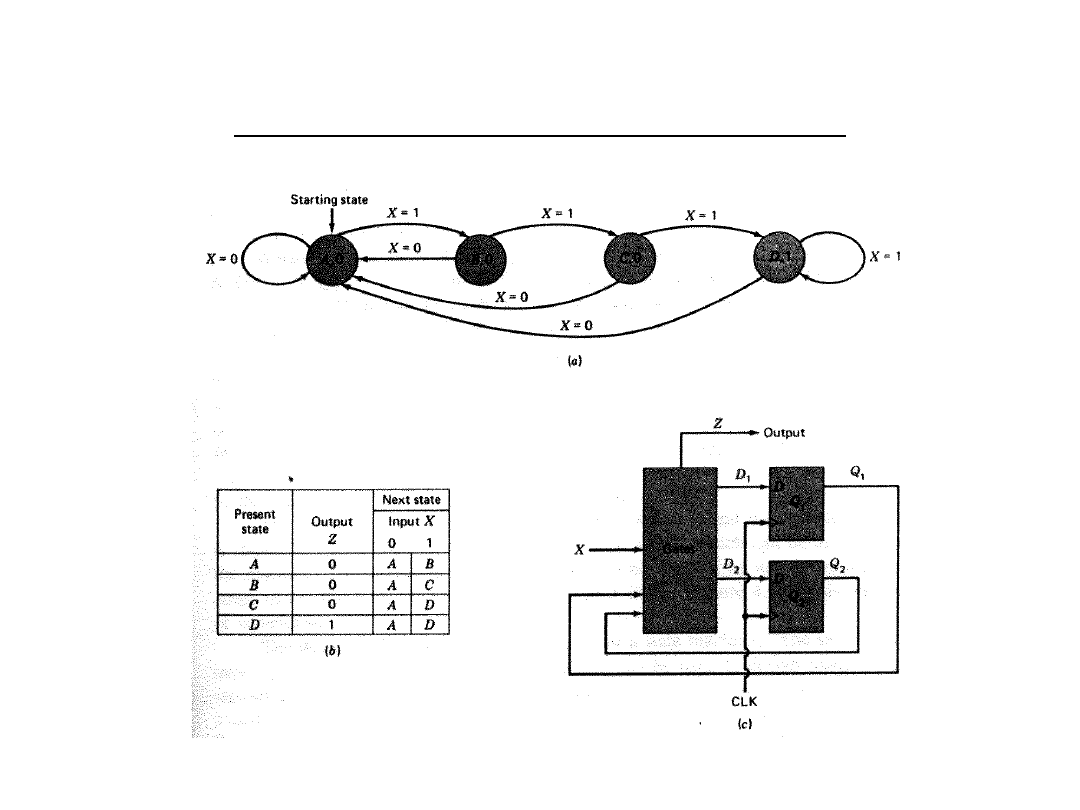

Binary Sequence Detector

Binary Sequence Detector c.d.

Gate

s

A ,0

B ,0

C ,0

D ,1

Q

1

Q

2

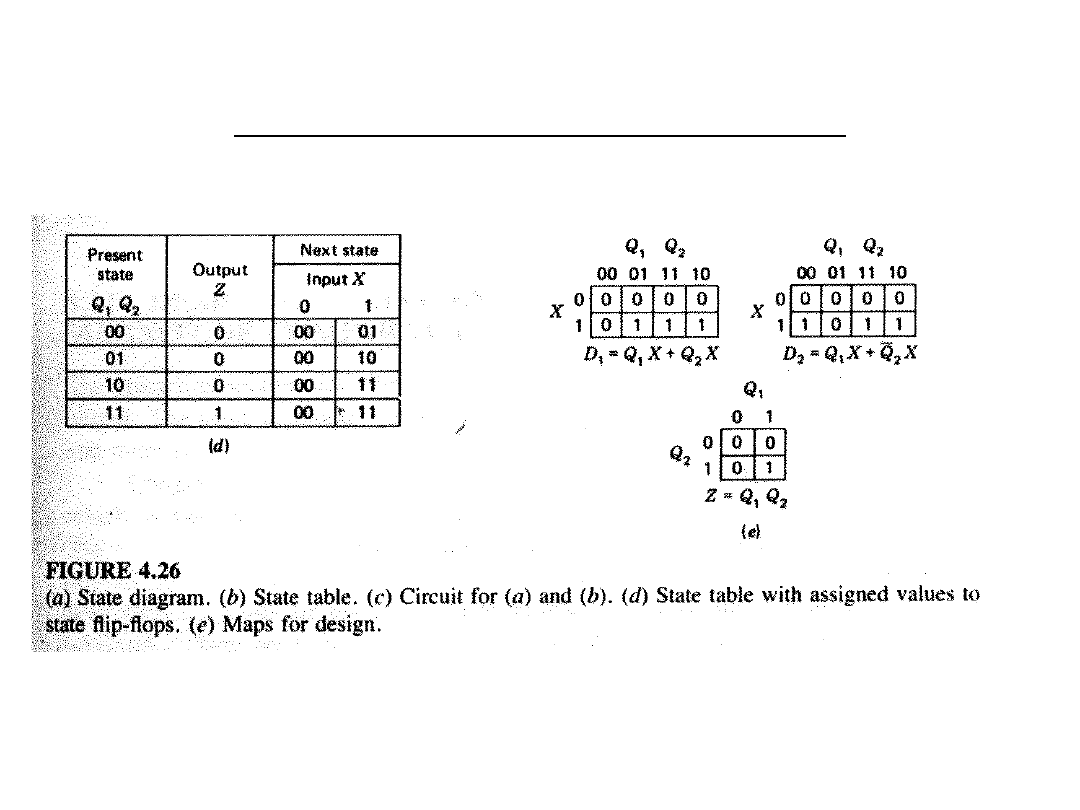

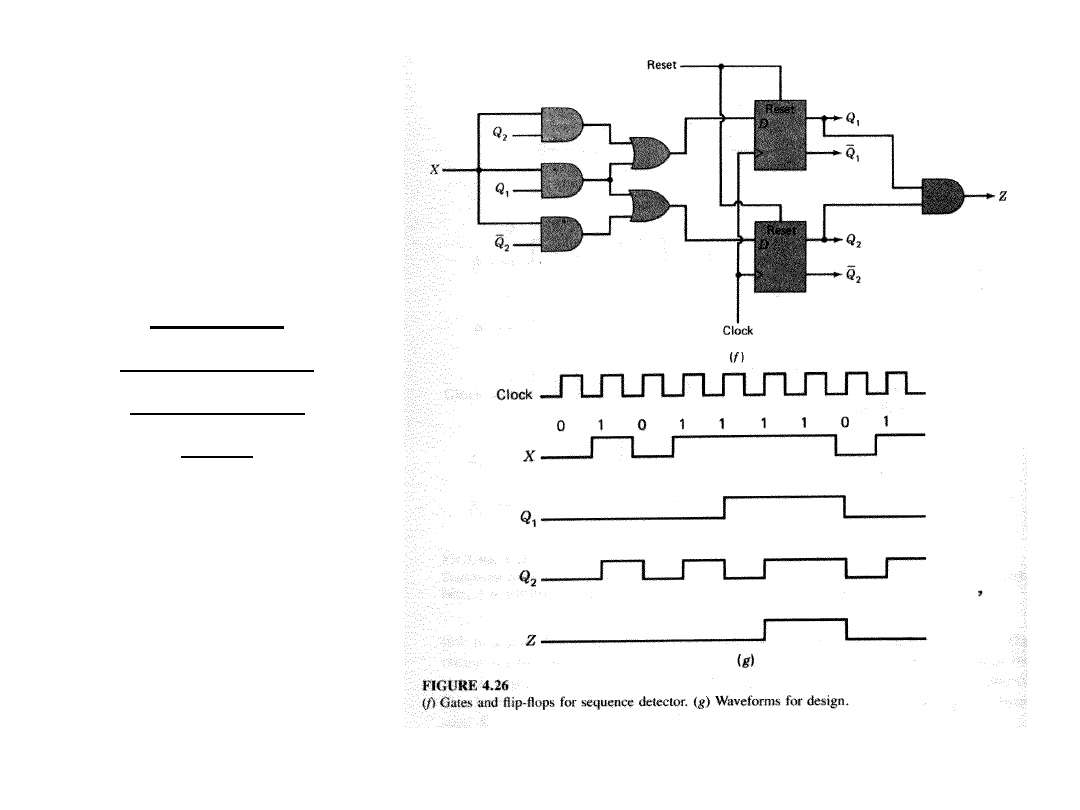

Binary Sequence Detector c.d.

Binary

Sequence

Detector

c.d.

D

D

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

Wyszukiwarka

Podobne podstrony:

Flipflop Timer

Transistor Flipflop

więcej podobnych podstron