RX SIGNAL PATH

TX SIGNAL PATH

MAIN VCO SIGNAL PATH

TUNING VOLTAGES

REFERENCE CLOCK

Orderable Part

Non - Orderable Part

925-960MHz

FL472

U432

SW_VCC

to WhiteCap

from WhiteCap

800MHz

RX

LOCAL

OSCILLATOR

CR249

CR248

VRef

A9

D8

Osc.

circuty

discrete

U200

MAGIC

Q203

PLL

C8,H7;B3

400 MHz

Q490

B

C

C

G1

S

W

IT

C

H

S

W

IT

C

H

C2

V1_SW

RF_V1

C8

SF_OUT

C1

SPI

TX

MODULATION

A1

A3

STEP

ATT.

DEMODULATION

SPI

RX

SPI

INTER

FACE

J2

G7

G5

H4

J3

( SDTX ) BDX

( TX_CLK ) BCLKX

( SPI_DATA ) DX1

( SPI_CLK ) MOSPI_CLK1

( CE ) MQSPI_CS1

F7

G9

G8

( SCLK_OUT ) BCLKR

( SDFS ) BFSR

( SDRX ) BDR

RX_ACQ

TX_KEY

DM_CS

CLK_SELCT

26MHz

J7

J9

J6

MAGIC_13MHz

Startup

PHASE

DET

Ref.

1 /2

MUX

LOGIC

CONTROL

H8

J4

H5

DCS

S

U

P

E

R

F

IL

T

E

R

R

E

G

.

GSM / DCS SELECT CIRCUIT

from WhiteCap

to WhiteCap

from WhiteCap

1805-1880MHz

13MHz

A7

C7

C6

F1

H1

H2

LOGIC

CONTROL

Y200

G6

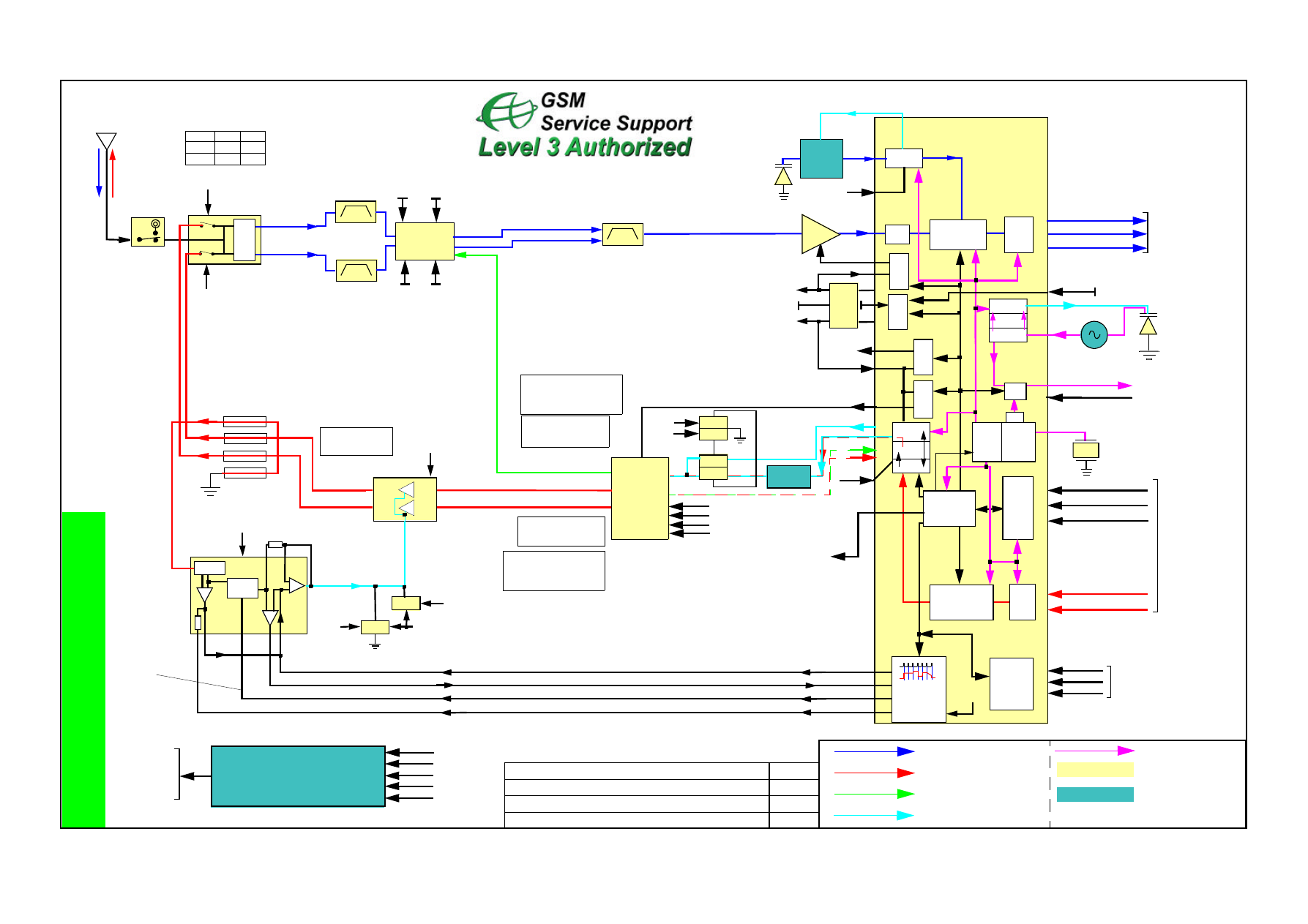

GSM SERVICE SUPPORT GROUP

12.07.01

LEVEL 3 RF Block Diagram

Rev. 1.0

T192 ( Barracuda )

Ralf Lorenzen, Michael Hansen, Ray Collins

Page1

B1

F2

REF. OSC.

26 MHz

Prog.

Divider

200KHz

REF.

Divider

200KHz

AFC

RXI

RXQ

TXI

TXQ

PLL

DET

PHASE

Divider

EGSM: 880-915Mhz

DCS: 1710-1785MHz

EGSM: 880-915Mhz

DCS: 1710-1785MHz

EGSM: 1325 - 1360Mhz

DCS: 1405 - 1480MHz

EGSM: CH 37 -- 1342,4Mhz

DCS: CH 700 -- 1442,8MHz

RX VCO MID CHANNELS

GSM: CH 62 -- 1347,4 MHz

RX VCO FRQ. RANGE

EGSM: CH 37 -- 897,4Mhz

DCS: CH 700 -- 1747,8MHz

TX VCO MID CHANNELS

GSM: CH 62 -- 902,4MHz

TX VCO FRQ. RANGE

TX FRQ. RANGE

RF_V2

2,3,5,

RVCO

10

RX_EN

DCS_SEL

16

24

7

FL490

3

4

1

2

1

2

2

5

5

GSM

U253

RX / TX

1

11

GSM_TX_VCO

12

DCS_SEL

C4

GP02

DCS_TX_VCO

GSM_TX_VCO

PAC_275

VC1

VC4

DCS_SEL

FRONTEND IC

FL480

A10

J100

VC4

5

Mech. Ant Switch

VC1

VC2

7

9

GSM

DCS

11

1

1

2

VC1

GSM

DCS

0

1

0

1

U10 / TX

RX

Filter

VC1

VC4

D101

T

1

9

2

(

B

a

rr

a

cu

d

a

)

6,20

PRE_IN

U506 PA

7

6

11

10

3,14

PAC_275

RF_IN

U501

PAC

VCTRL

4

5

9 8

INTEGR.

SAT.

DET.

COMP.

BUFFER

AMP

+

-

+

-

+ -

1

RF DET

Logic 1 at low power

Logig 0 at high power

(Gain 1or 3)

TX_KEY_OUT

SAT_DETECT

AOC_DRIVE

DETECT_SW

B6

C5

A5

B4

TX_KEY_OUT

SAT_DETECT

AOC_DRIVE

DETECT_SW

PA

CONTROL

GPRS_TX

GSM_TX_RF_OUT

DCS_TX_RF_OUT

DCS_PA_OUT

GSM_PA_OUT

14

16

4

2

PA_B+

14

10

12

Q505

Q201

B+

S1

S2

G1

RF_V1

RF_V2

D2

D1

2,75V

2,75V

4

5

2

6

1

3

B+

G2

6,8

PAC_275

DM_CS

Mute Switch

Q506

RF_V2

Bias Switch

if DM_CS is low

VCTRL is pulled to GND

VCO

DCS_TX_VCO

DCS_SEL

TX_EN

13

2

4

4

5

2

6

1

3

Q312

Q312

RX_LO_OUT

6

TX LOOP

FILTER

4

6

2

1

3

Q313

Q313

RVCO

TX_EN

Inverter

5

Iso.

Switch

RVCO

F9

RVCO

DCS_SEL

RF_V2

TX_EN

DM_CS

RX SIGNAL PATH

TX SIGNAL PATH

MAIN VCO SIGNAL PATH

TUNING VOLTAGES

REFERENCE CLOCK

Orderable Part

Non - Orderable Part

U900

U702

U701

G_CAP2

SRAM

EEPROM

SPKR

MIC

DATA BUS

ADDRESS BUS

H6 H7 K9

H9

SENSE

CNTL.

MAN_TEST_AD

BATT_ID

A1

B3

REAL TIME

CLOCK

Y

9

0

0

A7 B7

3

2

.7

6

8

K

H

z

S

P

R

-

S

P

R

+

A

L

R

T

O

U

T

ALRT_VCC

REG.

V2

REG.

V3

REG.

VBOOST1

REG.

L901

B+

V_BOOST1

V1

V2

V3

VREF

REG.

VREF

2.775V, for WhiteCap logic outputs, RAM, FLASH, EEPROM

1,8V, for WhiteCap

VSIM

REG.

VSIM1

V1

5.0V, for DSC Bus, Negative Voltage Regulator

Internal GCap use only (VSIM1, LS_V1)

3.0 or 5.0V, for SIM Card Circuit

P

A

_

D

R

V

RESET

2.775V for Magic

K5 E10

B10

J5

C6

B5

G9

A6

C7

DSC_EN

UPLINK

DOWNLINK

RX_ACQ

RX_EN

TX_KEY

DM_CS

TX_EN

CLK_SELECT

RESET

M

A

G

IC

_

1

3

M

H

z

G

C

L

K

A1

C1

E2

E1

E3

E4

BKLT_EN

J902

GND

V2

DP_EN_L

RESET

DP_EN_L

HEAD_INT

KEYBOARD

KBR0 - KBR2

KBC0 - KBC3

ON_2

KBR0-KBR2

KBC0-KBC3

( Keyboard )

CLK

RESET

SIM_I/O

VSIM1

1,5

3

2

4

6

LEVEL

EXT_B+

DEEP SLEEP

E8

( WhiteCap )

( GCAP2 )

ON2

C8

RSTO

CLKO

SIM_TX

SIM_RX

K7

G6

K10

RSTO

CLKO

SIM_TX

SIM_RX

H8

J902

SIM

Con.

SHIFT

( SDTX ) BDX

( TX_CLK ) BCLKX

from / to MAGIC

( SCLK_OUT ) BCLKR

( SDFS ) BFSR

( SDRX ) BDR

STBY_DL

CIRCUIT

V1

V1_SW

U700

WHITE_CAP

K2

SPI

INTERFACE

TIMER

SPI

INTERFACE

P4

H10

K3

N3

A11

H2, H1, H3

J5, J3, J2

M

E

M

O

R

Y

I

N

T

E

R

F

A

C

E

E9

E7

F3

B5

SIM

INTER

FACE

CTM

MODULE

DSC

SERIAL

INTER

FACE

DSP

CTM

CPU

B6

B3

B4

D4

A3

F1

J2

ALRT

Q904

J9

BKLT_EN

D900

F6

J8

J7

A

U

D

IO

S

P

I

G

C

A

P

S

P

I

D2

C3

EPROM

Display Con.

15-22

D7 - D0

1-6,13

14,26

24

25

R_W

4

23

A0

BACKLIGHT

V2

SR_VCC

CE0

CE1

CE2

CE3

R_W

( SPI_DATA ) DX1

( SPI_CLK ) MOSPI_CLK1

( CE ) MQSPI_CS1

( MAGIC SPI )

M7

K7

N8

D6, E1

B2

A1

G5

A4, E1, F5

D7

F8

C9

E10

B11

D9

B9

STBY_DL

G4

C4

RESET

B4

G

C

A

P

_

C

L

K

1

3

M

H

z

B7

F5

1

EXT_B+

B+

H3

Audio

Codec

Interface

SPI

INTERFACE

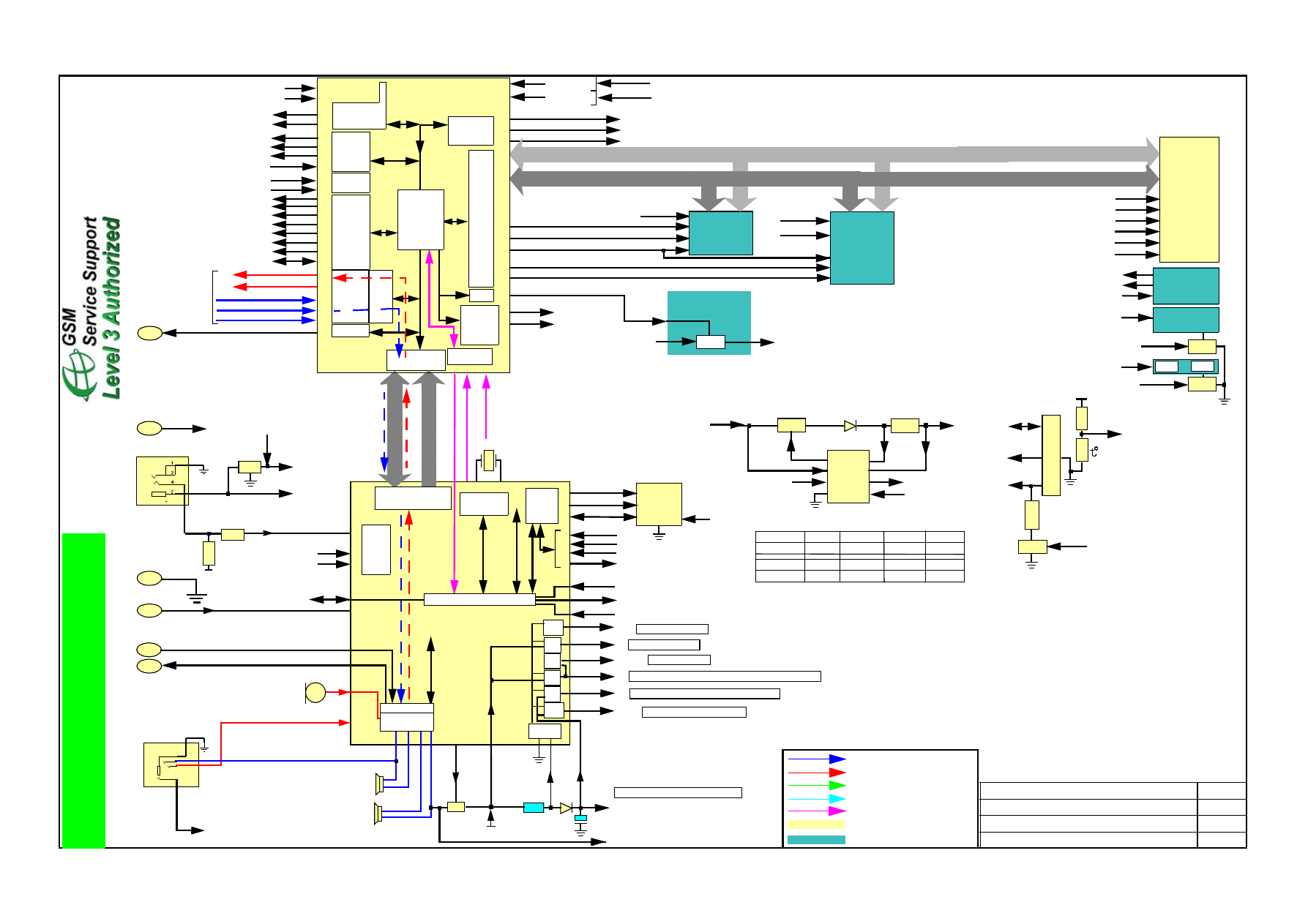

GSM SERVICE SUPPORT GROUP

12.07.01

LEVEL 3 AL Block Diagram

Rev. 1.0

T192 ( Barracuda )

Ralf Lorenzen, Michael Hansen, Ray Collins

Page2

G5

ON2

Q913

TP4

J903

CHARGER JACK

V2

TP5

TP3

TP6

GND

TP1

AUX_MIC

MIC

V2

BATT_THERM

L2

C956

F7

3

4

1,2,5,6

ALRT_VCC

(Magic)

15

-5V

E1

SR_VCC

2.775V, for SRAM

V2

V3

VDDS

VCC_MEMIF

VDD

VCCA

G12

A9,A10, C5, M8, M11

C14, F10, K13, P13

C4, H4, K5

B3

ALRT_VCC

U903

D902

Q900

COVIC

TRKL_SET

PWR_ON

ENABLE

R923

2

3

4

5

6

7

8

ISENSE

D10

PWR_ON

L7

ENABLE

TRKL_SET

P6

CHARGER

M901

BATTERY

CONN.

B+

R

9

4

1

V2

R

T

9

0

0

BATT_THERM_AD

ENABLE

TRKL_SET

Full Rate High Trickel Low Trikel

Off

Mode

Current

300mA

100mA

40mA

<1mA

Low

High

Low

High

Low

High

Low

High

( GCAP2 )

( White Cap )

R931

R

6

0

5

KEYPAD

INTERFACE

DISPLAY

Logic Control

TP2

B+

CHARGE

T

1

9

2

(

B

a

rr

a

cu

d

a

)

LS900

Q902

BATT_ID

3,4

1,6

2,5

GND

Q914

R

9

4

4

BATT_THERM

( White Cap )

( GCAP2 )

A3

BATT_THERM_AD

UART

EXTB+_DET

Q903

EXTB+_DET

M3

ALRT_VCC

( GCAP2 )

Q901

VIB_EN

VIB 1

VIB 2

J900

A10

CON.

J504

IRQ_2

HEADSET

1

3

4

2

Wyszukiwarka

Podobne podstrony:

block diagram

ALAN42MULTI block diagram

20060919095901218 09 Block Diagram

Block Diagram

System Block Diagram

ZEUS PRO BLOCK DIAGRAM

block diagram

Block Diagram

Block Diagram 2

POG IF Block Diagram

Thomson MT5655 BLOCK DIAGRAM

Block Diagram W510 L3 C A3 V1 0 Block Diagrams

Block Diagram V9POIFBlDi V975 L3 2[1] 0 050131145018

Block Diagram

Block Diagram

Block Diagram

więcej podobnych podstron