Servive, Engineering & Optimization

2005.09.12

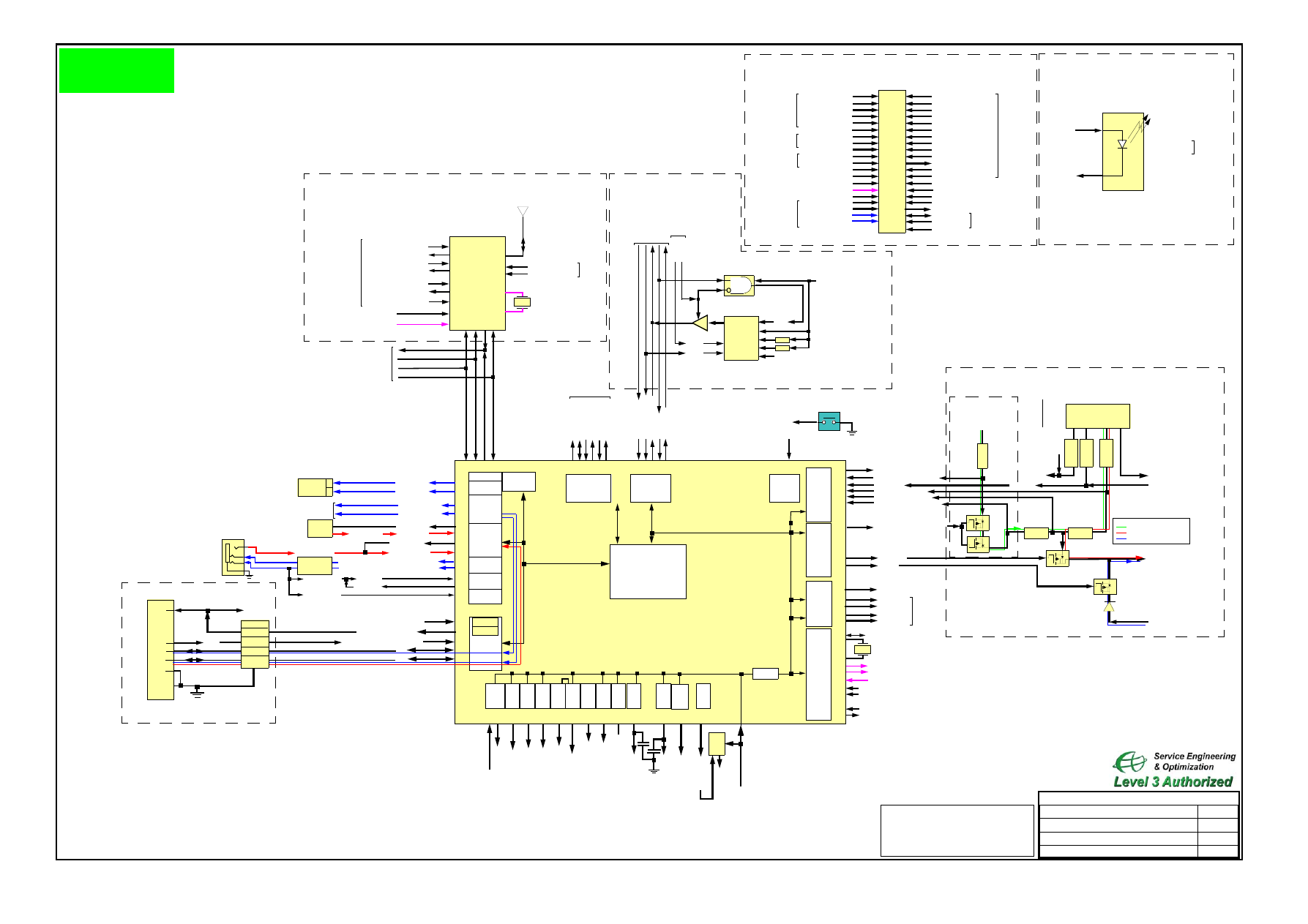

LEVEL 3 AL Block Diagram

Rev. 1.4

V360, V361,V365, V367

Alexander Buehler, Michael Mauderer

Page 1of 2

TCXO

Switch

Control

Circuit

U80

3

3

2

2

1

1

TX_EN

PA_BAND_SELECT

LNA

LNA

LNA

LNA

Quadrature

Polyphase

Quadrature

Mixer

Filter

Generator

FL100

Quard Saw Filter

6

3

High Band

1900MHz

4

1

and Matching

14

15

12

13

8

9

10

11

LP

LP

2

3

4

5

6

7

8

1

Low Band

900MHz

Low Band

850MHz

12

13

18

17

VRAMP

GSM850/GSM900 IN

DCS/PCS IN

DCS/PCS OUT

GSM850/

VRANGE

B+

7

3

2

4

5

6

1

9

11

GSM900 OUT

DC

Correct

22

21

20

19

27

25

26

14

15

16

GMSK/ EDGE Select

L

oop

Filter

RX/TX

Switch

ADC

13 bit

Sync

Filter

Anti

Drop

Anti

Alias

RX/TX

Switch

ADC

13 bit

Sync

Filter

Anti

Drop

Anti

Alias

Chanel

Filter

DAC

12 bit

LPF

Chanel

Filter

DAC

12 bit

LPF

Serial

Interface

Ser

ial

In

te

rface

GMSK

Modulator

EDGE

Modulator

EDGE

FIR

Filter

Anti

Alias

Pre-Distortion

Filter

Devider

PA Control

36

35

34

33

32

1

2

3

4

16

17

19

20

22

23

7

9

10

12

High Band

1800MHz

U50

PA

Antenna Switch

4

1

20

15

16

17

LD

T

O

RF

_

C

L

K

RF

_DA

T

A

R

F

_C

S

CT

RL

_

2

R

X

_A

NT

_E

N

P

A

_

B

A

ND_

SE

L

RF

_R

EG

9,10,32

31

30

29

28

VC

O

_

R

E

G

VTC

FIN

11

VT

U150

RF IC

ENR

CLKR

FSR

DRI

VRANGE

IIN

IBIN

QBIN

QIN

41

40

39

38

LDTO

TX

I

MS

MD

I

MC

LK

45

44

43

42

DA

C2

VR

AM

P

TX_EN

VCO2 (TX_HB)

VCO1 (TX_LB)

U200

RX/TX IC

from Neptune

22

ANTSW_1

Y806

26MHz

4

2

3

1800 MHz

1900 MHZ

850 MHz

900 MHz

900 MHz

850 MHz

1900 MHZ

1800 MHz

(Power Level control from U200)

(to U50)

(PA Disable function)

(High /Low Power Range control from U200)

(t

o U1

10)

(P

A P

o

wer

Contr

o

l)

J100

Mechanical

Antenna Switch

Output M

ixer

Digital TX

Interface

Reference

Devider

U51

Internal

Antenna

M1703

Control

Serial Data

Interface

23

RX_

AN

T_E

N

CNT

RL

_1

CNT

RL

_3

TX_

S

T

A

R

T

OSCA

OSCO

OSCM

OSCOM

48

31

30

O

sci

la

to

r and

C

loc

k G

en

er

at

o

r

(N

C)

5

2

(T

ra

ns

m

itt E

n

able)

MS

MDI

MCLK

RF_CLK

RF_DATA

RF_CS

(NC

)

( VCO Feedback )

(from U200)

(to U50)

( VCO Fine Tuning)

( VCO Coarse Tuning)

(100KHz)

14

15

DAC1

DAC2

(to U150)

(f

ro

m U200)

(to U200)

37

6

7

5

GPIO

CP

Phase Det.

(Main IC Control)

( Frontend Control

and Digital Modulation)

ADC

Voltage

Reg.

VCO_REG

RF_REG

PERIPH_REG

24

47

9,18

VCC’s from Atlas

A4

1Mbit RAM

DSP

DSP

UltraLite

104 MHz

DSP Peripherals

accelerator, encryption

Timer, Interupts

Shared Memory

MCU

52 MHz

ARM7

MCU

26 MHz

Oscillator

Memory

Memory

SIM

Interface

External

Interface

Memory

W7

Clock Generator

SPI

Power

NEPTUNE LTE

U800

G12

A13

N10

BaseBand

L1 Timer

V8

U6

U8

V7

W9

SPI

T9

W10

U9

(t

o U150)

(from U150)

(t

o U50)

UART / USB

Interface

Keypad

Interface

On

Off

6

4

1

SIM DIO

SIM RST

SIM CLK

SIM_PD

6

VSIM_REG

3

GND

Connector

J1350

SIM

1.8 or 3V

SIM Card

VSIM_EN

VBUCK

REF_REG

(VCC + 1.575V)

(VCC + 1,875V)

(from Atlas )

SIM_REG

(to Atlas)

PERIPH_REG

(VCC + 2.775V)

J4

L1

K3

R1

M1

K2

(from Atlas )

(from Atlas)

2

NC

IO_REG

( to Atlas

)

R

X

_

ANT

_E

N

TX

_ST

A

R

T

(f

ro

m U

8

0

0

)

(100KHz)

EGSM: CH 37 -- 942,4Mhz

DCS: CH 700 -- 1842,8MHz

PCS: CH 661 -- 1960MHz

RX MID CHANNELS

GSM: CH 62 -- 947,4 MHz

850: CH190 -- 881,6

MQSPI

Display

U700

EB1B

EB0B

OEB

R_WB

ADDRESS BUS

DATA BUS

K16

J19

G17

T16

BURSTCLK

LBAB

CS2B

ECBB

T19

L16

W19

N18

A1-24

D0-15

32 MB Flash

RESET OUT

F3

C2

E5

F5,D5

J2,H1,H8

G7

C6

G8

F4

K1

P2

LCD_RS

P1

LCD_SDATA_DATA(7)

M4

LCD_CLK_DATA(6)

N3

LCD_CS

L3...

LCD_DATA (0 - 5)

8MB SRam

(from Neptune)

FLASH

VBUCK

L4..

Timer

GPIO

Interface

BaseBand

Port Interface

Serial Audio

(tx)

(rx)

MQSPI

One

Bus

Wire

UART2

Universal

Asynchron.

Rx /Tx

BT

ANT_DET

(VCC from Q200)

PERIPH_REG

R204

OSCA

TCXO

PERIPH_REG

2,3

5

4,6

Q201

U220

OSCM

RF_REG

2,3

5

4,6

Q200

ANTSW_1

(VCC to U80)

OSCO

CS1B

CS0B

D6

V17

T18

STANDBY_GATEB

STANDBY

OSCM

U804

1

2

4

OSCM

( clock for the DC offset correction

system - 26 MHz)

DMA

Direct

Memory

Access

Controller

V36x

(only for GSM mode)

RF2722

PE

RI

P

H

_

R

EG

24

4

1

OSCB

SWITCH

SWITCH

HS INT

C14

(Flip Open/ Close

Detect)

ADC DATA

E1

Q801

LT_SNS_CTL

1

6

2

Light Sensor

C18

V6

ST

AN

DB

Y_

G

A

TE

B

(to J1300)

U1600

U1601

4

2

Reg.

Hall Effect

Switch

PERIPH_REG

6

1

ANT_DET

U12

(Antenna detect signal)

Ambient

U13

BB

_SA

P

_T

X

B

B

_

S

AP

_R

X

BB

_SA

P

_

F

S

BB

_S

A

P

_

C

LK

B13

B12

A12

D13

(fram

es

y

n

c)

(cl

o

ck)

CLK

13 MH

z

W13

C15

C16

D15

A16

BB

_

S

P

I_C

LK

BB

_S

PI_M

O

S

I

B

B

_S

PI_

M

IS

O

AU

L_

CS

Neptune Atlas

Communication

T11

V12

V11

W12

ST

AN

DB

Y_1

_5V

G8

ST

A

N

DB

Y

CL

K 32

KH

Z

E3

B14

AU

L_

INT

RE

SET

B

V13

(13 M

H

z)

(W

a

tc

h

dog)

WD

OG

OW

B

W11

O

n

e W

ire d

at

a from

B

at

ter

y

US

B_V

P

IN

U

S

B

_

XR

XD

US

B_V

P

O

U

T

US

B_V

M

IN

U

S

B

_

TX

EN

B

US

B_V

N

O

U

T

B16

A17

Neptune Atlas

USB/ RS232

Communication

(f

ro

m

/to

A

tl

a

s

RE

SET

O

U

T

W5

(t

o U700)

(from/ to Neptune

Serial Audio for Ringtone

and Voice Audio)

BL

UE

_R

X

B

L

U

E

_T

X

B

L

U

E

_R

TS

B

B

L

U

E

_C

TS

B

N17

N13

V16

D16

(from/ to U301 BT, J1300

Neptune - BT - Neptune

Communication and Wakeup)

BL

UE

_W

A

K

E

B

B

L

UE

_H

OS

T_W

A

K

E

B

D19

B15

KB

R0

-7

KB

C

0

-1

F3....

G3....

GA

_S

PI_C

S

D18

Neptune Display Diver

T10

GA

_

INT

2

4

(from

At

la

s)

U806

Level

(to

A

tl

as)

KEYPAD

MATRIX

0-9,*,#,

Up, Down

Left-Right,

Center,

Soft L+R,

Menu, Send,

Volume U-D

Smart,

PC

13

A15

VR

505-507

ESD

Customer

Clear

Shift

an

d

BT

))

VA, PTT

SIDE KEYS

(t

o U804)

(to

Atlas

)

B17

BL

UE_

C

L

K

_E

NB

(from Atlas)

PC0

U11

PE14

T8

SPI_CS0

T12

(enable signal for the T-Flash Clock at U1272)

TOUT12

U10

(bias for the THERM signal)

(VCC + 2.775V)

(from Atlas)

OSCB

(from Y806)

(Clock Enable)

(Clock Enable)

(Clock Enable)

(from U220)

11

10

(CS for CLI Display)

(asserts RESET to the ATI)

(VCC from Atlas)

(Deep Sleep Timing

(VCC from Atlas)

from Neptune)

(Crystal outputs

to U200)

(buffered 26 MHz

from U200)

(buffered / inverted

26 MHz to U800)

Revision Overview

Rev. 1.0: Initial Block Diagram

Rev. 1.1: updated Atlas Audio Interface

Rev.1.2: updated format

Rev.1.3: Updated Charger logic levels

Rev.1.4: Updated Atlas Stereo Codec

VBOOST

R1450- R1457

D1450- D1457

LEDKP

BACKLIGHT

LED´s

V30x, V400, V50x, V600

V36x

Revision Overview

Rev. 1.0: Initial Block Diagram

Rev. 1.1: updated Atlas Audio Interface

Rev.1.2: updated format

Rev. 1.3: Updated Charger logic levels

Rev.1.4: Updated Atlas Stereo Codec

Servive, Engineering & Optimization

2005.09.12

LEVEL 3 AL Block Diagram

Rev. 1.4

V360, V361,V365, V367

Alexander Buehler, Michael Mauderer

Page 2of 2

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

DISP_LED1

DISP_LED2

VBOOST1

CLI_LED2

GND

CLI_LED1

GND

CAM_REG

GND

RESETB

LCD_DATA0

LCD_DATA1

LCD_DATA2

LCD DATA3

LCD DATA4

LCD DATA5

LCD_CLK_DATA6

LCD_SDATA_DATA7

LCD_CS

LCD_RS

BB_SPI_MISO

CLK-32KHZ_2_7V

BB_SPI_MOSI

PC0

GND

(from Neptune - CS for CLI)

(from Neptune)

GND

BB_SPI_CLK

35

37

39

HAND_SPKR_GND

HAND_SPKR+

HAND_SPKR-

g1- g4

GND

36

38

40

GA_INT

RTC_BATT

VIB_REG

(fromNeptune)

(from Atlas)

(to Neptune)

(from Atlas)

(from Atlas)

J1300

FLIP CONNECTOR

Flip Connector

(from Atlas)

PERIPH_REG

IO_REG

GRAPH_REG

VBUCK

GND

(from Atlas)

(from Atlas)

PE14

(from Atlas)

GA_SPI_CS

(clock)

CLK 13 MHZ

V12

CLK_32KHZ_2_7V

P16

TIMER

WDOG

K10

CNTL.

PRI SPI

LOGIC

Logic

F

3

,E

1

3

...

..

...

S

w

itcher

BB-

SPI

_

CL

K

BB

_S

P

I_

M

OS

I

B

B

_

S

PI

_M

ISO

AU

L CS

U18

U1

6

T1

8

T1

7

R5

Interface

USB

Y900

V17

D12

RTC_BATT

V16

B+

HAND_SPKRM

HAND_SPKRP

T6

R7

T9

P9

V10

U8

ON

1

B

F1

4

B4

E3

F3

U900

ATLAS UL

ON

LOGIC

OWB

THERM

P13

THERM

CHRGISNSP

BATT+

D14

F13

GND

CHRGCTRL

B16

VBUS

S

G

D

CHARGE

Charger

BATT CONN.

CNTL.

LED

E12

B

B

SA

P FS

BB

SAP

C

L

K

BB S

A

P TX

BB SA

P RX

Neptune Atlas

Communication

ALERTM

ALERTP

STANDBY_1_5V

F12

(to Neptune and U301 BT)

AU

L_I

N

T

N1

4

RESETB

(from U800)

Neptune Atlas

Communication

USB_ID

H8

Q904 (M3)

G

S

B+

B12

BATTFET

Battery to BPLUS

USB

_

VP

IN

USB

_

XR

XD

USB

_

VP

OU

T

USB

_

VM

IN

U

S

B_

TX

E

N

B

USB

_

VM

O

U

T

USB/RS232

(communication)

B2

C4

F4

B1

B3

E4

MICINM

MICBIAS1

Det.

Stereo

B

oos

t 300m

A

G16

S

w

itcher

B

u

c

k

350mA

F16

( 1,

87

5V )

VB

U

C

K

H2

( 2,

7

75V

)

PE

RIP

H

_

R

E

G

U6

( 2,

77

5V

)

AUD

_ RE

G

M1

8

( 1,

2

75 )

GR

AP

H

_

R

E

G

K17

H4

H3

( 2,

7

75V

)

RF

_RE

G

L16

( 1

,57

5V

)

RE

F_R

E

G

N5

( 1,

8/

3V

)

SIM

_

R

E

G

VS

IM

V

S

IM

_E

N

K1

1

VBUSM4

CONTR.

E7

AD

C15

PE

RIP

H

RE

G

(B

ia

s)

(One Wire Bus

to Neptune)

BPFET

VBUS to BP

Switch

(Main Source

for Atlas)

(from Mini USB Connector)

Main Charge Path

B+ support without Ext Charger

B+ support with Ext Charger

Color definition only for this section !

D902

BB_SAP_TX

BB_SAP_RX

BB_SAP_FS

BB_SAP_CLK

(framesync)

Bluetooth

U301

32

30

28

27

BLUE_WAKEB

11

BLUE_HOST_WAKEB

9

BLUE_TX

5

BLUE_CTSB

BLUE_RTSB

31

BLUE_RX

33

29

RESET_B

22

(from Neptune/ Atlas)

(from/ to Neptune

Serial Audio for Ringtone

and Voice Audio)

PERIPH_REG

10

BT_REG

21

BT_ANTENNA

25

Strip Line

Antenna

(on PCB)

Y300

15

16

12

VIB

_

RE

G

(t

o

V

ibra

tor P

ads

ne

ar

(from Neptune)

NeptuneAtlas

Neptune Atlas

USB/ RS232

Communication

C6

B6

(Battery Sense)

(VBUS Sense)

CONV.

D/A

CLK_32KHZ

(from Atlas)

1

J1261

2

1

(from Atlas)

( 1,

3

V

)

POWER/END

(from/ to U301 BT,

Neptune - BT - Neptune

Communication and Wakeup)

Internal MIC

Alert

Pads

TX_START

U15

(from Neptune, Tx Mode indication for Atlas)

( 2,

7

75 )

IO

_R

EG

( 2,

77

5

)

CA

M_

REG

( 5,

5

V

)

VB

OO

ST

2

3

VBUSM4

1

4

5

(to Charging Circuit)

G1-G4

(Shield)

UID

CLK_32KHZ

R16

D-

D+

VBUS 5V

Pass FET

VBOOST

VBUS

D2

(PPD device support)

1

3

(from J1300)

(to J1300)

C9

13

C9

99

to V

ib

rator

VIB

REG

P2

B+ Sense

Mo

to

r

Mi

ni

U

S

B

C

onn

ec

to

r)

REF REG

RF

REG

PE

RI

PH

IO

REG

AUD

IO

REG

IO REG

GR

A

P

H

RE

G

CAM

E

RA

REG

K2

( 1,

87

5V

)

BT_

RE

G

BT R

E

G

4

Microphone

R3

P4

R4

(t

x)

(rx)

13 Bit

Handset

Amplifier

(to J1300)

Q90

1

VCO

REG

VC

O_

DR

V

(M

ain S

our

ce-

f

ro

m

M

3

)

( 2,

77

5V

)

VC

O_

RE

G

V2

SIM_PD

T14

CHRGRAW

S

G

D

Q903 (M4)

Q905 (M1)

(I Sense)

G

S

M1700

2

3

1

4

R910

R911

D

Switch

B14

CHRGISNSP

E15

(Charger output

Sense)

(Current Control)

Q906 (M2)

DISP_LED2

CLI_LED2

DISP_LED1

(o

nly us

ed in Atlas

)

CLI_LED1

F6

C5

LED_KP1

(t

o Neptune)

(A

tl

as

in

ter

n

al and

AL

cir

cuit)

( Atlas

, Neptun

e

,

U700,J

1300, L

evel Shif

ter

)

(t

o J

1300)

(t

o Neptune amd M

120

0)

)

(t

o U150,

U200, Q200)

(t

o

U301)

(t

o Atlas

, Neptune, J

1300)

(t

o Atlas

and J

1300)

(t

o

U250

Bluetooth

Mini USB

Charger and Power-

source Control

(toJ1300)

(from/ to Neptune and U700)

(toNeptune)

(from Atlas)

(from Neptune)

TOUT12

(Bias Voltage from

Neptune)

(Accessory Detection signal)

(from Acesory Connector)

(EXT Power)

(EXT Power)

VR1

70

0

VR

177

9

VR9

50

S514

T10

P6

AUX_MICM

HJACK_SPKR_R -

J1240

HJACK_DET

R9

P7

HJACK_SPKR_L -

R11

FL1240

ST_CMP

HJACK_MIC

MICBIAS2

4

2

3

1

RAW_A1INT

Det.

Headset

U2

ST_REF

T11

RT

C

K

3

7

5

2

4

6

J1270

Trans Flash

Card Reader

C2

A1

B1

CMD

(f

ro

m

N

ep

tu

n

e

)

SPI

_

CS

0

CLK

U1275

1

6

4

PERIPH_REG

(from Atlas)

5

U1271

(VCC)

(C

hip Select/ E

n

able)

DAT3

(Single Speed)

D0

D1

D2

D3

CMD

VCC

CLK

GND

8

1

BLUE_CLK_ENB

13

(ARIGHT_OUT)

(ALEFT_OUT)

(to Keypad LED´s)

INT_MIC+

(fromNeptune)

R

936

3

4

1

+

U200)

Keypad Backlight

ESD

VR939

VR1400

VR1401

VR998

T-Flash

(asserts RESET to the ATI)

Headset

Connector

SAP

Supply

Amplifier

Alert

Amplifier

Headset

Amplifier

EMU

L

/

H

/

H

H

/

L

/

L

H

/

H

/

H

H

/

H

/

H

L

/

H

/

H

L

/

H

/

L

CODEC

16 BIT

STEREO

Wyszukiwarka

Podobne podstrony:

block diagram

ALAN42MULTI block diagram

20060919095901218 09 Block Diagram

Block Diagram

System Block Diagram

ZEUS PRO BLOCK DIAGRAM

block diagram

Block Diagram

POG IF Block Diagram

Thomson MT5655 BLOCK DIAGRAM

Block Diagram W510 L3 C A3 V1 0 Block Diagrams

Block Diagram V9POIFBlDi V975 L3 2[1] 0 050131145018

Block Diagram

Block Diagram

Block Diagram

Block Diagram 5

więcej podobnych podstron