LE

DC

(p

in

13

) &

Ba

tt

er

y_

EN

(

p

in

1

5

)

J301

Headset

Connector

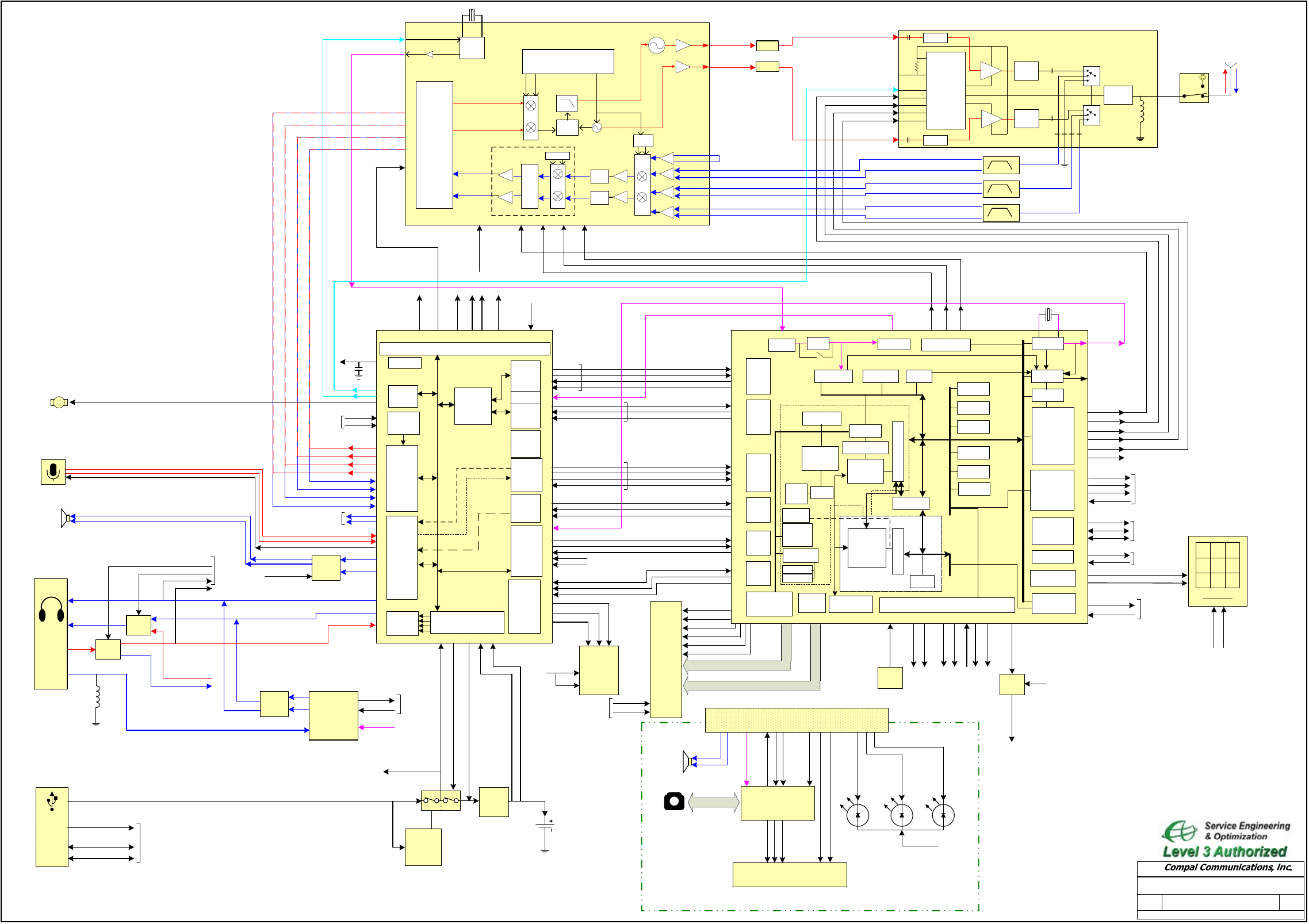

LNA850

LNA1800

U802

SI4210

FLASH

128Mbit

&

PSRAM

32Mbit

U200

SPI

GEA

DieID

TIMER1

TIMER2

ARMIO (GPIO)

TPU

TSP

LCD IF

UART

modem

ULPD

RTC

CK32KHz

GSM

Time

INTH

B

R

I

D

G

E

DSP subchip

cDSP

S28C128

8K API

DMA(6)

B

R

I

D

G

E

ARM7

Debug Unit

MEMIF

Memory

Protect

Unit

5Mbit

SRAM

JTAG

MCU TOP-CELL

PLL & CLKM

WTDOG

INTH

SLICER

DIV-2

RHEA bus

13MHz

External

Memories

Keypad Port

TSP

NAND

Flash IF

CLK32K

PA_EN

BS

ROW0 - ROW4

COL0 - COL4

AU

D

A

M

P

_

S

D

HS

_

EN

H

S

_

D

ET

EC

T

32.768KHz

XTAL

TSPDO

TSPCLK

TSPEN2

BS

Toppoly

TFT LCD Display

128*160 1.8inch 65K

AFC

XTAL

RF_CLK (26MHz)

APC

AFC

ADAC

Timing

Serial Port

(TSP)

Baseband

Codec

(BBC)

Audio

Codec

(AUC)

Monitoring

ADC

(MADC)

Baseband

Serial

Port

(BSP)

Clock

Gene

MCU

Serial

Port

(USP)

Test

Access

Port

(TAP)

Voiceband

Serial Port

(VSP)

I2S Audio

Serial

Port

Voltage

Reference

Power

Control

(VRPC)

SIM CARD

Interface

(SIM)

Battery Charger

Interface

(BCI)

APC

AFC

DAC

TSPDO

TSPEN0

TXQP

TXQN

TXIP

TXIN

RXQP

RXQN

RXIP

RXIN

VBAT

VBACKUP

VCHG

ICHG

SIM_I/O

SIM_CLK

SIM_RST

Voltage Regulation

(VREG)

V_R

A

M

V_S

IM

VB

A

T

V_

D

B

B

V_I

O

PC

H

G

V

CCS

ICT

L

VC

H

G

VB

A

T

S

Internal

Bus

Controller

(IBIC)

APC

APC

CLK13M

QN

QP

IP

IN

Vibrator

TSPEN0

U101 SYREN

BF800

26MHz

PDN

GSMRX

DCSRX

LBTXOUT

HBTXOUT

PDN

W375 EU Band Block Diagram

Title

Size

Rev

Document Number

Date : 25 October, 2006

A3

1.2

LNA900

LNA1900

PGA

PGA

Q

ADC

I

ADC

DI

G

IT

ALFI

L

FI

LTER

PGA

PGA

AN

ALO

G

I

N

TER

FACE

VCO+FREQUENCY SYNTHESIZER

DET

90/0

LOW-IF

DCXO

Att 3dB

R815

Att 3dB

R816

A800

V_F

LA

S

H

V_

R

T

C

LC

D_

n

R

ESE

T

From/to

headset

KE

Y

LI

G

H

T_

E

N

KE

Y

LI

G

H

T

_

E

N

SW_LO_TX

SW_HI_TX

RF_CLK (26MHz)

V_IO

RF2

V

8

(L

D

O

S

u

ppl

y)

Fr

om

U8

01

Write

Buffer

0.5Mbit

SRAM

48Kbytes

ROM/

Boot

CRYPTO

Processors

ARMIO

GSM_IN

PCS_IN

PA_EN

Memory

Interface

BACK

LI

GHT

_

E

N

U201

Charge

Pump

SW_LO_TX

SW_HI_TX

VBAT

LE

D

B

ac

klig

ht

(5

V

)

J500

USB

Connector

U502

Overvoltage

Control

(c

h

arg

e c

u

rr

en

t c

o

n

tr

o

l)

U504

Charge

IC

VBAT

(c

har

g

e c

u

rr

en

t s

ens

e)

From G2+

Voice

Band

Interfac

e

BaseBand

Interface

BFSR

BDR

BFSX

BDX

MCUDI

MCUDO

MCUEN0

VCLKRX

VDX

VDR

VFSRX

U100 G2+

SIM

SIM-IO3

SIM-CLK3

SIM-RST3

CLK13M

UDX

UDR

UEN

VCK

VFS

VDX

VDR

IT-WAKEUP

RPWON

CLK32K

AUDR

AUCK

AUFS

I2S

CDO

CSCLK

CSYNC

ARM-SYREN

intercommunication

Baseband

intercommunication

Voice Band

intercommunication

(Wakeup interrupt from RTC)

(from TP105 on Test point)

ONnOFF

nRESPWRON

(Chip Reset)

ARM

Serial

Port

RTC/

RESET

PWON

(From keypad)

(keypad ON indication from keypad interface processor)

To Key

pad

From H

ead

set

To H

ead

se

t

To S

pea

ke

r

RX_MODEM1

TX_MODEM1

To SYREN

Boot ROM

64b Key

128b Key

Camera

Module

1.5V

2.8V

2.8V

1.5V

2.8V

2.85

V

VB

A

T

VBACKUP

VBACKUP

For RTC Backup

C1

0

8

HSOR

HSMICP

EARP

EARN

MICIP

MICIN

MICBIAS

HS_DETECT

SPKN

SPKP

U301

Audio

AMP.

Speaker

AUDAMP_SD

(from G2+)

U303

MUX

U302

MUX

TX_MODEM1

RX_MODEM1

HS_EN1

900

BF801

1800

BF802

1900

Match/

Filter

PA

PA

U803

SKY77506

Match/

Filter

Match

Match

BiCMOS

Power

Amplifier

Controller

Antenna

Switch

Decoder

Duplexer

PCSRX

J800

K

eypad

SIM

Connecter

1.8 or 3V

SIM Card

U400

FM Radio

U401

Audio

AMP.

HSOL

HS_EN2

FM_Ant

FML

FMR

AUXI

I2C

SDA

SCL

From/to

FM radio

From/to

G2+

CLK32K

USB

USB_N

USB_P

USB_EN

From/to USB

connectror

MIC

U503

SDA

SCL

V_BUS

Ba

tt

er

y

Me

ss

ag

e

C

alle

r ID

Sub-Board

To Sub-board

EARP

EARN

VBAT

Me

ss

ag

e_

E

N

U20

Back-end IC

Address Bus ADD[1-24]

SDO

SCLK

LCD_nCS

From/to LCD

SDI

CAM_Data [0-7]

SD

O

SC

LK

BE

_

n

RE

S

E

T

SD

I

CLK

1

3

M

Data Bus DATA[0-15]

Main board to sub-board

FPC

LED

Ba

ck

lig

ht

(5

V

)

Receiver

LCD

_

SD

A

T

A

LC

D_

SC

LK

LC

D

_

C

S

LC

D_

nR

ES

ET

To L

CD

To L

CD

Antenna

From/to

G2+

To Syren

U701

Folder

sensor

FO

LD

_DE

T

BE

_

n

RE

S

E

T

Me

ss

ag

e_

E

N

To S

ub

-b

oard

To B

ack

-en

d

IC

USB_ID

USB_P / USB_EN

USB_N

From/to

G2+

1

4

3

2

6

3

2

5

IN

C

O

M

_

EN

1

(p

in

22)

&

IN

C

O

M_

EN

2 (

p

in

19

)

6

3

18

5

14

12

2

9 11

15 17 22

13

19

4

5

V_SIM

3

2

1

nCS5

nCS4

nBLE

nFOE

RnW

nBHE

V_FLASH

V_RAM

From SYREN

From SYREN

Document Outline

Wyszukiwarka

Podobne podstrony:

block diagram

ALAN42MULTI block diagram

20060919095901218 09 Block Diagram

Block Diagram

System Block Diagram

ZEUS PRO BLOCK DIAGRAM

block diagram

Block Diagram

W370 W375 Signal Flow Rev 1 2

Block Diagram 2

POG IF Block Diagram

Thomson MT5655 BLOCK DIAGRAM

Block Diagram W510 L3 C A3 V1 0 Block Diagrams

Block Diagram V9POIFBlDi V975 L3 2[1] 0 050131145018

Block Diagram

Block Diagram

więcej podobnych podstron