Wy

ś

wietlacz

siedmiosegmentowy

autorzy: Tomasz Perek

Tomasz Biernat

Projekt: Układ, który liczbę podaną w postaci binarnej wyświetla w systemie

szesnastkowym, ósemkowym oraz dziesiętnym.

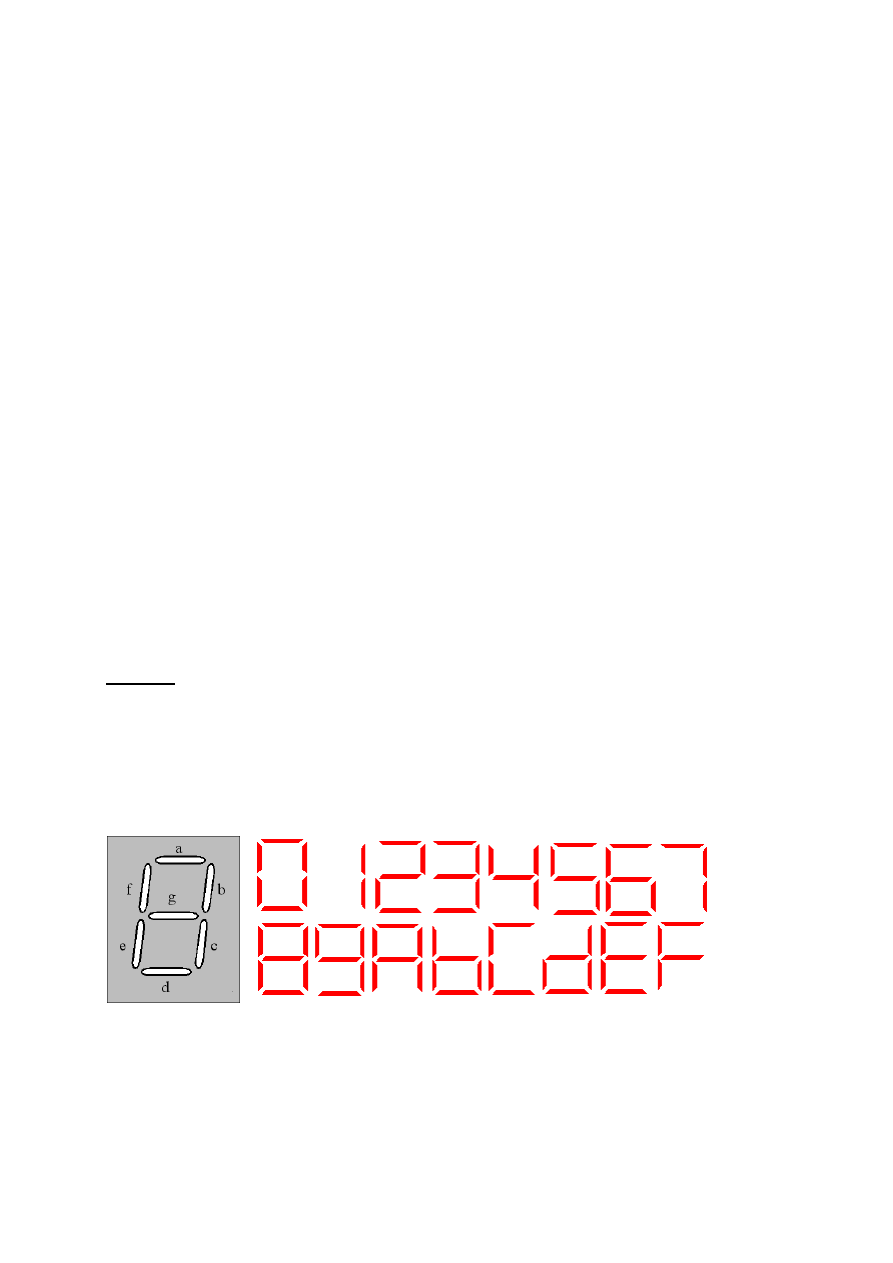

Wyświetlacz siedmiosegmentowy jest powszechnie stosowany do prezentacji cyfr,

liter. Składa się z siedmiu segmentów oznaczonych literami a-g (tak jak na rysunku),

które mogą być zapalone lub nie. Kolejne cyfry i litery wyglądają następująco:

1.

2

Symulacja w programie Multisim

załącznik: 7seg.ms10

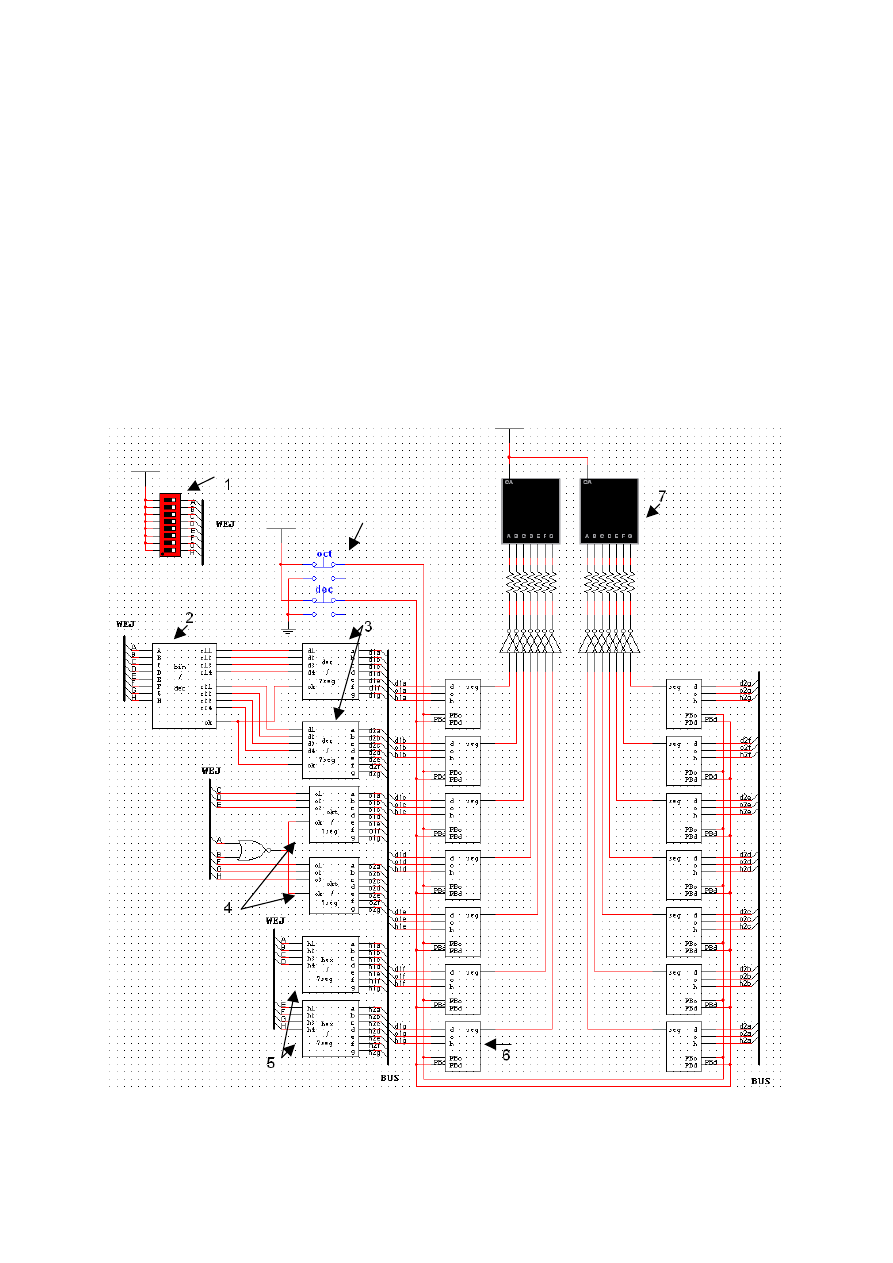

Układ zrealizowany w programie Multisim składa się z następujących elementów:

1. Wejście - ośmiobitowy przełącznik

2. Podukład zamieniający 8-bitową liczbę binarną na dwie 4-bitowe liczby binarne,

odpowiadające dziesiętnym cyfrom liczby wejściowej

3. Podukłady kodujące liczbę dziesiętną 0-9 do wyświetlacza siedmiosegmentowego

4. Podukłady kodujące liczbę ósemkową 0-7 do wyświetlacza siedmiosegmentowego

5. Podukłady kodujące liczbę szesnastkową 0-F do wyświetlacza siedmiosegmentowego

6. Podukłady wybierające odpowiednią reprezentację liczby

7. Wyjście - dwa wyświetlacze siedmiosegmentowe

8. Wejście – przyciski do wyboru reprezentacji

8

3

Opis poszczególnych elementów:

1.

Wej

ś

cie - o

ś

miobitowy przeł

ą

cznik

Jest to układ ośmiu przełączników, za pomocą których ustawiamy wejściową liczbę

binarną. Przełącznik znajdujący się najwyżej odpowiada najbardziej znaczącemu bitowi.

2.

Podukład zamieniaj

ą

cy 8-bitow

ą

liczb

ę

binarn

ą

na dwie 4-bitowe liczby

binarne, odpowiadaj

ą

ce dziesi

ę

tnym cyfrom liczby wej

ś

ciowej

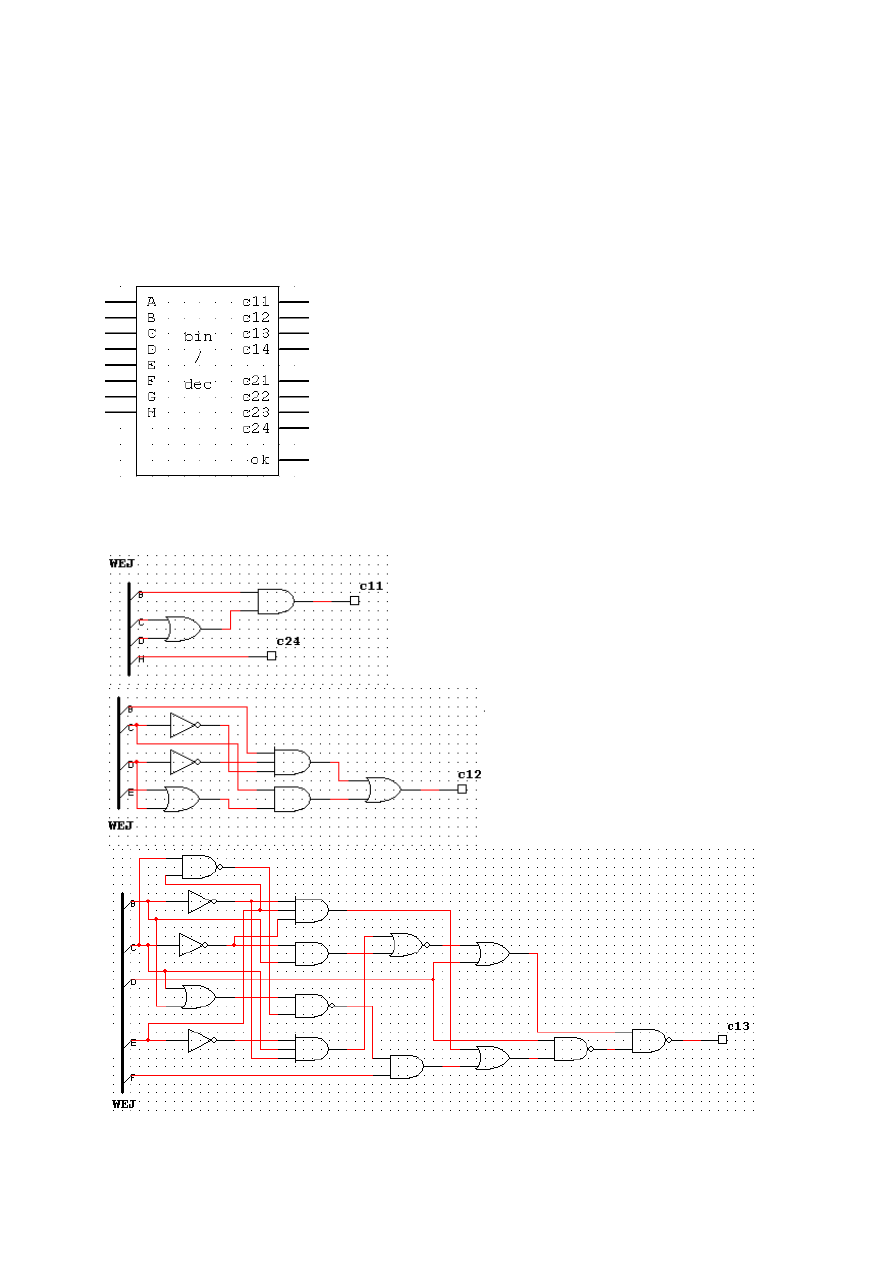

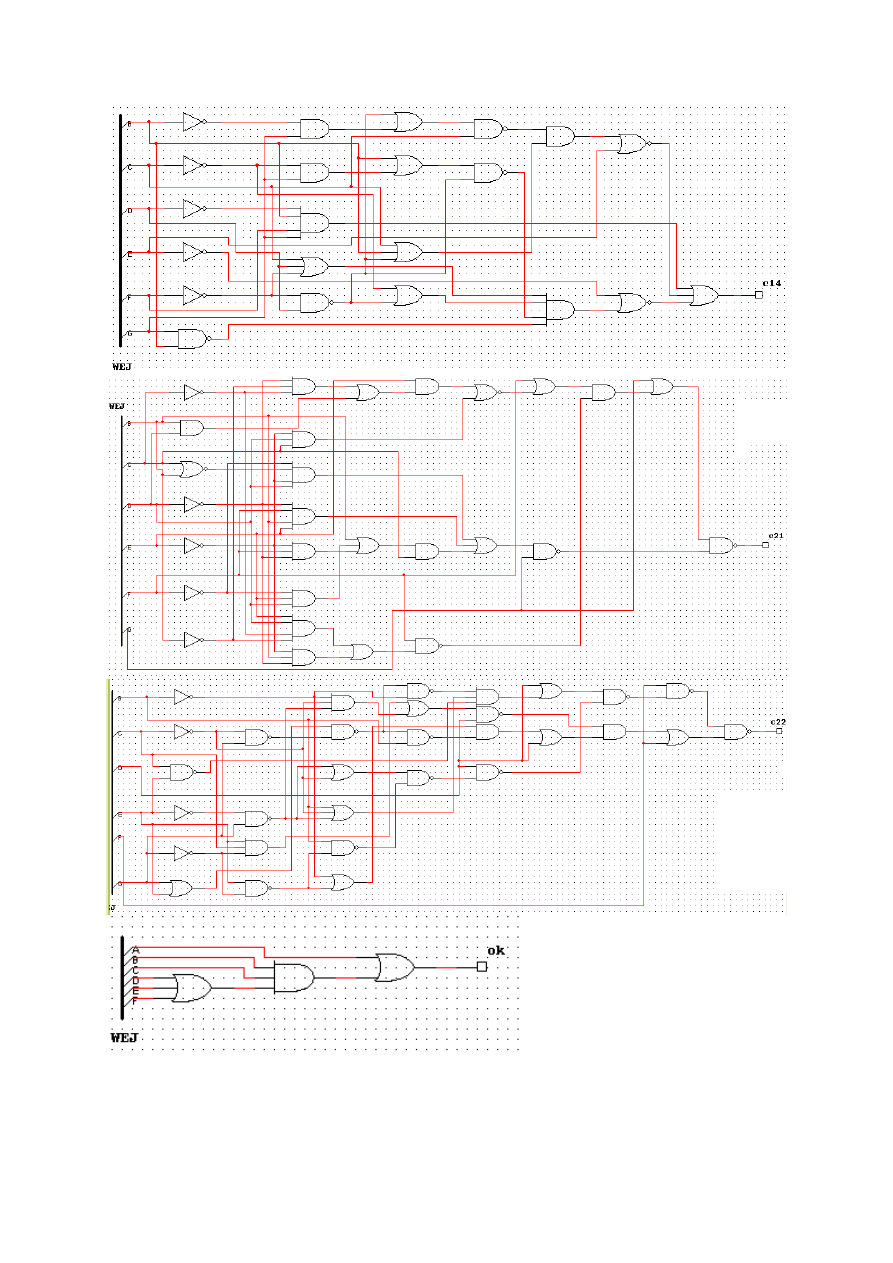

Układ posiada 8 wejść „A”-„H”, odpowiadających

ośmiu bitom liczby wejściowej. Wyjścia „c11”-„c14”

odpowiadają bitom pierwszej cyfry dziesiętnej, a „c21”-„c24” –

drugiej cyfry. Dodatkowe wyjście „ok” informuje, czy liczba

dziesiętna nie jest większa od 99. Na przykład, dla wejścia

A-H -> 00111011 (59) otrzymamy:

c11-c14 -> 0101 (5)

c21-c24 -> 1001 (9)

ok -> 0

Nie zamieszczamy wszystkich tabel prawdy, gdyż w tym przypadku mają one 100

wierszy, a tablice Karnaugh mają wymiary 8x16. Schematycznie, zminimalizowane

i uproszczone funkcje przedstawiają się następująco:

4

5

3.

Podukłady koduj

ą

ce liczb

ę

dziesi

ę

tn

ą

0-9 do wy

ś

wietlacza

siedmiosegmentowego

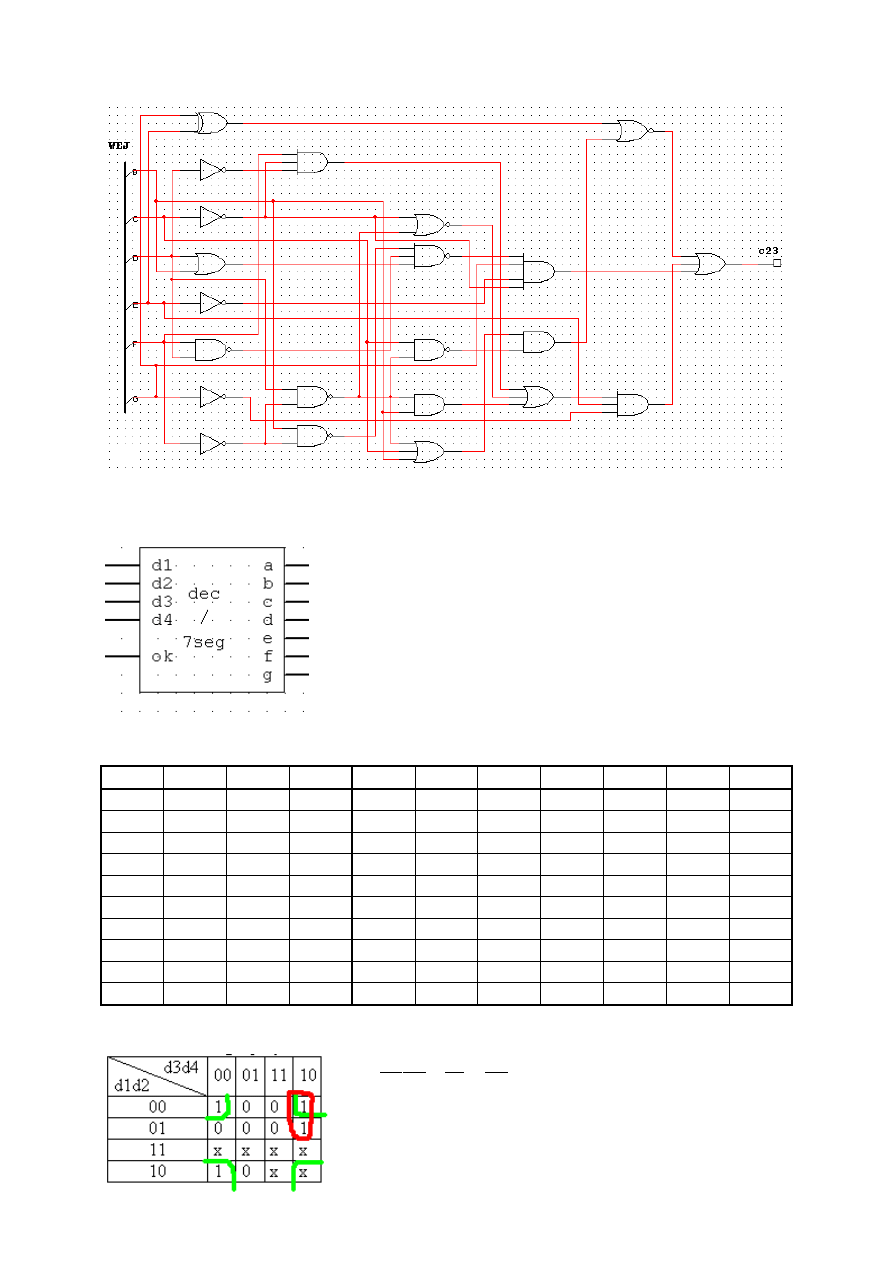

Wejście układu stanowią 4 bity cyfry dziesiętnej „d1”-

„d4”, oraz „ok” – informacja, czy liczba wejściowa nie jest

większa od 99. Wyjścia „a”-„g” odpowiadają poszczególnym

segmentom wyświetlacza. Jeśli ok=0, to na wyjściach

kodowana jest odpowiednia cyfra, a jeśli ok=1, to wyjście

ustawiane jest tak aby na wyświetlaczu pojawiła się pozioma

kreseczka, np:

d1-d4 = 0100 (4), ok=0 -> a-g = 0110011

d1-d4 = 1001 (9), ok=1 -> a-g = 0000001

Tabela prawdy:

d1

d2

d3

d4

a

b

c

d

e

f

g

0

0

0

0

1

1

1

1

1

1

0

0

0

0

1

0

1

1

0

0

0

0

0

0

1

0

1

1

0

1

1

0

1

0

0

1

1

1

1

1

1

0

0

1

0

1

0

0

0

1

1

0

0

1

1

0

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

0

1

1

1

1

1

0

1

1

1

1

1

1

0

0

0

0

1

0

0

0

1

1

1

1

1

1

1

1

0

0

1

1

1

1

1

0

1

1

Tablica Karnaugh, przykładowo dla segmentu e:

2 4

1 3 4

e

d d

d d d

=

+

6

Schemat:

4.

Podukłady koduj

ą

ce liczb

ę

ósemkow

ą

0-7 do wy

ś

wietlacza

siedmiosegmentowego

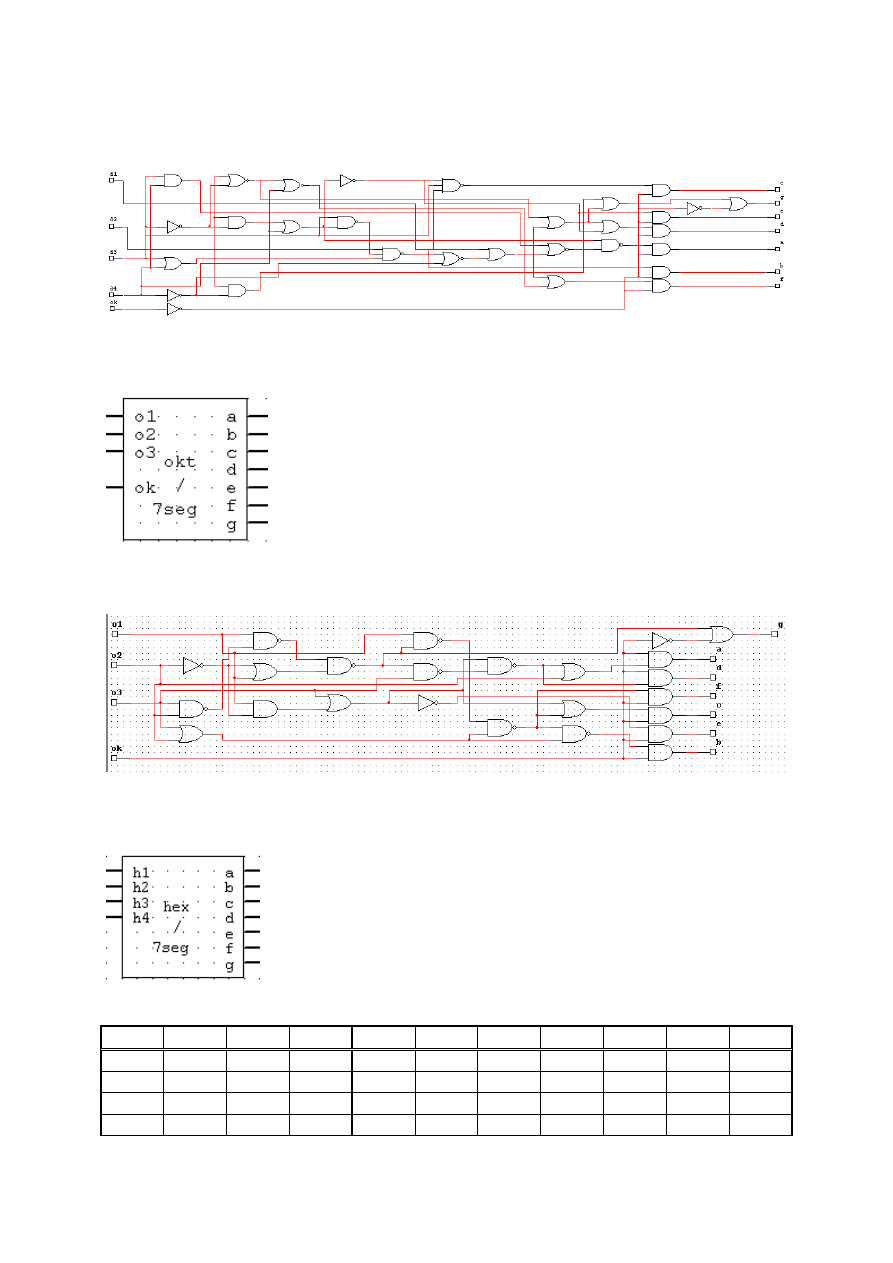

Wejście układu stanowią 3 bity cyfry ósemkowej „o1”-„o3”,

oraz „ok” – informacja, czy liczba wejściowa nie jest większa od 63.

Wyjścia „a”-„g” odpowiadają poszczególnym segmentom

wyświetlacza. Jeśli ok=1, to na wyjściach kodowana jest odpowiednia

cyfra, a jeśli ok=0, to wyjście ustawiane jest tak aby na wyświetlaczu

pojawiła się pozioma kreseczka, np:

o1-o3 = 101 (5), ok=1 -> a-g = 1011011

o1-o3 = 001 (1), ok=0 -> a-g = 0000001

Tabela prawdy jest identyczna jak w punkcie 3, tylko pomniejszona o dwa ostatnie wiersze.

Schemat przedstawia się następująco:

5.

Podukłady koduj

ą

ce liczb

ę

szesnastkow

ą

0-F do wy

ś

wietlacza

siedmiosegmentowego

Wejście układu stanowią 4 bity cyfry/liczby szesnastkowej

„h1”-„h4”. Wyjścia „a”-„g” odpowiadają poszczególnym segmentom

wyświetlacza.. Przykładowo:

h1-h4 = 1011 (B) -> a-g = 0011111

h1-h4 = 0011 (3) -> a-g = 1111001

Tabela prawdy jest taka jak w punkcie trzecim, tylko powiększona o wiersze:

d1

d2

d3

d4

a

b

c

d

e

f

g

1

0

1

0

1

1

1

0

1

1

1

1

0

1

1

0

0

1

1

1

1

1

1

1

0

0

1

0

0

1

1

1

0

1

1

0

1

0

1

1

1

1

0

1

7

1

1

1

0

1

0

0

1

1

1

1

1

1

1

1

1

0

0

0

1

1

1

Schemat:

6.

Podukłady wybieraj

ą

ce odpowiedni

ą

reprezentacj

ę

liczby

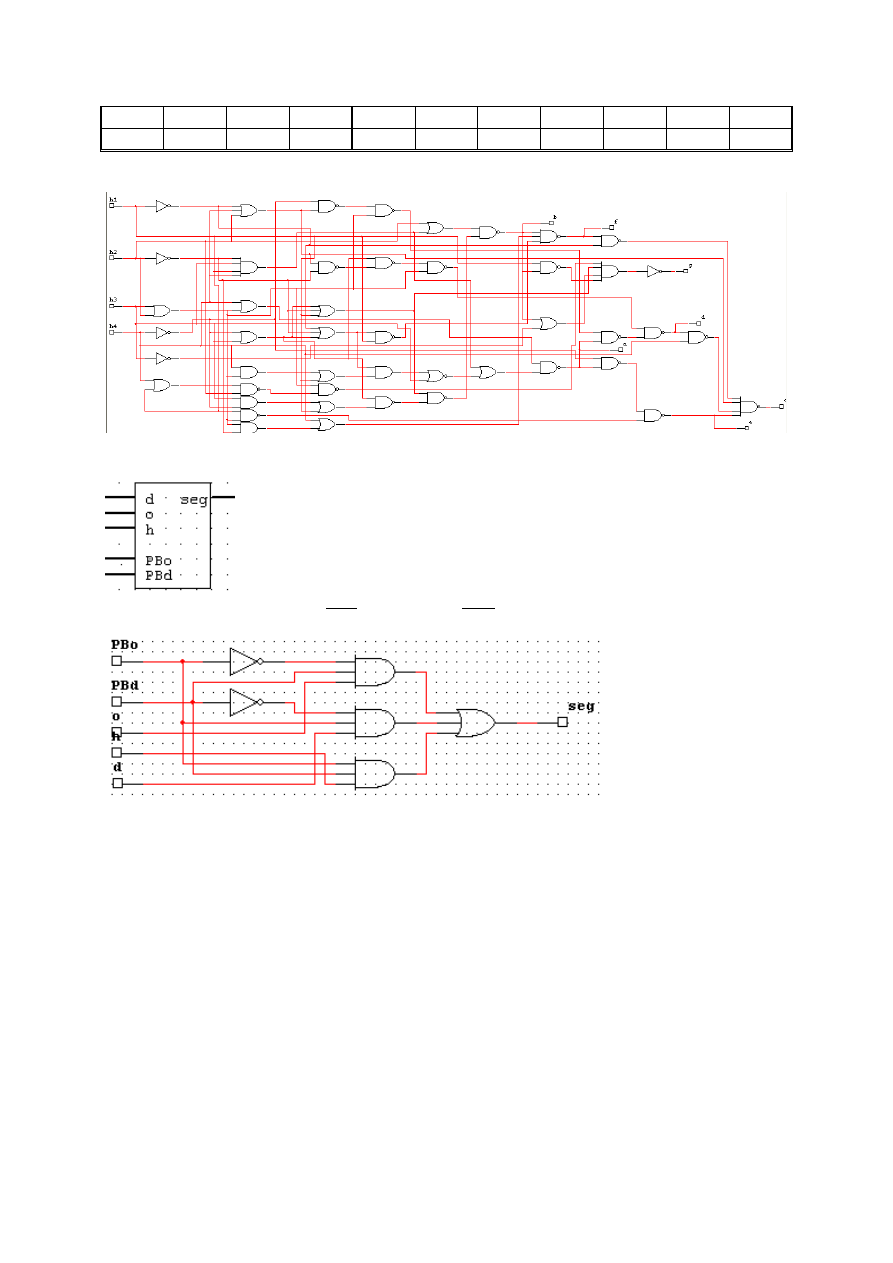

Tych układów jest w projekcie 14, po jednym dla każdego wejścia

wyświetlacza. Wejście „d” to stan odpowiedniego segmentu przy systemie

dziesiętnym, „o” – ósemkowym, „h” – szesnastkowym. „PBo” podłączone

jest do przycisku wyboru systemu ósemkowego, a „PBd” do przycisku

wyboru systemu dziesiętnego. Wyjście „seg” to stan odpowiedniego

segmentu, w wybranej za pomocą przycisków reprezentacji. Funkcja

wybierająca jest prosta:

seg

PBo PBd o

PBo PBd d

PBo PBd h

=

+

+

7.

Wyj

ś

cie - dwa wy

ś

wietlacze siedmiosegmentowe

W programie Multisim wybraliśmy wyświetlacze w konfiguracji wspólnej anody,

każde wejście podłączone jest przez rezystor

100

Ω

oraz przez bramkę NOT, ponieważ

segment zapala się przy „0” logicznym.

8.

Wej

ś

cie – przyciski do wyboru reprezentacji

Dwa przyciski push-button ustalające w jakiej reprezentacji ma byś pokazywana

liczba. Standardowo wyświetlana jest liczba w systemie szesnastkowym, przy wciśniętym

przycisku „okt” – w ósemkowym, przy wciśniętym przycisku „dec” – w dziesiętnym. Przy

przyciskach wciśniętych naraz na wyświetlaczu nic się nie pojawia.

8

2. Symulacja w programie Quartus II

Układ zbudowany jest na podobnej zasadzie jak w programie Multisim, załącznik zawiera

projekt zrealizowany w programie Quartus II - schematy, oraz pliki vhdl.

załącznik: 7seg.zip

3. Projekt w j

ę

zyku VHDL

konwersja.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY konwersja IS

PORT

(

A : IN STD_LOGIC;

B : IN STD_LOGIC;

C : IN STD_LOGIC;

D : IN STD_LOGIC;

E : IN STD_LOGIC;

F : IN STD_LOGIC;

G : IN STD_LOGIC;

H : IN STD_LOGIC;

c24 : OUT STD_LOGIC;

c23 : OUT STD_LOGIC;

c22 : OUT STD_LOGIC;

c21 : OUT STD_LOGIC;

c14 : OUT STD_LOGIC;

c13 : OUT STD_LOGIC;

c12 : OUT STD_LOGIC;

c11 : OUT STD_LOGIC;

ok : OUT STD_LOGIC

);

END konwersja;

ARCHITECTURE bdf_type OF konwersja IS

SIGNAL

NB : STD_LOGIC;

SIGNAL

NC : STD_LOGIC;

SIGNAL

ND : STD_LOGIC;

SIGNAL

NE : STD_LOGIC;

SIGNAL

NF : STD_LOGIC;

SIGNAL

NG : STD_LOGIC;

BEGIN

NB <= NOT(B);

NC <= NOT(C);

ND <= NOT(D);

NE <= NOT(E);

NF <= NOT(F);

NG <= NOT(G);

c24 <= H;

9

c23 <= (C AND ND AND E AND G) OR (C AND E AND F AND G) OR (B AND ND AND E

AND NG) OR (C AND ND AND NE AND NG) OR (B AND E AND F AND NG) OR (C AND NE

AND F AND NG) OR (NC AND ND AND E AND F AND NG) OR (C AND D AND E AND NF

AND NG) OR (NB AND NC AND D AND E AND NF AND G) OR (NB AND NC AND D AND NE

AND NF AND NG) OR (NB AND NC AND ND AND NE AND G) OR (NC AND D AND NE AND F

AND G) OR (B AND NC AND NE AND NF AND G);

C22 <= (B AND D AND NE AND F) OR (B AND D AND F AND G) OR (NB AND NC AND D

AND E AND NF) OR (C AND D AND NE AND F AND G) OR (B AND ND AND E AND F AND

NG) OR (NB AND NC AND D AND NF AND NG) OR (NB AND C AND ND AND NE AND NF

AND G) OR (C AND ND AND E AND F) OR (NB AND NC AND ND AND F AND G) OR (B

AND NC AND ND AND NF AND G) OR (NB AND ND AND NE AND F AND NG) OR (C AND D

AND E AND NF AND NG) OR (B AND ND AND NE AND NF AND NG);

C21 <= (B AND C AND G) OR (B AND ND AND E AND F AND G) OR (C AND ND AND NE

AND F AND G) OR (C AND D AND E AND NF AND G) OR (B AND ND AND NE AND F AND

NG) OR (B AND D AND E AND NF AND NG) OR (C AND D AND NE AND NF AND NG) OR

(NB AND NC AND D AND NE AND NF AND G) OR (NB AND NC AND D AND E AND F AND

NG) OR (NB AND NC AND ND AND E AND NF AND NG);

C14 <= (B AND ND AND E) OR (C AND ND AND NE) OR (B AND E AND F) OR (C AND

NE AND F) OR (B AND E AND G) OR (NC AND ND AND E AND F) OR (C AND D AND E

AND NF) OR (NC AND ND AND E AND G) OR (B AND ND AND F AND G) OR (NC AND E

AND F AND G) OR (NB AND NC AND D AND NE AND NF) OR (NB AND D AND NE AND NF

AND G);

C13 <= (B AND NC AND ND) OR (NB AND NC AND D AND E) OR (NB AND C AND ND AND

NE) OR (NB AND NC AND D AND F) OR (C AND D AND E AND F);

C12 <= (C AND D) OR (C AND E) OR (B AND NC AND ND);

C11 <= (B AND C) OR (B AND D);

OK <= ((D OR E OR F) AND B AND C) OR A;

END bdf_type;

---------------------------------------------------------------------------

dec_seg.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY dec_seg IS

PORT

(

d1 : IN STD_LOGIC;

d2 : IN STD_LOGIC;

d3 : IN STD_LOGIC;

d4 : IN STD_LOGIC;

ok : IN STD_LOGIC;

a : OUT STD_LOGIC;

b : OUT STD_LOGIC;

c : OUT STD_LOGIC;

d : OUT STD_LOGIC;

e : OUT STD_LOGIC;

f : OUT STD_LOGIC;

g : OUT STD_LOGIC

);

END dec_seg;

ARCHITECTURE bdf_type OF dec_seg IS

SIGNAL

Nd2 : STD_LOGIC;

SIGNAL

Nd3 : STD_LOGIC;

10

SIGNAL

Nd4: STD_LOGIC;

SIGNAL

Nok : STD_LOGIC;

BEGIN

Nd2 <= NOT(d2);

Nd3 <= NOT(d3);

Nd4 <= NOT(d4);

Nok <= NOT(ok);

a <= ((d3 AND d4) OR (d2 AND d3 AND Nd4) OR (d2 AND Nd3 AND d4) OR (Nd2 AND

Nd4) OR d1) AND Nok;

b <= ((Nd2 AND Nd3) OR (d3 AND d4) OR (Nd3 AND Nd4) OR (Nd2 AND Nd4)) AND

Nok;

c <= ((Nd2 AND Nd3) OR (d3 AND d4) OR (Nd3 AND Nd4) OR (d2 AND d3 AND Nd4)

OR (d2 AND Nd3 AND d4)) AND Nok;

d <= ((Nd2 AND d3) OR (d2 AND d3 AND Nd4) OR (d2 AND Nd3 AND d4) OR (Nd2

AND Nd4) OR d1) AND Nok;

e <= ((d2 AND d3 AND Nd4) OR (Nd2 AND Nd4)) AND Nok;

f <= ((Nd3 AND Nd4) OR (d2 AND d3 AND Nd4) OR (d2 AND Nd3 AND d4) OR d1)

AND Nok;

g <= ((d2 AND Nd4) OR (Nd2 AND d3) OR (d2 AND Nd3 AND d4) OR d1) OR ok;

END bdf_type;

---------------------------------------------------------------------------

okt_seg.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY okt_seg IS

PORT

(

o1 : IN STD_LOGIC;

o2 : IN STD_LOGIC;

o3 : IN STD_LOGIC;

ok : IN STD_LOGIC;

a : OUT STD_LOGIC;

b : OUT STD_LOGIC;

c : OUT STD_LOGIC;

d : OUT STD_LOGIC;

e : OUT STD_LOGIC;

f : OUT STD_LOGIC;

g : OUT STD_LOGIC

);

END okt_seg;

ARCHITECTURE bdf_type OF okt_seg IS

SIGNAL

No1 : STD_LOGIC;

SIGNAL

No2 : STD_LOGIC;

SIGNAL

No3 : STD_LOGIC;

SIGNAL

Nok: STD_LOGIC;

BEGIN

No1 <= NOT(o1);

11

No2 <= NOT(o2);

No3 <= NOT(o3);

Nok <= NOT(ok);

a <= ((o2 AND o3) OR (o1 AND No2 AND o3) OR (o1 AND o2 AND No3) OR (No1 AND

No3)) AND Nok;

b <= ((No1 AND No2) OR (o2 AND o3) OR (No2 AND No3) OR (No1 AND No3)) AND

Nok;

c <= ((No1 AND No2) OR (o2 AND o3) OR (No2 AND No3) OR (o1 AND No2 AND o3)

OR (o1 AND o2 AND No3)) AND Nok;

d <= ((No1 AND o2) OR (o1 AND No2 AND o3) OR (o1 AND o2 AND No3) OR (No1

AND No3)) AND Nok;

e <= ((o1 AND o2 AND No3) OR (No1 AND No3)) AND Nok;

f <= ((No2 AND No3) OR (o1 AND No2 AND o3) OR (o1 AND o2 AND No3)) AND Nok;

g <= ((o1 AND No3) OR (No1 AND o2) OR (o1 AND No2 AND o3)) OR ok;

END bdf_type;

---------------------------------------------------------------------------

hex_seg.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY hex_seg IS

PORT

(

h1 : IN STD_LOGIC;

h2 : IN STD_LOGIC;

h3 : IN STD_LOGIC;

h4 : IN STD_LOGIC;

a : OUT STD_LOGIC;

b : OUT STD_LOGIC;

c : OUT STD_LOGIC;

d : OUT STD_LOGIC;

e : OUT STD_LOGIC;

f : OUT STD_LOGIC;

g : OUT STD_LOGIC

);

END hex_seg;

ARCHITECTURE bdf_type OF hex_seg IS

SIGNAL

Nh1 : STD_LOGIC;

SIGNAL

Nh2 : STD_LOGIC;

SIGNAL

Nh3 : STD_LOGIC;

SIGNAL

Nh4: STD_LOGIC;

BEGIN

Nh1 <= NOT(h1);

Nh2 <= NOT(h2);

Nh3 <= NOT(h3);

Nh4 <= NOT(h4);

a <= (Nh1 AND h3 AND h4) OR (Nh1 AND h3 AND Nh4) OR (Nh1 AND h2 AND Nh3 AND

h4) OR (h1 AND h2 AND h3) OR (Nh2 AND Nh3 AND Nh4) OR (h1 AND h2 AND Nh4)

OR (h1 AND Nh2 AND Nh3) OR (h1 AND Nh2 AND Nh4);

12

b <= (Nh1 AND Nh3 AND Nh4) OR (Nh1 AND h3 AND h4) OR (Nh2 AND Nh3) OR (Nh1

AND Nh2 AND h3) OR (h1 AND h2 AND Nh3 AND h4) OR (h1 AND Nh2 AND Nh4);

c <= (Nh1 AND h3 AND h4) OR (Nh2 AND Nh3) OR (Nh1 AND h2 AND Nh4) OR (h1

AND h2 AND Nh3 AND h4) OR (h1 AND Nh2 AND h3 AND h4) OR (Nh1 AND h2 AND Nh3

AND h4) OR (h1 AND Nh2 AND Nh4);

d <= (Nh1 AND Nh2 AND h3) OR (Nh1 AND h3 AND Nh4) OR (h1 AND h2 AND Nh3 AND

h4) OR (h1 AND Nh2 AND h3 AND h4) OR (Nh1 AND h2 AND Nh3 AND h4) OR (Nh2

AND Nh3 AND Nh4) OR (h1 AND h2 AND Nh4) OR (h1 AND Nh2 AND Nh3);

e <= (Nh1 AND h3 AND Nh4) OR (h1 AND h2 AND Nh3 AND h4) OR (h1 AND Nh2 AND

h3 AND h4) OR (h1 AND h2 AND h3) OR (Nh2 AND Nh3 AND Nh4) OR (h1 AND h2 AND

Nh4) OR (h1 AND Nh2 AND Nh4);

f <= (Nh1 AND h2 AND Nh4) OR (h1 AND Nh2 AND h3 AND h4) OR (Nh1 AND h2 AND

Nh3 AND h4) OR (h1 AND h2 AND h3) OR (Nh2 AND Nh3 AND Nh4) OR (h1 AND h2

AND Nh4) OR (h1 AND Nh2 AND Nh3) OR (h1 AND Nh2 AND Nh4);

g <= (Nh1 AND Nh2 AND h3) OR (Nh1 AND h2 AND Nh4) OR (h1 AND h2 AND Nh3 AND

h4) OR (h1 AND Nh2 AND h3 AND h4) OR (Nh1 AND h2 AND Nh3 AND h4) OR (h1 AND

h2 AND h3) OR (h1 AND Nh2 AND Nh3) OR (h1 AND Nh2 AND Nh4);

END bdf_type;

---------------------------------------------------------------------------

wybor.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY wybor IS

PORT

(

d : IN STD_LOGIC;

o : IN STD_LOGIC;

PBo : IN STD_LOGIC;

PBd : IN STD_LOGIC;

h : IN STD_LOGIC;

seg : OUT STD_LOGIC

);

END wybor;

ARCHITECTURE bdf_type OF wybor IS

SIGNAL

NPBo : STD_LOGIC;

SIGNAL

NPBd : STD_LOGIC;

BEGIN

NPBo <= NOT(PBo);

NPBd <= NOT(PBd);

seg <= (NPBo AND PBd AND o) OR (NPBd AND PBo AND d) OR (PBo AND PBd AND h);

END bdf_type;

---------------------------------------------------------------------------

13

tc.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY TC IS

PORT

(

A : IN STD_LOGIC;

B : IN STD_LOGIC;

C : IN STD_LOGIC;

D : IN STD_LOGIC;

E : IN STD_LOGIC;

F : IN STD_LOGIC;

G : IN STD_LOGIC;

H : IN STD_LOGIC;

oct : IN STD_LOGIC;

dec : IN STD_LOGIC;

a1 : OUT STD_LOGIC;

b1 : OUT STD_LOGIC;

c1 : OUT STD_LOGIC;

d1 : OUT STD_LOGIC;

e1 : OUT STD_LOGIC;

f1 : OUT STD_LOGIC;

g1 : OUT STD_LOGIC;

a2 : OUT STD_LOGIC;

b2 : OUT STD_LOGIC;

c2 : OUT STD_LOGIC;

d2 : OUT STD_LOGIC;

e2 : OUT STD_LOGIC;

f2 : OUT STD_LOGIC;

g2 : OUT STD_LOGIC

);

END TC;

ARCHITECTURE bdf_type OF TC IS

COMPONENT konwersja

PORT(A : IN STD_LOGIC;

B : IN STD_LOGIC;

C : IN STD_LOGIC;

D : IN STD_LOGIC;

E : IN STD_LOGIC;

F : IN STD_LOGIC;

G : IN STD_LOGIC;

H : IN STD_LOGIC;

c24 : OUT STD_LOGIC;

c23 : OUT STD_LOGIC;

c22 : OUT STD_LOGIC;

c21 : OUT STD_LOGIC;

c14 : OUT STD_LOGIC;

c13 : OUT STD_LOGIC;

c12 : OUT STD_LOGIC;

c11 : OUT STD_LOGIC;

ok : OUT STD_LOGIC

);

END COMPONENT;

COMPONENT dec_seg

14

PORT(d1 : IN STD_LOGIC;

d2 : IN STD_LOGIC;

d3 : IN STD_LOGIC;

d4 : IN STD_LOGIC;

ok : IN STD_LOGIC;

a : OUT STD_LOGIC;

b : OUT STD_LOGIC;

c : OUT STD_LOGIC;

d : OUT STD_LOGIC;

e : OUT STD_LOGIC;

f : OUT STD_LOGIC;

g : OUT STD_LOGIC

);

END COMPONENT;

COMPONENT okt_seg

PORT(o1 : IN STD_LOGIC;

o2 : IN STD_LOGIC;

o3 : IN STD_LOGIC;

ok : IN STD_LOGIC;

a : OUT STD_LOGIC;

b : OUT STD_LOGIC;

c : OUT STD_LOGIC;

d : OUT STD_LOGIC;

e : OUT STD_LOGIC;

f : OUT STD_LOGIC;

g : OUT STD_LOGIC

);

END COMPONENT;

COMPONENT hex_seg

PORT(h1 : IN STD_LOGIC;

h2 : IN STD_LOGIC;

h3 : IN STD_LOGIC;

h4 : IN STD_LOGIC;

a : OUT STD_LOGIC;

b : OUT STD_LOGIC;

c : OUT STD_LOGIC;

d : OUT STD_LOGIC;

e : OUT STD_LOGIC;

f : OUT STD_LOGIC;

g : OUT STD_LOGIC

);

END COMPONENT;

COMPONENT wybor

PORT(PBo : IN STD_LOGIC;

PBd : IN STD_LOGIC;

o : IN STD_LOGIC;

d : IN STD_LOGIC;

h : IN STD_LOGIC;

seg : OUT STD_LOGIC

);

END COMPONENT;

SIGNAL

NA : STD_LOGIC;

SIGNAL

NB : STD_LOGIC;

SIGNAL

NC : STD_LOGIC;

SIGNAL

ND : STD_LOGIC;

SIGNAL

NE : STD_LOGIC;

15

SIGNAL

NF : STD_LOGIC;

SIGNAL

NG : STD_LOGIC;

SIGNAL

NH : STD_LOGIC;

SIGNAL

okt_ok : STD_LOGIC;

SIGNAL

d1a : STD_LOGIC;

SIGNAL

d1b : STD_LOGIC;

SIGNAL

d1c : STD_LOGIC;

SIGNAL

d1d : STD_LOGIC;

SIGNAL

d1e : STD_LOGIC;

SIGNAL

d1f : STD_LOGIC;

SIGNAL

d1g : STD_LOGIC;

SIGNAL

d2a : STD_LOGIC;

SIGNAL

d2b : STD_LOGIC;

SIGNAL

d2c : STD_LOGIC;

SIGNAL

d2d : STD_LOGIC;

SIGNAL

d2e : STD_LOGIC;

SIGNAL

d2f : STD_LOGIC;

SIGNAL

d2g : STD_LOGIC;

SIGNAL

o1a : STD_LOGIC;

SIGNAL

o1b : STD_LOGIC;

SIGNAL

o1c : STD_LOGIC;

SIGNAL

o1d : STD_LOGIC;

SIGNAL

o1e : STD_LOGIC;

SIGNAL

o1f : STD_LOGIC;

SIGNAL

o1g : STD_LOGIC;

SIGNAL

o2a : STD_LOGIC;

SIGNAL

o2b : STD_LOGIC;

SIGNAL

o2c : STD_LOGIC;

SIGNAL

o2d : STD_LOGIC;

SIGNAL

o2e : STD_LOGIC;

SIGNAL

o2f : STD_LOGIC;

SIGNAL

o2g : STD_LOGIC;

SIGNAL

h1a : STD_LOGIC;

SIGNAL

h1b : STD_LOGIC;

SIGNAL

h1c : STD_LOGIC;

SIGNAL

h1d : STD_LOGIC;

SIGNAL

h1e : STD_LOGIC;

SIGNAL

h1f : STD_LOGIC;

SIGNAL

h1g : STD_LOGIC;

SIGNAL

h2a : STD_LOGIC;

SIGNAL

h2b : STD_LOGIC;

SIGNAL

h2c : STD_LOGIC;

SIGNAL

h2d : STD_LOGIC;

SIGNAL

h2e : STD_LOGIC;

SIGNAL

h2f : STD_LOGIC;

SIGNAL

h2g : STD_LOGIC;

SIGNAL

dec_ok : STD_LOGIC;

SIGNAL

c11 : STD_LOGIC;

SIGNAL

c12 : STD_LOGIC;

SIGNAL

c13 : STD_LOGIC;

SIGNAL

c14 : STD_LOGIC;

SIGNAL

c21 : STD_LOGIC;

SIGNAL

c22 : STD_LOGIC;

SIGNAL

c23 : STD_LOGIC;

SIGNAL

c24 : STD_LOGIC;

SIGNAL

a1 : STD_LOGIC;

SIGNAL

b1 : STD_LOGIC;

SIGNAL

c1 : STD_LOGIC;

SIGNAL

d1 : STD_LOGIC;

SIGNAL

e1 : STD_LOGIC;

SIGNAL

f1 : STD_LOGIC;

16

SIGNAL

g1 : STD_LOGIC;

SIGNAL

a2 : STD_LOGIC;

SIGNAL

b2 : STD_LOGIC;

SIGNAL

c2 : STD_LOGIC;

SIGNAL

d2 : STD_LOGIC;

SIGNAL

e2 : STD_LOGIC;

SIGNAL

f2 : STD_LOGIC;

SIGNAL

g2 : STD_LOGIC;

BEGIN

NA <= NOT(A);

NB <= NOT(B);

NC <= NOT(C);

ND <= NOT(D);

NE <= NOT(E);

NF <= NOT(F);

NG <= NOT(G);

NH <= NOT(H);

b2v_inst : konwersja

PORT MAP(A => NA,

B => NB,

C => NC,

D => ND,

E => NE,

F => NF,

G => NG,

H => NH,

c24 => c24,

c23 => c23,

c22 => c22,

c21 => c21,

c14 => c14,

c13 => c13,

c12 => c12,

c11 => c11,

ok => dec_ok);

b2v_inst8 : dec_seg

PORT MAP(d1 => c11,

d2 => c12,

d3 => c13,

d4 => c14,

ok => dec_ok,

a => d1a,

b => d1b,

c => d1c,

d => d1d,

e => d1e,

f => d1f,

g => d1g);

b2v_inst9 : dec_seg

PORT MAP(d1 => c21,

d2 => c22,

d3 => c23,

d4 => c24,

17

ok => dec_ok,

a => d2a,

b => d2b,

c => d2c,

d => d2d,

e => d2e,

f => d2f,

g => d2g);

okt_ok <= NA OR NB;

b2v_inst10 : okt_seg

PORT MAP(o1 => NC,

o2 => ND,

o3 => NE,

ok => okt_ok,

a => o1a,

b => o1b,

c => o1c,

d => o1d,

e => o1e,

f => o1f,

g => o1g);

b2v_inst11 : okt_seg

PORT MAP(o1 => NF,

o2 => NG,

o3 => NH,

ok => okt_ok,

a => o2a,

b => o2b,

c => o2c,

d => o2d,

e => o2e,

f => o2f,

g => o2g);

b2v_inst13 : hex_seg

PORT MAP(h1 => NA,

h2 => NB,

h3 => NC,

h4 => ND,

a => h1a,

b => h1b,

c => h1c,

d => h1d,

e => h1e,

f => h1f,

g => h1g);

b2v_inst14 : hex_seg

PORT MAP(h1 => NE,

h2 => NF,

h3 => NG,

h4 => NH,

a => h2a,

18

b => h2b,

c => h2c,

d => h2d,

e => h2e,

f => h2f,

g => h2g);

b2v_inst15 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o1a,

d => d1a,

h => h1a,

seg => a1);

b2v_inst16 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o1b,

d => d1b,

h => h1b,

seg => b1);

b2v_inst17 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o1c,

d => d1c,

h => h1c,

seg => c1);

b2v_inst18 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o1d,

d => d1d,

h => h1d,

seg => d1);

b2v_inst19 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o1e,

d => d1e,

h => h1e,

seg => e1);

b2v_inst20 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o1f,

d => d1f,

h => h1f,

seg => f1);

19

b2v_inst21 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o1g,

d => d1g,

h => h1g,

seg => g1);

b2v_inst22 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o2a,

d => d2a,

h => h2a,

seg => a2);

b2v_inst23 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o2b,

d => d2b,

h => h2b,

seg => b2);

b2v_inst24 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o2c,

d => d2c,

h => h2c,

seg => c2);

b2v_inst25 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o2d,

d => d2d,

h => h2d,

seg => d2);

b2v_inst26 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o2e,

d => d2e,

h => h2e,

seg => e2);

b2v_inst27 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o2f,

d => d2f,

h => h2f,

20

seg => f2);

b2v_inst28 : wybor

PORT MAP(PBo => oct,

PBd => dec,

o => o2g,

d => d2g,

h => h2g,

seg => g2);

a1 <= NOT(a1);

b1 <= NOT(b1);

c1 <= NOT(c1);

d1 <= NOT(d1);

e1 <= NOT(e1);

f1 <= NOT(f1);

g1 <= NOT(g1);

a2 <= NOT(a2);

b2 <= NOT(b2);

c2 <= NOT(c2);

d2 <= NOT(d2);

e2 <= NOT(e2);

f2 <= NOT(f2);

g2 <= NOT(g2);

END bdf_type;

Wyszukiwarka

Podobne podstrony:

8051 wyswietlacz 7seg

8051 wyswietlacz 7seg

8051 wyswietlacz 7seg

Wyświetlanie tekstu na ekranie

Znakowe wyświetlacze VFD

Kolejny miernik na ICL7107 i wyświetlaczach LED wspólna anoda schemat

cw7 BCD 2 7SEG

Jak wyświetlić zawartość katalogu jako linki służące do pobrania plików, PHP Skrypty

Obsługa wyświetlacza Lcd z układem sterowania Hd44780U

Aplikacja wyświetlacza VFD

Woltomierz, amperomierz i watomierz z wyświetlaczem Nokia5110

Wyświetl wiadomość tekstową przy logowaniu systemu

Realizacja funkcji na wyświetlaczu 8 segmetowym

lista komunikatów na wyświetlaczu

Daty w Excelu wyświetlane z nazwą dnia tygodnia

wymiana wyswietlacz na kolor p12

Wskazówka wyświetlana po kliknięciu komórki, Dokumenty(1)

więcej podobnych podstron