Ćw 1.

Podać metody eliminowania wpływu drżenia zastyków (8.04.2004 Kawalec).

Narysować układ eliminacji na elementach Nor (8.04.2004 Kawalec).

Narysuj schemat eliminacji drgań z użyciem NOR (RS).

Czy zawsze należy eliminować wpływ drgań?

Nie w żarówce nie trzeba bo ludzkie oko nie jest w stanie tego zobaczyć.

Narysować licznik Modulo 16.

Sposoby eliminowania wpływu drgań. układ formujący (przerzutnik RS), filtr dolnoprzepustowy i układ formujący, uniwibrator (gdy odp. Przełączania ma być impulsem)

Z badanego licznika zbudować licznik Modulo 5 podłączyć sygnały aby licznik był gotowy do zliczania.

Czy badany licznik był układem synchronicznym czy asynchronicznym

Wyjaśnić co to drżenie zestyków

Narysować na nandach i wyjaśnić dlaczego układ eliminujący wpływ drżenia zestyków na układ

Kiedy należy eliminować wpływ drżenia zestyków na współpracujące układy cyf.

Cechy jakie muszą mieć elementy pamięci zastosowane do badania zestyków

Ćw 2.

Porównać badane metody realizacji ukł. kombinacyjnych (8.04.2004 Kawalec).

Różnice między implikantem a zasadniczym układem prostym (8.04.2004 Kawalec).

Zrealizować na decoderach i elementach logicznych funkcję y=Σ (0,5,15,20,25)

(15.04.2004 Kawalec).

Podać sposoby usuwania hazardu dynamicznego (15.04.2004 Kawalec).

Różnice pomiędzy hazardem statycznym a dynamicznym, jak usuwamy.

Metoda realizacji funkcji logicznych.

Opisać i porównać metody minimalizacji. (firląg)

Zbudować najprostszy multiplekser dla y=∏ (0,3).

Przyczyna występowania hazardu

Sprawdzić czy występuje hazard:

Co to jest system funkcjonalnie pełny i które funkcje z pośród 2 zmiennych samodzielnie tworzą system.

Co to dekoder, rodzaje i jak działa

Podaną funkcję zrealizować na multiplekserze y=Σ [1,3,8,10,19,23,28,(4,9,17,20,27)]

Ćw 3.

Różnice między automatem Moora a Mealy'ego (7.04.2004 Kawalec).

Zaprojektować licznik modulo 3 z przerzutników JK i Nand, Not (8.04.2004 Kawalec).

Wyjaśnić dlaczego do kodowania stosuje się podziały wyłącznie dwublokowe (15.04.2004 Kawalec).

Wyjaśnić zależność między ceną układu a jego złożonością (15.04.2004 Kawalec).

Wyjaśnić czy do kodowania mogą być stosowane podziały nieprawidłowe (odp. można) (15.04.2004 Kawalec-poprawa).

Wyjaśnić i porównać automaty elementarne (przerzutniki) (15.04.2004 Kawalec-poprawa).

Co to jest rodzina końcowa i rodzina końcowa optymalna?

Napisać różnice między automatem Millego - Moorego. (jedna podstawowa różnica)

Czy podział niewłaściwy może być wzięty do rodziny końcowej?

Różnice miedzy układem kombinacyjnym a sekwencyjnym.

Cena układu- jak się liczy.

Podać sposoby opisu układów sekwencyjnych.

Do czego służy i z czego budujemy pamięć układu (sekwencyjnego), ile elementów pamięciowych będzie miał układ o 8 różnych stanach wewnętrznych.

Jakie podziały nazywamy prawidłowymi.

Czy do kodowania automatów synchronicznych możemy wykorzystać podziały nieprawidłowe.

Wyjaśnić różnice między automatami moorea i mealego.

Wyjaśnić jak liczymy cenę rodziny końcowej dla automatu moorea.

Obliczyć cenę w automacie Meale'go / Moore'a.

Dlaczego rachunek podziału wpływa na uproszczenie układu?

Dany automat Mealye'go:

Tk=(τ12 τ13 τ34) wyznaczyć cenę wyjść.Co określa wielkość pamięci synchronicznych ukł sekwencyjnych i jaka będzie wielkość dla licznika Modulo 10 (Moore'a).

sposoby opisu synchronicznych automatów sekwencyjnych

czy podział tał może być prawidłowy

jak nazywamy najmniejszy i największy podział

czy podziały nieprawidłowe mogą być używane do tworzenia …nie rozumiem czego..?

dany aut.moore'a, 5 stanów, 1 WE, 1 WY, i(y)=0. Podać cenę układu przy założeniu że podziały zamykają się na sobie (te w rodzinie końcowej)

Ćw 4.

Podać założenia przy których prowadzona jest synteza ukł asynchro (8.04.2004 Kawalec).

Wyjaśnić pojęcie warunków separacji (8.04.2004 Kawalec).

Wyjaśnić pojęcie stanów niestabilnych (15.04.2004 Kawalec).

Podać sposoby realizacji układów asynchronicznych (15.04.2004 Kawalec).

Porównać metody realizacji układów.

Cechy wykresów czasowych.

Wyścig, wyścig krytyczny i wyścig niekrytyczny.

Narysować i wyjaśnić strukturę automatów synchronicznych.

Jak rozpoznać czy automat jest synchroniczny czy asynchroniczny

Założenia przy jakich prowadzona jest synteza automatów asynchronicznych

Czy podziały nieprawidłowe mogą być w rodzinie końcowej

Co to wyścig(?) w układach synchronicznych- rodzaje i kiedy występuje

Czy tał może być nieprawidłowy

W jaki sposób eliminujemy/wykrywamy wyścigi niekrytyczne

Ćw 5.

Obliczyć rezystancję. Odp Ucc=5, Ud=2, Id=16mA=0,016, R=180 (8.04.2004 Kawalec).

Narysować poprawnie schemat (8.04.2004 Kawalec).

Obliczyć punkt pracy Diody.

Narysować i wyjaśnić właściwy sposób podłączenia diody święcącej do wyjścia układu z rodziny TTL.

Podać zasady budowy układów cyfrowych ze standardowych układów scalonych.

Czy suma logiczna i negacja stanowią system funkcjonalny pełny?

Obciążalność bramki.

Wyjaśnić formowanie impulsów poprzez układy cyfrowe.

Sygnały priorytetowe na przerzutnikach sekwencyjnych JK.

Punkt pracy Diody opisać.

Zrealizować na NANDach funkcję logiczną Xsar.

Narysować układ sygnalizacji stanu wyjaśnić na diodzie świecącej i wyznaczyć punkt pracy diody znając prąd znamionowy I=20μA spadek napięcia na diodzie 1,2V.

Zbudować z dowolnych elementów dzielnik częstotliwości przez 2

Udowodnić że suma i negacja stanowią system funkcjonalnie pełny.

Co to jest system funkcjonalny pełny i jak to sprawdzić.

Wyznaczyc rezystancję w obwodzie diody świecądej przy założeniach: spadek napięcia, prąd diody, napięcie.

W jaki sposób udowadniamy że jakieś operatory stanowią system funkcjonalnie pełny

Udowodnić że nand stanowi system funkcjonalnie pełny

Daną funkcję narysować na norach

Różnica między językami opisu sprzętu(?) a językami programowania

Jakie cechy musi posiadać identyfikator jednostki projektowej lub architektury

Porównać znane sposoby minimalizacji

Narysować i uzasadnić sposób podłączenia diody świecącej do wyjścia układu cyfrowego

Ćw 6.

Wyspecyfikować dekoder 1 wejściowy (7.04.2004 Kawalec).

Powiązanie architektury i jednostki projektowej (7.04.2004 Kawalec).

Wyjaśnić różnicę między językiem programowania a językiem opisu sprzętu

(8.04.2004 Kawalec).

Wyspecyfikować 3 wejściową bramkę NOR (8.04.2004 Kawalec).

Wyspecyfikować dekoder 1 wejściowy 1 z n (15.04.2004 Kawalec).

Różnica między bit a std_logic (15.04.2004 Kawalec).

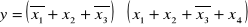

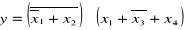

Napisać program VHDL do rysunku:

Odp: ![]()

.

Wyjaśnić listę czułości i podać w jakim typie instrukcjach ona występuje.

Współbieżne i sekwencyjne języki.

.Wyjaśnić różnicę między językiem programowania a językiem opisu sprzętu.

W edytorze tekstowym wyspecyfikować wykorzystując „ if ” dwuwejściową bramkę NOR.

W języku VHDL w najprostszy sposób zdestabilizować dwu wejściową bramkę NAND.

Wyjaśnić różnice pomiędzy językami opisami sprzętu, a językami programowania.

Różnica między językami opisu sprzętu(?) a językami programowania

Jakie cechy musi posiadać identyfikator jednostki projektowej lub architektury

Zgodnie z zasadami ( jak w komputerze) narysować graf układu który w dowolnie długim ciągu wykryje 00110- aut. Moorea

Wypisać różnice pomiędzy grafami automatów synchronicznych i asynchronicznych

W vhdlu wyspecyfikować układ realizujący funkcję (cały program)

Napisać jak wykonaliście implementację swojego układu(rodzina itd.)

Ćw 7.

Różnice między wyjściem kombinowanym a rejestrowym.

Wyspecyfikować w edytorze FSM układ wykorzystujący w dowolnie długim ciągu sekwencję 110.

Różnice między automatem Mealye'go a Moore'a

Licznik Modulo 4 (graf)

Sposób tworzenia grafów

Różnice w funkcji wyjść w obu automatach

Jakie są ułatwienia w FSM (odp @else, dvstate)

Różnicę między grafem synchronicznym a asynchronicznym.

Zgodnie z zasadami edytora ssm(?) wyspecyfikować układ który w dowolnie długim ciągu binarnym podawanym na we wykryje 0110- moore

Podać zasady tworzenia synchronicznych grafów przejść dla moora i mealyego

Ćw 8.

Suma 91+12

20-30 w u1 i u2

Różnice między mnożeniem sz-r a unitarnym.

Narysować ALU.

Bloki funkcjonalne w ALU (2003 Kawalec).

Opisać mnożenie unitarne (szeregowo - równoległe) (2003 Kawalec).

Wyszukiwarka

Podobne podstrony:

Metrologia, odpowiedzi na pytania z laboratorium, Lab 2

pytania laboratorium

3 pytania z laboratorium wytrz. mat zaoczni. 067, Akademia Morska -materiały mechaniczne, szkoła

pytania laboratoryjne tzizc 2013

Pytania, Laboratorium Napędu Elektrycznego

Mechanika płynów Laborki, Laboratoria z Mechaniki Płynów - matlak - pytania, Laboratoria z Mechaniki

opracowane pytania z laboratorium

Wahadło matemtyczne cw1 opracowane pytania Laboratorium Fizyka

Pytania z laboratorium techniki cyfrowej, pytania

pytania z laborat, fizyka(15)

pytania do keta wszyastkie, TC

Elektroenergetyka pytania na zal laboratorium, Nauka i Technika, Elektroenergetyka

Laboratorium 1 pytania

,laboratorium podstaw fizyki, pytania do laborek

nieorgany-pytania2, Studia - Chemia kosmetyczna UŁ, II rok, III semestr, CHEMIA NIEORGANICZNA labora

Pytania Diagnostyka Laboratoryjna skonsolidowane egz i zal do 11 włącznie

PYTANIA ZALICZENIOWE Laboratoryjna

pytania TMC, pytania sprezarka, Laboratorium „Termodynamika”

IBN Pytania na ćwiczenia laboratoryjne z chemii

więcej podobnych podstron