Bramka trójstanowa, bramka TS (ang. three-state) - jest to bramka logiczna, która na wyjściu, oprócz dwóch stanów logicznych (0 i 1 logicznej), może przyjmować stan logicznie nieokreślony. Stan ten nazywany jest stanem wysokiej impedancji i oznaczany jest (Z).

Bramki trójstanowe, oprócz standardowych wejść, posiadają również wejście dodatkowe S.

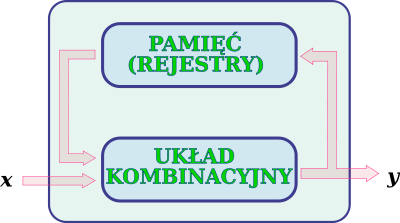

Układ sekwencyjny jest jednym z rodzajów układów cyfrowych. Charakteryzuje się tym, że stan wyjść y zależy od stanu wejść x oraz od poprzedniego stanu, zwanego stanem wewnętrznym, pamiętanego w zespole rejestrów (pamięci).

Jeżeli stan wewnętrzny nie ulega zmianie pod wpływem podania różnych sygnałów X, to taki stan nazywa się stabilnym.

Rozróżnia się dwa rodzaje układów sekwencyjnych:

asynchroniczne

synchroniczne

Układ kombinacyjny jest jednym z rodzajów układów cyfrowych. Charakteryzuje się tym, że stan wyjść zależy wyłącznie od stanu wejść; stan wyjść opisują funkcje boolowskie - w przeciwieństwie do układów sekwencyjnych, których stan wyjść zależy od stanu wejść oraz od poprzedniego stanu wyjść. W układach kombinacyjnych nie występuje sprzężenie zwrotne.

Multiwibrator - układ elektroniczny, zrealizowany w oparciu o przekaźniki elektromechaniczne, lampy (w tym neonówki), tranzystory, diody tunelowe bądź inne elementy przełączające, posiadający dwa lub więcej stanów równowagi trwałej bądź nietrwałej.

Multiwibrator dwustanowy monostabilny - czyli uniwibrator - jest to multiwibrator o jednym stanie równowagi trwałej i jednym nietrwałej.

ACTIVE - CAD firmy ALDEC jest pakietem umożliwiającym projektowanie

układów cyfrowych oraz symulację ich działania zarówno w trybie funkcjonalnym,

pozwalającym na badanie zależności logicznych, jak i w trybie czasowym,

umożliwiającym uwzględnienie czasów propagacji sygnałów w poszczególnych

elementach logicznych. Program ten pozwala stosować następujące sposoby specyfikacji projektowanych układów:

przy pomocy edytora schematów (Schematic Capture), umożliwiającego tworzenie schematów ideowych budowanych układów;

przy pomocy grafów przejść automatów skończonych FSM (Finite State Machine );

przy użyciu języka opisu sprzętu VHDL.

Oznaczenie

Funkcja

Symbol

Tabela prawd

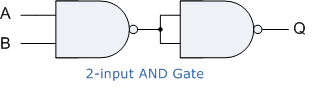

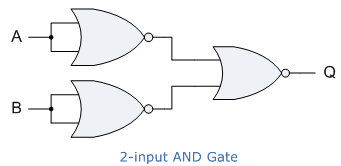

AND

W = A B

A |

B |

W |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

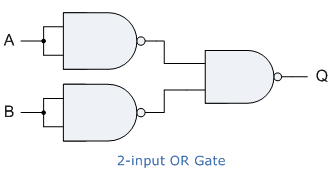

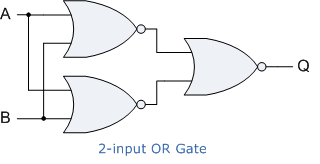

OR

W = A + B

A |

B |

W |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

NAND

___

W = A B

A |

B |

W |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

NOR

____

W = A + B

A |

B |

W |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

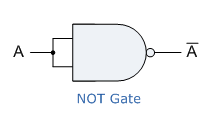

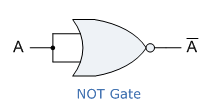

NOT

_

W = A

A |

B |

W |

0 |

0 |

1 |

0 |

1 |

0 |

XOR (exclusive or)

_ _

W = A B + A B

A |

B |

W |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

XNOR (exclusive nor)

_ _

W = A B + A B

A |

B |

W |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Realizacja przerzutników synchronicznych.

JKT

|

JKD

|

DJK

|

Wyszukiwarka

Podobne podstrony:

spr 23 moje, Szkoła, Semestr 4, Podstawy elektroniki

elektronika ćw 4- tyrystor i trika, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektron

sprawko ćw2, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektroniki LAB, Podstawy Elekt

ćw 26 - sprawko moje, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektroniki LAB, Podst

sprawko z diody, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektroniki LAB, Podstawy E

ćw 26 - sprawko moje kopia, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektroniki LAB,

elektronika 22, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektroniki LAB, Podstawy El

Cw 6 elektronika h&j, Szkoła, Semestr 4, Podstawy elektroniki, Ćw. 6

sprawko ćw4, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektroniki LAB, Podstawy Elekt

tyrystor, Szkoła, Semestr 4, Podstawy elektroniki, Ćw. 4

Sprawozdanie I 4 Tyrystor i Triak (II), Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elek

sprawko ćw 6, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektroniki LAB, Podstawy Elek

aaaasas, Szkoła, Semestr 4, Podstawy elektroniki, Bart

strona tytulowa elektronika, Szkoła, Semestr 4, Podstawy elektroniki, Bart, Podstawy Elektroniki LAB

Z2, Szkoła, Semestr 5, Podstawy Automatyki - laboratoria, Automaty lab, Automaty, Zestawy

sprawko pbm, Szkoła, Semestr 2, Podstawy Budowy Maszyn I, PBM'y

Moja ściąga 2. kolos, Szkoła, Semestr 4, Podstawy automatyki

Z9, Szkoła, Semestr 5, Podstawy Automatyki - laboratoria, Automaty lab, Automaty, Zestawy

Część I, Szkoła, Semestr 2, Podstawy Budowy Maszyn I, Spawanko, Spawanie, Sprawko Spawanie, Sprawko

więcej podobnych podstron