Laboratorium z Elektrotechniki

Ćwiczenie nr 3.

Temat: Badanie podstawowych elementów logicznych oraz układów przerzutników.

Układy elektroniczne, których sygnały wyjściowe są funkcjami logicznymi sygnałów wejściowych noszą nazwę układów logicznych. W układach logicznych są realizowane operacje logiczne. Wykorzystuje się aparat algebry Boole'a jako że jest on najdogodniejszy do analizy elektronicznych obwodów przełączających, czyli obwodów, w których daje się łatwo wyróżnić dwa stany:

stan niski L, utożsamiany w logice dodatniej z zerem logicznym,

stan wysoki H, utożsamiany w logice dodatniej z jedynką logiczną.

Podstawowym zadaniem układów logicznych jest przetwarzanie sygnałów binarnych, czyli sygnałów dających się przedstawić w postaci ciągów zer i jedynek logicznych, na przykład w celu wykonywania operacji logicznych i arytmetycznych, a także sterowanie strumieniem danych w mikrokomputerach.

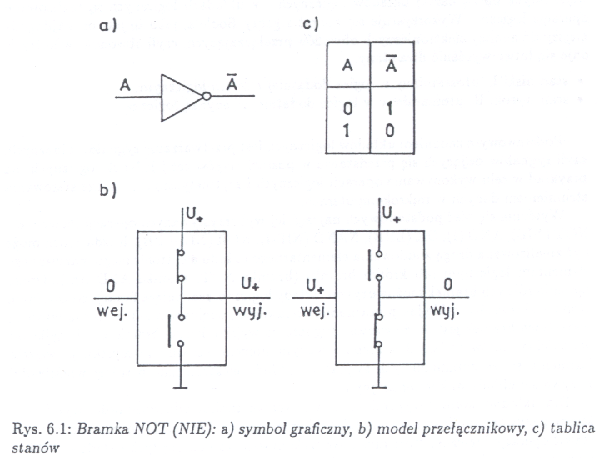

Bramka NOT (NIE). Bufor

Operację inwersji, czyli operację negacji, oznacza się kreseczką nad poddawaną inwersji wielkości. Przykładowo „NIE A” zapisuje się jako A. Operacja ta jest realizowana

w elemencie nazwanym bramką NOT (NIE) lub inwerterem. Symbol graficzny bramki NOT (NIE), jej model przełącznikowy, a także tablicę stanów pokazano na rysunku6.1.

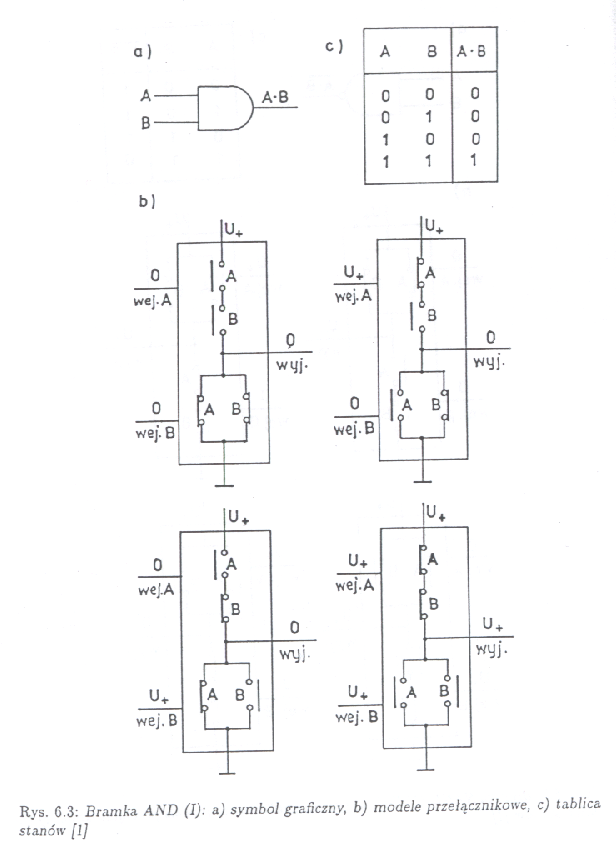

Bramka AND (I)

Symbol graficzny bramki AND (I), modele przełącznikowe dla wszystkich możliwych kombinacji sygnałów wejściowych oraz tablicę stanów pokazano na rysunku 6.3. Bramka AND (I) realizuję operację iloczynu logicznego oznaczaną kropką (jak przy zwykłym mnożeniu), czytaną jak spójnik „i”. Tak więc A B jest iloczynem logicznym wielkości A i B - czyta się A i B.

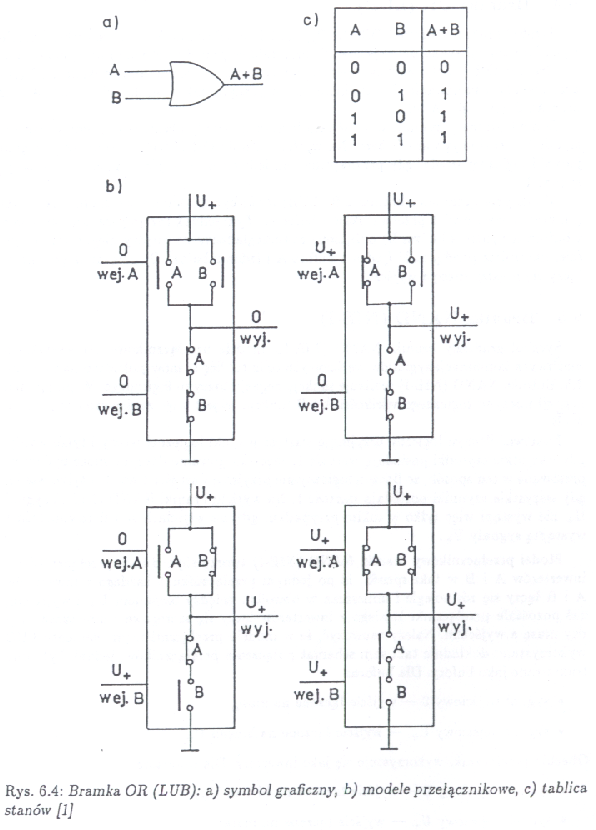

Bramka OR (LUB)

Symbol graficzny bramki OR (LUB), modele przełącznikowe dla wszystkich możliwych kombinacji sygnałów wejściowych oraz tablicę prawdy pokazano na rysunku 6.4.

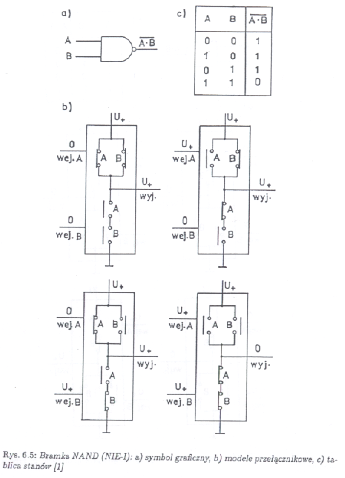

Bramka NAND (NIE - I)

Symbol graficzny bramki NAND (NIE - I), modele przełącznikowe dla wszystkich możliwych kombinacji sygnałów wejściowych oraz tablicę stanów pokazano na rysunku 6.5. Bramka NAND (NIE - I) realizuje funkcję negacji iloczynu logicznego. W przypadku negacji iloczynu logicznego wielkości A i B funkcja ta jest więc zapisywana w postaci: A B.

Badanie podstawowych układów przerzutników.

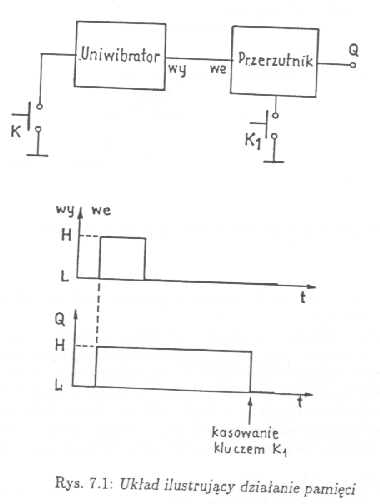

Element pamięci charakteryzuje się tym, że zachowuj swój stan wyjściowy po zaniku przyczyny, która ten stan spowodowała. Podstawowymi układami pamięci są przerzutniki stanowiące elementy liczników i rejestrów.

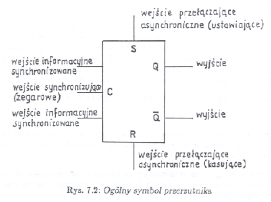

Przerzutnik jest układem o dwóch wyjściach komplementarnych (Q,Q) oraz o pięciu wejściach.

W przerzutniku można wyróżnić następujące wejścia:

wejścia informacyjne synchronizowane przebiegiem synchronizującym (zegarowym),

wejścia programujące asynchronicznie,

wejścia synchronizujące (zegarowe).

Wejścia informacyjne synchronizowane mają tę własność, że nie powodują natychmiastowej zmiany stanu wyjścia. Zmiana wartości wyjść przerzutnika - pod wpływem zmian wartości na wejściach informacyjnych synchronizowanych - następuje w takt impulsu zegarowego. Oznacza to, że informacja z tych wejść może być wpisana do przerzutnika tylko w pewnych określonych momentach czasowych. Momenty te wyznacza sygnał zegarowy.

Ze względu na sposób oddziaływania wejść informacyjnych na stan przerzutnika, przerzutniki dzielimy na dwie grupy:

przerzutniki jednowejściowe (np. typu D),

przerzutniki dwuwejściowe (np. typu JK).

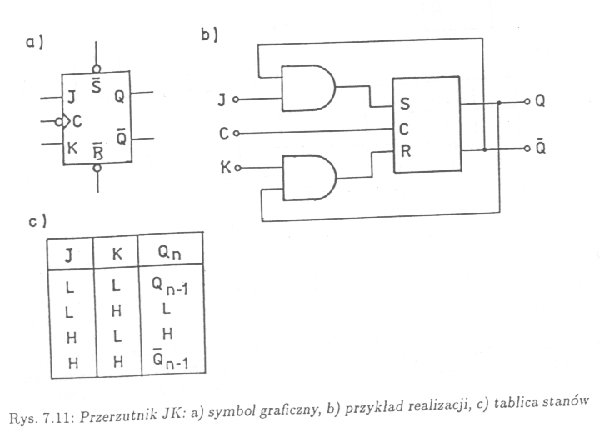

Przerzutnik JK ma dwa wejścia informacyjne J i K, wejście zegarowe C oraz wejścia R i S służące tylko do ustawiania i zerowania przerzutnika. W normalnym trybie pracy przerzutnika S = 1 i R = 1.

W przerzutniku JK dopuszcza się aby na obu wejściach występował jednocześnie stan wysoki. Ustawianie i kasowanie przerzutnika odbywa się w chwili, gdy sygnał zegarowy zmieni stan z poziomu wysokiego na niski. Przełączanie przerzutnika JK zboczem opadającym sygnału zegarowego jest symbolizowane przez kółeczko negacji na wejściu zegarowym C.

Wnioski:

W modelu przełącznikowym bramki AND (I) wykorzystuje się dwa przełączniki - bufory

A i B połączone w taki sposób, że po jednym przełączniku z każdego z buforów A i B połączono szeregowo i włączono między biegun U+ i wyjście, zaś pozostałe przełączniki

z każdego z buforów połączono równolegle i włączono między masę a wyście. Tak więc

w przypadku bramki AND (I) iloczyn logiczny przyjmuje wartość jedynki logicznej wtedy

i tylko wtedy, gdy wszystkie czynniki posiadają wartość 1. Na wyjściu bramki AND (I) wystąpi sygnał 1, gdy na wszystkich jej wejściach równocześnie pojawią się sygnały 1.

W przypadku przerzutnika JK, kiedy to na wejściach J i K istniał niski poziom napięcia, to stan wyjścia nie ulegał zmianie pomimo zmiany sygnału zegarowego. Natomiast w przypadku gdy na wejściu J istniał niski poziom napięcia a na wejściu K występował wysoki poziom przerzutnik był kasowany (Q = 0) w chwili wystąpienia zbocza odpadającego sygnału zegarowego. W sytuacji odwrotnej tzn. gdy J = 1 i K = 0 nastąpiło ustawienie przerzutnika

(Q = H). Informacja z wejścia J była przesyłana na wyjście w momencie wystąpienia odpadającego zbocza sygnału zegarowego. Dla kombinacji wejść J = 0 i K = 1 oraz J = 1 i K = 0 przerzutnik JK pełnił funkcję elementu pamiętającego. Jeżeli J = 1 i K = 1 to stan wyjść zmieniał się na przeciwny w czasie impulsu zegarowego.

Wyszukiwarka

Podobne podstrony:

NIEUSTAL, LABORATORIUM ELEKTROTECHNIKI TEORETYCZNEJ

Elektra c, Elektrotechnika teoretyczna

Elektra e, Elektrotechnika, Elektrotechnika teoretyczna

Elektra h, Elektrotechnika, Elektrotechnika teoretyczna

literatura Podstawy Elektrotechniki Teoretycznej

Elektra p, Elektrotechnika, Elektrotechnika teoretyczna

Elektra n, Elektrotechnika, Elektrotechnika teoretyczna

Elektra k, Elektrotechnika teoretyczna

Elektra l, Elektrotechnika, Elektrotechnika teoretyczna

Egzamin z Elektrotechniki Teoretycznej II, Egzamin z Elektrotechniki Teoretycznej II - 29

Elektra j, Elektrotechnika teoretyczna

literatura Podstawy Elektrotechniki Teoretycznej

2012 01 Elektromechanik Pojazdów Samochodowych Teoretyczny

Drgania elektryczne (2), Wprowadzenie teoretyczne

więcej podobnych podstron