Temat: Sumator-Subtraktor

Celem ćwiczenia jest zapoznanie się z budową oraz zasadą działania układu dodająco-odejmującego liczby binarne.

Zagadnienia do sprawdzianu:

funkcje logiczne, bramki logiczne

budowa tablic prawdy

budowa tablic Karnaugh

minimalizacja funkcji na podstawie tablic Karnaugh

realizacja funkcji logicznych w oparciu o bramki logiczne

zasada działania sumatora/subtraktora

Przebieg ćwiczenia:

Pełny jednobitowy sumator binarny.

Wypełnić tablicę prawdy

Zdefiniować siatki Karnaugh

Dokonać minimalizacji funkcji:

Zrealizować pełny sumator jednobitowy liczb binarnych, przy pomocy bramek logicznych, w programie DSCH2

Korzystając z menu „Scheme to new symbol” utworzyć symbol pełnego sumatora jednobitowego.

Sprawdzić działanie pełnego sumatora jednobitowego. Jako sygnałów wejściowych należy zadawać odpowiednie stany logiczne na wejścia Ai, Bi i Ci, a następnie porównać otrzymane stany na wyjściu z założonymi w tabeli prawdy.

Pełny jednobitowy subtraktor (sumator odejmujący) binarny.

Wypełnić tablicę prawdy

Zdefiniować siatki Karnaugh:

Dokonać minimalizacji funkcji:

W wyrażeniach opisujących działanie sumatora odejmującego zamiast Bi wstawić Bi', a zamiast Ci wstawić Vi'.

Porównać otrzymane wyrażenia logiczne dla przeniesienia Vi+1' i różnicy Di w przypadku sumatora odejmującego z sumą Si i pożyczką Ci+1 dla sumatora. Jakie da się zauważyć zależności pomiędzy Di a Si oraz Vi+1' i Ci+1?

Zrealizować pełny subtraktor jednobitowy liczb binarnych, wykorzystując układ pełnego sumatora jednobitowego w programie DSCH2.

Korzystając z menu „Scheme to new symbol” utworzyć symbol pełnego subtraktora jednobitowego.

Sprawdzić działanie pełnego subtraktora jednobitowego. Poprzez zmianę stanów logicznych pinów wejściowych.

Sumator wielobitowy binarny.

Zrealizować czterobitowy sumator równoległy z przeniesieniami szeregowymi wykorzystując gotowe ogniwo pełnego sumatora jednobitowego.

Korzystając z menu „Scheme to new symbol” utworzyć symbol 4-bitowego sumatora równoległego.

Sprawdzić działanie pełnego sumatora jednobitowego. Jako sygnały wejściowe należy zadawać odpowiednie stany logiczne na piny wejściowe odpowiadające poszczególnym składnikom tzn. A i B, a następnie odczytywać sygnały wyjściowe w postaci binarnej na wyjściu sumy S.

Wielobitowy binarny układ sumatora-subktraktora (dodająco-odejmującego).

Odejmowanie wielobitowe binarne równoległe.

Wypełnić tablicę prawdy układu jednobitowego, którego zadaniem jest wytworzenie negacji (U1) liczby wejściowej dla operacji odejmowania oraz przepisanie jej na wyjście bez zmian w przypadku operacji dodawania.

Zdefiniować siatki Karnaugh

Dokonać minimalizacji funkcji:

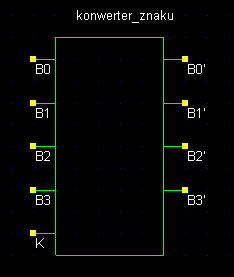

Zrealizować 4-bitowy układ komplementera (programowalnej negacji w zależności od wyboru operacji) w programie DSCH2:

Korzystając z menu „Scheme to new symbol” utworzyć symbol 4-bitowego sumatora równoległego.

Sprawdzić działanie 4-bitowego komplementera (konwertera znaku). Jako sygnały wejściowe należy zadawać odpowiednie stany logiczne na piny wejściowe odpowiadające poszczególnym bitom składnika II / odjemnika B, a następnie odczytywać sygnały wyjściowe w postaci binarnej na wyjściu B'.

Używając gotowych ogniw zaprojektować przetestować działanie pełnego 4-bitowego układu dodająco-odejmującego (sumatora-subtraktora).

Korzystając z menu „Scheme to new symbol” utworzyć symbol układu dodająco-odejmującego (sumatora-subtraktora).

przetestować działanie pełnego 4-bitowego układu dodająco-odejmującego (sumatora-subtraktora) . Jako sygnały wejściowe należy zadawać odpowiednie stany logiczne na piny wejściowe odpowiadające poszczególnym składnikom / odjemnej / odjemnikowi tzn. A i B, a następnie odczytywać sygnały wyjściowe w postaci binarnej na wyjściu sumy / różnicy S i bitu znaku.

Wejścia |

|

|

Wyjścia |

|

Składnik I Ai |

Składnik II Bi |

Przeniesienie Ci |

Suma Si |

Przeniesienie Ci+1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AiBi |

|

|

|

Ci |

00 |

01 |

11 |

10 |

0 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

Si |

|

AiBi |

|

|

|

Ci |

00 |

01 |

11 |

10 |

0 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

Ci+1 |

|

|

|

|

|

|

|

|

|

|

Si =

Ci+1 =

Wejścia |

|

|

Wyjścia |

|

Pożyczka Vi |

Odjemna Ai |

Odjemna Bi |

Różnica Di |

Pożyczka Vi+1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AiBi |

|

|

|

Vi |

00 |

01 |

11 |

10 |

0 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

Di |

|

AiBi |

|

|

|

Vi |

00 |

01 |

11 |

10 |

0 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

Vi+1 |

|

|

|

|

|

|

|

|

|

|

Di =

Vi+1 =

Di =

Vi+1' =

Uwaga: Przy sumowaniu liczb dodatnich wejście przeniesienia początkowego C0 nie jest wykorzystywane (C0=0).

Uwaga: Podczas dyskusji odnośnie odejmowania jednobitowego stwierdzono bardzo istotną zależność, że odejmowanie polega na dodawaniu negacji ( uzupełnienia do 1 - U1) odjemnika.

A-B = A + (-B),

czyli aby odjąć od odjemnej A odjemnik B, należy dodać do liczby A liczbę (-B). Zasada ta jest również podstawą odejmowania wielobitowego

Jednym ze sposobów uzyskania ujemnej reprezentacji odjemnika jest przedstawienie go zapisie uzupełnienia do jednego (U1), czyli poprzez przepisanie wszystkich bitów z zaprzeczenie (uzupełnienie do 1 liczby binarnej jest zawsze negacją bitów tej liczby).

Wskazówka: Wprowadzić bit wyboru operacji K przyjmujący wartość „logicznego 0” dla operacji sumy oraz „logicznej 1” w przypadku realizacji przez układ różnicy liczb.

Wejścia |

|

Wyjścia |

Wybór operacji K |

Składnik II/ Odjemnik Bi |

Składnik II/ Odjemnik Bi' |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|

Bi |

|

|

|

Ki |

0 |

1 |

||

0 |

0 |

1 |

||

1 |

1 |

0 |

||

|

|

Bi' |

|

|

|

|

|

|

|

Bi '=

Uwagi odnośnie operacji odejmowania:

1. Gdy podczas odejmowania istnieje przeniesienie z najbardziej znaczącej pozycji C3 to wynik zostaje zwiększony o jeden, czyli przeniesienie dodajemy do najmniej znaczącej pozycji.

2. Jeżeli wynik dodawania jest dodatni (gdy nie występuje przeniesienie z najbardziej znaczącej pozycji) to otrzymana liczba jest szukaną liczbą binarną.

3. Jeżeli natomiast wynik jest ujemny (przeniesienie z najbardziej znaczącej pozycji istnieje) to należy wykonać na nim jeszcze raz zapis U1, pozostawiając bit znaku bez zmian, i wtedy wynik przyjmie postać binarną.

Uwagi odnośnie operacji dodawania:

W przypadku dodawania dwu liczb 4-bitowych może zajść przypadek, że wynik będzie większy od „15”. Zajdzie wówczas konieczność zastosowania kolejnego bitu do jego zapisu. Zostanie wówczas wytworzony bit przeniesienia, który będzie traktowany jako najbardziej znaczący bit sumy. Dlatego też należy zastosować jeszcze jeden układ sumatora 4-bitowego.

Wyszukiwarka

Podobne podstrony:

Cwiczenie 4 - Zegar, Energetyka AGH, Semestr IV, Elektronika

Cwiczenie 5 - Komparator, Energetyka AGH, Semestr IV, Elektronika

Cwiczenie 2 - Sterownik BCD na multiplekserach, Energetyka AGH, Semestr IV, Elektronika

ENERGETYKA2010 S4, Energetyka AGH, Semestr IV, Elektronika

Maszyny Elektryczne - Pytania Z Egzaminów (2), Energetyka AGH, semestr 4, IV Semestr, Maszyny Elekt

Maszyny Elektryczne - Pytania Z Egzaminów (4), Energetyka AGH, semestr 4, IV Semestr, Maszyny Elekt

Ćwiczenie M 5 - Oscyloskop - Sprawozdanie, Energetyka AGH, semestr 4, IV Semestr, Metrologia, LABO

Materiały kolos, Energetyka AGH, semestr 4, IV Semestr, Materiały Konstrukcyjne I Eksploatacyjne, Ś

Pracownia Paliw Stałych - KOLOKWIUM1, Energetyka AGH, semestr 4, IV Semestr, Technika Cieplna, LAB

Liczniki - sprawko, Elektrotechnika AGH, Semestr IV letni 2013-2014, Podstawy Elektroniki, Laborator

ogniwo metanolowe by Slupski, Energetyka AGH, semestr 5, V Semestr, Konwersja Energii, LABORKI, Ćwi

Zadania do testu, Elektrotechnika AGH, Semestr IV letni 2013-2014, Elektromechaniczne Przetwarzanie

sprawozdanieAGH vel Czaro, Elektrotechnika AGH, Semestr IV letni 2013-2014, Elektromechaniczne Przet

ściąga TWN 1-3, Elektrotechnika AGH, Semestr IV letni 2013-2014, TWN, Technika wysokich napięć - SEM

StablizatorySprawozdanie, Elektrotechnika AGH, Semestr IV letni 2013-2014, Podstawy Elektroniki, Pod

Ogniwo paliwowe metanolowo - powietrzne, Energetyka AGH, semestr 5, V Semestr, Konwersja Energii, L

więcej podobnych podstron