Akademia Górniczo-Hutnicza

im. Stanisława Staszica

w Krakowie

PROJEKT

Przedmiot: PODSTAWY STEROWANIA LOGICZNEGO

Temat: Sumator/substrator szeregowy.

Przygotowali: Wilk Piotr

Czapla Marek

Bulanda Michał

Założenia / cel projektu.

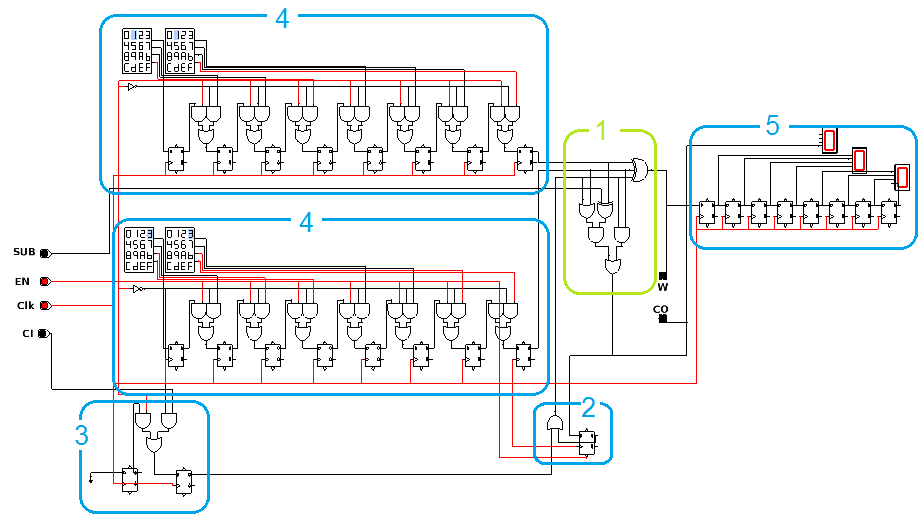

Celem projektu było zrealizowanie sumatora/substratora szeregowego z wykorzystaniem podstawowych funktorów logicznych oraz układów sekwencyjnych. Schemat ideowy został przedstawiony poniżej:

Rys. 1 Ogólny schemat układu.

A- wejście pierwszej przetwarzanej liczby

B- wejście drugiej przetwarzanej liczby

Cin- wejściowy bit przeniesienia lub pożyczki

S- bit decydujący o wykonywanym działaniu; 0-dodawanie, 1- odejmowanie

EN- rozpoczęcie dodawania/odejmowania

CLK- wejście zegarowe

W- wynik aktualnie przetwarzanych bitów

Cout- wyjściowe przeniesienie/pożyczka

REALIZACJA PROJEKTU

Układ sumatora/substratora składa się 5 głównych podukładów funkcyjnych.

Rys. 2 Schemat przedstawiający poszczególne bloki funkcyjne realizowanego układu.

1. Sumator/substrator właściwy- jest to układ, który sumuje lub odejmuje zadane bity zależnie od wartości bitu sterującego S. Układ ten jest sercem całego układu sumatora/substratora.

S- bit sterujący

A, B- bity wejściowe

Ct-1- bit pożyczki/przeniesienia wypracowany w poprzednim cyklu (ewentualnie bit wejściowego przeniesienia/pożyczki)

Ct- przeniesienie lub pożyczka wypracowane w obecnym cyklu

Zapisana została tabela prawdy układu.

S |

Ct-1 |

A |

B |

|

W |

Ct |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

|

0 |

0 |

Tab. 1 Tabela prawdy bloku sumującego/odejmującego bity.

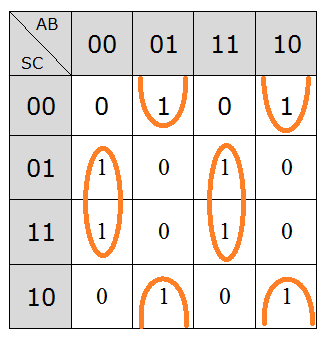

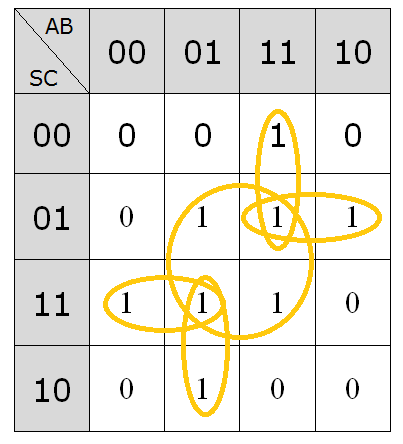

Funkcje FW oraz FC zostały zminimalizowane przy pomocy tablic Karnaugh'a.

![]()

Tab.2 Tablica Karnough'a funkcji FW

Tab.3 Tablica Karnough'a funkcji FC

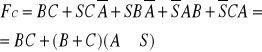

Obie funkcje zostały zrealizowane na bramkach logicznych.

Rys.3 Realizacja układu sumatora na bramkach logicznych.

2. Przerzutnik opóźniający typu D, odpowiedzialny za przekazywanie bitu przeniesienia/pożyczki wypracowanego w obecnym cyklu do cyklu następnego.

Rys.4 Realizacja układu przerzutnika opóźniającego D.

3. 2-bitowy rejestr przesuwny PISO, odpowiedzialny za obsługę wejściowego bitu pożyczki lub przeniesienia Ci

Rys.5 Realizacja układu do wprowadzania bitu przeniesienia(pożyczki).

Powyższy układ został tak skonstruowany, aby w przypadku wprowadzenia bitu przeniesienia(pożyczki) został on przetworzony jedynie w pierwszym cyklu sumowania (tzn. uwzględniony tylko w dodawaniu/odejmowaniu pierwszego bitu).

Pierwszy bit podawany na wyjście układu zależny jest od ustawienia bitu Ci . Dla każdego kolejnego bitu układ daje na wyjście 0. Wartość z wyjścia układu jest sumowana z bitem przeniesienia/pożyczki wypracowanym przez główny układ sumatora i opóźniony przez przerzutnik D (bramka OR w poprzednim schemacie).

4, 5. Rejestry PISO oraz SIPO, pełniące funkcje buforów dla danych wejściowych oraz wyjściowych. Zastosowanie ich zlikwidowało konieczność mozolnego wprowadzania danych po jednym bicie oraz takim samym odczytywaniem wyniku w przypadku długich liczb. Rejestry wejściowe zostały podłączone do klawiatur, a wyjściowy do wyświetlaczy siedmiosegmentowych w celu zapewnienia wygodniej obsługi.

Rys.6 Realizacja rejestru PISO.

Rys.7 Realizacja rejestru SIPO.

W powyższym układzie wyświetlacz odpowiedzialny za wyświetlanie najstarszego bitu został bezpośrednio podłączony do sumatora przez wyjście przeniesienia, przez co możliwe jest wyświetlanie wyniku 3-cyfrowego.

Operacje sumowania lub odejmowania są realizowane w następujący sposób:

Składniki (lub odjemna i odjemnik) są wprowadzane przy użyciu klawiatur. Następnie przy jednym zboczu rosnącym zegara wartości zostają zapisane w dwóch 8-bitowych rejestrach PISO. Gdy poszczególne wartości znajdują się już w buforach, wartością 1 na wejściu EN zostaje wydane pozwolenie na wykonanie danego działania i po pojawieniu się ośmiu zboczy rosnących na zegarze (zsumowanie wszystkich bitów rejestrów wejściowych) nastąpi wyświetlenie pożądanego wyniku na wyświetlaczach.

PODSUMOWANIE

Zaprojektowany oraz zrealizowany sumator poprawnie sumuje oraz odejmuje 2-cyfrowe liczby wyświetlając wynik na trzech wyświetlaczach 7-segmentowych. W przypadku odejmowania, gdy wynik jest liczbą ujemną, zostaje użyty zapis dopełnienia do dwóch. Jedyną niedogodnością przy korzystaniu z sumatora/substratora jest ręczna obsługa impulsów zegara.

Wyżej wymienione ograniczenie długości liczb wynika jedynie z wielkości rejestrów jakie zastosowaliśmy. Jednak sam układ sumujący/odejmujący jest w stanie obsłużyć liczby dowolnej długości (zgodnie z założeniami).

Dzięki temu doświadczeniu poszerzyliśmy swoją wiedzę na temat funktorów logicznych, układów sekwencyjnych oraz ich praktycznego zastosowania w konstruowaniu układów spełniających określoną funkcję.

Wyszukiwarka

Podobne podstrony:

FiltryAdaptacyjne sprawozdanie, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, Teoria i

filtracja adaptacyjna, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, Teoria i Przetwarz

projekty-2011-2012, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C),

A-03 Komparator, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C), Pod

2Filtry analogowe, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C), T

EA5, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C), Elektromaszynow

kolokwium2-ts, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, Teoria i Przetwarzanie Syg

sprawko kompensacja, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C),

Licznniki, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C), Podstawy

jh, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C), Podstawy sterowa

substraktor jakis ale spoko, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (m

Liczniki1, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C), Podstawy

3-fazowe silniki indukcyjne, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (m

FIRy, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, Teoria i Przetwarzanie Sygnałów, Ko

TC-S-04 Rejestry, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C), Po

Sprawko PSL, Elektrotechnika AGH, Semestr V zimowy 2014-2015 - MODUŁ C, semestr V (moduł C), Podstaw

więcej podobnych podstron